國

立

交

通

大

學

電機學院 電信學程

碩

士

論

文

3.1-10.6GHz 互補式金氧半製程之超寬頻低雜

訊放大器

3.1-10.6GHz UWB CMOS Low-noise Amplifier

研 究 生:馬家國

指導教授:周復芳 博士

國

立

交

通

大

學

電機學院 電信學程

碩

士

論

文

3.1-10.6GHz 互補式金氧半製程之超寬頻低雜

訊放大器

3.1-10.6GHz UWB CMOS Low-noise Amplifier

研 究 生:馬家國

指導教授:周復芳 博士

3.1-10.6GHz 互補式金氧半製程之超寬頻低雜訊

放大器

3.1-10.6 GHz UWB CMOS Low-noise Amplifier

研 究 生:馬家國 Student:Chia-Kuo Ma

指導教授:周復芳 博士 Advisor:Dr.Christina F. Jou

國 立 交 通 大 學

電機學院 電信學程

碩 士 論 文

A ThesisSubmitted to College of Electrical Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science

in Communication Engineering April 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年四月

i

3.1-10.6GHz 互補式金氧半製程之超寬頻低雜訊

放大器

研 究 生:馬家國 指導教授:周復芳 博士

國立交通大學電機學院電信學程(研究所)碩士班

中文摘要

本篇論文主要是探討超寬頻低雜訊放大器之設計與分析。為了達到寬頻的輸 入匹配,我們利用電阻電容負載的方式,分別對高頻及低頻作輸入匹配,及利用 電感(LS)、電容(Cgd)回授來達成輸入匹配;為了達到寬頻的增益,使用並串連尖 峰(shunt-series peaking)電感的頻寬延伸技術來完成寬頻增益的目的;利用修改後 的疊接(cascode)架構電路,獲得較大的增益與隔絕度;此放大器利用第一級的輸 出端負載及一個電感 (Lg)作匹配,以減少輸入端的匹配元件,可有效改善高頻 的雜訊指數;最後加上一級源極追隨器(source follower)完成輸出阻抗匹配。這個 寬頻低雜訊放大器量測結果如下:頻寬為 3.1 ~ 10.6 GHz,平均增益為 9.9 dB, 雜訊指數為 3.9 ~ 4.9 dB,輸入反射係數為 -7.7 ~ -12 dB,input P1dB最小值為 -15.5dBm,IIP3 最小值為-4.5dBm,功率消耗為 51.3mW。ii

3.1-10.6GHz UWB CMOS Low-noise Amplifier

Student:Chia-Kuo Ma Advisor:Dr.Christina F. Jou

Master Program of Communication Engineering

National Chiao Tung University

Abstract

This thesis discusses the design and analysis of an ultra wideband low-noise amplifier. Resistive and capacitive loading with shunt-shunt feedback (LS-Cgd) can achieve input

wideband matching. In order to obtain the wide-band gain, the shunt-series peaking inductor (Ld2-Lpk) is used to extend the bandwidth. A modified cascode structure is

used to achieve the sufficient gain and isolation. In the meantime, the only one inductor (Lg) is used as input matching network, so the noise figure is good. The final

stage is source follower for output matching. The UWB LNA measured result are as follows: The bandwidth is 3.1 ~ 10.6 GHz. The average gain is 9.9 dB. The noise

figure is 3.9 ~ 4.9 dB. The input return loss is -7.7 ~ -12 dB. The input P1dB(min.) is

iii

致 謝

研究所將近三年的日子裡,需要兼顧學業、工作與家庭,讓我更覺得時間的 可貴。很榮幸的,我有機會寫這篇致謝,因為有太多的人需要感謝,首先我要感 謝我的指導教授周復芳博士,由於您的鼓勵與指導,提升我射頻領域的視野並吸 收到很多寶貴的知識;同時要感謝口試委員張志揚教授與胡政吉博士的蒞臨指 導,使這篇論文更加完整;另外,在晶片的設計過程中,特別要感謝匯儀與子豪 的指導,使晶片的特性趨於完善;在佈局與下線的過程中,特別要感謝沛遠、志 豪與昱順的協助,使晶片能夠下線順利,在晶片的測試上,也要感謝昱順不厭其 煩的耐心量測,還有俊偉、智鵬、宜星、岳昌及實驗室的所有學弟們在生活上的 照顧與幫忙。 最後我要感謝我的家人,尤其是我老婆佳慧的支持與協助,才能讓我在學業 上無後顧之憂,全力衝刺,此時正值我老婆懷孕,也督促著我,要儘快完成學業, 期待寶貝女兒的到來。同時我要感謝我的父母與兄姐,由於你們的鼓勵,讓我在 學業的進修上更加堅持,讓我能順利的完成碩士學業,最後,僅以此論文獻給我 最親愛的家人及身邊所有關懷我的朋友們,並與你們分享我的喜悅。iv

目 錄

中文摘要………..…...i

英文摘要………..…..ii

致謝……….….….iii

目錄……….………..iv

表目錄………...vi

圖目錄………..…vii

第一章 緒論……….…...1

1.1 背景………..……….1

1.2 論文組織……….…….2

第二章 寬頻電晶體放大器設計………3

第三章 超寬頻低雜訊放大器設計………6

3.1 電路結構

……….6

3.2 輸入匹配網路

………. 9

3.3 寬頻延伸

………..14

第四章 晶片製作的實現與量測的結果………..…18

4.1 佈局考量

………...18

4.2 量測考量………...19

4.2.1 S 參數

……….……..20

4.2.2 Noise Figure 參數

………....21

v

4.2.3 Input P1dB參數

………21

4.2.4 IIP3 參數

………...22

4.3 量測結果與討論

……….22

4.4 比較

………...…….29

第五章 結論………...….30

參考文獻………..31

vi

表 目 錄

表 4.3.1 量測與模擬數據比較表……….………....29

表 4.4.1 UWB LNA 量測結果比較表………..29

vii

圖 目 錄

圖 2.1 補償配原理……….………3

圖 2.2 平衡式放大器……….………3

圖 2.3 電阻性匹配網路……….…………4

圖 2.4 串聯電阻負回授法……….……….4

圖 2.5 並聯電阻負回授法……….……4

圖 2.6 散佈並接放大器……….…….5

圖 3.1.1 3 級共源級放大器電路結構………6

圖 3.1.2 參考文獻[4]的放大器電路結構………..7

圖 3.1.3 超寬頻低雜訊放大器電路結構……….…..9

圖.3.2.1 超寬頻低雜訊放大器小信號等效電路……….9

圖 3.2.2 超寬頻低雜訊放大器小信號等效電路高頻模式………10

圖.3.2.3 超寬頻低雜訊放大器小信號等效電路低頻模式(a)……….10

圖 3.2.4 超寬頻低雜訊放大器小信號等效電路低頻模式(b)………..11

圖 3.2.5 超寬頻低雜訊放大器小信號等效電路低頻模式(c)………..12

圖 3.2.6 虛線 1 是方程式 3-2-2 的計算結果, 實線 1 是方程

式 3-2-2 的模擬 結果,虛線 2 是 Ya

的計算結果……….12

圖 3.2.7 曲線 1 代表 LS1=200pH 的輸入反射係數,曲線 2 代表 LS1=38pH

viii

的輸入反射數 ………..13

圖 3.2.8 曲線 1 為不加 Lg

電感時的輸入反射係數,曲線 2 為加上 Lg

電感時的輸入反射係數………..13

圖.3.2.9 超寬頻低雜訊放大器輸入反射係數(S11)………14

圖 3.3.1 並聯尖峰共閘極放大器………14

圖 3.3.2 並聯尖峰共閘極放大器等效電路………15

圖 3.3.3 並串聯尖峰共閘極放大電路……….16

圖 3.3.4 並聯尖峰與並串聯尖峰共閘極放大器頻率響應比較………16

圖 3.3.5 並聯尖峰與並串聯尖峰共閘極放大器雜訊指數比較……….17

圖 4.1.1 超寬頻低雜訊放大器佈局圖(1.06 X 1 mm

2)………...18

圖 4.1.2 超寬頻低雜訊放大器縮影照片(1.06 X 1 mm

2)…………..19

圖 4.2.1 量測下針圖……….20

圖 4.2.1.1 S 參數量測圖………..20

圖 4.2.2.1 N.F. 量測圖………...……….21

圖 4.2.3.1 Input P1dB

測圖………...…...21

圖 4.2.4.1 IIP3 量測圖……….22

圖 4.3.1 S21……….24

圖 4.3.1 S11………..24

圖 4.3.1 S22………..24

ix

圖 4.3.1 S12………..…..25

圖 4.3.5 NF………..…...25

圖 4.3.6 Input P1dB………..…..25

圖 4.3.7 IIP3………..……...26

圖 4.3.8 S21 修改後圖形………..……...…26

圖 4.3.9 S11 修改後圖形………..……...……26

圖 4.3.9 S22 修改後圖形………..………...……27

圖 4.3.9 S12 修改後圖形………..…………...……27

圖 4.3.12 最小 k 值………27

圖 4.3.13 1-20GHz 的 K 值………28

圖 4.3.14 1-20GHz 的 delta 值………28

1

第一章

緒論

1.1. 背景

近年來,隨著網路及通信技術不斷的發展,無線通信技術得到迅速的進步, 無線通信技術在人們生活中發揮著越來越重要的功能。在 2002 年美國聯邦通信 委員會 ( FCC ) 正式立法通過超寬頻無線通訊技術 (UWB),開放頻率從 3.1GHz ~10.6GHz,它可將大量的資料,以此寬頻率範圍,在極短的時間內發射出去, 因此具有高傳輸速率、低耗電量、低成本、抗干擾及保密性好等特性,並且成為 極具競爭力的短距離無線傳輸技術。曾經有二十多個標準在競爭,如今只剩下 DS-CDMA (Direct Sequence-CDMA)及 MBOA (Multi-Band OFDM Alliance) 這兩個標準,DS-CDMA 技術是單頻帶方式或窄脈衝方式,多個傳輸任務可共 享整個頻帶頻率,對現有的、許可頻帶內的用戶造成的干擾比較小,成本可做的 比較低,易於實現低功耗無線傳輸,可實現更高速數據無線傳輸;MBOA 技術 是多頻帶方式,技術上易於實現,功耗可以很低,頻帶的利用率高,多個頻率子 帶並列,可以避開某些頻帶、靈活配置,速率的擴展性好。所以 UWB 可說是未 來個人近距離無線傳輸的主流技術,在發展初期,為了迅速讓消費市場所接受, 預期將會先由目前佔消費市場比重最大的資通訊產品著手,利用既有市場,來促2 使 UWB 技術普及化,主要的應用有三項:1. 影像系統( 低於 960MHz 及 1.99-10.6GHz)、2.車用雷達(22-29GHz)、3.通訊量測系統(3.1-10.6GHz)。

1.2. 論文組織

本論文內容分為五個章節;第一章為緒論,說明超寬頻的基礎概念與論文結 構,第二章在探討寬頻電路所使用的相關技術,第三章將詳述此顆晶片的設計原 理與概念,第四章將說明晶片的電路佈局概念、量測數據與模擬數據的比較及此 顆晶片與其他論文的比較,最後一章為此篇論文的總結。

3

第二章

寬頻電晶體放大器設計[1]

設計寬頻微波放大器時,一般常用的方法如下所列,要注意的是,在每一種 改善頻寬的方法中,均必須付出相對的代價,如增益、雜訊指數、電路複雜度等。 1. 補償匹配網路 :妥善設計輸入端與輸出端的匹配網路,可補償|S21|增益隨 頻率增加的遞減,但可能也同時犧牲輸入與輸出的匹配品質如圖 2.1 所示。 圖 2.1 補償配原理 2. 平衡式放大器:如圖 2.2 所示,在兩放大器的輸入與輸出端同時使用 900 耦 合器,就有可能得到一個倍頻以上的頻寬。其增益與單顆電晶體放大電路的 增益相同,但是此種設計需要兩顆晶體,以及兩倍的 DC 功率。 . . . . . . . . . . 圖 2.2 平衡式放大器 RFin Z0 GB GA RFout Z0 900 Hybrid 900 Hybrid S21 VSWR Degraded Final4 3. 電阻性匹配網路:如圖 2.3 所示,使用電阻性匹配網路,可以得到很好的輸 入與輸出匹配,但增益會減小,雜訊指數會增加。 圖 2.3 電阻性匹配網路 4. 負回授:如圖 2.4 ~ 2.5 所示,負回授可以使增益的響應變的較為平坦,改善 輸入與輸出的匹配,並增進電路的穩定性。用這種方法設計的放大器,頻寬 可達十倍頻以上,代價是功率增益與雜訊指數。 圖 2.4 串聯電阻負回授法 圖 2.5 並聯電阻負回授法 5. 散佈並接放大器:如圖 2.6 所示,沿著傳輸線,將一些電晶體串接起來,可 以在寬頻中得到很好的增益、匹配、及雜訊指數。但其電路較佔面積,且其 總增益不如同樣級數的單顆晶體放大器增益之相乘效果。 R R R

5 . . 圖 2.6 散佈並接放大器 Q1 Li Z0 Z0 Q2 Q3 Qn RFout RFin Li Li Li Li Li Li Li

6

第三章

超寬頻低雜訊放大器

3.1. 電路結構[2,4]

參考文獻[2]的電路架構如圖 3.1.1 所示,為 3 級共源級(common source)放 大器串接,在第一級放大器的輸出端,串上 RC 負載做為輸入匹配,而在第三級 輸出端串上電容與電阻作為輸出匹配,以此簡潔的電路架構可使低雜訊放大器達 到寬頻與低雜訊的結果,與傳統利用 LC 來做輸入匹配,需要更大的面積,同時 輸入匹配的元件數增加將使得 NF 變的更差,於是此電路架構受到本實驗室學長 們的注意,此電路使用的製程為 HEMT,其量測結果如下 :頻寬 (Bandwidth):10-20GHz、輸入反射係數(S11)<-10、增益(S21)~20dB、雜訊指數(Noise Figure):1.4~1.6dB、功率消耗(Power consumption)=39.6mW。 圖 3.1.1 3 級共源級放大器電路結構

7

參考文獻[4]為本實驗室學長,參考上述架構後,所設計的寬頻低雜訊放 大器,如圖 3.1.2 所示。他將第二級共源級放大器改為共閘級放大器,形成修改 過的疊接架構(coscode structure),可獲的較好的頻率響應(Frequency Response) 及隔絕度(Isolation),在第一級放大器的輸入端串上一顆電感,同時加入一顆回 授電容,使輸入反射係數(S11)效果更好,將第三級共源級(common source)放大 器改為共汲級(common drain)放大器,使得輸出匹配效果更好;而這顆晶片是使 用 CMOS 製程,其量測結果如下:頻寬(Bandwidth):2.75-7.7GHz、雜訊指數(Noise Figure):3.7-5.5dB、功率消耗(power consumption):21.1mW。 圖 3.1.2 參考文獻[4]的放大器電路結構 我引用學長的架構做了一些修改,首先將 Lg由 1nH 改為 0.466nH,同時 拿掉第一級的回授電容,而把 R1 由 32K ohm 降為 1K ohm,這樣將使輸入反射 係數在低頻時保持負值,使系統更穩定,NF 會更好,同時在第二級放大器的輸

8 出端串上一顆 series peaking 電感,使增益在高頻時不會有明顯下滑的現象,達 到寬頻的結果。 此電路使用台灣積體電路製造公司(TSMC)0.18um CMOS 製程設計製作 完成。前後兩個電容 Cb1,Cb2為量測 RF 時,阻隔直流電源,避免直流電源跑進 網路分析儀,M1為共源極(common source)放大器,可提供很高的輸入阻抗(只 受限偏壓電阻 R1的大小限制),很大的負電壓增益及很大的輸出電阻,R1、Ld1、

Rd1、Ld2、Rd2及 LS2為 RF choke,LS1與 Lg為 Noise Figure 及 S11的匹配電路關鍵

點, M2為一個共閘極(common gate)放大器,其輸入阻抗 Rin≅ 1/Gm與 C01形成 M1的 RC 負载電路,分別對高頻及低頻作輸入匹配,及利用電感(LS1)與電容(Cgd) 回授來達成輸入匹配;同時 Lg、LS1、M1、C01、M2、Ld2、Rd2形成一個修改後的 疊接(cascode)架構,提供較好的頻率響應(frequency response)與隔絕度 (isolation);利用並串連尖峰(shunt-series peaking)電感(Ld2-Lpk)的頻寬延伸技 術,來達成頻寬延伸的目的,Mb為一個源極追隨器(source follower)與 Mi 組 合後,用來提供一個高輸入阻抗,低輸出阻抗和電壓增益接近一的緩衝放大器, 調整緩衝放大器,使 Rout≅ 1/Gm=50 Ohm,作為此超寬頻低雜訊放大器的輸出匹 配。此電路結構如圖 3.1.3 所示,使用偏壓 VDD=1.8V,Vbias=0.7V,量測結果: 頻寬為 3 .1~ 10.6 GHz,平均增益為 9.9 dB,雜訊指數為 3.9 ~ 4.9 dB,輸入反射 係數為 -7.7 ~ -12 dB。

9 . . . . . . . . . . . . 圖 3.1.3 超寬頻低雜訊放大器電路結構

3.2. 輸入匹配網路[2]

傳統窄頻低雜訊放大器的輸入匹配,在輸入端使用複雜的 LC 匹配網路來完 成,這樣將造成在矽這樣的損耗基板上,會有較高的雜訊指數(noise figure)及較 大的訊號衰減;此電路利用第一級放大器輸出端的 RC 負載及 LS1 與 Cgd 回授 (feedback)及 Lg作輸入匹配,降低輸入端的匹配網路複雜度,以達到寬頻的需求。 圖 3.2.1 為超寬頻低雜訊放大器小信號等效電路,為了分析輸入匹配網路, 將它分成高頻模式及低頻模式分別如圖 3.2.2 及圖 3.2.3 所示。 . 圖.3.2.1 超寬頻低雜訊放大器小信號等效電路 RFin Cb1 Cb2 VDD VDD VDD Ld1 Rd1 C01 M1 LS1 Vbias M2 LS2 Ld2 Rd2 C02 R2 Vbias Mb Mi Vbias RFout Lg R1 Lpk G Cgs Lg Cgd C01 RL LS Vgs r0 GmVgs10 . 圖 3.2.2 超寬頻低雜訊放大器小信號等效電路高頻模式 . 圖.3.2.3 超寬頻低雜訊放大器小信號等效電路低頻模式(a) 在高頻模式下,假設ωLS << 1/ωCgs,ωLS << RL,由圖 3.2.2 小信號等效電 路可求出輸入阻抗方程式(3-2-1)如下: ZinH= jωLg

+(

gs C jω 1+

gs m S C G L γ)(

1+ gs gd C C (1+γGmRL))-1 (3-2-1) γ = S L j L R r r ω + + 0 0 Lg Cgd RL G Cgs Vgs GmVgs LS r0 ZinH Lg Cgs VgS ZinL G Cgd LS GmVgs r0 C0111 在低頻模式下,如圖 3.2.3 超寬頻低雜訊放大器小信號等效電路所示,藉由 KVL,KCL 可逐步化簡成圖 3.2.4 及圖 3.2.5 等效電路,可推出其低頻模式下的 輸入阻抗方程式(3-2-2)如下: ZinL= jωLg

+

(Y +a b Z 1 )-1 (3-2-2) a Y = 1 2 1 V V V C jω gd − = jωCgd+(R +a a C jω 1 + jωLa)-1 a R = gd mC G C01 , C =a Gmr0Cgd , L =a gd m S C r G C L 0 01 (1+Gmr0 ) b Z = gs C jω 1 3 1 1 V V V − = jωCgs 1 +( b R 1 + jωCb+ b L jω 1 )-1 b R = gs S m C L G , C =b 0 r G C m gs , L =b gs m S C C r G L 0 01 圖 3.2.4 超寬頻低雜訊放大器小信號等效電路低頻模式(b) Lg G Cgs GmRdsVc Rds Cgd C01 Vc Zb LS V1 V2 V3 Ya12 圖 3.2.5 超寬頻低雜訊放大器小信號等效電路低頻模式(c) 在低頻模式下的匹配頻率可用公式(3-2-3)近似如下: 0 f

=

a aC L π 2 1=

) 1 ( 2 1 0 01 G r C LS + m π(3-2-3)

在低頻模式下,計算與模擬的輸入反射係數的 SMITH 圖的比較如圖 3.2.6 所示: 圖 3.2.6 虛線 1 是方程式 3-2-2 的計算結果, 實線 1 是方程式 3-2-2 的模擬 結 果,虛線 2 是 Ya的計算結果 La Lg Cgs Cb G Zb Lb Rb Ra Ca Ya Cgd13 LS1的大小對輸入反射係數的影響如圖 3.2.7 所示: 圖 3.2.7 曲線 1 代表 LS1=200pH 的輸入反射係數,曲線 2 代表 LS1=38pH 的輸入反射數 第一級放大器輸入端的 Lg電感對輸入反射係數的影響如圖 3.2.8 所示:

圖 3.2.8 曲線 1 為不加Lg電感時的輸入反射係數,曲線 2 為加上Lg電感時的輸入反 射係數

14 由上述輸入匹配網路的分析,可獲得在不同的製程變異下的輸入反射係數 (S11)如圖 3.2.9 所示:

0

5

10

15

-40

-30

-20

-10

0

Frequency , GHz dB TT FF SS 圖.3.2.9 超寬頻低雜訊放大器輸入反射係數(S11)3.3. 頻寬延伸[3]

此電路利用頻寬延伸技術,達到寬頻的目的。圖 3.3.1 為一個簡單的共閘極(common gate)放大電路,L 為並聯尖峰(shunt peaking)電感,R 為負載電阻,C1

為汲極寄生電容,C2為負載電容及下一級的閘極電容。 . . 圖 3.3.1 並聯尖峰共閘極放大器 V M2 Mb C2 C1 Vin R L Vout

15 其等效電路如圖 3.3.2 所示,我們可由歐姆定律導出其阻抗表示式(3-3-1) 如下: ) (s Z = Iin Vout =( sC 1 )∥(R+sL)= LC s sRC sL R 2 1+ + +

(3-3-1) 將Z(s)標準化後得到方程式(3-3-2): = ) (s Z 0 2 0 0 / / 1 / 1 ω ω ω m s s m s + + + ,ω0 =1/RC,m=R2C/L (3-3-2) 由(3-3-2)式可知,此放大電路有兩個極點一個零點。 . . 圖 3.3.2 並聯尖峰共閘極放大器等效電路 圖 3.3.3 為此篇論文所用的並串聯尖峰(shunt-series peaking)放大電路。我 們一樣也可由歐姆定律導出其阻抗表示式(3-3-3)如下: 4 0 4 2 1 3 0 3 2 2 0 2 2 1 0 0 1 ) 1 ( ) 1 ( ) 1 1 ( 1 ) 1 ( 1 ) ( ω ω ω ω ω s m m k k s m k k s m k m s s m s Z C C C C C + − + − − + + + + = (3-3-3) C C kC = 1/ ,m1 =R2C/ L1 ,m2 =R2C/ L2 ,C=C1 +C2 由(3-3-3)式可知,此放大電路有四個極點一個零點;比較式 3-3-2 與式 3-3-3 可知,在加入一個電感(L2)後增加了兩個極點,利用極點數的增加,來 達成頻寬延伸的目的。 V Vin C=C1+C2 Vout M2 Iin R L Mb

16

.

.

圖 3.3.3 並串聯尖峰共閘極放大電路

圖 3.3.4 為並聯尖峰(shunt peaking )電路與並串聯尖峰電感(shunt-series

peaking)電路的輸出頻率響應比較圖;由圖中可得到頻寬分別為 4.5GHz 及 9.7GHz,頻寬增加 5.2GHz 其 BWER(Bandwidth extension ratios)為 (4.5+5.2) / 4.5=2.16;圖 3.3.5 為其相對應的雜訊指數比較圖,從圖中可知增益與雜訊指數 呈反比,增益愈高雜訊指數就愈低。

0

5

10

15

0

5

10

15

Frequency , GHz dB shunt-series peaking shunt peaking 圖 3.3.4 並聯尖峰與並串聯尖峰共閘極放大器頻率響應比較 V L1 M2 L2 C1 Mb C2 R Vin Vout17

0

5

10

15

2

3

4

5

6

Frequency , GHz dB shunt-series peaking shunt peaking 圖 3.3.5 並聯尖峰與並串聯尖峰共閘極放大器雜訊指數比較18

第四章

晶片製作的實現與量測結果

4.1. 佈局考量

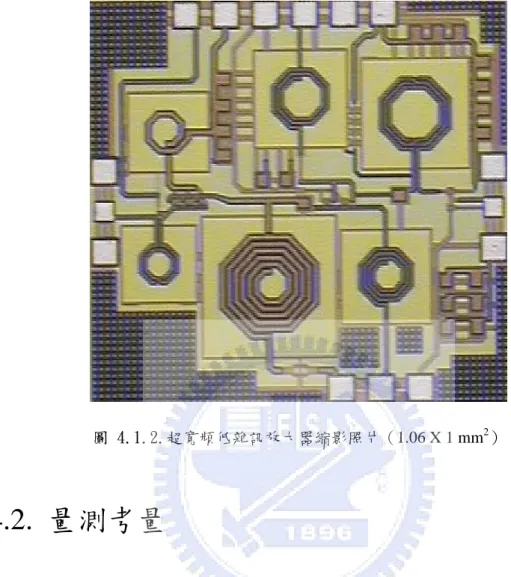

當電流流量為 1mA,金屬線寬至少 1um,走線轉角均須為 45 度角,避免尖 端放電產生。RF 走線盡量走最短距離,以減少損耗及不必要的電感電容效應; 若有長走線,均須將走線代入電磁模擬軟體,增加電路的正確性,DC 走線應加 上足夠的旁路電容,避免走線的電感效應。最後執行 DRC 和 LVS 驗證無誤後完 成佈局。此晶片尺寸為 1.06 X 1 mm2,如圖 4.1.1.所示。縮影照片如圖 4.1.2.所 示。 圖 4.1.1.超寬頻低雜訊放大器佈局圖(1.06 X 1 mm2)L

gM

bM

2M

1L

pkL

d2L

s2L

d1L

s119

圖 4.1.2.超寬頻低雜訊放大器縮影照片(1.06 X 1 mm2)

4.2. 量測考量

由於晶片測試是由國家晶片中心(Chip Implementation Center,CIC)協助 量測,所以晶片在佈局時,需依據 CIC 的測試規範;量測環境如圖 4.2.1.所示, 上方與下方為 DC PAD,提供電路所需的偏壓,左右兩邊為 RF 的輸入及輸出, 量測時,DC 探針均有加上對地的旁路電容約 100pF,此電路仍內接旁路電容約 6pF,避免低頻震盪。此電路進行 On Wafer 量測,量測項目包含有:S 參數、noise

20 圖 4.2.1. 量測下針圖

4.2.1. S 參數

量測圖如圖 4.2.1.1.所示,其中網路分析儀與探針之間的阻隔電容已納入模 擬時的考量。量測的範圍為 1G-20GHz,取樣 401 點,並做 128 次平均取樣。輸 入 POWER 為 -35dBm。 圖4.2.1.1. S 參數量測圖21

4.2.2. Noise Figure 參數

圖 4.2.2.1. 所示為 noise figure 量測圖,欲量測的頻率範圍為 3.0G-12GHz, 欲 0.5GHz 取樣一點共 19 點,並做 16 次平均取樣。 圖4.2.2.1. N.F. 量測圖4.2.3. Input P

1dB參數

如圖 4.2.3.1 所示,將輸入端接上 CIC 所提供的訊號產生器,將輸入訊號大 小做 SWEEP,並觀察頻譜分析儀上的圖形。 圖4.2.3.1. Input P1dB量測圖22

4.2.4. IIP3 參數

欲量測 IIP3 必須使用 two tone 測試的技巧,如圖 4.2.4.1.所示,需使用兩組 訊號源,two tone 頻率相差 10 MHz;(3.0 GHz 和 3.01 GHz)、(7.5GHz 和 7.51GHz)、(12.0 GHz 和 12.01 GHz),且輸入功率大小相等,由於放大器為非線 性電路,觀察 3 次諧波項和基頻項的關係。 圖4.2.4.1. IIP3 量測圖

4.3. 量測結果與討論

本論文的晶片是使用 TSMC 0.18um CMOS 製程,完成設計與製作;S 參 數的量測與模擬的數據比較圖顯示於圖 4.3.1. ~ 圖 4.3.4.,在整個 UWB 頻帶的 量測結果,S21:6.7 ~ 12.3 dB、S11<-7.7 dB、S22<-7.2 dB、S12<-31 dB。雜訊指

23 數的量測與模擬的數據比較圖顯示於圖 4.3.5,在整個 UWB 頻帶的量測結果: 3.9dB<雜訊指數<4.9dB。Input P1dB分成三個頻率點(3.1GHz、7.5GHz 及 12GHz) 作量測,其量測與模擬的數據比較圖顯示於圖 4.3.6.,P1dB量測結果如下:P1dB @ 3.1GHz = -15.5 dBm ,P1dB @ 7.5GHz = -15 dBm, P1dB @ 12GHz = -15dBm。IIP3 分成三個頻率點(3.1GHz、7.5GHz 及 12GHz)作量測,其量測與模擬的數據比

較圖顯示於圖 4.3.7.,IIP3 量測結果如下:IIP3@ 3.1GHz = -4.5 dBm ,IIP3@

7.5GHz = -4 dBm, IIP3@ 12GHz = -2 dBm。整個量測與模擬的數據比較如表 4.3.1.所示,模擬與量測主要的差異有 S21及 S22,利用模擬的方式調整元件值, 使模擬結果接近量測結果,來判定誤差造成的原因;由於 LS2(1.829nHÆ1.547nH, 15%)變小的誤差與 LS1(0.375nHÆ0.411nH, 9.1%)變大的誤差造成 LNA 在低 頻的增益變差,Ld2(1.418nHÆ1.587nH, 11.9%)變大的誤差與 POSTSIM 時漏掉 一條導線(Mb的汲極偏壓導線=0.3nH)造成 LNA 在高頻的增益凸起,同時這條導 線也會造成輸出反射係數在高頻變差,修改後的圖形如圖 4.3.8~圖 4.3.11 所示。 由於 LNA 在高頻時增益有突起的現象,所以將在 CIC 量測的 S 參數帶入 K 與 delta 的公式中來驗證系統是否符合無條件穩定的條件,公式如下所示: k= 1 21 12 2 22 11 1 2 2 2 > Δ + − − S S S S (4.3.1) Δ = S11S22−S12S21<1 (4.3.2)

驗證結果如圖 4.3.12~圖 4.3.14 所示,因此 UWB LNA 為無條件穩定;由於 CIC 的 S 參數量測數據是由 1GHz ~ 20GHz,所以 1GHz 以下沒有數據可供參考。

24

0

5

10

15

-10

0

10

20

Frequency , GHz dB Measurement Simulation 圖4.3.1. S21 0 5 10 15 -30 -20 -10 0 Frequency , GHz dB Measurement Simulation 圖 4.3.2. S110

5

10

15

-40

-30

-20

-10

0

Frequency , GHz dB Measurement Simulation 圖 4.3.3. S2225

0

5

10

15

-100

-80

-60

-40

-20

Frequency , GHz dB Measurement Simulation 圖 4.3.4. S12 0 5 10 15 2 4 6 8 Frequency dB Measurement Simulation NFmin 圖 4.3.5. NF 0 5 10 15 -19 -18 -17 -16 -15 Frequency , GHz dB m Measurement Simulation 圖 4.3.6. Input P1dB26 0 5 10 15 -8 -6 -4 -2 Frequency , GHz dB m Measurement Simulation 圖 4.3.7. IIP3 0 5 10 15 -10 0 10 20 Frequency , GHz dB Measurement Modification 圖 4.3.8. S21 修改後圖形 0 5 10 15 -20 -10 0 Frequency , GHz dB Measurement Modification 圖 4.3.9. S11 修改後圖形

27 0 5 10 15 -30 -20 -10 0 Frequency , GHz dB Measurement Modification 圖 4.3.10. S22 修改後圖形 0 5 10 15 -100 -80 -60 -40 -20 Frequency , GHz dB Measurement Modification 圖 4.3.11. S12 修改後圖形 2 4 6 8 10 12 14 16 18 0 20 1 2 0 3 freq, GHz k 圖 4.3.12. 最小 k 值

28 2 4 6 8 10 12 14 16 18 0 20 1000 2000 3000 0 4000 freq, GHz k 圖 4.3.13. 1-20GHz 的 K 值 圖 4.3.14. 1-20GHz 的 delta 值 2 4 6 8 10 12 14 16 18 0 20 0.05 0.10 0.00 0.15 freq, GHz d

29

表 4.3.1. 量測與模擬數據比較表

Specification Measurement Simulation

Bandwidth(GHz) 3.1 ~ 10.6 2.5 ~ 12 VDD(volt) 1.8 1.8 S21(dB) 6.7 ~ 12.3 10 ~ 12 S11(dB) max. -7.7 -9.9 S22(dB)max. -7.2 -10 S12(dB)max. -31 -31

Noise Figure(dB)min. 3.9 2.7

Input P1dB(dB)min. -15.5 -17.6

IIP3(dB)min. -4.5 -8.7

UWB LNA Power(mW) 45.2 41.5

Buffer Power(mW) 6.1 6.4

4.4. 比較

將此論文與 UWB LNA 相關論文的量測數據做比較,比較結果如表 4.4.1 所

示。

表 4.4.1 UWB LNA 量測結果比較表

BW S11 S22 Gain NF IIP3* VDD Power

Ref. Topology Process

(GHz) (dB) (dB) Avg.(dB) (dB) (dBm) (volt) (mW)

0.18um

This work N/A

CMOS 3.1-10.6 <-7.7 <-7.2 9.9 3.9-4.9 -4 1.8 51.3 0.18um [4]2007 N/A CMOS 2.75-7.7 <-10 <-10 10 3.7-5.5 -1 1.5 21.1 0.18um [5]2007 current reused CMOS 3.4-11.4 <-8 <-12 13.5-16 3.1-6 -7 1.8 11.9 0.18um [6]2007 Shunt-series

feedback CMOS 3.1-10.6 <-9 <-15 12 3.8-6 N/A 1.8 9.8

0.35um 20 1 40 [7]2006 Distributed SiGe BiCMOS 1.6-12.1 <-8 <-8 12 <6.5 N/A 0.8 6.4 *at 6GHz

30

第五章

結論

本論文提出 3.1-10.6GHz 之超寬頻低雜訊放大器的設計與製作;此晶片使用

高頻模擬軟體 ADS 與 MOMENTUM 模擬設計,使用 TSMC 0.18um CMOS 製程 來製作晶片,整個論文中,討論了設計的觀念,量測與模擬的結果比較及量測結 果的討論。

此晶片利用第一級放大器的輸出負載(RC Loading)及 兩個電感 (Lg,LS1)

作匹配,減少輸入端的匹配電路,有效的降低雜訊指數,使整個 UWB LNA 的 N.F.落在 3.9~4.9dB;而 cascode 架構提供較好的頻率響應(frequency response) 與隔絕度(isolation), 搭配 shunt-series peaking 電路,使得頻寬可達到

3.1~10.6GHz,同時在 UWB 的平均增益可達到 9.9dB;而在第一級放大器輸入端

串上一個電感,輸出端利用 RC 負載的方式並與 Cgd及 LS回授來達到寬頻的輸入

匹配,S11最大值為-7.7dB。

31

參 考 文 獻

[1] David M.Pozar, Microwave Engineering, 2nd ed, John Wiley & SONS,INC., New York, 1998.

[2] Robert Hu , “Wide-Band Matched LNA Design Using Transistor’s Intrinsic Gate–Drain Capacitor”, IEEE TRANSACTIONS ON MICROWAVE THEORY

AND TECHNIQUES, VOL. 54, NO. 3, MARCH 2006.

[3] Studip Shekhar, Jeffrey S. Walling and David J. Allstot, “Bandwidth

Extension Techniques for CMOS Amplifiers ”, IEEE Solid-State Circuit , VOL. 4, NO. 11, NOVEMBER 2006.

[4]Zi-Hao Hsiung and Christina F. Jou, “ Novel Wideband CMOS LNA with Only an inductor as input matching network”, IEEE TENCON Conference, October 30 –

November 2,2007,Taipei,Taiwan.

[5] Yi-Jing Lin, Shawn S.H.Hsu, Jun-De Jin, and C.Y. Chan, “A 3.1-10.6GHz

Ultra-Wideband CMOS Low Noise Amplifier With Current-Reused Technique”, IEEE MICROWAVE AND WIRELESS COMPONENT LETTERS, VOL.17,

NO.3, MARCH 2007.

[6] Haolu Xie, Xin Wang, Albert Wang, Zhihua Wang, Chun Zhang, Bin Zhao, “A

Fully-Integrated Low-Power 3.1-10.6 GHz UWB LNA in 0.18um CMOS”, Radio and Wireless Symposium, 2007 IEEE.

32

[7] Shih-Chieh Shin, Chin-Shen Lin, Ming-Da Tsai, Kun-You Lin, Huei Wang, “A Low-Voltage and Variable-Gain Distributed Amplifier for 3.1-10.6 GHz UWB

Systems”, IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, VOL. 16,NO.4,APRIL 2006.

33