採用高層次操作模式及閘氧化層的高性能及可靠性 SONOS 快

閃記憶體之研究(1/3)

計畫類別: 個別型計畫 計畫編號: NSC93-2215-E-009-031- 執行期間: 93 年 08 月 01 日至 94 年 10 月 31 日 執行單位: 國立交通大學電子工程學系及電子研究所 計畫主持人: 莊紹勳 計畫參與人員: 蔣步堯 林佑聰 陳靖泓 報告類型: 精簡報告 處理方式: 本計畫可公開查詢中 華 民 國 95 年 3 月 14 日

採用高層次操作模式及閘氧化層的高性能及可靠性

SONOS 快閃記憶體之研究(1/3)

Operating Schemes and Advanced ONO Gate Stacks for Designing High Performance and Reliable SONOS Flash Memory

計畫編號:NSC93-2215-E009-031

執行期限:93 年 08 月 01 日至 94 年 07 月 31 日

主持人:莊紹勳 國立交通大學電子工程學系

一、中文摘要 SONOS 結構快閃式記憶體的研究,在國 內研究相當缺乏,本計劃著眼於此,規劃三 年時程的研究計劃,建立一套完整的 SONOS Flash cell 架構。利用開發高品質 ONO 介電 層、成長高可靠性低漏電流穿隧氧化層技 術、探討新穎操作方式(即 program and erase) 之低電壓、低功率記憶體元件,建立相關製 程模組,並探討其可靠性的分析方法。 首先,根據製程、元件模擬,對現有 SONOS 結構快閃式記憶體做最佳化設計,製 作元件一批。利用製作不同 ONO 厚度,本文 首先探討各漏電流機制及路徑,最後建立 ONO layer 微縮準則。SONOS 元件的兩個主 要可靠性指標-耐久性以及資料保存力可以 藉由不同上下氧化層厚度樣品加以分析。 本文提出一個新式的漏電流分離技術被 建立以區分三種由直接穿隧、熱發射、多次 寫入/抹除循環後的 trap-to-trap 穿隧造成的漏 電流成分。經由實驗,我們可以分離出三種 漏電成分,直接穿隧、熱發射、trap-to-trap 穿隧。接著評估元件的耐久性(Endurance)及 資料保存(data retention)特性,以此為指標, 建立 ONO 上下氧化層厚度的設計區間,這些 結果對於 SONOS 元件繼續微縮,主要漏電 物理機制的了解將會有很大幫助。 關鍵詞:非揮發性記憶體、快閃記憶體、氮化 閘極快閃記憶體、資料保存、耐久性、寫入、 抹除。 AbstractCurrent studies on the SONOS are in the beginning for domestic industry. Based on this understanding, we

proposed a 3-year plan to achieve a goal for establishing a complete study of the SONOS cell technology. First, we start from designing new programming and erase schemes, which will be modified from our developed schemes for floating cells in previous year studies. Then, we will attempt to fabricate a high quality ONO layer of the SONOS cell for achieving high performance and highly reliable cells, supported by a study on the reliability characterization technique as well as establishing the most important leakage current models related to the cell reliabilities.

First, we designed the cells based on the process and device simulation tools and with cell optimizations. Based on the designed cells with various ONO layer thickness, first we investigate the leakage current paths and the related physical mechanism, which results in a scaling rule for the layer thickness. The two major cell characteristics, endurance and data retention, can be analyzed, based on various ONO split samples.

In this work, we proposed a new technique to separate the three leakage current components, i.e., direct-tunneling, thermionic, and trap-to-trap tunneling. Based on the measured endurance and data retention characteristics, we have been able to design a window for an optimum cell operation. These results are essential toward the understanding of the dominant leakages as well as the scaling of SONOS cell.

Keywords: Nonvolatile memory, Flash memory,

SONOS flash, Data retention, Endurance, Programming, Erase.

二、計劃緣由與目的

現今快閃式記憶體(flash memory)的兩大 主流技術為傳統的 floating gate 與 SONOS 二 種。快閃式記憶體,具有高密度、低功率、 長 時 間 資 料 保 存 能 力 、 高 效 能 及 可 抹 除 (erasable)特性,目前主要運用於電腦、週邊 產品、攜帶式系統、行動通訊及消費性電子

等方面,但近年來的應用明顯大幅成長。然 而在其生產技術及產品研發上,主要的專利 及技術仍來自國外,國內的發展卻遠遠落後 國外,這將是國內半導體業界的一個嚴重問 題。再者,就目前國內研發環境而言,熟悉 快閃式記憶體之人才匱乏,所以使得快閃式 記憶體的研發層次及技術更面臨挑戰。

傳統的 floating gate 與 SONOS 快閃式記 憶體,主要差別有幾項:(一)floating gate flash technology 在 90nm 可 能 碰 到 微 縮 (scaling) 的 瓶 頸 , 原 因 是 : n 穿 隧 氧 化 層 (tunnel oxide)的微縮(scaling)限制,主要受限 於 tunnel oxide 無法繼續 scaling,蓋因 SILC 漏電流及 disturb 問題;o 因為 coupling,需 要較高寫入(program)操作電壓(>12V),也 會造成元件的微擾(disturb)問題;p 耐久性 (endurance)及資料保存特性(data retention)在 scaling 以 後 , 將 繼 續 變 差 , 以 致 將 來 的

embedded technology 無法配合。(二)SONOS

cell 較容易 scaling 且適合 embedded 的應用; (三)SONOS cell density 可以較高;(四) 二者的 programming 及 erase scheme 有所差 異。(see Fig. 1)。

本 研 究 群 , 在 過 去 多 年 來 , 致 力 於 floating gate flash memory 的研究,包含結構 [1]、programming scheme[2-3]、flash 可靠性 分析[4-5] 都已完成具體成果。最近更完成只 要工作在正負 4V 以內,即可操作的 ETOX cell,且達到低功率、高速操作的功能[6]。最 近 的 一 篇 2003IEDM 論 文 [7] 則 是 有 關 SONOS data retention 的研究。累積過去的經 驗,運用在 SONOS cell 的研究上,可以多所 發揮。

SONOS 的研究,雖已經歷很長一段時 間[8],但仍有很多待研究的空間。在電性上, 它 和 floating gate flash 的 最 大 差 異 在 : (一)Floating gate 最常使用的寫入操作是 Hot

electron programming,抹除操作是 electron erase , 然 SONOS 因 為 是 以 nitride 做 為 storage,因此,programming 是屬於 localized programming , erase 則 是 利 用 hot hole injection 來完成。(二)floating gate 受限於 tunnel oxide 厚 度 , 操 作 電 壓 不 易 壓 低 ; SONOS 則 是 需 要 用 較 薄 tunnel oxide 及 nitride 上層的 ONO 來防止 charge loss。因 此:n原有 floating gate 上的 programming 或 erase scheme 並不能完全適用於 SONOS, oSONOS 的 ONO 氧化層很薄,屬於 direct tunneling,因此,設計上需考量 ONO 組成 中,nitride、blocking oxide、tunnel oxide 的 厚度最佳化,以達較佳的 performance 及 reliability。p正因為 SONOS 的 scalability, 它可以低電壓操作,但問題是如果 tunnel oxide 太 薄 , SILC(Stress Induced Leakage Current)將會導致 data retention(或 charge loss) 問題,因此,需有好的 ONO 製程。

本計劃著眼於此,研究發展一中程的 SONOS flash cell 技術,包含適當的操作模 式、可靠性的研究方法、以及利用成長高品 質 JVD Nitride 的 SONOS cell。

首先,建立 SONOS cell 的 ONO 厚度微 縮與特性之間的關係,藉由可靠性的分析, 探討 ONO 各層的漏電物理機制,最後建立成 長高品質 ONO tunnel oxide、nitride 等的方 法。另一分面,探討寫入(program)、抹除(erase) 方式,建立更有效率的寫入與抹除,進而達 到適合更低電壓操作之方法,建立一套高效 能、高可靠性、低功率之快閃式記憶體元件 操作模式。 三、結果與討論 本計劃第一年建立一套完整的 SONOS Flash cell 架構。首先完成 SONOS cell 一批, 分別有各種不同 ONO layer 厚度,再依此建 立漏電流的分析及 ONO 厚度與記憶體元件 可靠性的相關性探討。

A. 物理機制與單元特性

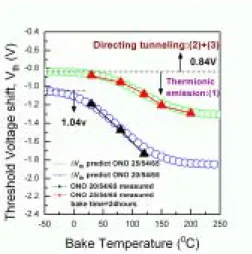

SONOS 元件結構及各項 ONO split 條件 如 Fig 1 所示,其中包含不同上氧化層以及 下氧化層厚度。在此實驗中我們使用 FN 寫 入與抹除,源極、汲極和基極都接地。 (1) 下氧化層的微縮效應 Fig 2 是不同下氧化層厚度的寫入/抹除 特性,我們可觀察到 no.4 只比 no.2 快一些 點,且再在高電壓只有些微差異。然而對於 不同下氧化層厚度卻有很大差別。這是因為 電洞是以直接穿隧穿過下氧化層而電子是經 由 FN 穿隧注入氮化矽層,因此抹除速度對 上氧化層厚度特別敏感。當電荷被注入氮化 矽中,下氧化層的電場減小造成臨界電壓改 變飽和。結果在大寫入電壓時,較薄下氧化 層的元件一開始的寫入速度較快,到最後就 一樣了。事實上,較薄下氧化層元件的資料 保存能力較差,如 Fig 3 所示。因此對於 SONOS 的下氧化層微縮,在資料保存力與寫 入/抹除速度之間必須要有折衷。在我們的實 驗中,抹除速度比寫入速度對下氧化層厚度 更敏感。因此對於元件最佳化,抹除速度與 資料保存特性決定了 SONOS 元件的下氧化 層厚度。 (2) 上氧化層的微縮效應 Fig. 4 顯示在相同下氧化層電場經過多 次寫入/抹除後,SONOS 元件的耐操特性。 直到 104循環時仍保持好的操作窗。103寫入 /抹除循環後,抹除臨界電壓升高使操作窗變 小。Fig. 5 是元件經過 105寫入/抹除循環後的 電荷幫浦法電流量測,其中電荷幫浦電流與 臨界電壓改變隨上氧化層厚度而增加,意味 著若非氧化層裡有負電荷就是在基極與氧化 層間有介面缺陷存在。我們也看到較厚的上 氧化層的耐操度較差,這原因可從 Fig. 6 獲 得解釋。 Fig. 6(a) 顯 示 在 低 電 場 和 高 電 場 時 的 IGVG圖有不同斜率。Fig. 6(b)是抹除時閘極電 流成分的能帶圖。在廣範圍的閘極電壓,我 們相信在高電場區域是電洞注入主宰。在此 區域在寫入/抹除循環後有較多的電子在較 厚的上氧化層中被抓住,加強抹除時的下氧 化層電場,因而增加電洞注入電流導致較差 的耐操度,也造成較厚的上氧化層元件有較 大的臨界電壓改變。 (3) 直接穿隧與熱激發電荷流失成份 Fig. 7 是 SONOS 元件漏電路徑的能帶 圖。在 stress 之前,電荷流失有兩個主要漏 電流成分,一個是 Frenkel-Poole mechanism[9] 後的熱發射,另一個是經由下氧化層及上氧 化層的直接穿隧。此兩成粉的分離可利用一 系列不同 ONO 厚度的樣品的特殊技術。Fig. 8 是直接穿隧以及熱發射。當溫度夠低時, 經由直接穿隧的漏電由 Fig. 8 中的(2)(3)表 示,另一個熱發射漏電則由(1)表示。假設這 些元件有相同由下氧化層直接穿隧漏掉的 量,則由上氧化層直接穿隧漏掉的量可以被 預測。在長期寫入/抹除循環後的元件有另一 個經由產生的缺陷的 trap-to-trap 穿隧的漏電 流,即 Fig. 7 中(4)的分量。 Fig. 9 是ΔQ 對氧化層厚度的圖以作為 考慮資料保存力的標準。若我們希望電荷流 失只有 1.3V,我們可以調整下氧化層和上氧 化層厚度已達到我們的要求。薄下氧化層有 較大的電荷流失。雖然薄下氧化層可提供較 快的寫入/抹除速度,他的資料保存力將成為 嚴重的問題。 (4) Trap-to-Trap 穿隧電荷流失成分 接著我們討論 103次寫入/抹除循環後的 元件資料保存力。Fig. 10 是 103次寫入/抹除

循環前後所量到的 IGIDL-VD曲線。IGIDL因為

103 次寫入/抹除循環後產生的氧化層電荷而 增加。所以我們確定在 103次寫入/抹除循環 後產生許多氧化層電荷。事實上,SONOS 元 件在 103次寫入/抹除循環後的資料保存能力 變差了,如 Fig. 11 所示。這是因為產生的氧 化層陷阱導致更多的 trap-to-trap 穿隧引起的 傷害。從這張圖中我們可以更進ㄧ步的分離 多次寫入/抹除循環後的 trap-to-trap 穿隧成

分。 在 Fig. 12 裡,我們知道多次寫入/抹除循 環將會產生額外的氧化層傷害。較厚的上氧 化層會捕捉較多的氧化層電荷而導致較差的 資料保存能力。越厚的上氧化層厚度,其資 料衰減率越差。雖然對 fresh 元件而言,厚的 上氧化層厚度提供較好的資料保存能力,但 經過 103次寫入/抹除循環後,元件劣化的更 嚴重。我們也可以看到 trap-to-trap 穿隧的效 應。所以我們在上氧化層和下氧化層厚度方 面考慮資料保存能力以達到更好的 SONOS 元件性能。 C. 結果與討論 SONOS 元件的兩個主要可靠性測試-耐 操性以及資料保存力可以藉由不同上下氧化 層厚度樣品加以分析。本文提出一個新式的 漏電流分離技術被建立以區分三種由直接穿 隧 、 熱 發 射 、 多 次 寫 入 / 抹 除 循 環 後 的 trap-to-trap 穿隧造成的漏電流成分。我們已 經可以分離出三種漏電成分,直接穿隧、熱 發射、trap-to-trap 穿隧。較薄的上氧化層在 多次寫入/抹除循環後有較少的傷害,然而在 不同的烘烤溫度下卻有較多的電荷流失。 這些結果對於 SONOS 元件繼續微縮,主 要漏電物理機制的了解將會有很大幫助。 四、計劃成果自評 本計劃第一年,發展出一套適合 SONOS cell 新式的漏電流分離技術,區分三種由直 接穿隧、熱發射、多次寫入/抹除循環後的 trap-to-trap 穿隧造成的漏電流成分。用以提 供未來 SONOS 元件不同 ONO 厚度在元件 可靠性設計上的考量。 研究的成果已發表一篇 IEDM[7]及一篇 IPFA 論文[10]。第二、三年的計劃將就元件 ONO layer 的改善、scaling 的研究、嘗試低 電壓寫入抹除方式的研究及研究高品質 JVD Nitride 成長的 SONOS cell。預期在工業界, 可應用於新世代 SONOS 元件之可靠性設計 分析上,有實質的經濟效益。所以,本計劃 的完成,將對學術研究水準的提昇及工業界 的實際應用上都有莫大的助益。

五、參考文獻

[1] S. S. Chung et al., in Technical Digest of Symposium on VLSI

Technology, pp. 11-12, 1999.

[2] S. S. Chung, S. N. Kuo, C. M. Yih, and T.S. Chao, in Tech.

Digest of International Electron Devices Meeting (IEDM), pp. 295-298, Washington D.C., December 7-10, 1997.

[3] S. S. Chung et al., Proc. of International Reliability Physics Symposium (IRPS), pp. 67-72, 2001.

[4] S. S. Chung et al., in Tech. Digest Symposium on VLSI

Technology, pp. 111-112, 1997.

[5] S. S. Chung et al., IEEE Transaction on Electron Devices, vol.

ED-46, pp. 1883-1889, 1999.

[6] S. S. Chung et al., in SSDM, pp. 612-613, 2002.

[7] S. S. Chung et al., in IEDM Tech. Digest, pp. 617-620, 2003.

[8] M. H. White et al., IEEE Circuits and Devices Magzine, pp. 22-31, 2000.

[9] S. Sze, Physics of Semiconductor Devices, John Wiley, 1981 [11] Y. T. Lin et al., Proceedings of IEEE IPFA, pp. 239-242 July 5-8,

2004. .

Fig. 1 (a) The experimental SONOS device structure

with trap rich nitride. (b) The split conditions of samples with different blocking oxide and tunnel oxide thicknesses.

Fig. 2 (a) The program transients of sample 2 and

sample 5 with different tunnel oxide thickness. (b) The erase transients of sample 2 and sample 5.

Fig. 3 The calculated charge loss versus bake time

for different tunnel oxides. Thin tunnel oxide cell shows much larger charge loss as expected.

Fig. 4 The endurance of cells, samples 4, 5, and 6,

with different blocking oxide thicknesses, in which thin blocking oxide shows better endurance characteristics.

Fig. 5 Measured charge pumping current after 105

PE cycles for samples 4, 5, and 6.

Fig. 6 (a) IG-VG curve at negative gate biases. The

curve has different slopes at low and high electrical field regions respectively. (b) The schematic band diagram showing the gate current component during erase.

Fig. 7 The charge loss path and the various leakage current components in a SONOS cell,

(1): thermionic emission (2)+(3) : direct tunneling. (4): trap-to-trap tunneling 65A 46A 34A 65A 46A 34A Tblock oxide 54A Tnitride 20A 25A Ttunnel oxide 6 5 4 3 2 1 Wafer no. ONO 1.4um / 0.6um W/L 65A 46A 34A 65A 46A 34A Tblock oxide 54A Tnitride 20A 25A Ttunnel oxide 6 5 4 3 2 1 65A 46A 34A 65A 46A 34A Tblock oxide 54A Tnitride 20A 25A Ttunnel oxide 6 5 4 3 2 1 Wafer no. ONO 1.4um / 0.6um W/L (b) Blocking Oxide Nitride Tunnel Oxide 54Å 34Å~65Å 20Å~25Å N+ N+ P-Sub (a) (b) (a) Tunnel oxide=20A Tunnel oxide=25A 100 101 102 103 104 0 1 2 3 4 5 Threshold Voltage, Vth (V) P/E cycles ONO 20/54/65 ONO 20/54/46 ONO 20/54/34 Gate Electron trap to band

tunneling

Hole injection

(1)

(2)

Substrate

With different block oxide thickness (a) (b) Domintated by hole injection Domintated by electron injection Gate Electron trap to band

tunneling

Hole injection

(1)

(2)

Substrate

With different block oxide thickness

Gate Electron trap to band

tunneling

Hole injection

(1)

(2)

Substrate

With different block oxide thickness (a) (b) Domintated by hole injection Domintated by electron injection

Fig. 8 The measured (triangle) and predicted (circles) ΔVth versus temperature plot. Note that the two major

leakage components can be differentiated.

Fig. 9 The relationship between ΔQ and the oxide

thickness. It can be used as a criterion of the data retention to find a combination of tunnel and blocking oxide thicknesses.

Fig. 10 The measured GIDL currents in sample 4

for fresh and after 103 P/E cycles devices. The

increase of GIDL current is due to the generated oxide damage.

Fig. 11 The calculated charge loss for sample no.5

fresh and 103 P/E at an elevated temperature 80oC.

Note that the trap-to-trap tunneling component can be differentiated

Fig. 12 The calculated decay rate versus block

oxide thickness in the first 3 hours for sample no. 5

and no. 6 measured at fresh and 103 P/E cycles at an

elevated temperature 80oC. Charge Loss= 1.3V Qox 2.0 2.2 2.4 2.6 4x10-13 6x10-13 8x10-13 10-12 1.2x10-12 1.4x10-12 GIDL Cu rren t, I GI D L (A) Drain Voltage, V D (V) Fresh PE10K 0 5 10 15 20 25 30 0 1 2 3 4 5 6 Cha rge Loss , ∆ Q (fC/ u m 2)

Bake Time (hour)

PE10K Fresh ONO 20/54/46 Baked@80o C (4) (1)+(2)+(3) (4) trap-to-trap tunneling 3 0 3 5 4 0 4 5 5 0 5 5 6 0 6 5 7 0 4 .5 5 .0 5 .5 6 .0 6 .5 7 .0 7 .5 T h resh o ld Vol tag e Decay R a te, ( ∆ mV/min)

B lock O xide Thickness (Å)

Fresh P E 10K tunnel oxide=20Å