行政院國家科學委員會專題研究計畫 成果報告

利用基於積分方程式之快速電磁解答器實現晶片導線之頻

域及時域分析

計畫類別: 個別型計畫 計畫編號: NSC94-2213-E-009-068- 執行期間: 94 年 08 月 01 日至 95 年 07 月 31 日 執行單位: 國立交通大學電信工程學系(所) 計畫主持人: 趙學永 共同主持人: 陳念偉 計畫參與人員: 郭益廷 王義志 方國誌 莊肇堂 報告類型: 精簡報告 報告附件: 出席國際會議研究心得報告及發表論文 處理方式: 本計畫可公開查詢中 華 民 國 95 年 10 月 31 日

行政院國家科學委員會專題研究計畫成果報告

利用基於積分方程式之快速電磁解答器實現晶片導線之頻域及時域

分析

計畫編號: NSC 94-2213-E-009-068-

執行期限: 94 年 8 月 1 日至 95 年 7 月 31 日

主持人:

趙學永 國立交通大學電信工程系所

共同主持人:陳念偉 國立中央大學電機工程系所

計畫參與人員: 郭益廷、王義志 國立交通大學電信工程系所

方國誌、莊肇堂 國立中央大學電機工程系所

中文摘要 當積體電路設計進入深次微米及數十 億赫玆的時代,導線分析逐漸顯現其 重要性。由於半導體元件體積縮小, 導線寄生元件所造成的時間延遲遠大 於邏輯閘所造成的延遲。此外,當高速 數位訊號包含更多的高頻成份時,訊 號在導線上傳輸時將會遇到更多的振 鈴、反射、及串音等效應。為了正確 分析晶片上導線的時域及頻域特性, 本計畫發展了基於電場積分方程式的 多層介質解答器之數種關鍵技術。其中 包含低頻電磁裡多層介質格林函數之 電磁分解、萃取複雜結構圈與樹基底 函數之快速演算法及寬頻等效電路生 成之最佳演算法。 關鍵詞:導線分析、電場積分方程式、 圈與樹基底函數分解、寬頻等效電路 生成 AbstractInterconnect analysis becomes increasingly important as IC design enters the deep-submicron and

multi-gigahertz era. As device sizes shrink, the time delay due to interconnect parasitics far exceeds the gate delay. Besides, high-speed digital signals encounter more ringing, reflection, and crosstalk as their spectrums consist of more high-frequency components. In order to accurately capture frequency- and time-domain characteristics of on-chip interconnects, we have developed several key technologies for multilayered electromagnetics solvers based on the electric field integral equation, including decomposition of multilayered Green’s functions at low frequencies, fast algorithms of loop-tree extraction for complex structures, and optimal algorithms for broadband equivalent circuit generation.

Keywords: Interconnect analysis,

integral equation, loop-tree decomposition, broadband equivalent circuit generation

I. Introduction

interconnect analysis are under avid research in recent years. On-shelf commercial tools based on the finite element method (FEM), such as Ansoft HFSS and Q3D, are too computationally expensive for calculating S-parameters or equivalent circuits in whole-chip simulation. Since IE-based methods only involves surface unknowns, the number of unknowns is far less than that of FEM. Therefore, the former is more promising for solving large-scale problems than the latter. However, the superior computational efficiency of the IE-based method is not without cost. The multilayered Green’s function involves singular integral in spectral domain and is much harder to be formulated and implemented than the FEM. Besides, the multilayered Green’s function becomes unstable when the dimension of the structure is less than one wavelength. The only remedy is to decompose the electric current by loop and tree functions at low frequencies, so the magnetostatic and electrostatic contributions to the field can be captured accurately. Furthermore, the results obtained from frequency-domain EM simulation, such as S-parameters, cannot be readily used in timing analysis of interconnects. Therefore, it is necessary to convert system transfer functions into broadband equivalent circuits, so the net lists can be incorporated seamlessly into SPICE-like circuit simulators.

In this report, we will introduce key accomplishments of the one-year project, including the decomposition of multilayered Green’s function at low frequencies, fast algorithms for loop and tree extraction, and an optimal algorithm for broadband equivalent circuit extraction.

II. Decomposition of the Multilayered Green’s Function at Low Frequencies

For interconnects embedded in

dissimilar dielectric layers, the most efficient way to analyze signal propagation is to apply IE-based methods, such as the method of moments (MoM) with dyadic Green’s functions for multilayered media [1]. If we apply the surface integral formulation, currents are assumed to flow on the surface of conductors. Since only surface unknowns are involved, it generally requires less computational resources than volume-unknown based methodsm, such as FEM and finite-difference time-domain (FDTD) method.

The dyadic Green’s function can be decomposed into TM and TE contributions [2]. We further separate

the divergence-free and non-divergence-free contributions from

the TM and TE components to make the integral equation stable at low frequencies.

If both source and observation points are located in the same layer of dielectric materials, the dyadic Green’s function has the form

(

)

(

)

(

)

(

)

(

)

2 , 2 , 2 2 , 2 , , , , , , RWG p m m TM R z m m TM R s s s mh m s TE R s s s m s g k g k g k k g k ⎛ ∇∇⎞ ′ =⎜ + ⎟ ′ ⎝ ⎠ ⎛∇∇ ⎞ ′ +⎜ + ⎟ ⎝ ⎠ ⎛∇∇ ∇ ∇ ⎞ ′ +⎜ − ⎟ ⎝ ⎠ ⎛ ∇ ∇ ⎞ ′ +⎜ + ⎟ ⎝ ⎠ G r r I r r zz r r r r I r r where RWGG represents the interaction between points on RWG basis functions. If the source and field points are in different layers, the dyadic Green’s function assumes a different form

(

)

(

)

(

)

(

)

(

)

2 2 2 2 2 2 1 , , 1 , , , RWG TM z n n m TM n s s s nh m m TE s s s n s k g k k g k k g k ′ = ∇∇ + ′ ⎛ ⎞ ′ − ⎜ ∇ ∇ − ∇∇ ⎟ ⎝ ⎠ ⎛ ∇ ∇ ⎞ ′ +⎜ + ⎟ ⎝ ⎠ G r r zz r r r r I r rwhere the above equation is equivalent to the previous one when the layer indices m and n are the same.

Using the divergence-free property of the loop basis, the dyadic Green’s function can be reduced when either basis or testing function is a loop basis. The above equations become

(

,)

(

,)

(

,)

L TM TE m s m g g ′ = ′ + ′ G r r zz r r I r r and(

,)

22(

,)

(

,)

, L n TM TE n s n m k g g k ′ = ′ + ′ G r r zz r r I r rrespectively. Since the dyadic Green’s function can be reduced for a loop basis, it takes less time to compute the impedance matrix elements associated with loop bases.

III. Fast Loop-Tree Extraction in Low-Frequency Electromagnetics

Traditional loop-tree extraction algorithms generate loop and tree basis functions separately. Since trees can be generated easily by graph traversing algorithms, we exploit the information embedded in the tree to generate loops, i.e. closing the acyclic paths by chords. Since the procedure is totally independent of the geometry of the structure, it is also called a topological loop-tree extraction.

However, the fundamental loops are quite long and their total length far

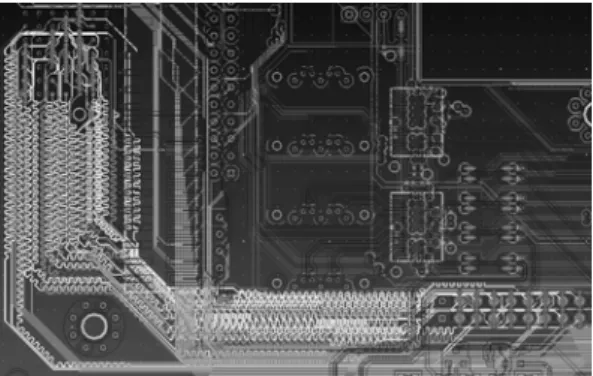

exceeds that of the minimal loop basis. We use the fact that local loops are located in between comb-like branches of breadth-first-search trees and further reduced the fundamental loops by shortcuts [3]. By applying the algorithm, loops on a donut-shaped ground plane (Fig. 1) can be extracted in linear time as the electric size of the plane increases (Fig. 2).

Fig. 1. The surface mesh of a donut structure with many holes and the corresponding graph (top) and the spanning tree (bottom) [3].

104 106 100

101 102 103

Number of loop bases

T im e fo r l o o p e x tr a c ti o n ( s e c ) BFS DDS UE MXL 104 106 100 101 102 103

Number of loop bases

T im e fo r l o o p e x tr a c ti o n ( s e c ) BFS-reduced DDS-reduced UE-reduced MXL-reduced

Fig. 2. The CPU time for extracting loop bases from BFS, DDS, UE, and MXL trees with (right) and without (left) loop reduction [3].

We further develop an efficient loop reduction algorithm is to reduce global loops [4], so the overall loop sizes is close to minimal. Comparing with the greedy method [5], our algorithm is

more efficient for extracting loops on structures with large surfaces and a few interconnects. Hence, it is especially advantageous for the analysis of interconnects in between large reference planes.

IV. Broadband Equivalent Circuit Generation for Large-Scale Interconnect Analysis

For the broadband equivalent circuit generation, we find that the vector fitting method (VFM) [6] is superior to the complex frequency hopping (CFH) method [7]. The main reason is that VFM can predict poles outside of the range of sampling frequencies, where CFH can not. More detailed comparison of the two methods can be found in Wang’s thesis [8], where broadband macromodels (i.e. equivalent circuits) are generated for simple antenna systems. For dipole antennas with clear resonant/anti-resonant peaks, there must be one pole associated with each peak. Only VFM can extract the correct poles

associated with the resonant/anti-resonant peaks.

We further modify VFM for macromodel generation of a 32-port PCI Express bus on a PCB. With

Fig. 3. Schematic capture of the PCI Express bus on a PCB.

proprietary technologies, the number of circuit elements generation by our in-house code is 32% less than the

traditional VFM (291,230 vs. 427,584). The reduction in circuit simulation time is even more obvious (1,890 vs. 10,593 sec). As the number of ports increases, our algorithm exploits the distinctive characteristic of individual transfer function. Therefore, the number of poles for the state-space realization is significantly reduced. A statistic model has also been developed for predicting the percentage reduction of circuit elements prior to equivalent model generation. Detailed results will be shown in [9].

Fig. 4. Frequency responses of the original full-wave simulation, fittings by VFM and our modified algorithm.

V. Conclusions

We have developed three key technologies for interconnect analysis at low frequencies. Using the topologically based algorithm for loop-tree extraction, there is no need to discern the types of basis functions. The loop reduction process guarantees the independence of loops. Therefore, there is no need to perform independence check repetitively as in the greedy method. Besides, the decomposition of multilayered Green’s function at low frequencies enables us to see divergence-free (loop) and non-divergence-free (tree) current components even before the surface current is discretized. It also make the computation of MoM impedance matix

efficient and stable. In addition, our algorithm for macromodel generation significantly saves circuit simulation time because it can represent a single frequency response with less number of circuit components, as compared with the original VFM.

VI. Self-Evaluation

Under the sponsorship from NSC, we have developed two programs: one for fast loop-tree extraction and another for broadband equivalent circuit generation. Results related to the project have been presented at the 2006 IEEE AP-S Symposium [3] and have received widespread interests from the audience. More results are in preparation for submission to the Journal of Experimental Algorithms [4] and the IEEE Transactions on Circuits and Systems [9].

References

[1] W. C. Chew, Waves and Fields in

Inhomogeneous Media, IEEE Press,

New York, 1995.

[2] W. C. Chew, J. S. Zhao, and T. J. Cui, “The layered medium Green’s function – a new look,” Microwave and Optical Technology Letters, vol. 31, no. 4, pp. 252-255, 2001.

[3] H. Y. Chao and W. C. Chew, “Linear-time algorithm for extracting tree and loop bases in computational electromagnetics,” Proc. of the 2006

IEEE AP-S Symposium, July 2006.

[4] H. Y. Chao and W. C. Chew, “Efficient loop extraction and reduction algorithms for low-frequency electromagnetics,” in preparation for submission to Journal of Experimental

Algorithms.

[5] L. Bai, “An efficient algorithm for

finding the minimal loop basis of a graph and its application in computational electromagnetics,” Master thesis, University of Illinois, Urbana, IL, 1997.

[6] B. Gustavsen and A. Semlyen,“Rational approximation of frequency domain response by vector fitting,” IEEE Trans. PWRD, vol. 14, no. 3, pp. 1052-1061, July 1999.

[7] E. Chiprout and M. S. Nakhla, “Analysis of interconnect networks using complex frequency hopping (CFH),”IEEE Trans. Computer Aided Design, vol. 14, no. 2, pp. 186-199, Feb. 1995.

[8] Y. C. Wang, “Equivalent circuit generation for antenna systems,” Master thesis, Department of Communication Engineering, NCTU, July 2006.

[9] Y. T. Kuo and H. Y. Chao, “Broadband macromodel generation for large-scale interconnect analysis,” in preparation for submission to IEEE

![Fig. 1. The surface mesh of a donut structure with many holes and the corresponding graph (top) and the spanning tree (bottom) [3]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8242270.171375/4.892.470.743.698.908/fig-surface-donut-structure-holes-corresponding-graph-spanning.webp)