國 立 交 通 大 學

顯 示 科 技 研 究 所

碩士論文

奈米矽晶於光子晶體發光元件之應用

Applications of Nanocrystalline Silicon on

Photonic Crystal Light Sources

研

研

究

究

生

生

:

:

林

林

義

義

淵

淵

..指

指

導

導

教

教

授

授

:

:

余

余

沛

沛

慈

慈

教

教

授

授

中

中

華

華

民

民

國

國

九

九

十

十

七

七

年

年

三

三

月

月

奈米矽晶於光子晶體發光元件之應用

Applications of Nanocrystalline Silicon on Photonic Crystal

Light Sources

研究生:林義淵 Student: Yi-Yuan Lin 指導教授:余沛慈 教授 Advisor: Prof. Pei-Chen Yu

國 立 交 通 大 學 顯示科技研究所

碩 士 論 文

A Thesis

Submitted to Display Institute

College of Electrical Engineering and Computer Science National Chiao Tung University

in Partial Fulfillment of the Requirements for the Degree of

Master In Display March 2007

Hsinchu, Taiwan, Republic of China

奈米矽晶於光子晶體發光元件之應用 研究生:林義淵 指導教授:余沛慈 教授 交通大學顯示科技研究所 摘要 矽基光源整合在光通訊以及光電系統中是非常吸引人的應用,主要是因為它 能利用現有廉價成熟的 CMOS 製程來實現,在矽基板上整合 CMOS 電路與光電主被 動元件成為光電系統晶片已是未來的潮流。但受限於矽本身為間接能隙的材料, 作為發光光源並沒有效率,然而發展光波導與光偵測器元件仍可獲得極佳的效 率。為發展矽基半導體光源,我們以兩方面來著手,一材料本質利用鍺奈米微晶 材料作為發光主動層,因為其具有可調的激發頻譜以及高於矽塊材的內部量子效 率;外部結構上,因為光子晶體具有優異控制光的能力,可以利用來提昇外部出 光效率。而且,因為光子晶體,元件的維度得以大量縮小以整合在晶片上。光子 晶體用來增加外部出光效率的方式有二,一為利用光子晶體能隙; 二為利用光子 晶體光錐上不受侷限的出光膜態,在此我們利用的是第二種方式,光因為相位連 續會耦合到不受侷限的出光膜態。在此我們也利用第二種方式,以在元件上方量 測的室溫微光致激發螢光以探討其垂直方向出光增益。 我們主題分為兩部分,在第一部份我們利用文獻的資料以驗證模擬,其利用 光子晶體增加外部出光強度的方式為能帶邊緣近Γ點低群速的膜態。我們利用光 子晶體出光態密度的觀念模擬預測出光頻譜,模擬的出光頻譜與文獻上的量測頻 譜有非常高的相似度,除了特定頻譜區域深谷差異,我們利用此差異將在後續對 模擬有詳細探討。在第二部份我們以實驗加以佐證,我們選用內嵌鍺奈米微晶的 奈米孔洞二氧化矽當作塊材,製作直角方形孔洞二維光子晶體於上以嘗試製作矽 基光源,使峰值出光強度增加了一點五到三倍。我們利用之前模擬出光態密度的 方式以實驗量測頻譜驗證,結果預測頻譜與量測頻譜相似度非常高。

Applications of Nanocrystalline Silicon on Photonic Crystal Light Sources

Student: Yi-Yuan Lin Advisors: Prof. Pei-chen Yu

Institute of Display, National Chiao Tung University Abstract

Silicon-based light sources are attractive components in optical communication and optoelectronic systems, since one can take advantage on widely-available CMOS technology; however bulk silicon fails for light source applications in optoelectronics due to an indirect band gap of 1.1 eV. Here, we employ two approaches to overcome the drawbacks. Internally, germanium (Ge) nanocrystals were employed in the matrix for optical applications because of tunable spontaneous emission and better internal quantum efficiency compared to bulk Silicon. Externally, due to good capability to modify light extraction, photonic crystals were employed to enhance light extraction efficiency. Moreover with photonic crystals, dimension of devices can be scaled down much to integrate electronic devices on a chip. Enhancement of light extraction from photonic crystals can be distinguished into two ways. One is carried out by the vertical modes of photonic band gap. The other is performed by Bloch modes above light cone. In the work, we investigate the Bloch modes above light cone. The emitted light couples to radiation modes in accordance with phase match. We investigate the spectra of vertical radiation on samples by micro-photoluminescence experiments measured normal to the surface at room temperature.

We separate the subject into two parts. In the first part, we make use of data from paper for simulation. The way to enhance external light extraction efficiency is by low group velocity flat band modes near Γ point. We employ the concept about photonic density of states (DOS) to simulate light extraction spectrum. The simulated spectrum

resembles the measured one on paper well besides a dip. By the difference between them, detail discussion about DOS simulation was as follow in context.

In the second part, We investigate light extraction characteristics from two-dimensional photonic crystals with a square lattice of air box. The photonic crystals are fabricated on mesoporous silica film with embedded Ge quantum dots for potential applications in Silicon-based light sources. The peak emission from photonic crystals exhibit 1.5- to 3-fold enhancement. Moreover, the spectral features are well explained by the calculations of photonic density of states near the in-plane

誌 謝 感謝!!!數十個月的碩士生活,終要隨著這本論文劃下句點,心情 很複雜。一路上許多的人伸出援手,就像心的碼頭,讓我累了可以不 再漂流;感謝的人好多,第一個是余老師,我知道我被混血了,但我 更要戰戰兢兢,如同被視為黑掉一般,那時老師適時伸出援手,還記 得老師不帶一絲猶豫,好酷!接著謝謝實驗室的人,講半句話就可以 讓我笑的昌哥,真強者我學長的晉哥,羽球魔人的安哥,與我奮戰的 同袍以及實驗室真一哥的華爺,完美鄉民與腦域隨時縮小的桌球高手 阿生哥,熱愛足球的綱哥,有你們實驗室才有歡樂的氣氛。當然還有 故人們,戰友宅男老楊,深愛老楊的球友老劉,還有 CP 朱,你這神 奇的傢伙。還要感謝郭浩中老師,謝嘉民老師,小賴學長實驗上的指 導與幫忙。最重要的得感謝家人無私的付出與關懷,讓我盡力完成學 業。或許要離開新竹了,總覺得風城的風特別怡人,雖然新竹飆仔深 夜依然精力充沛,郊區房租還是好貴,交大餐廳談不上美味,但我卻 似乎還是有點不捨,是的,是因為大家!不過,我將帶走的是數十個 月的滿滿回憶,感謝!!!

目 錄 摘要 (中文)……….…………...i 摘要 (英文)………..…………..………..ii 誌謝………...………iv 目錄…………...………...……….……...…..v 圖目錄………...vii 表目錄………...x 第一章 緒論...1 1-1 奈米矽晶之光子晶體發光元件簡介...1 1-2 動機...4 第二章 實驗原理及樣品介紹...6 2-1 實驗原理...6 2-1-1 電漿原理...6 2-1-2 沈積薄膜的成長模式...9 2-1-3 薄膜成核沈積理論...10 2-2 樣品介紹:矽(鍺)奈米微晶於奈米孔洞二氧化矽薄膜...12 2-3 樣品介紹:矽奈米微晶於氮化矽薄膜...18 2-3-1 文獻回顧...20 2-3-2 實驗結果...29 2-4 HDPCVD系統...40 2-4-1 HDPCVD系統簡介...40 2-4-2 HDPCVD參數...43 第三章 光子晶體與製程相關分析方法...53 3-1 光子晶體...53 3-1-1 光子晶體簡介...53

3-1-2 光子晶體理論基礎(波動方程式)...57 3-2 元件設計...60 3-3 光子晶體製程與分析方法...64 3-3-1 光子晶體製程...64 3-3-2 光激發螢光發光(Photoluminescence)&微光激發螢光發光 (Micro- Photoluminescence) ...65

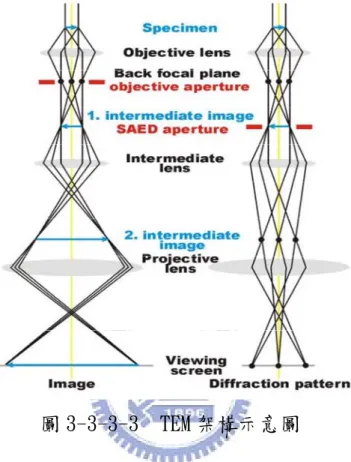

3-3-3 掃描電子顯微鏡(scanning electron microscope(SEM)) ...70

第四章 分析與實驗結果討論...78

4-1 文獻模擬分析...78

4-2 實驗模擬分析...88

圖 目 錄 圖 1-1 矽光電晶片示意圖...1 圖 1-2 近年二維光子晶體 Q 值成長統計圖………3 圖 1-3 文獻上利用光子晶體增強 PL 強度的量測結果………….……….…………4 圖 2-1-1-1 電漿化學氣相沈積系統結構示意圖………...…………9 圖 2-1-2-1 三種薄膜成長模型示意圖……….………10 圖 2-1-3-1 化學氣相沈積薄膜過程示意圖……….………12 圖 2-2-1 不同結構之奈米規則孔洞二氧化矽 SEM 圖………..………15 圖 2-2-2 Silylation reaction 保護薄膜防止水氣入侵鍵結圖………….………15 圖 2-2-3 矽奈米微晶於奈米孔洞二氧化矽薄膜 TEM 圖………..……17 圖 2-2-4 矽奈米微晶嵌入之奈米孔洞二氧化矽薄膜流程圖...…………..………18 圖 2-3-1 氮化矽薄膜相關發光缺陷能階圖…………...………..………24 圖 2-3-2 氮化矽晶相結構圖………...………..………25 圖2-3-3 表2-3-2變溫參數室溫PL量測圖………...……….30 圖2-3-4 表2-3-3變溫參數室溫PL量測圖………...……….31 圖2-3-5 圖2-3-3 300℃室溫PL圖………...………..31 圖2-3-6 文獻上量測氮化矽薄膜室溫PL圖……..…………...……….32 圖2-3-7 文獻上氮化矽缺陷能階圖………..………...……….32 圖2-3-8 表2-3-4變厚度參數室溫PL圖………...…..………...33 圖2-3-9 量子點於薄膜內造成多重干擾示意圖…………..……...………...34 圖2-3-10 表2-3-5變基板直流偏壓功率室溫PL圖……..…………...………..…...34 圖2-3-11 表2-3-7室溫PL量測圖………..…...……….37 圖2-3-12 氮化矽相關缺陷簡圖………..……...………...37 圖2-3-13 表2-3-8室溫PL量測圖………...………..………...38 圖2-3-14 表2-3-8退火後室溫PL量測圖…………..…...…..………...38

圖2-3-15 氮化矽相關缺陷簡圖………..……...………...39 圖 2-4-1 高密度化學氣相沈積系統結構示意圖………...…..………40 圖2-4-2 黏滯力關於邊界層在反應室壁間的過渡區示意圖…………...…..…….45 圖2-4-3 氣相沈積反應速率對溫度典型關係圖………...…..…….45 圖3-1-1-1 一,二,三維光子晶體結構示意圖………...…..…….54 圖3-1-1-2 文獻中布拉格反射鏡側面SEM圖………..………...…..…….54 圖3-1-1-3 文獻中布拉格反射鏡的反射率圖…..…..………...…..…….55 圖3-1-1-4 文獻中光子晶體光波導SEM圖…………..………...…..…….55 圖3-1-1-5 文獻中光子晶體光纖SEM剖面圖…………..………...…..…….56 圖3-1-1-6 文獻中微腔半導體雷射共振腔示意圖…………..………...…..…….57 圖3-2-1 文獻中利用二維光子晶體增強PL強度的量測結果………...…..……….60 圖3-2-2 文獻中利用能帶圖與出光頻譜對照圖………...………..……….61 圖3-2-3 光子晶體三維波向量空間示意圖………...………..……….62 圖3-3-2-1 光激發螢光發光架構示意圖………...………..…….67 圖3-3-2-2 微光激發螢光系統架構示意圖………...………..…….67 圖3-3-2-3 輻射復合可能路徑之能帶圖………...………..…….68 圖3-3-3-1 電子束入射介質之後的各種行為圖………...………..…….71 圖3-3-3-2 電子顯微鏡系統示意圖………...………..…….71 圖3-3-3-3 TEM架構示意圖………...………...………..…….74 圖4-1-1 文獻上量測的出光PL圖與SEM側面圖………...………..…….79 圖4-1-2 模擬的矽直角方形柱能帶圖…………..……...………..…….79 圖4-1-3 能帶圖與出光頻譜峰值對照圖………...……….80 圖4-1-4 ΓM方向模擬的出光態密度圖………...………..……….81 圖4-1-5 ΓM方向模擬的出光頻譜圖………...………..……….82 圖4-1-6 各方向模擬的出光態密度圖………...………....……….82 圖4-1-7 各方向模擬的出光頻譜圖………...………....……….83 圖4-1-8 標準差1整個倒晶格空間模擬的出光態密度圖………...……….84 圖4-1-9 標準差1整個倒晶格空間模擬的出光頻譜圖……….………..…….84

圖4-1-10 標準差5整個倒晶格空間模擬的出光態密度圖………...……..…….85 圖4-1-11 標準差5整個倒晶格空間模擬的出光頻譜圖……….………..…..…….85 圖4-1-12 近Γ點倒晶格空間模擬的出光態密度圖………...……..…….86 圖4-1-13 近Γ點倒晶格空間模擬的出光頻譜圖………...………....…….87 圖4-1-14 量測光於晶體中傳播之距離分佈圖………...………....…….88 圖4-2-1 三種光子晶體掃瞄式電子顯微鏡圖與結構示意圖………...…....…….89 圖4-2-2 製程實驗流程圖………...…....…….90 圖4-2-3 ΓM方向能帶圖與近Γ點出光態密度圖………..…...…....…….91 圖4-2-4 量測的微光激發螢光頻譜圖………..…...…....…….92 圖4-2-5 倒晶格空間近Γ點的模擬出頻譜圖………..……..…...…....…….92

表 目 錄 表 2-2-1 成長奈米孔洞二氧化矽薄膜之準備溶膠凝膠流程圖……...…..………16 表 2-3-1 氮化矽等相關晶格參數表……...………..………26 表2-3-2 變溫實驗參數…...………..………..30 表2-3-3 另一變溫實驗參數…...………..………..30 表2-3-4 變薄膜成長時間參數…...………..……….33 表2-3-5 變基板直流偏壓功率實驗參數…...………..……….35 表2-3-6 變感應式耦合電漿功率實驗參數…...…..……….35 表2-3-7 變矽烷流量實驗參數…...…..……….36 表2-3-8 變矽烷流量實驗參數…...……….37 表 4-2-1 三種光子晶體規格表……...………..………90

第一章 緒論 1-1 奈米矽晶之光子晶體發光元件簡介 現今科技發展中,光電科技應用涵蓋各重要範疇,如光纖通訊、 光顯示、光資訊儲存、高效率照明及生物醫學等方面的應用。隨著科 技的進步,在矽基板上整合CMOS電路與光電主被動元件成為光電系統 晶片已是未來的潮流,如圖1-1所示,此類的晶片可應用在通訊、生 醫偵測、環境監控等領域。現行的光電系統晶片約略可分成三部分: 光源、光波導及光偵測元件。因為矽本身為間接能隙的材料,作為發 光光源並沒有效率,然而發展光波導與光偵測器元件仍可獲得極佳的 效率。文獻上也可見許多報導,因此大部分的半導體光源多是採用如 砷化鎵(GaAs)等III-V族化合物作為材料。 圖1-1 當雷射發射與接收電路都與CPU等矽晶片光子元件整合在 一般的矽晶片上,如此一顆晶片便可應用在通訊、生醫偵測、 環境監控等許多領域[1]

試圖讓矽發光一直是長遠的目標,2004年秋天,UCLA 教授Bahram Jalali的團隊拔全球頭籌首次讓矽發出雷射;2005年二月,英特爾光 子科技實驗室利用拉曼效應使矽雷射從脈衝雷射成為連續雷射,突破 了以往受制矽基雷射光源的不穩定性,但離矽光子晶片整合的目標還 需克服許多問題,如能發展矽基為主的半導體光源,即可利用現有價 廉的CMOS製造技術,取代III-V族發光元件與矽基板wafer bonding 的製程,節省量產成本,另一方面,當光子及微電子元件整合在同一 個矽基底上,光電系統晶片在訊號的運算處理上將更快更有效率。 過去關於利用光子晶體以增加出光效率的研究已累積相當大量 而臻於成熟,由於電磁波相位週期性的本質,使得週期性結構成為關 鍵要素,經由微觀的材料成長與製程,製作幾何尺寸與波長相近之元 件結構,來達到控制調變光訊號的目標。一維的光子晶體早已廣泛地 用在許多光電元件上,例如光纖中的布拉格光柵, 垂直共振腔面射型 雷射中的布拉格反射鏡(DBR),及分布回授雷射(DFB Laser)等,如果 光子晶體週期性的排列中有一些瑕疵,會對原本被阻擋的電磁波波段 產生一些可穿透的通道,二維光子晶體中的點缺陷可以侷限光子以形 成高Q值的共振腔或濾波器,進一步線缺陷則可用以做光波導用,整合 這些以二維光子晶體為主的主動及被動元件可形成極小且多功能的 光子電路,近幾年來文獻中可見二維光子晶體的奈米共振腔已可達到 極高的Q值,而這些量測到的Q值(單位光週期所儲存之能量與消耗之 功率之比值)顯示出光子晶體共振腔可提供極佳且三維的光子侷限, 為前瞻性光電元件的基礎,圖1-2為近年來二維光子晶體發展的簡圖 [2],上下由空氣包圍發光層,在發光層上的光子晶體,藉由不具空氣 孔洞的缺陷區域來形成光子晶體雷射的微共振腔,平面方向的侷限主 要是由光子晶體光能隙的效應所提供,在垂直方向的侷限則是由發光 材料層與空氣間折射率差所造成的全反射作用所提供,其Q值已達到 數百萬等級。光子晶體可以針對不同光波長以及所需的光能帶關係來 個別設計製作,因此具有非常大的彈性與無限的可能性可應用於許多

光電元件,包括:微小化低電流的半導體雷射、可調放射波長且高效 率的發光二極體、高效率光放大器、低耗損的彎曲波導、微腔振盪器、 可調式窄波通光柵等等。以光波導來說,傳統積體光學所製作之波 導,其彎曲的角度通常很小,但光子晶體組成的光波導利用光子能隙 使光過不去,如果引入缺陷,破壞晶體結構的週期性,造成在光子能 帶隙中產生了光缺陷模態帶,可以控制光波在缺陷模態能帶的傳輸, 能以90°(甚至可達120°以上)大轉彎的光學波導中轉彎,在極短距 離內控制光進行的方向,亦能在空氣中傳播,也可以做分光、轉彎、 耦合等動作,而且只有少量的能量損失於光波導中。 為了實現矽基半導體光源,可以從兩方面來著手,一. 利用高內 部量子效率的奈米矽晶材料作為發光層,如奈米矽晶結構或量子侷限 效應可以增加內部量子效率並控制出光頻譜範圍,藉由高度均勻的量 子點來增加特定發光波長效率,也可以利用對量子點的操控性,調整 工作的波長,二為利用光子晶體優異控制光的能力來提昇出光效率。 圖1-2 二維光子晶體共振腔的Q值在過去7年中 有穩定的成長,插圖為奈米腔的SEM照片

近年來受到世界上研究者矚目的光子晶體可以提供新型光電元件的 製作,尤其重要的是可以大幅縮小元件的體積,並密集的積成、降低 製作成本避免昂貴的元件成本成為阻礙,在這方面光子晶體將對光電 技術發展產生革命性的影響。 1-2 動機 文獻方面利用光子晶體結構設計搭配量子點結構發展矽光源, 2006年Stanford University發表一篇以富矽氮化矽當發光材料,如 圖1-3所示,單純利用二維光子晶體點缺陷結構使得光激發螢光發光 強度達到4.5倍的改善,證實矽半導體光源的可行性[3] 。為發展矽 基半導體光源,我們將利用矽基奈米微晶搭配光子晶體來改善內外部 的出光效率,利用實驗量測出光頻譜來歸納光子晶體影響出光的眾多 因素,搭配模擬的假設利用出光頻譜以驗證,進而增加模擬對於出光 頻譜預測的可靠性,幫助對於發展矽基半導體光源出光做進一步探 討。 圖1-3 2006年Stanford University發表利用富矽氮化矽發光材料 搭配二維光子晶體結構達到光激發螢光發光強度7倍的改善

參考文獻

[1] Digitalhome月刊95年8月號(圖片來源:Intel)

[2] Benisty, H.; Lourtioz, J.-M.; Chelnokov, A.; Combrie, S.; Checoury, X. “Recent advances toward optical devices in semiconductor-based photonic crystals"Proceedings of the IEEE 94,997 (2006).

[3] Maria Makarova, Jelena Vuckovic, Hiroyuki Sanda, and Yoshio Nishi,

Appl. Phys. Lett.

89, 221101 (2006).第二章 實驗原理及樣品介紹 在所使用的樣品中,包含矽(鍺)奈米微晶於奈米孔洞二氧化 矽薄膜,以及矽奈米微晶於氮化矽中的兩種樣品,因為我們都需要利 用到高密度化學氣相沈積系統,在此先介紹以此系統發生反應的理論 背景,以及在眾多化學氣相沈積系統中,我們選擇高密度電漿化學氣 相沈積系統的原因。 2-1 實驗原理 2-1-1 電漿原理 為瞭解化學氣相沈積系統工作原理,首要需瞭解的就是電漿的工 作原理,電漿是為一種部份離子化之氣體,由於其性質異於一般物質 三態固態、液態和氣態,可稱為是物質的第四態,正常情形下整體呈 電中性,其內部組成包括帶電荷之電子、離子及不帶電的中性氣體原 子(分子)和激動狀態的中性分子(Radicals)等物種,一般激發方 式可對氣體施加電場、電子束轟擊或雷射,都能得到電漿,內部組成 端看氣體種類、氣體壓力以及施加能量等等來決定。 首先,電漿可區分為低溫電漿和高溫電漿(熱電漿)兩種。用以分別 此二者主要取決於氣體壓力。高溫電漿(熱電漿)狀態為當在較高的 操作氣壓時,因為電子、離子和中性粒子碰撞頻繁,粒子間的能量可 以互相傳遞,使得三種粒子溫度接近,因此氣體的溫度可高達數萬或 數十萬K,氣體的離子化程度(degree of ionization)可以達到較 高的程度,甚至可以高達100﹪,高溫電漿(熱電漿)可應用於焊接 及切割和電漿焚化等等。低溫電漿狀態為當在較低之操作氣壓時,一 個粒子的動能可經下式轉換成溫度:動能 = 1/2mv2 = 3/2kT,因此 離子溫度遠比電子來得低,且中性原子或分子因無法被電場加速,加 上低溫電漿狀態為操作壓力小的緣由,受電子或離子的碰撞頻率較

低,以致於粒子間能量轉換頻率很低,因此整體溫度接近室溫,所以 氣體的離子化程度往往非常低,傳統電漿離子化程度約在1%左右,稱 之為低溫電漿。 藉由控制低溫電漿中的電子溫度,動能轉換成溫度可能達幾萬度K的 能量,利用電子碰撞原子或分子的能量轉換,由於電子的質量遠小於 原子或分子的質量,原子或分子的動能幾乎不會增加,所以能量幾乎 以位能形態傳給原子或分子,如此以高能電子打斷化學鍵,但卻不會 提高原子或分子的溫度,其最大優勢是藉由電漿反應可以取代以往需 要利用高溫分解程序的反應,甚至可應用於積體電路元件的製程,擺 脫後段製程熱穩定性問題[1]。 對於激發電漿的能量形式來說,如果以直流放電的方式,電極需裝置 在反應器內部,為避免電荷累積的情況產生,電極區也必須為良導 體,但電極裝置在反應器的內部會使得電極受到電漿的轟擊,於這種 方式容易造成電極上某些地方的損害而形成表面的小突起,如此非常 容易形成電荷累積產生小電弧(Arc),而且直流方式因為無法來回 反覆碰撞,因此需要輔以離子撞擊電極以產生二次電子來幫助解離, 如此才能產生足夠的電漿,但結果將會造成電極材料的損耗。如以射 頻激發放電,激發的情況可利用反覆碰撞一直持續下去而無需二次電 子的發射,電極或腔體也不怕損害,而且較高的離子化程度能讓系統 在較低的電極電壓下操作,對於電漿轟擊元件所導致之損壞可大幅改 善。 電漿的產生是靠極高動能電子碰撞氣體原子或分子而產生解離,其反 應包含以下數種 激發(Excitation):電子能階由基態上升至激發態 離子化(Ionization):電子撞擊中性粒子而產生離子-電子對 弛緩(Relaxation):能量狀態由激發態降至另一較穩定之能階 再結合(Recombination):正電荷與負電荷中和並釋放能量

解離(Dissociation):電子將分子間鍵結打斷而形成自由基 電荷轉移(Charge Transfer):粒子間電荷互換 等反應,由電場中累積到大於離子化所需要的最低能量,而能量的累 積取決於電場和平均自由徑的大小。 電子(離子)的最高動能 = 電場對電子(離子)作功的累積 = F × d (作用力 × 距離) = q‧ε‧λ 其中q 表粒子的帶電量;ε代表電場大小;λ是粒子的平均自由路 徑,平均自由路徑是指平均移動多少距離就會碰撞到一個原子或分 子, 由上式比較電場對電子或離子做功的累積程度,在同系統中所 受相同電場作用下,由於離子有相對於電子較大的半徑,其碰撞的機 率上升許多,其平均自由路徑會比電子小,且每經過一次碰撞,原先 累積的能量效應就會耗損,而需重新累積,加上離子質量遠大於電 子,所以於相同電場下之加速度遠小於電子,故離子所具有的動能遠 較電子為低,就電子而言,因平均速度快於離子許多,如果將平板電 極其中一極以射頻驅動並以電容耦合,一般使用的是13.56MHz 頻率 下,可視為僅有電子可遵循外加電位的變動,即電子具有較大遷移 率,亦即電子海會依著射頻頻率在相對穩定的離子海中前後運動,於 是電子向邊界漂移並造成邊界附近有較多帶負電之電子,相對於接近 兩極區域的邊界,離兩極較遠的中心稱之為電漿區,則相對有較多帶 正電之離子,因而建立電場,相對於邊界電位其電漿區電位為正電 位,稱之為電漿電位。若以電流的觀念敘述,於一週期內驅動端電極 的淨電流不為零,於是電極上開始堆積負電荷,形成負偏壓,穩定時 負偏壓值將剛好使驅動端電極的淨電流為零,如此形成的電漿電位負 偏壓稱為自我偏壓(self bias),而基材表面或系統槽壁上會形成負 偏壓的電漿暗區(Sheath)[2],sheath將開始減速電子而加速離子, 離子則因受sheath的影響乃被加速而撞擊基材表面,而導致整個系統 電漿反應。如圖2-1-1-1所示,利用電漿暗區的觀念,電感式耦合電 漿系統其晶體基板放置的那一電極,稱為基板電極,串聯一個阻絕電

容,因為產生一自我偏壓的原因,會使的電漿暗區的負壓強度加深, 使得操作的相對負壓範圍加深許多,因此基板電極所受到對離子的電 場強度相對提高,對於製程反應提升有所幫助。 2-1-2 沈積薄膜的成長模式 決定沈積薄膜成長的模式在於三種參數,分別為基板,界面,薄 膜的表面自由能。文獻中[3]提出會有三種薄膜成長模式接近熱平 衡,決定於三種參數在整個表面自由能之間的關係,如圖 2-1-2-1[7],第一種成長模型[4]是依次成長二維層狀薄膜在基板 上,其特徵為薄膜和界面之間的自由能總合會小於基板的自由能。第 二種成長模型[5]是運用在沈積材料若能最小化它本身的自由能,而 這最小化的方式是以增加表面區域交換以減少的界面區域,如同水滴

RF

Dielectric cap

阻絕電容

ICP source

圖2-1-1-1 電漿化學氣相沉積系統結構示意圖, (基板電極串聯阻絕電容)滴在玻璃上,此成長模型會形成島狀結構,和第一種模式相反,它的 薄膜和界面的自由能總合會大於基板的自由能。第三種成長模型[6] 是因為沈積材料的晶格常數與結晶基板的不匹配導致,加上界面能 低,若磊晶厚度高於張力所能承受的臨界厚度,薄膜會破裂而產生缺 陷,SK模式可用於自聚性量子點成長,其特點就是在薄膜破裂前,島 狀物剛形成時,即停止成長磊晶,這樣可得到無缺陷的量子點,其成 長是由建立二維的潤溼層開始,在形成幾層單一層之後會開始島狀結 構的形成,其成因是在島狀結構內部為了降低應力而使得錯位合併。 在此,薄膜與界面自由能的總合不一定會大於或小於基板的自由能, 由薄膜厚度改變來決定。由於不匹配產生應力的貢獻增加,厚度上升 會使的薄膜的表面自由能上升,因此對於薄膜和界面之間的自由能總 合會小於基板的自由能的成長狀態,會形成層狀成長,但膜厚增加, 便會使薄膜和界面之間的自由能總合會大於基板的自由能的成長狀 態,於是島狀結構的成長會產生。 2-1-3 薄膜成核沈積理論 晶圓上之所以可以產生薄膜,初始於達基板的原子必須將縱動 圖2-1-2-1 三種薄膜成長模式示意圖

量發散,佈滿在晶圓表面上的許多氣體分子或其他粒子,如原子團 (Radical)和離子等。這些粒子可能因為發生化學反應,再沉積在晶 圓的表面上,或是在表面擴散運動之後,被晶圓表面所吸附而再進 行沉積的。而薄膜沉積的機制,以下與圖2-1-3-1說明整個化學氣相 沉積的過程[8][9][10]: (a)長晶(Nucleation) 反應氣體粒子到達晶圓表面時,因失去部分的動能而成為吸附原 子。這些吸附原子可能與其他的吸附原子因交互作用,或者反應, 在晶圓的表面上形成一穩定的核團(Cluster),如果核團的半徑大於 此一臨界半徑(Critical Radius),此核團不但能在表面上存在,且化 學性地被吸附在表面上。吸附原子可能經吸解(Desorption)而回到原 來的氣相內。因此佈滿晶圓表面的氣體分子所進行的成長凝結 (Condensation)為粒子的吸附與吸解達平衡時的結果。基本上,晶 圓表面溫度愈高,因為粒子在表面所具有的活動力較高,吸附原子 被表面所吸附的能力就愈低。 (b)晶粒成長(Grain Growth) 當進入個別的晶粒成長之後,晶粒成長所需要的原子來源,除了吸 附原子,也可以是氣相中傳來的粒子,經晶粒碰撞後而成為晶粒的 一部份。但晶粒初期的成長大多都依賴吸附原子的加入,因為當晶 粒的體積還小時,粒子碰撞發生的可能性較低。 (c)晶粒聚結(Coalescence) 因晶粒的成長所增加的半徑,使得原本個別且獨立的晶粒已大到開 始與附近的其他晶粒相接觸時,晶粒間的內擴散便開始進行,兩者 在調降表面能的驅動力之下,合併形成一個半徑較原來晶粒大的新晶 粒。若是兩晶粒的晶格結構不同,則晶粒內部還要再經過“再結晶 (Recrystallization)"的步驟,使新的晶粒能態比原來兩個個別晶粒 還來的穩定。原則上,成長位置溫度愈高,擴散能力愈好,吸附原 子也就愈容易找到理想的位置進行聚結。所以,溫度愈高,成長的 晶粒也就愈大,薄膜的均勻性也就愈好。

(d)縫道填補(Filling of Channel) 晶粒合併為了調降彼此的表面能,連接兩個晶粒的頸部(Neck)將在 晶粒間的內部擴散下形成。接著,擴散將漸漸的把頸部填滿,而形成 的縫道,基本上,就是晶圓表面尚未被吸附原子或是晶粒所覆蓋的 區域。當這些位於晶粒間的縫道也陸續地被填滿之後,整個完整的 薄膜便初步的在晶圓表面上形成了。 (e)沉積膜成長(Film Growth) 當薄膜初步的在晶圓表面上形成後,接著,薄膜沉積便往增加薄 膜厚度的方向繼續的進行。 2-2 樣品介紹:矽(鍺)奈米微晶於奈米孔洞二氧化矽薄膜 首先介紹的是我們利用溶膠凝膠法搭配電漿化學氣相沈積製作 矽(鍺)奈米微晶於奈米孔洞二氧化矽薄膜,矽是半導體製程中最 圖2-1-3-1 化學氣相沉積薄膜沉積的過程

重要材料,但因為其有著間接能隙(約1.1eV)以及非常小的激子束 縛能(約15meV),所以其室溫下發光效率非常低。利用空間上的量子 侷限可以克服矽的天生缺陷,突破即能接躍遷受到倒晶格空間限制的 間接能隙,且使得激子束縛能增加。此前已有許多文獻對於矽發出可 見螢光有重大突破[11.12],因為塊材單晶矽本身的波爾半徑大約為 4nm,因此必須要讓我們空間侷限到奈米等級以下使得直接能隙出現 才有達到量子侷限目的[13.14]。而在目前的文獻當中,對於矽奈米 微晶的發光機制來源可分為兩方面,第一種來源是量子侷限效應 (quantum confinement effect):奈米微晶鑲嵌在高能隙材料中的量 子侷限產生的不連續能階,作為其發光機制[15,16]。第二種來源是 由於矽奈米微晶與外圍高能隙塊材介面的表面態 (interfacial state):此主要發生在奈米微晶的介面處會產生侷域能階 (localized state),因此侷限載子並復合發光[17,18]。 在此所使用的矽(鍺)奈米微晶樣品,其發光機制來源是利用奈 米微晶介面處產生的侷域能階來發光[19],即介面處的氧缺陷能階, 所以與多孔洞之矽薄膜發光來源一樣,利用奈米孔洞二氧化矽薄膜多 孔性的特徵,將矽(鍺)奈米微晶鑲嵌於內部表面,利用製程控制奈 米孔洞二氧化矽薄膜的多孔性(30~75%),以及孔洞大小(2~ 10nm),相對於塊材而言有著非常高的面積對體積比,對於利用介面 處侷域能階發光的機制為極大的優點,在下段將有更詳係說明。 為瞭解成長樣品使用HDPCVD的原因以及目的,必須先瞭解整個樣 品的製程流程及其原理,在此介紹本論文中所使用的矽(鍺)奈米微 晶樣品,首先是成長矽奈米微晶於奈米孔洞二氧化矽薄膜,為此必 須先在p-型矽基板上形成奈米孔洞二氧化矽(mesoporous silica, MS)薄膜作為矽奈米粒子沉積的模板[20],在這步驟使用分子自行 聚成奈米孔洞二氧化矽薄膜的方法,首先配製二氧化矽溶膠凝膠, 在70℃下將水、鹽酸、四乙氧基矽烷tetraethylorthosilicate (TEOS) 、乙醇流動混合90分鐘,TEOS為提供二氧化矽的來源,接

著將選用十六烷基三甲基溴化銨(cetyltrimethyl Ammonium bromide (CTAB)), 或非離子型C16EO10 polyoxyethylene cetyl ether

(Brij-56), 或Triblock copolymer Pluronic P-123 (P123))三種有 機溶劑混入,以形成奈米規則孔洞二氧化矽薄膜的溶膠凝膠先驅體, 這三種有機溶劑其功用主要為用來控制孔洞大小,如同肥皂一端親油 端,一端親水端的結構,選用此三種任一種都可以藉此調變孔洞大 小,此外選用其他有機溶劑亦可達到三維奈米規則孔洞二氧化矽的結 構[20],如圖2-2-1所示,而且其有結構引導形成奈米孔洞的媒介功 能,但於我們所需用途不符,因此不列入參考。所有反應液體混合的 摩爾比例範圍為1:0.008-0.03:3.5-5:0.003-0.03:10-34 (TEOS/(P123,CTAB,Brij-56)/H2O/HCl/ethanol),而後置於室溫下攪 拌三小時以上,利用酸當催化劑幫助使其成熟,再以旋轉塗佈於矽基 板上,轉速2200轉,時間30秒,最後先在40℃下五小時使之乾燥,為 了也是讓內部鍵結如同肥皂一般有時間完全形成聚合,接著可利用類 似一般黃光製程步驟的軟烤與硬烤來完成,以110℃下三小時 hotplate烤乾,以使之揮發掉乙醇且結構引導自行聚合成奈米孔洞二 氧化矽,將會使其體積以及孔洞距離縮減,使結構更為緊密結實 [21],如果只是成長奈米孔洞二氧化矽而無其他後處理步驟,因為 此為內含有機物質的奈米孔洞二氧化矽,水氣可能會造成結構效率降 低,為防止水氣在表面形成鍵結,可利用HMDS和表面親水性Si-OH (Silanol group)形成鍵結(Silylation Reaction)達到保護作用 [22],如圖2-2-2所示,或者選用trimethylchlorosilane(TMCS)也有 和HMDS同樣的功能,另外如果只是要除去奈米孔洞二氧化矽的內部 有機物質以得到單純的奈米孔洞二氧化矽,可利用兩種方式,第一 種方式是因為有機物質很容易藉由熱能揮發,因此我們可利用爐管退 火燒結的方式去除有機物質,第二種方式是單純利用氫氣電漿去除有 機物質而已,整個反應流程如表2-2-1所示。

圖2-2-1 文獻中選用不同有機溶劑,以形成一維,二維,三 維奈米規則孔洞二氧化矽結構

圖2-2-2 奈米孔洞二氧化矽表面,防止水氣在表面形成鍵結, Silylation Reaction為親水性Si-OH group形成鍵結達到保護作用

其次再利用電漿沉積技術,以成長矽奈米微晶於奈米孔洞二 氧化矽薄膜的模板內,電感耦合式電漿化學沈積系統(Inductivity coupled plasma-chemical vapor deposition (ICPCVD))為廣泛沈 積薄膜使用的系統工具,在此我們使用高密度電漿化學沈積系統 (High-Density Plasma Chemical Vapor Deposition (HDPCVD)), 其擁有低沈積氣體壓力與高電漿解離密度等優點,可控制大量的離子 流進入反應,降低離子對於反應表面的傷害,未反應時系統處於高真 空壓力高達10-6torr,在反應時定射頻功率於500W,如要成長矽奈米 微晶,操作時基板溫度定於400℃,如要成長鍺奈米微晶,操作時 基板溫度定於250℃,而10mtorr為整體氣體操作壓力,為使矽奈米 微晶嵌入奈米孔洞二氧化矽薄膜的模板內,利用通入H2/SiH4(or H2/GeH4)反應氣體電漿達成,中間以氫電漿處理隔開,以一秒/三秒週 期進行12-18次。 在奈米孔洞二氧化矽薄膜的模板內嵌入矽奈米微晶牽涉到多種 反應,其奈米微晶TEM圖為圖2-2-3,實驗反應的流程如圖2-2-4所示 [19],先後分為三個步驟,第一個步驟,週期中的純氫電漿將會輕微

Aging for 3-6 hours, RT

Spin coating on Si wafer Precursor sol gel :

TEOS/H2O/HCl/ethanol 70℃, 90min

MS template preparing flowchart

表2-2-1 流程圖為成長奈米孔洞二氧化矽薄 膜所準備的溶膠凝膠步驟

的在二氧化矽孔洞內移除一些有機模板,使得二氧化矽孔洞表面 Si-OH群裸露出來,第二個步驟,在二氧化矽孔洞表面形成的Si-OH

群用以支撐用使的SiHn(GeHn)進入致使成核反應的,此即類似原子層

化學氣相沉積(Atomic Layer Chemical Vapor Deposition, ALCVD) 的中心概念SLR反應(self-limiting reaction)[23],因此有著非

常好的階梯覆蓋率,接著電漿解離的SiHn (GeHn)自由基將擴散到孔洞

內,結晶位置最後以HER反應(hydrogen-elimination reaction)成 矽量子點,其反應為[Si-OH + SiHn(GeHn) → Si-O-SiHm(GeHm) + H2],

第三個步驟,利用爐管退火方式使釋放出氫氣,反應如

[Si-O-SiHm(GeHm) → Si-O-Sin(Gen) + H2] 將轉換Si-O-SiHm(GeHm)

成Sin (Gen) 成核反應[24],此外通氫電漿有另外一個緣由,亦即利 用電漿在化學氣相沉積半導體製程中,氫氣自由基於薄膜成長中有控 制晶粒大小以及增長晶粒大小甚至形成單晶的能力,利用的是氫自由 基高機動性在內部遷移造成應力釋放以及缺陷填補的能力,藉由壓低 蟄伏層的能力來控制結晶大小[25],此成長方法其量子點密度可以高 達0.7 x1012/cm2,2.5x1018/cm3,量子點大小約3~5nm,其TEM圖如下 所示。 圖2-2-3 奈米孔洞二氧化矽薄膜的模板內 嵌入矽奈米微晶的TEM圖

2-3 樣品介紹:矽奈米微晶於氮化矽薄膜 在此介紹的是我們所欲成長的第二種樣品,矽奈米微晶於氮化 矽薄膜,製程主要是利用高密度電漿化學氣相沈積系統搭配熱退火方 式完成。此前已有許多文獻對於矽奈米微晶於氮化矽薄膜發出可見 螢光有深入研究[26]。 而在目前的文獻當中,對於矽奈米微晶的發光機制來源依然可分 為兩方面,第一種來源是量子侷限效應(quantum confinement 圖2-2-4 (a) 奈米孔洞二氧化矽與有機模版示意圖 (b) P-123聚合物與奈米孔洞二氧化矽表面反應放大圖 (c) 圖示為嵌入於奈米孔洞二氧化矽有機物質的SiHn鍵結 (d) 利用ICP電漿處理成HER反應之後於奈米孔洞二氧化矽 內形成的矽奈米微晶示意圖

effect):利用奈米微晶鑲嵌在高能隙材料中的量子侷限產生的不連 續能階,作為其發光機制[27]。第二種來源是由於矽奈米微晶與外圍 高能隙塊材介面的表面態 (interfacial state):此主要發生在奈米 微晶的介面處會產生侷域能階 (localized state),因此侷限載子並 復合發光[28]。一般情況樣品發出可見螢光的來源會由此二互相競 爭,與我們所採用的第一種樣品不同的是,我們所欲利用的發光訊號 是源自於量子侷限效應,因此通常需要利用熱退火以降低其他額外的 訊號來源,以利分析。 氮化矽薄膜廣泛地被應用在半導體製程上,因為它有適當的能障 高度以防過低導致的漏電流上升,可降低元件的操作電壓與讀寫速率 和效率,高的介電常數可防止直接穿遂電流與應力誘發漏電流,具有 抗氧化,抗水氣,以及防堵鹼金屬離子滲透與擴散阻擋層的特性,常 用於製程蝕刻的遮罩,亦能做為半導體元件的保護層[29],而我們選 用氮化矽當塊材而非二氧化矽的原因主要有二,首先以光波導的觀念 來看,需要的是更多的能量分佈於主動區以激發矽奈米微晶,而對 氮化矽而言其折射率(2~2.1)相較於二氧化矽(~1.4)大許多, 因此為其優點之一。第二個原因是為了發展矽基材料的半導體光源, 對於外在激發載子能量的注入絲毫不能浪費,否則發光效率將會極 低,而二氧化矽其非常高的能隙(~8.5eV),使得矽奈米微晶與塊 材之間的能障太高,將嚴重限制載子注入,會侷限我們操作電壓 於較高的範圍,此使得應用於矽基材料的半導體光源將受到非常大的 限制[30],因此以氮化矽較低能隙(~5.3eV)來取代二氧化矽[31 同高溫4],可以改善激發載子能量的注入奈米微晶的問題,與矽基 材料的半導體光源的激發效率。 目前常見的矽奈米微晶的製程方式有以下幾種:(1)離子佈植 技術(Ion implantation):是利用矽離子源,直接以離子佈植方式 將矽原子植入高能隙材料層,但製程本身相對緩慢不切經濟。(2) 電漿化學氣相沉積技術(Chemical vapor deposition):利用解離方 式激發反應氣體,形成電漿態以磊晶。文獻上還有許多方法成長矽奈

米微晶,但受限於製程因素大多都是以二氧化矽為塊材,因為對 二氧化矽成長奈米微晶的方式,直觀來看只要超過原子比例的當 量讓額外的矽原子析出,或是利用熱退火,濺鍍蒸鍍等物性化性 方式皆可,如(1)真空濺鍍技術(Sputter):利用雙靶材控制矽 原子份量[32],(2)電子槍蒸鍍技術(Evaporation):利用電子槍 蒸鍍控氧化矽粉末[33]。 相對之下,三五族製程就受限許多,而且如以TEM驗證方面 的難度來看,大部分的奈米微晶大多為非晶質,氮化矽薄膜不似 二氧化矽有結晶相分佈,因此非晶氮化矽將會使得矽奈米微晶更 難以分辨。目前文獻上利用成長矽奈米微晶於氮化矽薄膜,幾乎 都是用電漿化學氣相沉積系統(Chemical Vapor Deposition)來做, 主要是因為其擁有相對之下低成本,製程簡單,以及大面積高速成長 等優點,因此廣泛為大家所使用。 2-3-1 文獻回顧 目前文獻上成長矽奈米微晶於氮化矽薄膜絕大部分是以增強 式電漿化學氣相沉積系統製作,如果我以成長反應時的基板溫度作 為分野,明顯有兩派文獻,一派是設定以幾近室溫當作基板的成 長溫度,另一派是設定以攝氏三.四百度當作基板的成長溫度, 因此以基板溫度的參數做分野來做文獻回顧。首先是回顧以幾近 室溫當作基板成長溫度一派的文獻,當然其最大的好處在於低製 程溫度能讓製程整合的選擇性廣泛,而不怕後段熱處理對元件或 摻雜物造成影響。 在2003年Y. Q. Wang等人使用增強式電漿化學氣相沉積系統沈積 矽奈米微晶於氮化矽薄膜[34][35],而他們也沈積了矽奈米微晶 於二氧化矽薄膜當作比較,內文提到選用氮化矽取代二氧化矽當 作塊材的優點有二,第一是因為成長矽奈米微晶於二氧化矽薄膜 需要後段退火高達1100℃以上,才能使奈米微晶與塊材介面分隔

清楚,以理清量子侷限以外的訊號,如介面或是缺陷等侷限能 階,但高的製程溫度嚴重限制製程整合的選擇性。第二是因為如 此高溫退火會限制到奈米微晶的大小,因為退火會助長奈米微晶 成長,也可能和鄰近的奈米微晶合一而變的更大,造成量子侷限 訊號紅移而限制在紅光甚至紅外波段區。他將成長溫度控制在不 高於60℃,最後他們量測出光強度比無矽奈米微晶於二氧化矽薄 膜高5倍的改善。在2005年Cheng Liu等人同樣在成長溫度控制不高 於50℃下長膜[36][37],內文提到控制奈米微晶大小的參數,一 般是利用控制SiH4和N2或者NH3流量比例來控制,但其比例讓矽 奈米微晶生存有一個下限,亦即不能太小,所以矽奈米微晶於氮 化矽薄膜以光致激發螢光偵測,訊號限制量子侷限出光頻譜為 400nm以上,即3.1eV以下。在2006年L. B. Ma等人同樣在成長溫度 控制不高於50℃下長膜[38],差別在於其實一般的電漿是屬於放 熱反應,因此會造成溫度不斷上升,如此會影響到製程上需要幾 近室溫的狀態,所以他們每當溫度達50℃時,即等系統冷卻到室 溫再繼續進行。 接著回顧以高達250~300℃作基板成長溫度一派的文獻,當然 其最大的好處在於,大多文獻在薄膜成長時同步形成奈米微晶, 不需要額外熱退火處理,還有高溫的基板狀態使得反應前驅物成 核後有足夠能量,來移動到適當的位置與成晶排除缺陷,所以薄 膜品質較佳,不怕過多的缺陷造成發光效率低落,讓能量能進入 奈米微晶發出量子侷限訊號。 在2001年Nae-Man Park等人使用增強式電漿化學氣相沉積系統 沈積矽奈米微晶於氮化矽薄膜[31][39],利用氮氣當反應氣體,並 無通其他載氣(carrier gas),其目標是利用可調的奈米微晶其量子 侷限能階,來當作發光光源以達到全彩發光二極體的目標,利用光致 激發螢光訊號推算其量子侷限空間,假設侷限於三維無窮大的能障去 推算內部的不連續能階,量子侷限能階可由塊材能隙加上理想的不連 續能階,其公式(2.1)如下 [40],

⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ + + + + + + = − ⊥ − − ⊥ − − − 2 1 1 1 2 1 1 1 2 1 1 1 2 2 0 2 d m m d m m d m m E Egap gap l h t h t h h π (2.1) 對於矽在300°K下其能隙為1.12eV,n以一取代,縱向與橫向有效質量 (longitudinal and transverse electron effective masses)為ml = 0.92m0, mt

= 0.19m0,重電洞質量(heavy-hole mass)與在垂直於侷限方向的重電

洞質量為mh = 0.54m0, mh┴ = 0.2m0,如果假設奈米微晶三維侷限的空

間皆對稱,可令d1,d2,d3,同等於a,將以上條件代入其公式可簡化

為E(eV) = Ebulk + C/a 2 ,利用出光訊號的峰值來推算,因此可以推算 出奈米微晶能隙,一般皆為非晶矽(1.5~1.6eV),以及可算出C值(侷 限因子)以比較其奈米微晶的量子侷限程度。在2004年Tae-Youb Kim 等同一批人沈積矽奈米微晶於氮化矽薄膜[41],特別在於他們認為 於薄膜內成長矽奈米微晶,內部氫鍵功用遵守著內部氫自由基促成 的擴散機制,氫鍵幫助奈米微晶成長的機制詳細於後段描述,如此 擴散機制能幫助奈米微晶成晶,所以他們認為薄膜長速必須夠慢,才 能使擴散機制夠時間即時去幫助奈米微晶成晶,因為一般原子在其上 方繼續成長薄膜,厚度增加只會造成下層原子更難移動,他們提出薄 膜長速在高於2.3nm/min時,會使得奈米微晶成非晶質,在低於 1.7nm/min時,奈米微晶才能即時成晶,如此對奈米微晶才有較佳的 空間侷限。在2005年Baek-Hyun Kim等同一批人提出以氨氣取代氮氣 當做反應製程氣體[42],對於出光強度的改善非常大,其出光強度甚 至比退火後利用氮氣當反應氣體的薄膜更強,主要是利用來自氨氣更 多的氫鍵來幫助鈍化許多的非發光性缺陷,其他文獻解釋為氫鍵幫助 降低介面缺陷能階密度以及有更高密度的奈米微晶,文獻上[43]利用 C-V量測以觀查奈米微晶儲蓄載子的能力,發現經氫鍵鈍化的樣品漏 電較少,其證實若缺陷能階未被鈍化,將可能產生接近量子侷限能階 的電子或電洞陷阱,導致放電途徑的產生,使得載子更容易進入奈米 微晶以發光,此外相較於使用氮氣當反應氣體,來自氨氣的氫鍵也使 得奈米微晶更容易成晶,內容也提出光致激發螢光的出光訊號來源其

實不只量子侷限,因此理清訊號來源也是實驗非常重要的一環,當然 還包括一些發光的缺陷以及介面相關能階,詳細矽奈米微晶於氮化 矽薄膜的相關發光缺陷能階將於後段描述。在2006年Tae-Wook Kim等人同樣以氨氣當反應氣體一步成長奈米微晶[44],可以使 得奈米微晶的侷限因子提升到13.9,而且其能隙降到1.13,遠低於非 晶矽能隙(1.5~1.6eV),顯示奈米微晶已非常接近塊材矽的1.12,主 要是因為氫鍵幫助鈍化以及幫助原子移動到適當位置,使得矽不規則 排列轉向規則排列。 文獻上已經有許多研究針對於矽奈米微晶於氮化矽薄膜的相 關發光缺陷能階的分析探討,首先必須直觀地了解到對於矽奈米微 晶於薄膜品質佳的氮化矽薄膜來說,發光缺陷能階最容易大量地存 在於界面處,如奈米微晶與塊材界面處或者薄膜表面介面處,缺陷於 奈米微晶與塊材界面處將捕捉載子使之不易進入奈米微晶,且此缺陷 發光能階的發光生命期一般為奈秒等級[45],比起奈米微晶短許多, 文獻上[38,46]指出一般矽奈米微晶的發光生命期隨奈米微晶大小成 正比,小奈米微晶因為載子波向量重疊更多以致於生命期更短,但幾 乎都達微秒等級,這也是缺陷較易搶得載子能量之因,一般來說氮化 矽其能隙非一個定值(4.5~5.1eV),其實某些發光訊號是會因此有點 變化,而以Mr. John Robertson所取用的值是針對非晶質氮化矽 5.3eV,大多文獻上皆以在1983年Mr. John Robertson利用tight bonding method方法提出的能帶圖為基準[47],一般發光缺陷能階

包括帶電子與不帶電子的矽、氮的空懸鍵(≡Si0,═N0,≡Si-,═N-),

以及≡Si─ Si≡,還有Mr. John Robertson當時並未提出的氧相關缺陷 鍵結,其相關發光缺陷能階如圖2-3-1所示[48,49],將氮化矽能 隙定為5eV,由Robertson文獻上可以知道能隙間並無═N0的能階存 在,由於其能階位於塊材氮化矽的價帶以下,而≡Si─ Si≡的σ*能階 (Antibonding state)是位於導帶內,由價帶向上算起的能階差依序 為0.2、0.3、0.4、0.7、3.1、3.5eV,不同文獻能階位置都有些微差 距,另外還有矽或氮以外原子參與發光缺陷能階,氧和氫能與矽的空

懸鍵形成鍵結,氮化矽薄膜於室溫即可能受到氧打斷矽間鍵結而侵 入,尤以當低溫成長薄膜時導致薄膜品質不佳影響更甚,氧化會從表 面漸而侵入內部,影響力以水氣為最[50],因此在≡Si─ Si≡附近形成 ═Si─ O─ Si═, N─Si─ O鍵結能階[48,49],另外Si─ H鍵結的σ和σ

* 能階皆落在能隙以外,這也是因為氫鍵能鈍化氮化矽等空懸鍵的原 因[51]。 因此一般樣品其光致激發螢光的訊號可能包含量子侷限訊號,介 面能階訊號,缺陷能階,或者其他原子鍵結造成的訊號,有文獻對於 光致激發螢光的訊號做分析討論[17],其認為量子侷限訊號競爭會在 侷限空間越小時而失去其優勢,主要是因為不連續能階差距越開,導 致較小的氧缺陷能階取代量子侷限訊號而成為主要發光途徑,另一文 圖2-3-1 氮化矽薄膜的相關發光缺陷能階圖

獻也提到[52]矽奈米微晶大約在小於1.8nm,本來受氫鍵鈍化的矽奈 米微晶,如果氫鍵被氧鍵所取代,其發光途徑會被氧雙鍵的介面鍵結 所取代,其認為因為空氣中氣體以氧的電負度夠高,而且水氣亦提供 氧鍵,所以一般討論以氧為主,氮化矽晶相一般分為兩種晶相[53], 如圖2-3-2所示,α-氮化矽與β-氮化矽,皆為六角晶格,α-氮化矽 循著c軸的堆疊順序是ABCDABCD,β-氮化矽循著c軸的堆疊順序是 ABAB,由矽的四面體鍵結搭配氮的平面鍵結組成,Si2N2O排列方式會 由[Si2N2]n組成一面搭配氧組成第三軸,而雙鍵造成矽原本sp 3 軌域形 變,將會使得能隙降低更多,這也是雙鍵影響力比單鍵強的原因,其 晶格參數如表2-3-1所示。 圖2-3-2 氮化矽晶相結構示意圖

由以上文獻可以發現到,幾近室溫當作基板成長溫度來成長矽 奈米微晶,他們表示矽奈米微晶皆呈非晶質狀態,因為當反應氣 體形成電漿,在基板上成核反應後,其後續薄膜沉積的能量來源 即由基板的溫度來提供,而幾近室溫的基板狀態使得成核後並沒 有多餘的能量來移動到適當的位置與成晶,薄膜品質不佳,容易 有缺陷,而且薄膜與基板的附著會相對較差許多,因此無法填補 沈積時所形成的縫隙及孔洞,而使得薄膜相對破碎[54],從其他文獻 中指出,在溫度15~150℃沈積出的氧化矽氫薄膜[55],以及在溫度 50~250℃沈積出的氮化矽薄膜[50],比較將薄膜放在空氣中與乾氧 氣中和去離子水後的矽氫鍵結的量,發現矽氫鍵結會被氧化矽取代, 其氧化會從表面開始侵入薄膜內部[50],反應式為2Si-H + H2O → Si-O-Si + 2H2(g),而薄膜放置於去離子水中的氧化速率較放置於空 氣中或乾氧氣中快很多,因此證明了環境中水氣對低溫成長氧化非晶 氮化矽薄膜的氧化速率扮演非常重要的角色,所以大量的空懸鍵可能 讓空氣中的水氣得以滲入,進一步形成穩定的氧化態,如此嚴重影響 我們的薄膜特性,從這一派文獻可以知道,即除了反應氣體之外, 表2-3-1 氮化矽等相關晶格參數表

都會額外通所謂的載氣(carrier gas),皆使用氫氣當作載氣, 原因在於氫氣的功用即幫助薄膜移動成晶,品質更佳,詳細將在 後段闡述[35]。 另外文獻上可以發現到在以近室溫機版溫度來薄膜沈積之 後,都需要快速熱退火幾分鐘加以處理,溫度大約都是500℃即 可,經過熱退火會使得光激螢光訊號增強數倍,一般熱退火顧慮 的是如果薄膜內含氫鍵鈍化等鍵結,如果退火溫度太高將會導致 氫鍵斷裂而逸出,但注意的是,有文獻指出[56],其退火導致氫 鍵斷裂釋出氫氣的臨界溫度粗略地依薄膜內原子比例而定,是一 項值得注意問題,如此造成更多的空懸鍵裸露,產生大量的非復 合輻射中心,因而大大地降低出光效率,這是文獻上指出為何選 用較低的退火溫度的主因[34],但相反的退火溫度高點能幫助內 部原子移動,促使量子點聚合,可使缺陷等消失,以及奈米微晶 與塊材介面分隔更絕對,其介面轉換空間更薄,降低介面能階數 量,因此減低介面抓住載子阻擋進入奈米微晶的機會[36]。所以 文獻上都認為其發光不能單一的認為是特定機制,應當是量子侷 限以及利用奈米微晶大量表面對體積比產生的大量介面能階機 制混合才能合理的解釋出光的訊號[17],詳細退火溫度對於薄膜 內部鍵結影響將於下段描述。 文獻上研究關於退火溫度對於氮化矽薄膜內部鍵結的影 響,一般來說,矽本身外接4鍵結以遵守八堣體狀態,所以退火 會造成Si-Si4-nNn的n(0~4)趨於越大的趨勢,如此會促使奈米微 晶與塊材介面分隔更絕對,其介面轉換空間更薄[57],有文獻以 矽和氮於薄膜內部比例做分野來研究退火溫度的影響,如果以富 氮的氮化矽薄膜而言,所以內部被氫鍵鈍化幾乎都是氮鍵,其退 火反應要到900℃以上才會對薄膜內部鍵結造成反應,為釋放氫

氣反應,反應式為Si-N-H + Si-N-H → 2(Si-N) + H2(g),對非富

氮的氮化矽薄膜而言,當退火溫度高於500℃時,內部鍵結反應 為Si-Si + N-H → Si-N + Si-H,因為Si-H的σ階比Si-Si的低,因

此會造成出光頻譜藍移,並無任何氣體釋放,當退火溫度大於600

℃時,內部鍵結反應為Si-N + N-H + Si-H → N2

↑

+ H2↑

+ Si-Si,整體觀察到的結果來說,就是越富氮的薄膜因為奈米微晶越小而 造成內部鍵結改變,所需的臨界溫度就越高[45,56]。 在此整理以氫氣當載氣的功用,載氣通常用於氣相反應中以 幫助推動反應氣體進入反應室,文獻上認為其功用即幫助薄膜移 動成晶,品質更佳,藉助氫氣可以在較低成長溫度下沈積同樣成 晶品質的薄膜,其反應機制文獻上分為三派,都是以成長矽薄膜 來作為研究樣品,第一種機制為表面擴散機制,其認為反應時氫 離子流或自由基流嵌於表面,會提升表面反應前驅體 (Precursors)的遷移率(mobility),因此增加成晶的大小與機率 [58,59],第二種機制為選擇性蝕刻機制,其認為反應時會同時 成長已結晶相與非晶質而同時存在,但由於氫離子流的存在,將 會選擇性的蝕刻剛成長上去的薄膜,非晶質區域將會遭到較強的 蝕刻程度而已成晶的區域會相對存活下來,如此反應一直下去造 就成晶區域的擴大而完成反應[60]。支持此機制的文獻[61],因 此非常強調蝕刻的相關參數,其改變電漿反應時的射頻功率,發 現功率太大會造成光致激發螢光的訊號強度下降,其解釋為功率 太強導致鍵結受損,因而降低出光強度,因此對此機制而言,良 好的控制反應時沈積與蝕刻相互競爭,才能良好的控制奈米微晶 的生存。第三種機制類似第一種機制,為擴散機制,差別在於為 內部氫自由基促成的擴散機制,利用薄膜內氫鍵的存在,因為其 鍵結能較小的緣故,容易來利用打斷內部氫鍵,造成內部原子的 擾動,因而釋放內部的應力以成晶,因此內部非晶質部份會漸漸 由結晶相所取代。支持此機制的文獻[62],為唯一成長奈米微晶 於高能隙塊材內的文獻,其即利用氫自由基成長矽奈米微晶於二 氧化矽薄膜內。 從以上描述可知道低溫成長的薄膜可能破碎,孔洞化而品質不 佳,雖然有其他優點,如三五族需要熱穩定,低製程溫度能達到

製程整合目的,或因低溫沉積造成SiNx 薄膜內應力的產生,在內應 力較大的地方,行熱退火處理時,容易形成矽量子點 (recrystallization)[62,63,64]。但對於我們目標發光元件化 來說,因為低溫製程造成的薄膜孔洞破碎化而品質不佳,是極大 的缺點,而且文獻上對於發光機制的解釋,卻包含了量子侷限和 介面能階兩種發光機制,對於我們只需要量子侷限發光機制來 說,需要精準控制奈米微晶大小以控制出光頻譜,介面能階的出 現是一個缺點。 2-3-2 實驗結果 以下我們將整理樣品利用高密度電漿化學沈積系統成長的氮化 矽薄膜,首先我們來觀察溫度由300到400℃變化,雖然激發態會使質 量傳輸區域溫度下限更低,但電漿氣體會受到基板直流電壓吸引加速 抵達基板,因為實驗確認操作在質量傳輸控制區對於化學氣相沈積系 統是必要的,實驗參數在表2-3-2與2-3-3,以及薄膜長速和PL強度的 影響,首先對於長速而言,三塊樣品差異不大,因此確認成長操作區 域在質量傳輸控制區,反應受溫度影響不大,可能是因為我們基板電 壓只加了十伏,電漿氣體受到加速的幅度不大,以及我們氣體操作壓 力較大使得擴散速度較慢,電漿氣體抵達基板的速度不會快到超過表 面反應消耗的速度,而當基板速度加大其實會牽扯到的反應不止氣體 電漿物質抵達基板的速度,其實還有他們對薄膜造成的物理蝕刻反 應,將複雜許多,此在2-4-2節有詳細討論,而PL強度大致隨溫度上 升而下降,猜測是因為缺陷發光所致,低溫造成缺陷容易存在之因, 而頻譜震盪的原因猜測為Fabry-Perot共振造成的,計算如下。 表2-3-2 變溫實驗參數

SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 25 475 50 50:10 300 300 1800 1.9994& 11146 (x) 25 475 50 50:10 350 300 1800 1.9229& 12450 (x) 25 475 50 50:10 400 300 1800 1.9454& 11636 (x) SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 25 475 50 50:30 300 300 1800 1.9594& 13745 (x) 25 475 50 50:30 350 300 1800 2.0991& 10914 (x) 25 475 50 50:30 400 300 1800 2.1588& 10819 (x) 表2-3-3 另一變溫實驗參數 圖2-3-3 表2-3-2變溫參數室溫PL量測圖 300 400 500 600 700 800 0 2000 4000 6000 8000 10000 300 350 400 PL inten s ity Wavelength

取圖2-3-3基板300℃參數的室溫PL圖來觀察,於圖2-3-5所示,將氮 化矽的折射係數以2帶入,ΔV=0.56~0.63(10^14),如果厚度大略值 來看,ΔV=0.6(10^14)帶入Fabry-Perot公式,ΔV=c/2nd,光程大約 是1.25μm,對照表2-3-2樣品厚度,以Fabry-Perot共振來看,差異方 面猜測只是光程差的變化,如非正向入射樣品會導致光程差變長之 因,有文獻猜測此乃氮化矽薄膜缺陷能階所造成的訊號分佈[49],如 圖2-3-6與2-3-7所示,但如為缺陷能階發光應該不會受到光程差改 變,而改變其出光峰值位置,因此排除此因素。 圖2-3-4 表2-3-3變溫參數室溫PL量測圖 300 400 500 600 700 800 0 2000 4000 6000 8000 10000 PL intensity Wavelength 423nm 459nm 502nm561nm 635nm 圖2-3-5 圖2-3-3 300℃室溫PL圖 300 400 500 600 700 800 0 1000 2000 3000 4000 5000 6000 7000 8000 PL intensity Wavelength 300 350 400

為排除其發光為缺陷能階的因素,以及確認為Fabry-Perot共振造 成,採用同樣實驗參數但成長時間不同的樣品來比較其PL訊號差異, 實驗參數如表2-3-4,PL圖為2-3-8,可以發現如果PL打在不同位置的 點,有不同的訊號峰值位置發生,這對缺陷能階訊號是不符合的,而 當樣品厚度較薄時,出光頻譜峰值會減少,由Fabry-Perot共振來解 釋,ΔV=c/2nd,當厚度越低峰值間距越大,所量測到的固定頻譜範 圍出現的峰值將越少,可以發現到厚度較薄的樣品其峰值只有2個, 而厚度較厚的其峰值有三個,符合Fabry-Perot的預測,而利用 Fabry-Perot計算出來的理論厚度,以表2-3-4成長時間1800秒的樣品 來計算,大約0.9μm,也是非常接近量測到的厚度。 圖2-3-7 文獻上氮化矽缺陷能階圖 圖2-3-6 文獻上量測氮化矽薄膜室溫PL圖

此外也有人認為這種多重隨頻譜震盪的頻譜可能是因為量子點造成 的多重干擾所造成(Multi interference effect)[65],如圖2-3-9 所示,當光穿過不同介質時,有部分光穿透以及反射,反射部分公式 為 2 1 2 2 1 2 ) ( ) n -(n R n n + = ,當經過偶數次介面反射以及穿透,即可以返回薄膜 與空氣介面,但此考慮太不切實際,且我們經過Fabry-Perot共振計 算其厚度也非常接近,因此排除量子點多重干擾的效應。 SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 25 475 50 50:10 300 280 1800 1.84& 8642 25 475 50 50:10 300 280 1200 1.84& 6732 表2-3-4 變薄膜成長時間參數 圖2-3-8 表2-3-4變厚度參數室溫PL圖 300 400 500 600 700 800 0 5000 10000 15000 20000 PL intensity Wavelength 1800sec,865nm,n=1.84 1200sec,673nm,n=1.84

接著察看基板直流偏壓功率(Bias POWER)改變對薄膜長速和PL 強度的影響,因為當偏壓太大導致蝕刻太強,會傷害到沈積時的表面 自由基或鍵結力較弱的氫鍵,實驗參數在表2-3-5所示,氣相沈積為 沈積與蝕刻同時存在競爭的製程,可以看到在直流偏壓上升時沈積速 度上升越來越慢,象徵蝕刻效果開始大於沈積,而觀察圖2-3-10室溫 PL圖,亦可發現到樣品在直流偏壓30W時其PL強度最弱,當然這必須 忽略厚度造成的影響,一般樣品在厚度越厚的情況下其PL強度會越 強,如果以單位厚度除光強度來看,直流偏壓30W時其PL強度最弱, 如發光源為缺陷造成,因為此時蝕刻效果小於沈積,氫鍵含量較多可 能幫助缺陷鈍化的原因,使出光下降。 300 400 500 600 700 800 0 1000 2000 3000 4000 5000 6000 7000 PL intensity Wavelength Bias=10W 1114nm Bias=30W 1292nm Bias=100W 1409nm 圖2-3-9 量子點於薄膜內造成多重干擾示意圖 圖2-3-10 表2-3-5變基板直流偏壓功率室溫PL圖

接著察看感應式耦合電漿功率(ICP POWER)改變對薄膜長速的影 響,由文獻回顧已知,低長速對於奈米微晶的成長環境非常重要,如 長速太快會導致矽原子來不及移動就被覆蓋住而來不及結晶,實驗參 數在表2-3-6所示,雖然溫度有差異,但已由前面實驗得知,此等級 溫度對薄膜長速影響不大,觀看ICP power發現從70W降低到25W讓薄 膜長速大量降低三分之一以上,長速已達到小於10nm/min,另一個影 響長速的參數是氣體操作壓力,詳述於參考2-4-2節,其長速最高值 在15mtorr,因此我們操作在遠大於15mtorr來幫助降低長速。 SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 25 475 50 50:10 300 300 1800 1.9994& 11146 (x) 25 475 50 50:30 300 300 1800 1.9594& 12925 (x) 25 475 50 50:100 300 300 1800 2.03& 14096 (x) SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 10 190 20 70:10 300 100 1800 1.56& 3151 (x) 10 190 20 25:10 350 120 1800 1.65& 1944 (x) 表2-3-5 變基板直流偏壓功率實驗參數 表2-3-6 變感應式耦合電漿功率實驗參數

最後將ICP power降低以大量降低長速,並且利用調變矽烷流量 來嘗試有無奈米微晶的產生,實驗參數為表2-3-7,隨矽烷流量變化, 薄膜折射係數變化非常大,拿表2-3-7和表2-3-6第一個參數比較,ICP power不同卻使得折射係數差異很大,主要原因在於矽烷的解離能比 氨氣小很多,所以同樣流量比例下,ICP power較低會讓矽烷解離比 例上升較大,折射係數較高,文獻上以PECVD成長內含矽量子點的氮 化矽薄膜其矽烷比氨氣流量大約是1:2~1:10,但我們HDPCVD卻得往增 加矽烷流量方向走即是矽烷的解離能比氨氣小很多的原因,圖2-3-10 為室溫PL量測圖,當矽烷流量上升其強度削弱許多,而相對其他位置 強度上升,有紅移現象,可能為量子侷限訊號,因為矽烷流量的增加 會導致奈米微晶的尺寸上升,使得量子侷限能階差下降,因為矽烷流 量40sccm樣品其訊號有兩包截然不同的表現,分成2方式來討論,以 峰值400初來討論的話,其位置剛好有一相對的氮缺陷發光能階,如 圖2-3-11所示[66],可以解釋為量子侷限訊號受到空間限制,當奈米 微晶超過其波爾半徑的4倍時,量子侷限不具意義,太小容易被缺陷 能階所取代,當奈米微晶過大亦會使得密度下降或者可能導致彼此結 合而使得PL強度降低許多,以上猜測解釋40sccm兩種訊號的可能性。 SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 10 190 20 15:10 300 140 900 1.78&460 20 190 20 15:10 300 140 900 2.17&480 30 190 20 15:10 300 140 900 2.36&690 40 190 20 15:10 300 140 900 2.61&980 表2-3-7 變矽烷流量實驗參數

此外我們也嘗試了另外一組變氣體流量參數的實驗,差別在於成長時 間更久使得膜厚更厚,主要是我們嘗試了熱退火來幫助降低缺陷的發 光強度以及幫助量子點結晶,實驗參數如表2-3-8, SiH4 (sccm) N2 NH3 ICP:Bias Power (W) Temparature (℃) Pressure (mtorr) Deposition Time(sec) N& Thickness (Å) 20 190 20 15:10 300 140 5400 2.29& 2460 25 190 20 15:10 300 140 4500 2.47& 2250 30 190 20 15:10 300 140 3900 2.46& 2604 35 190 20 15:10 300 140 3300 2.65& 2193 40 190 20 15:10 300 140 2400 2.58& 1905