低壓降線性穩壓電路的靜電放電防護應用

全文

(2) 低壓降線性穩壓電路的靜電放電防護應用 ESD Impacts on Low Dropout Voltage Circuit. 研 究 生:李宗隆. Student:Zon-Lon Lee. 指導教授:陳科宏. Advisor:Ke-Hong Chen. 戴亞翔. Advisor:Ya-Hsiang Tai. 國 立 交 通 大 學 電機學院光電顯示科技產業研發碩士班 碩 士 論 文. A Thesis Submitted to College of Electrical and Computer Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Master in Industrial Technology R & D Master Program on Photonics and Display Technologies June 2008 Hsinchu, Taiwan, Republic of China. 中華民國九十七年一月.

(3) 低壓降線性穩壓電路的靜電放電防護應用. 學生: 李宗隆. 指導教授:陳科宏 戴亞翔. 國立交通大學電機學院產業研發碩士班. 摘. 要. 本篇論文詳細討論了利用低壓降線性穩壓器,來實現靜電放電防護應用,文章內容 主要可以分成二個部分。第一部分是探討低壓降線性穩壓器。隨著可攜式電子產品的快 速發展,例如:手機、數位照相機等等;電源管理已經變得越來越重要與關鍵,並且朝 著減少功率消耗發展。低壓降穩壓器大量的用在電源管理上,因為相較於切換式的穩壓 器有著較好的暫態響應、較小的雜訊與較少的外接元件。 穩定度一直是在設計低壓降線性穩壓器的過程中一個重要的議題。在傳統的電路架 構中,負載電流大小以及輸出電容值為兩項主要影響穩定度的因素。因此,到目前為止 已有許多補償的方法被提出來改善整體的效能。就應用的方面來說大致分為輸出電容外 接和內建兩類,利用電容外接的方式可增加輸出電容的容值並產生一個主極點維持穩 定,主要應用在系統較大對於面積較不注重的產品如電視。另一類的低壓降線性穩壓器 的輸出電容靠著米勒效應使得電容值小且可整合在晶片當中,省下不少面積因此適合應 用在可攜式電子產品裡作為穩定的直流電壓源。 第二部分探討靜電放電防護應用。功率電晶體雖然被設計應用於高電壓、大電流的 偏壓條件,但對於動輒上千伏特的靜電放電電壓、數安培的靜電放電電流而言,功率電 晶體仍嫌脆弱,所以為了確保功率電晶體等高功率元件的可靠度,靜電放電保護電路設 計是當務之急。 當積體電路製成的精密度,越來越細緻,積體電路的可靠性工程,一直有著非常重 要的地位,在設計、製程、技術的改善,均可提高積體電路的可靠度,在良率提升之後, 還有其他影響可靠性工程的因素,ESD 的破壞是其中之一項,而遭 ESD 的破壞是可避免 的,學術上已有許多的 ESD 保護電路的產生。本論文將以保護電路的元件做 ESD 電擊測 試,分析其抗 ESD 能力。. i.

(4) ESD Impacts on Low Dropout Voltage Circuit. student:Zon-Lon Lee. Advisors:Dr. Ke-Hong Chen Dr. Ya-Hsiang Tai. Industrial Technology R & D Master Program of Electrical and Computer Engineering College National Chiao Tung University Abstract The thesis proposes a low-dropout (LDO) regulator with ESD Impacts. Thus, the content of this thesis contains two parts. The first part discusses the design of a low-dropout regulator. With the exponentially increasing of portable battery-powered electronic equipments, such as mobile phones, digital cameras and so on, power management has becoming more and more important and popular. The design of low dropout regulators is widely used in power management since it has a better load transient response, less output noise, and few off-chip components compared to the design of switch-mode regulators. Stability is an important issue in the design of LDO linear regulators. In the conventional architecture, the key factors affecting the system stability are the wide load current range and the value of the output capacitor. Therefore, there exist many proposed compensation techniques to stabilize and improve the whole system. According to the type of output capacitor, LDO regulators can be simply classified into two groups: LDOs with off-chip or on-chip output capacitor. These LDO linear regulators with off-chip capacitor need a large capacitance at output node to generate a dominant pole at low frequency to achieve the stability. They are mostly used for supplying the system with the characteristic of low quiescent current at light loads owing to the current efficient buffer used in the LDOs. The other LDO regulators use an on-chip small output capacitor based on the Miller-compensated technique. Thus, the capacitor can be integrated into the chip, which has the advantage of the saving the footprint area. This type of capacitor-free LDOs is well suited as a stable dc voltage supply for portable electronic devices. The second part of this thesis discusses how ESD impacts the low-dropout regulators. In some situation, the latent damage of electrostatic discharge in a power MOSFET can't easily find out immediately. Eventually, in order to make sure a good reliability and long lifetime of power MOSFETs, the ESD protection circuit design is needed to prevent ESD damages in a power MOSFET design. This thesis provides the reliability engineers of integrated circuit a most important concept of ESD design of power IC. The improvement of the ESD will enhance the reliability of integrated circuit in power IC designs. ii.

(5) 誌. 謝. 首先要感謝指導教授陳科宏老師的教導,讓我感受到追求學問與思考問題的樂趣, 老師總是要我們跳脫傳統思維來面對問題,才能有新的突破,真的很感謝您。同時由衷 的感謝口試委員,王清松教授及黃立人博士對本論文費心地提供寶貴的意見與指正,使 本論文更加完善。 感謝紹璋學長在學期間,利用晚上時間撥空指導,研究專業與待人處世讓筆者學習 生涯獲益匪淺。 在研究所期間,難免遭遇到種種挫折和困難,感謝實驗室心欣學姊、宗隆、柏逢在 實驗室的照顧以及 703、701、802 實驗室同學給予的幫助,大家互相鼓勵,一起伴我度 過一段美好的日子,在這裡由衷的感謝大家。 最後要感謝我的父母及女友馨玉,感謝你們多年來的關懷與支持,並在背後支持著 我,讓我得以在求學期間專心唸書無後顧之憂,我心中也是充滿無限感激這一路上所有 幫助過我的人,謹將此論文獻給我家人。. iii.

(6) 目. 摘. 錄. 要...................................................................................................................1. Abstract..............................................................................................................................ii 誌. 謝..................................................................................................................iii. 目. 錄..................................................................................................................iv. 圖 目 錄.........................................................................................................................vii 表 目 錄..........................................................................................................................ix 第一章 概論.....................................................................................................................1 1.1 研究背景..............................................................................................................1 1.2 研究動機及目的................................................................................................1 1.3 論文架構.............................................................................................................1 第二章 低壓降線性穩壓器概論與重要特性參數......................................................2 2.1 低壓降線性穩壓器概論 ...................................................................................2 2.2 重要特性參數 ....................................................................................................3 2.2.1 輸出電壓差(Dropout Voltage)................................................................3 2.2.2 線性調節率(Line Regulation) ................................................................4 2.2.3 負載調節率(Load regulation).................................................................6 2.2.4 靜態電流或接地電流(Quiescent current or Ground Current) .............7 2.2.5 功率效率(Efficiency) ..............................................................................8 2.2.6 輸出準確率(Output accuracy)................................................................9 2.2.7 暫態響應(Transient response) ..............................................................12 iv.

(7) 2.2.8 頻率響應(Frequency response) ..........................................................15 第三章. 回授穩定度及頻率補償.............................................................................19. 3.1 等效串聯電阻 ...................................................................................................20 3.2 極零點補償 ......................................................................................................21 3.3 追蹤零點補償 ..................................................................................................23 3.4 米勒頻率補償 ..................................................................................................27 第四章 低壓線性穩壓器設計與模擬.........................................................................32 4.1 Pole Tracking(電阻R2、電晶體MP3) ............................................................32 4.2 模擬結果(TT, SS, FF, FS, SF).........................................................................33 第五章 靜電放電防護設計概念與測試.....................................................................39 5.1 靜電放電防護概論...........................................................................................39 5.2 靜電放電模式 ..................................................................................................39 5.2.1 人體模式(HBM)....................................................................................39 5.2.2 機械模式(MM)......................................................................................41 5.2.3 元件電荷模式(CDM)............................................................................42 5.3 靜電放電放護設計概念 .................................................................................43 5.3.1 靜電放電防護設計................................................................................45 5.4 靜電放電測試及判讀......................................................................................50 5.4.1 靜電放電測試組合................................................................................50 5.4.2 靜電放電防護的測試 ...........................................................................52 第六章 結論...................................................................................................................55 v.

(8) 參考文獻.........................................................................................................................56. vi.

(9) 圖 目 錄 圖 2-1 性穩壓器的基本架構圖..............................................................................................................2 圖 2-2 輸出電壓差...................................................................................................................................3 圖 2-3 線性調節率...................................................................................................................................4 圖 2-4 LDO電路架構.................................................................................................................................5 圖 2-5 靜態電流.......................................................................................................................................7 圖 2-6 輸出電壓誤差...............................................................................................................................9 圖 2-7 誤差放大器電壓偏移................................................................................................................10 圖 2-8 電阻值誤差.................................................................................................................................11 圖 2-9 步階負載.....................................................................................................................................12 圖 2-10 輸出電壓對於負載之變化......................................................................................................13 圖 2-11 交流分析等效模型..................................................................................................................15 圖 2-12 低壓降線性穩壓器的頻率響應.............................................................................................17 圖 2-13 等效串聯電阻過大之情形......................................................................................................17 圖 2-14 等效串聯電阻過小之情形......................................................................................................18 圖 3-1 輸出阻抗示意圖 ........................................................................................................................20 圖 3-2 利用電容前饋產生零點............................................................................................................21 圖 3-3 產生左半平面的零點................................................................................................................22 圖 3-4 極零點補償低壓降線性穩壓器 ...............................................................................................22 圖 3-5 主極點及頻寬隨負載電流之變化...........................................................................................23 圖 3-6 用 NMOS 取代補償電路中的電阻.............................................................................................24 圖 3-7 改變 VDS 時電阻值的變化 ..........................................................................................................25 圖 3-8 追蹤零點補償低壓降線性穩壓器...........................................................................................26 圖 3-9 SMC 兩級放大器示意圖.............................................................................................................27 圖 3-10 SMC 兩級放大器的頻率響應 ..................................................................................................28 圖 3-11 MULTI-STAGE LDO ........................................................................................................................29 圖 3-12 電流持續增加, P1st _ non 和 PPar 的根軌跡.............................................................................30 圖 3-13 P1st _ non 和 PPar 行成 COMPLEX 圖 4-1 圖 4-2 圖 4-3 圖 4-4 圖 4-5 圖 4-6 圖 4-7 圖 4-8. POLES ............................................................................................31. POLE TRACKING的四級放大器LDO主要電路 ...............................................................................32 頻率響應(FOR VDD=5V, ILOAD=200MA, 5 CORNER).......................................................................33 頻率響應(FOR VDD=5V, ILOAD=1MA, 5 CORNER)...........................................................................34 POWER SUPPLY REJECTION RATIO(FOR VDD=5V , ILOAD =200MA, 5CORNER)........................................35 暫態響應(VDD=5V, ILOAD =0.1MA~200MA, 5 CORNER)................................................................35 LINE REGULATION(FOR VDD=0V→5.5V, ILOAD =0.1MA, 5CORNER)..................................................36 LINE REGULATION(FOR VDD=0V→5.5V, ILOAD =200MA, 5CORNER)..................................................37 LOAD REGULATION(FOR ILOAD=0.1MA →200MA, 5 CORNER)...............................................................37 vii.

(10) 圖 5-1 典型的人體模式靜電放電等效電路.......................................................................................40 圖 5-2 典型的機械模式靜電放電等效電路.......................................................................................41 圖 5-3 元件電荷模式的電流波形........................................................................................................42 圖 5-4 WHOLE-CHIP 靜電放電防護電路.................................................................................................43 圖 5-5 異常靜電放電損傷積體電路內部的原因示意圖..................................................................44 圖 5-6 典型的輸入電路 ........................................................................................................................46 圖 5-7 (A)N 型金氧半導體的剖面圖,包含旁路電晶體 NPN。(B)0.13ΜM 製程下,高電流的電 流對電壓曲線圖,包含 LNPN 打開電壓(VAV)、突然跳回的操作電壓(VSP)與熱能導致的第 二次崩潰電流(IT2)。...................................................................................................................47 圖 5-8 典型的輸出電路 ........................................................................................................................48 圖 5-9 典型的二極體電路 ....................................................................................................................49 圖 5-10 ESD 測試的幾種模式...............................................................................................................52 圖 6-1 使用 POLE TRACKING 改良 MULTI-STAGE 震盪..............................................................................55. viii.

(11) 表 目 錄 表 1-1 壓器分類.......................................................................................................................................1 表 4-1 模擬數據.....................................................................................................................................38. ix.

(12) 第一章 概論. 1.1 研究背景 隨著可攜式電子產品的發展與盛行,低功率與高效率成為可攜式電子 產品的首要考量,因此這些利用電池提供電源的電子電路必須工作在低電 壓與低電流以減少功率消耗,使得電池得以延長工作時間。因此,有效率 的電源管理已成為電子電路設計的重要因素之一。電源效率可在三個設計 領域加以處理:首先是電池管理,它必須能將電池充飽,長期保持所儲存 的電力,並在重新充電之前供應最多電力;其次是系統功率消耗零件的主 動管理,例如處理器和周邊,它們的功率消耗可以根據系統效能需求進行 管理;第三則是電源轉換程序,它必須能將不斷變動的電池電壓轉換成系 統所需的多個固定電壓。為了節省功率消耗,穩壓器常被用來降低工作電 壓,將較高的輸入電壓轉換為較低的電壓以供其他的電路使用。電壓轉換 的方式大致分為切換式與線性穩壓器兩種,如表(1-1)。 儲能元件 線性穩壓器. 切換式穩壓器. 電感. 穩壓電路. 優點. LDO. z z. Buck Boost. z. z z 電容. Charge Pump z. z. 結構簡單 z 低雜訊與 z 輸出電壓 漣波 三種轉換 z 形式: z 升、降、 負壓 z 易達成多 重輸出 較高的轉 換率 三種轉換 z 形式: 升、降、 z 負壓 較LDO高 的轉換率. 表 1-1: 壓器分類。. 1. 缺點. 應用. 僅有降壓 轉換率不高. 類比、射頻或 電流較小的 電路. 面積大 需外接電感元 件 有較大雜訊與 輸出電壓漣波. 數位電路或 其它電流需 求較大的電 路. 雜訊大且具有 電流需求小 輸出電壓漣波 的電路 易發出電磁干 擾.

(13) 由上圖(1-1)可知,線性穩壓器中又以低壓降線性穩壓器(LDO)在可 攜式電子產品蓬勃發展的今日更顯重要,其優點在於輸出電壓對輸入電壓 或負載的變化反應較為迅速、輸出電壓的漣波與雜訊較低、電路結構較簡 單、體積較小、價格較為低廉,且近年來更因為其轉換效率的提升,成為 小功率降壓與穩壓電路的主流。在各式由電池供應的電子產品如手機、數 位相機…等,由於是利用內部電池來維持運作,因此電源的功率消耗部份 更是格外受到重視,這些產品需要低功率消耗、高操作效率,能讓電池壽 命延長,低壓降線性穩壓器在這些產品之中被大量地使用。. 1.2 研究動機及目的 低壓降線性穩壓器為電源管理系統一不可或缺的元件,在較低電壓、 較小功率的電壓轉換場合,低壓降線性穩壓器是相當經濟的選擇。而低壓 降線性穩壓器根據應用場合的需要,也分成許多不同種類:針對低輸出雜 訊、高速暫態響應、低靜態電流、大輸出電流等不同的需求,均要作電路 架構上的修改,方能達到理想的特性。 本論文針對低壓降線性穩壓器,操作在不同負載電流下,其穩定度的 問題加以研究,為了能夠在負載電流改變時,維持良好的暫態響應以及頻 率響應,達到輸出電壓迅速穩定的功用,將在論文中提出低壓降線性穩壓 器的頻率補償方式。 除了主要頻率補償電路架構,積體電路的可靠性工程,一直有著非常 重要的地位,在設計、製程、技術的改善,均可提高積體電路的可靠度, 在良率提升之後,還有其他影響可靠性工程的因素,ESD的破壞是其中之一 項,而遭ESD的破壞是可避免的,為了增加晶片之靜電放電防護本論文將以 保護電路的元件做ESD電擊測試,分析其抗ESD能力。. 1.3 論文架構 論文共分6章,首先第一章介紹研究背景、研究動機及目的。第二章, 針對低壓降線性穩壓器特項特性做詳細說明。第三章,則是本論文所使用 的頻率補償技術。第四章,低電壓線性穩壓器設計與模擬結果。第五章則 是靜電放電防護設計與測試。最後一章,再對本論文所採用之低壓降線性 穩壓電路的靜電放電防護應用作一個總結,並提出未來研究之方向。. 1.

(14) 第二章 低壓降線性穩壓器概論與重要特性參數. 2.1 低壓降線性穩壓器概論 線性穩壓器的基本架構圖如圖2-1所示[1],大略上可分成四個部份: 參考電壓源(Vref)、誤差放大器(Error Amplifier)、兩個分壓電阻(Rfb1、Rfb2) 所組成的回授網路以及輸出功率電晶體(Pass Transistor)。其中的參考電 壓源目的在於提供一個不隨外外部環境變化如工作電壓[2]、溫度及半導體 製程而改變的固定電壓VREF,而分壓電阻則是用來觀測輸出電壓,並提供 一個和輸出電壓成正比的VFB來供比對,其工作原理是將誤差放大器的兩個 輸入端,分別接到參考電壓源與回授網路,則誤差放大器便會隨著參考電 壓與回授電壓之間的差,來調整功率電晶體閘極端的電壓,進而控制輸出 端的電流以產生穩定的輸出電壓值;回授電壓大於參考電壓時,誤差放大 器就會控制功率電晶體,使其輸出電流減小以降低輸出電壓,反之亦然。 如此一來,輸出電壓就可以被控制在一個準確的值,無論輸入供應電壓或 輸出負载電流有任何變化,輸出電壓都可在很短的時間內拉回至一個固定 的位準。輸出的電壓值[3]可表示如式(2.1): ⎛ R fb1 ⎞ ⎟ Vout = Vref ⎜1 + ⎜ ⎟ R fb 2 ⎠ ⎝ Vin. (2.1)式 Vout. Pass Transistor Rfb1. RESR. Error Amplifier VFB. Vref. Rfb2. CL. 圖 2-1: 性穩壓器的基本架構圖。. 2. RL.

(15) 2.2 重要特性參數 2.2.1 輸出電壓差(Dropout Voltage) 輸出電壓差在線性穩壓器中是一個非常重要的參數,而其定義為: 當輸入電壓(電壓源)降到某個程度時,其輸出電壓將不再穩壓在預計 的輸出電壓,而在臨界點時的輸入電壓與輸出電壓的差值即為壓降電 壓。以圖 2-2 為例,其輸出電壓差為 3.3V-2.5V=800mV。簡單來說就 是輸出功率電晶體的汲極和源極的壓差,直接關係到的就是電源功率的 消耗,越大的跨壓所損失的功率就越大,所以說,輸出電壓差是越小越 好。 Vout. 2.5V. Cut-Off Region. Dropout Region. Regulation Region. 3.3V. Vin. 圖 2-2: 輸出電壓差。 對輸出PMOS 電晶體而言,其汲極是連接到輸出端,因此當輸入端 (源極)電壓很小時,電晶體是關閉狀態,當源極電壓加大後,電晶體 開啟,輸出端電壓開始爬升,一直到穩定的設定值之間的這段輸入電壓 差,即是輸出電壓差。其實對於輸出電晶體來說,就是它的飽和電壓差 (VSD-sat),當MOS 電晶體大小確定,且閘極電壓固定之後,其飽和電壓差 基本上就不會改變,所以提供閘極電壓的前一級放大器,和輸出電晶體 的大小在設計上都要能達到理想的輸出電壓差。. 3.

(16) 對於電源功率消耗的部份,將電晶體飽和電壓(VSD-sat)差乘上輸出 端所流過的電流,即是消耗功率如式(2.2)。 P = Iout ×VSD-sat (2.2)式 對於一個可攜帶式電子產品來說,都是由電池來提供電源,這部份 的電源消耗當然是越小越好,以求電池壽命能夠長久,低壓降線性穩壓 器能夠如此受歡迎的原因,就是在這方面能夠節省很多的電力。. 2.2.2 線性調節率(Line Regulation)[4] 這項參數在線性穩壓器中也是非常重要的,指的是當輸入電壓產生 變化時,相對於輸出端電壓的改變如式(2.3)。 Line Regulation =. ΔVout ΔVin. (2.3)式. 我們預期當輸入電壓改變時,輸出電壓能一直維持穩定,但是實際 上是有小幅改變,通常以百分比(%)表示,如圖(2-3)所示。 Vout 輸出電壓變化. Regulation Region. Vin. 圖 2-3: 線性調節率。. 4.

(17) 如圖(2-4)所示,分析電路可得: Vin Gm. Vref AEA. MP Vout. Rfb1 Vfb. Rout. Rfb2. 圖 2-4: LDO 電路架構。 ΔVout =. Rout Vin − Vout Rds + Rout. ΔVout = ΔI out × Rout Vout = Vf b =. Vout. Rout × Vin − Gm (V fb − Vref )Rout Rds + Rout R fb 2 R fb1 + R fb 2. Vout. Rout (R fb1 + R fb 2 ) Vin + (R fb1 + R fb 2 )GmVref Rout Rds + Rout = R fb1 + R fb 2 + Gm R fb 2 Rout ≅. R fb1 + R fb 2 Gm R fb 2. Vin +. R fb1 + R fb 2 R fb 2. Vref. R fb1 + R fb 2 ΔVout 1 = × ΔVin Rds + Rout Gm R fb 2. (2.4)式. 最後可以得到如上式(2.4)新的線性調節率(Line Regulation),其 中Rds為傳輸電晶體(MP)的等效電阻,Rout為負载電阻,Gm是Error Amplifier的Gain與傳輸電晶體(MP)轉導(gmp)的乘積。 由於輸入電壓改變時,會造成回授電壓的改變,再由誤差放大器加 以調節輸出電晶體(PMOS),來控制輸出電壓,因此若增加整個電路的 開迴路增益,對於線性調節率的提升有很大的幫助。. 5.

(18) 2.2.3 負載調節率(Load regulation)[5] 相對於線性調節率,線性穩壓器另ㄧ個主要考量就是負載調節率, 表示當負載端有變化,也就是輸出電流有改變時,輸出電壓的變化率如 式(2.5)。 Load Regulation =. ΔVout ΔI out. (2.5)式. 當負載有變化時,輸出電壓會跟著改變,再藉由回授網路讓誤差放 大器對於電壓變化作反應,控制輸出電晶體,輸出電流也會隨之改變來 應整個電壓的變化。如圖(2-4)所示, ΔI out = Gm ΔV fb = Gm. ⇒. R fb 2 R fb1 + R fb 2. × ΔVout. ΔVout R fb1 + R fb 2 1 = × ΔI out R fb 2 Gm. (2.6)式. 由式子(2.6)可以看出,負載的改變造成電壓的變化,經誤差放大 器放大之後,輸出電流也跟著做變化。明顯的,最後的式子可以得知, 負載調節率被線性穩壓器的轉導(Gm,也就是誤差放大器的增益乘上輸 出電晶體的電流增益)所限制,所以要改善負載調節率,可以增加DC的 電流增益,可以得到不錯的效果。. 6.

(19) 2.2.4 靜態電流或接地電流(Quiescent current or Ground Current) 接地電流又稱為偏壓電流(Quiescent current),就是輸入電流與輸出 電流的差值如式(2.5)及圖(2-5),關係到整體的電流效率。 Iq = Iin −. Iout. (2.5)式. Vin. Iin. OUT. IN. Iout. Vout. GND. Iq. 圖 2-5: 靜態電流。 ㄧ般而言,靜態電流包括了電路中的偏壓電流(如:誤差放大器、 參考電壓源)和驅動輸出電晶體的電流,這些對於輸出效率並無幫助, 造成無謂的消耗電源,因此在設計上是越小越好。 ㄧ個以雙載子電晶體做為輸出端的線性穩壓器,天生就存在有蠻 大的靜態電流,也就是基極電流,且基極電流是正比於輸出電流,因此 它的靜態電流是會隨輸出電流增加而變更大。在低壓降線性穩壓器中, 是使用MOS電晶體來當作輸出電晶體,MOS電晶體是用VGS來控制電 流,而其閘極並無電流通過,因此其靜態電流可以保持固定,且無視於 負載端的變化,這也是用MOS當輸出端優於雙載子電晶體的好處之一 [6]。. 7.

(20) 2.2.5 功率效率(Efficiency) 低壓降線性穩壓器的效率,定義為輸出功率和輸入功率的比值如 式(2.6): Efficiency = =. I out × Vout I in × Vin I out × Vout (I q + I out )×Vin. (2.6)式. 由上式(2.6)可以看出,靜態電流(Iq)和輸出、輸入電壓,也是影 響效率的因素之一,在輕載時,為了改善功率效率,必須降低靜態電 流。 當Iq很小,小到可以忽略時如式(2.7), Efficiency ≅ =. I out × Vout I out × Vin Vout. (2.7)式. Vout + (Vin − Vout ). (2.8)式. 由上式(2.7)可知,當Iout很大時,功率效率值大約等於一。 由上式(2.8)可知,當Iq很小,小到可以忽略的時候,明顯的效率是 由輸入電壓和輸出電壓的差值決定,由此可知,為了增加功率效率,降 低靜態電流及減少輸出電壓差(Dropout Voltage)。. 8.

(21) 2.2.6 輸出準確率(Output accuracy) 輸出電壓的準確度如式(2.9)和低壓降線性穩壓器的各個部份的電 壓誤差關係密切,像是:線性調節率(ΔVLR)、負載調節率(ΔVLDR)、參 考電壓偏移(ΔVo,REF)、誤差放大器電壓偏移(ΔVo,EA)、外部回授電阻的 誤差(ΔVo,res)、溫度係數(ΔVTC)…等,如圖(2-6)。. ? VLR. ? Vref ? VEA REF Error Amp. ? VLDR. Pass Element. Rfb1+? Rfb1. ? Vout ? VTC. Rfb2+? Rfb2. 圖 2-6: 輸出電壓誤差。. Accuarcy ≈. ΔVLR + ΔVLDR + ΔVo2,ref + ΔVo2,EA + ΔVo2,res + ΔVTC2 Vo. × 100%. (2.9)式. 輸出電壓誤差主要是由環境溫度改變所造成的參考電壓偏移、誤差 放大器的特性改變(增益誤差、偏移電流)、電阻值誤差,這些誤差加上 線性調節率和負載調節率通常會使得精確度改變1%~3%。另外,製程上 的變異也同樣會造成上述各部份產生誤差。 接下來仔細討論各部份造成的誤差,就參考電壓源的部份,和輸出 電壓的關係式: ⎛ R ⎞ Vout + ΔVo , ref = ⎜1 + fb1 ⎟ × (Vref + ΔVref ) ⎜ R ⎟ fb 2 ⎠ ⎝. 9.

(22) ⎛ R fb1 ⎞ ⎟ ×V ΔVo ,ref = ⎜1 + ⎜ R ⎟ ref fb 2 ⎠ ⎝. (2.10)式. 從上述式(2.10)可以得到,參考電壓的誤差會直接影響到輸出電 壓,而且是直接正比於誤差百分比。 再來是關於誤差放大器的誤差部分,如圖(2-7): gmp. Vin. Vo±∆Vo,EA Rfb1 RL. AEA Vref. Rfb2. 圖 2-7: 誤差放大器電壓偏移[5]。 ΔV fb =. R fb 2 R fb1 + R fb 2. ΔVo , EA. ΔVo, EA = g mp ΔVEA RL + AEA g mp ΔV fb RL. 考慮 AEAgmp>>1,將上兩式合併的結果: ΔVo ,EA =. ΔVEA (R fb1 + R fb 2 ) g mp R fb 2. 10.

(23) 最後是電阻的誤差部分,如圖(2-8): gmp. Vin. Vo±∆Vo,R Rfb1±∆Rfb1 RL. AEA Rfb2±∆Rfb2 Vref. 圖 2-8: 電阻值誤差[5]。. Vo + ΔVo , R =. ⇒ ΔVo, R =. R fb1 + ΔR fb1 + R fb 2 + ΔR fb 2 R fb 2 + ΔR fb 2. ΔR fb1 + ΔR fb 2 R fb 2 + ΔR fb 2. Vref. (2.11)式. Vref. 關係式如(2.11)式,顯然的,電阻誤差影響輸出電壓相對於前面幾 項來得比較小,且Rfb2的影響要比Rfb1還要大。. 11.

(24) 2.2.7 暫態響應(Transient response) 主要是當負載電流在瞬間改變時,如圖(2-9),輸出電壓變化的情 況以及電壓回穩的時間。影響到暫態響應的包括:穩壓器的頻寬、輸出 電容(Cout)、輸出電容的等效串聯電阻(Resr)、最大負載電流…等。 Vin. Vout. Pass Transistor Rfb1. Resr. Error Amplifier. Load Current. VFB. Vref. Rfb2. Cout. RL. 圖 2-9: 步階負載。 接下來分成幾個部分來分析當負載改變時,輸出電壓的變化。首先 以一個步階負載應用,觀察相對的輸出電壓反應,當負載端忽然從穩壓 器抽取大量電流,此時由於穩壓器頻寬的關係,反應不及造成無法及時 提供負載端足夠的電流,輸出電壓就如圖(2-10)中T1時間內的反應, 產生一段不小的壓降(Vdip),這段時間內由輸出電容暫時提供負載所需 的大量電流,由Cout流向VOUT。 這段壓降我們可以經由計算得到如式(2.12): Vdrop =. I out × T 1 + ΔVesr Cout. (2.12)式. 12.

(25) T3 T2 T1 Vpeak Output Voltage. Load Regulatoion. Vdrop T4 IL( MAX) Load Current. IL( MIN) Time. 圖 2-10: 輸出電壓對於負載之變化。 T1這段時間主要受限於低壓降線性穩壓器的頻寬和變化率(slew rate),一個頻寬大反應快的低壓降線性穩壓器自然可縮短這段時間, 此外夠大的輸出電容,足以用來提供時負載電流,才能保持輸出電壓, 減少瞬間的壓降。接下來,當過了T1這段時間後,回授網路感測到電壓 變化,並加以做穩定的工作,也就是T1時間內的反應,其中的穩定值和 原來零負載時的輸出電壓有一段差距ΔVout ,就是之前提到的負載調節 率。 T2 長短即輸出電晶體對輸出電容充電所需時間,和整個電路必迴 路的相位邊限也有關係。 相對於上面的情況,現在考慮將加在輸出端的負載抽離,輸出電 壓的反應剛好和之前相反, T3時間內產生一段不小的電壓脈衝,其值 可以經由計算得到如式(2.13): V peak =. I out × T 3 + ΔVesr Cout. (2.13)式. 同樣地,脈衝過後電壓回穩,不過此時輸出端電流為0,故必須透 過回授電阻放電,放電電流固定由圖中T4斜率可知。. 13.

(26) 總之,想要有良好的暫態響應,必須提升低壓降線性穩壓器的頻 寬,並增加其變化率(slew rate),或降低等效串聯電阻值,諸如:瞬 時壓降、穩定時間、順時脈衝⋯ 等暫態現象,都可以獲得改善。. 14.

(27) 2.2.8. 頻率響應(Frequency response). 為了分析低壓降線性穩壓器的頻率響應,將其迴路打斷後顯示如 下圖(2-11):. VS. Error Amplifier. Pass Element. VOUT Rfb1. Cpar. Vfb. RPass. Rpar. Resr. Rfb2. Cb. ROUT. COUT. 圖 2-11: 交流分析等效模型[7]。 其中RPass是輸出電晶體的輸出阻抗,Cb則是估計下一級電路的輸入 電容,通常Cb遠小於Cout,進一步計算其轉換函數: T (s ) =. ⎛ 1 = Gm ,Amp G m,Pass ⎜ R par // ⎜ Vs sC par ⎝. V fb. ⎞ Rfb2 ⎟ Z OUT ⎟ R fb1 + R fb2 ⎠ ⎛. 其中輸出阻抗: Z OUT = R Pass // (R 1 + R 2 )//R OUT // ⎜⎜ R esr + ⎝. 1 sC OUT. ⎞ 1 ⎟⎟ // ⎠ sC b. 由上式,可以得知整個迴路中存在 3 個極點以及一個零點,這對於 低壓降線性穩壓器的穩定度來說,是非常重要的訊息。 首先,第一個極點,也就是主極點,是由輸出電容以及低壓降線性穩壓 器的輸出阻抗所形成: f P1 =. 1. 2π (ROUT // RPass + Resr )COUT. 15.

(28) 因為等效串聯電阻通常遠小於輸出阻抗,故可做此近似。第二個極 點,是由誤差放大器到輸出電晶體之間的寄生電容和電阻所形成: f P2 =. 1 2πR par C par. 第三個極點,是由輸出電容的等效串聯電阻以及Cb所形成: f P3 =. 1 2πResr Cb. 而唯一的零點,是由輸出電容以及其等效串聯電阻所形成: fZ =. 1 2πResr COUT. 至於,極點和零點的位置,就看實際上的電路如何設計了,和誤差 放大器及輸出電容大小,都有關係。不過就常理來說,主極點是確定小 於其他極點,因此fP1<fP2<fP3這個關係是確定的。因此,為了讓整個電路 達到良好的穩定度,接下來的極點和零點位置的分布,就顯的很重要。 一般作法是用零點來消除其中一個極點的影響,將零點位置控制在單增 益頻率(fT)附近,可有效提昇電路的相位邊限,進而使穩定度更高。 因為系統穩定度的考量,低壓降線性穩壓器的各項效能如:線性調 節率、負載調節率、穩態精確度及負載暫態響應都受到了限制。線性調 節率、負載調節率與精確度的限制,是因為開迴路直流增益由於穩定度 的限制而無法提高造成。一般而言,若有要最佳的線性調節率和負載調 節率與精確度,需提昇開迴路直流增益,但無限制地提高開迴路直流增 益,則會造成相位邊限不足。 由上面所述,一個沒有補償的低壓降線性穩壓器,會因為兩個極點 的效果,使得相位在單增益頻率時變為-180°,整個電路也會因此而震 盪,故由等效串聯電阻所形成的零點,對於一個低壓降線性穩壓器而言 十分重要,以下對於這個等效串聯電阻加以討論:. 16.

(29) Gain(dB). P1 P2 Zesr fP3. 0. fP1. fP2 fZ. ft. Frequency. P3. 圖 2-12: 低壓降線性穩壓器的頻率響應。 等效串聯電阻的值關係到的就是零點的位置,太大或者太小對於電 路的穩定度都有影響[8],先看等效串聯電阻太大的情形,如圖(2-13) 所示,造成零點位置過小,使得原本在單增益頻率之下的第三個極點也 跑到前面,又拉低了相位邊限,導致電路不穩定。 再看等效串聯電阻太小的情形,如圖(2-14)導致零點位置低於單增 益頻率,致使相位邊限並沒有獲得提升,原本要對電路作補償的效果就 消失了。 Gain(dB). P1 P2 Zesr. 0. P3 fP1. fP2 fZ. fP3. 圖 2-13: 等效串聯電阻過大之情形。. 17. Frequency.

(30) Gain(dB). P1 P2. 0. fP1. fP2. fZ. fP3. Zesr. P3. Frequency. 圖 2-14: 等效串聯電阻過小之情形。 總而言之,等效串聯電阻的值有一個適合的範圍,在這範圍內都可 以使低壓降線性穩壓器更加穩定。因此輸出電容的選取,也顯得重要許 多,ㄧ般認為鉭質電容是最佳選擇,4.7μ的電容值在25℃時其等效串 聯電阻值約1.3Ω。其它如大於1μF的陶瓷電容,由於其等效串聯電阻 值非常小,約20mΩ左右,易使得電路震盪,所以如果要選用這類電容, 常常需要再外掛小電阻和其串聯,增加其等效串聯電阻值[9]。. 18.

(31) 第三章 回授穩定度及頻率補償. 低壓降線性穩壓器為一負回授系統,因此有穩定度的問題。若系統的 開迴路轉移函數沒有足夠的相位邊限,輸出便會發生振盪。要確保系統穩 定,必須維持足夠的相位邊界。但是,低壓降線性穩壓器之開迴路直流增 益與主極點的頻率,均會隨著負載不同而變動,進而造成單增益頻率、相 位邊限的改變。因此,要在各種負載下均能保持系統的穩定,其輸出電容 與等效串聯電阻均需嚴格地限制。通常低壓降線性穩壓器的使用說明上, 均會列出建議使用的輸出電容值及其等效串聯電阻的範圍。而且之前提 過,穩定度關係到低壓降線性穩壓器的各項效能,若要有最佳的電源和負 載調節率與輸出精確度,需提昇開迴路直流增益,但是容易造成相位邊限 不足。負載響應則是受限於輸出電容之等效串聯電阻以及單增益頻率的限 制。當負載瞬間發生ΔI 的變動時,因為系統無法即時反應,此ΔI 的電流 均由輸出電容提供,而輸出電容之等效串聯電阻與負載變化,會造成輸出 電壓有瞬間壓降。輸出電壓的穩定時間則與單位增益頻率成反比,單位增 益頻率越高,表示頻寬越大,反應的時間越短,也就能越快達到穩定。因 此輸出電容之等效串聯電阻越小、單位增益頻率越高,負載響應便越優異。 但是因為穩定度的考量,輸出電容之等效串聯電阻無法為零,單位增益頻 率也無法提昇至十分高頻。 由以上的討論可知,低壓降線性穩壓器主要缺點是輸出電容與其等效 串聯電阻受到限制。由於等效串聯電阻會隨著溫度、頻率等因素而變動, 又要配合適當的電容值,令低壓降線性穩壓器在使用上不甚方便,且等效 串聯電阻的存在亦會影響負載響應的效能。此外由於開迴路直流增益不能 太高,無法有效地提昇電源和負載調節率與輸出穩態精確度之效能。所以 目前在低壓降線性穩壓器的設計上,無非是希望降低或去除輸出電容與其 等效串聯電阻的限制,或是有效提昇開迴路直流增益。. 19.

(32) 3.1 等效串聯電阻 前一章有討論過,利用等效串聯電阻來產生一個零點,對提升相位 邊限有幫助,這一節就說明一下等效串聯電阻如何產生零點,如圖(3-1). ZOUT. Resr ROUT COUT. 圖 3-1: 輸出阻抗示意圖。. Z OUT. ⎛ 1 ⎞ ⎟ ROUT ⎜⎜ Resr + sCOUT ⎟⎠ ROUT (1 + COUT Resr ) 1+ Z ⎝ = = = 1 Resr + + ROUT 1 + sCOUT (Resr + ROUT ) 1 + P sCOUT. 式(3.1). 從上面的式(3.1),可以看出透過等效串電阻,產生了一個零點和 一個極點,其頻率為: fZ =. 1 2π (Resr × COUT ). fP =. 1 2π (Resr × COUT )COUT. 此極點即為低壓降線性穩壓器的主極點,藉由等效串聯電阻多產生 了一個零點,且零點位置可以由等效串聯電阻值的大小來控制,要挑選 到適合的輸出電容,才能配合適當的等效串聯電阻值,達到使電路穩定 的效果[10]。. 20.

(33) 3.2 極零點補償 極零點補償這種方式是目前最常用的補償方法[11],其作法是利用補 償電容的前饋效果(feed forward),來產生零點並用來提升相位邊限。首 先來敘述一下電容的前饋如何產生零點,如圖(3-2)所示。 ICc V1. V2 Cc Ro Io. 圖 3-2: 利用電容前饋產生零點。 考慮一個跨在兩級放大器之間的補償電容,原本 V2 的輸出電壓是由輸 出電流 IO 流過輸出電阻來提供,若是此時電容前饋效果使得通過補償電容 的前饋電流 ICc,剛好等於原本的 IO,即此時 IO 為零,V2 也變成零,也就是 產生了一個零點。換句話說,此種零點產生的方式就是在原本的輸出電流 路徑上,因為加了補償電容,造成另一條路徑可以產生輸出電流,取代了 原本的路徑,讓輸出電壓變成零。但此種方法所產生的零點,有可能在右 半平面,不但對相位沒有幫助,反而是使得相位下降更快,因此就有些方 法來防止產生右半平面的零點,在此不另加贅述。. 21.

(34) 有了上面的觀念,要產生一個零點就很容易了,但是要確保此零點是 位於左半平面,作法如圖(3-3):. V1. V2 Cc. Rc. 圖 3-3: 產生左半平面的零點。 其產生零點的位置為: fZ ≈. 1 2π (Rc × Cc ). 如此一來,調整Rc的值,就可以控制零點的位置來達到提升相位的效 果。實際應用到低壓降電性穩壓器上,就如下圖(3-4)。 VIN. VREF. Power Transistor. Errpr Amplifier. Rc. rPass. VOUT. Cc Compensation. R2. RESR. R1. COUT. 圖 3-4: 極零點補償低壓降線性穩壓器。. 22.

(35) 3.3 追蹤零點補償 根據前一節所述,極零點補償對於低壓降線性穩壓器來說,確實是個 不錯的方法,不過若要使得穩壓壓操作負載範圍更廣,可以更進一步改善 零點產生的方式。仔細觀察的零點位置,可以發現它的位置是固定的,並 不會因為負載改變而變動,而低壓降線性穩壓器有個很重要的特性,就是 它的主極點位置會隨著負載改變[12]。當負載電流小的時後,因為等效輸 出阻抗變大,所以由輸出電容和輸出阻抗形成的主極點位置就會往前,造 成頻寬縮減,容易使電路發生震盪。因此一般低壓降線性穩壓器設計時都 會限制其操作負載範圍,以免產生電路不穩的現象。圖(3-5)顯示了當負載 電流改變時主極點及頻寬的變化。 Gain(dB) 主極點fp1位置變化. IOUT減少. 0dB. 單位增益頻寬(UGF)Frequency(Hz). 圖 3-5: 主極點及頻寬隨負載電流之變化[12]。. 23.

(36) 為了讓負載電流的改變盡量不要影響到頻寬,就需要一個可以移動的 零點,讓它也可以隨著負載電流變化,並且和主極點同步,如此即可讓頻 寬不受影響。要產生可以移動的零點,可以利用之前的極零點補償的方法, 將其中的電阻改成操作在線性區(linear region)的MOS電晶體,當作一個 可變電阻使用,如下圖(3-6)所示。. VDD MC. Cc V1. V2 -VSS. 圖 3-6: 用 NMOS 取代補償電路中的電阻。 經由計算,可以算出利用電晶體來當作電阻的值及其範圍,該電晶體 操作在線性區,將線性區的電流對兩端電壓微分的倒數就是其對應的電 阻,表示如下: I DS =. [. 1 W 2 2(VDD − V2 − Vth )VDS − VDS μ n Cox 2 L. ⎛ ∂I ⇒ R C = ⎜⎜ DS ⎝ ∂VDS. ⎞ ⎟⎟ ⎠. ]. −1. VDS =0. W ⎡1 ⎤ = ⎢ μ nCox 2(VDD − V2 − Vth )⎥ L ⎣2 ⎦. −1. (3.2)式. 24.

(37) RC. RCmax. RCmin. V2min. 0V. V2max. V2. 圖 3-7: 改變 VDS 時電阻值的變化。 從上面的式(3.2)可以得知,電阻的值可以用電晶體的或是寬長比來控 制,改變Vgs(也就是VDD-V2)來觀察電阻值的變化,如圖3-7,電阻值並 不是呈規則的線性變化,不過大致上還是隨增加而減少。 有了可移動的零點之後,接下來就要針對主極點的變化,來放置零點 的位置,主極點頻率約為. 1 2πROUT COUT. ,而零點頻率約為. 1 ,其中C和C比 2πRC CC. 值是固定的,所以在設計上只要讓 ROUT COUT ≈ RC CC 。 如此一來產生的零點,便會跟隨主極點移動,使得頻寬在主極點往前 移時不會迅速縮減,此即追蹤零點(Tracking Zero)補償的方法。. 25.

(38) 實際應用到低壓降線性穩壓器上,如下圖(3-8)。 VIN VREF. MC Power Transistor. Errpr Amplifier. ROUT VOUT. ZC. Cc Compensation. R2. RESR. R1. COUT. 圖 3-8: 追蹤零點補償低壓降線性穩壓器。 利用輸出電晶體的閘極同時控制當作電阻補償用電晶體的 MC 閘極,當 負載有變化時,MC 的閘極同時跟著做變化,只要設計時調整 MC 和輸出電晶體 的大小比例,再藉由同樣的 Vgs 控制可變電阻的值,就可以讓零點的位置追 蹤主極點,達到補償頻寬及相位邊限的效果。. 26.

(39) 3.4 米勒頻率補償 本設計之線性穩壓器採用簡單米勒頻率補償(Simple Miller Compensation,SMC)技術[13],使得在頻率為 2MHZ 的時候,仍然能得到頗 大的閉迴路增益。從放大器的觀點來看,所設計的線性穩壓器在無迴授的 情況實際上是一個兩級放大器(Two-Stage Amplifier),誤差放大器為第一 級,而傳輸元件為第二級,其示意圖如圖(3-9)所示。. Vref. Power Transistor (A2). P1. Error Amplifier (A 1). P2. Vout. Cm. Feedback Network. CL. Iout. 圖 3-9: SMC 兩級放大器示意圖。 由圖(3-9)可以推導出經過簡單米勒頻率補償後的兩級放大器轉換函 數如下:. Vout Vin. ⎛ C ⎞ Gm1Gm 2 Ro1 Ro 2 ⎜⎜1 − s m ⎟⎟ Gm 2 ⎠ ⎝ ≅ ⎛ (1 + sC m Gm 2 Ro1 Ro 2 )⎜⎜1 + s C L Gm 2 ⎝. (3.3)式. ⎞ ⎟⎟ ⎠. 由(3.3)式得知,此兩級放大器含有兩個左平半面(Left Half Plane, LHP)極點和一個右半平面(Right Half Plane,RHP)零點,分別是主極點 P−3db =. G C 1 ,次主極點 P2 = m 2 和零點 Z1 = m ,其頻率響應如圖(3-10) C m Gm 2 Ro1 Ro 2 CL Gm 2. 所示。. 27.

(40) Gain(dB) P-3dB. 0. GBW. Frequency(HZ) Z1. P2. 圖 3-10: SMC 兩級放大器的頻率響應。 從複變函數的定理可知,右半平面零點會令換函數在該零點頻率上的 相位(Phase)急遽下降,使電路因相位邊際(Phase Margin,PM)不足而發散, 故必須變免零點 Z1 頻率落在放大器的截止頻率(Cutoff Frequency)前面。 截止頻率的值等於電子學中所定義的增益頻寬積(Gain Bandwidth Product),從式(3.3)可得到增益頻寬積 GBW =. Gm1 。為了確保 SMC 放大器 Cm. 的穩定性,P2 和 Z1 必須遠落在截止頻率之後,一般增益頻寬設計成等於兩 分之一的次主級頻率及***以得到很好的相位邊際,由此可得: Cm = 2. Gm1 CL Cm. (3.4)式. 式(3.4)的前提是 P2 的頻率比 Z1 的頻率低,若. Gm1 很大的話,會使 Cm Gm 2. 遠大於 CL,結果 P2 的頻率比 Z1 的頻率來的高且會發散,故 Z1 的頻率也要落 在 P2 之後。 由(3.3)式和(3.4)式得: GBW =. Gm1 Gm 2 = Cm 2C L. (3.5)式. 改變 Gm1 和 Cm 並不會改變 GBW,因為由式(3.5)可知它們永遠成比例,故 想提高 GBW 就必須把 Gm2 增大或把縮小,由於 CL 可能會在不同的情況下發生 28.

(41) 改變,故在本論文後續就是提高放大器的串聯級數來增加頻寬。 下圖(3-11)為四級放大器組成之線性穩壓器採用米勒頻率補償稱為 Multi-Stage LDO[14][15]。. VREF. 1. Pdon. 2. 3. Ppar. 4. Iout P1st_nonVout. Cm Feedback Network. RESR CL. 圖 3-11: Multi-Stage LDO。 由圖(3-12)可以推導出轉換函數如下:. Vout Vin. ⎡ ⎛ C gd ⎞ ⎤ C m C gd ⎞ ⎛ Cm ⎟⎟ − 1⎥ ⎟⎟ − s⎜⎜ G m1G m 2 G m 3Gm 4 Ro1 Ro 2 Ro 3 Ro 4 ⎢ s 2 ⎜⎜ + ⎢⎣ ⎝ G m 2 G m 3G m 4 Ro 2 ⎠ ⎝ G m 2 G m 3G m 4 Ro 2 Ro 3 G m 4 ⎠ ⎥⎦ = C gd C L ⎞ ⎛ CL (1 + sGm Gm 2 Gm3Gm 4 Ro1 Ro 2 Ro3 Ro 4 )⎜⎜ s 2 −s − 1⎟⎟ G m 2 G m 3 G m 4 Ro 2 Ro 3 ⎠ ⎝ G m 2 G m 3 G m 4 Ro 2. 其中, dc gain = Gm1Gm 2 Gm3 Gm 4 Ro1 Ro 2 Ro 3 Ro 4. Pdon =. 1 Gm1Gm 2 Gm 3 Gm 4 Ro1 Ro 2 Ro 3 Ro 4. P1st _ non = PPar =. G m 2 G m 3 G m 4 Ro 2 Ro 3 CL. 1 Ro 3C gate. 由上式可知當 Iout 增大時,因 A1、A2、A3、A4 變小,使得 P1st _ non 會往高頻移 動使系統穩定,但 Cgate 增大, PPar 會移到較低頻,當電流持續增加, P1st _ non 和. 29.

(42) PPar 將越接近,如圖(3-12). 1 P1st_non. P par. jω. 0.5. -4.E+05. -3.E+05. -2.E+05. σ. -1.E+05. 0.E+00. 圖 3-12: 電流持續增加, P1st _ non 和 PPar 的根軌跡。 由轉移函數可知其二次網路特性方程式之標準型式: s2 +. w0 s + w02 Q. 其中 Gm 2 Gm3 Gm 4 Ro 2 C gd C L. w0 =. Q=. C gd CL Gm 2Gm 3Gm 4 Ro 2. Gm 2Gm3Gm 4 Ro 2 Ro 3 CL. a0 as + bs + c 2 b > 4ac : two separate pole. T (s ) =. 2. b 2 < 4ac : complex pole. 30.

(43) 當 Iout 增大時,Q 值上升使得 P1st _ non 和 PPar 越接近而行成 complex poles, 如圖(3-13): Loop Gain. Llight_load. Gain-dB. Lheavy_load non-dominant complex poles occurs. 0dB. UGF =. Gm (transconductance of input stage) CM (CompensationCapacitor). Frequency-Hz. 圖 3-13: P1st _ non 和 PPar 行成 Complex Poles。. 31.

(44) 第四章 低壓線性穩壓器設計與模擬. 圖(4-1)為 LDO 的主要電路,在 Error Amplifier 方面,它大致上由 4 個級數所構成,包含第 1 級的差動放大器,第二級負載是電晶體二極體 (MOS-diode)的共源級放大器(CS amplifier);第三級共源級疊接共閘極放 大器(CS-CG cascode amplifier),負載是 R1、R2 且 R1>R2 與 MP3;Power MOS 的最後一級,會是一個大尺寸的 PMOS 電晶體。 VDD. R1. R2. Vg. MPB21. MPB11 VBP1. MP3 MPP41 22. MPB22 MPB. MPB12. VBP2. I1. I2. MPP42. Switch MP3. VB. VFB. VREF MP1. CM1. MP2. Vout MN6 VP. RF1. VFB MN1. MN2. MN3 MN4. MN5 RF2. 1 st Stage. 2 nd Stage. 3 rd Stage. CL. RL. P par. RE. Routn. g mp ∝ I out Mp Iout. P1st_non. Vout. Power Stage. 圖 4-1: Pole Tracking 的四級放大器 LDO 主要電路。. 4.1 Pole Tracking(電阻R2、電晶體MP3) 由 3.4 得知主極點會隨著輸出電流增大往高頻跑,假如第一個非主極 點與第二個非主極點均不動的話,此時就會有穩定度的問題。所以可以在 電流大的時候,降低迴路增益,同時將第二個非主極點拉到更高頻,如圖 (4-1)也就是讓電晶體 MP3 導通,減少第三級負載阻值[16]。. 32.

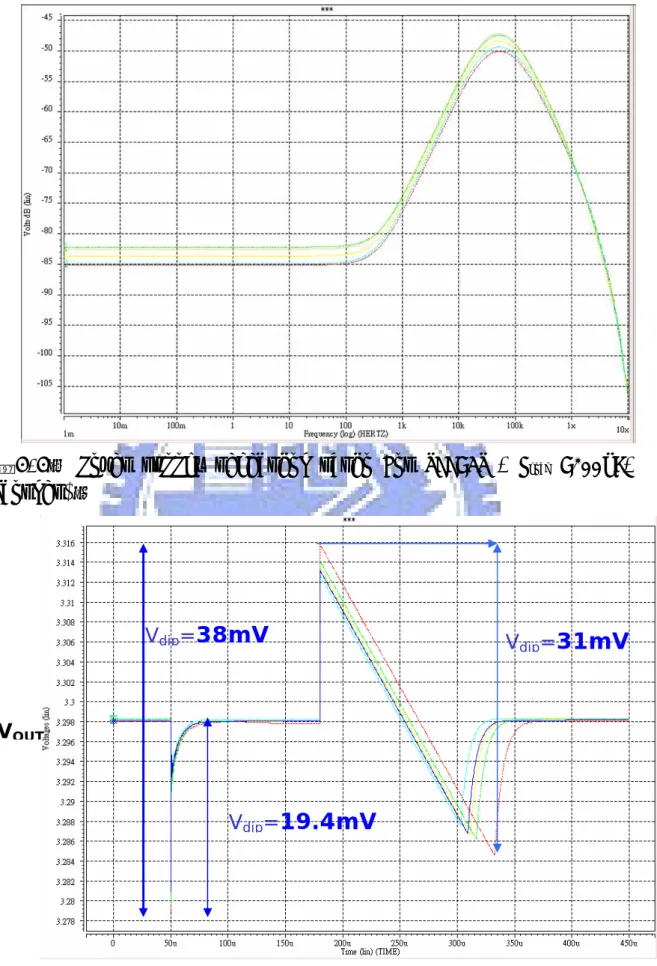

(45) 4.2 模擬結果(TT, SS, FF, FS, SF). 圖 4-2: 頻率響應(For VDD=5V, Iload=200mA, 5 corner)。. 33.

(46) Gain=121dB . TT SS FF FS SF. UFG=56KHz. Phase=62°. 圖 4-3: 頻率響應(For VDD=5V, Iload=1mA, 5 corner)。. 34.

(47) 圖 4-4: Power supply rejection ratio(For VDD=5V , Iload =200mA, 5corner)。. Vdip=38mV. Vdip=31mV. VOUT. Vdip=19.4mV. 圖 4-5: 暫態響應(VDD=5V, Iload =0.1mA~200mA, 5 corner)。. 35.

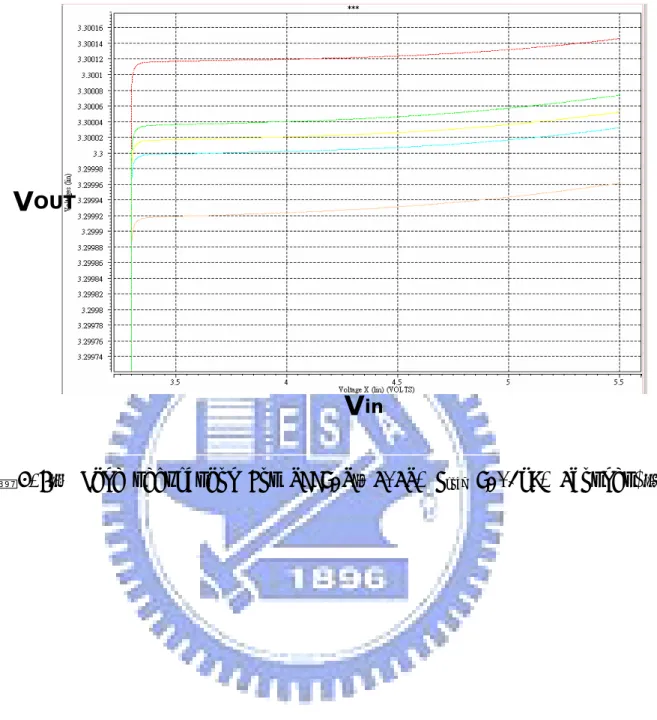

(48) VOUT. Vin 圖 4-6: Line regulation(For VDD=0V→5.5V, Iload =0.1mA, 5corner)。. 36.

(49) VOUT. Vin 圖 4-7: Line regulation(For VDD=0V→5.5V, Iload =200mA, 5corner)。. VOUT. ILoad 圖 4-8: Load regulation(For ILoad=0.1mA →200mA, 5 corner)。. 37.

(50) Technology Supply voltage Output voltage Load transient response. Simulation TSMC 0.35μm 2P4M 3.5~5.5 3.3 19.4 @ Io= 0.1mA-200mA 31mV @ Io= 200mA-0.1mA. PSR F=20KHz F=1MHz F=1.5MHz Load Regulation Line Regulation. Units V V mV. 50 dB 67 72 0.24 @ Io= 0.1mA-200mA mV/mA 0.25 @ Vin= 0V-5.5V, Io= mV/V 200mA Power Consumption (no load) μW 551 2 Active Area μm 400x500 表 4-1: 模擬數據。. 38.

(51) 第五章 靜電放電防護設計概念與測試. 5.1 靜電放電防護概論 隨著科技的進步,積體電路的尺寸也隨之縮小。然而,靜電對於積體 電路晶片的傷害並沒有隨之下降,因而導致晶片對於靜電放電的免疫能力 下降。為了增加晶片之靜電放電防護,許多解決之道相繼被提出。. 5.2 靜電放電模式 一般而論,有三種主要的靜電放電模式:人體模式(HBM) 、機械模式 (MM) 與元件電荷模式(CDM)。. 5.2.1 人體模式(HBM) 人體模式的靜電放電來自於人體。假設某人身上有高電位的靜電, 將其手指放置在積體電路晶片的腳位;於此同時,至少有一晶片腳位是 被接到低(或地)電位。根據電流原理(電荷由高電位流向低電位),電流 將會在手指接觸的腳位流往低電位的腳位,此放電的過程會在短到幾百 毫微秒的時間內產生數安培的瞬間放電電流。據此分析,對於積體電路 靜電放電,有兩個最基本的需求 :一則必需要有靜電的存在;另一則 是必需有電流路徑的存在。舉例說明, 空氣中的電荷並不會傷害晶片; 而人體若只接觸晶片的某腳位,而無接地腳位,也不會有靜電流產生。. 39.

(52) 有關於HBM的ESD已有工業測試的標準,為先今各國用來判斷IC之 ESD可靠度的重要依據。標準人體模式靜電放電的等效電路如圖(5-1) 所示[16]。其中人體的等效電容定為一個100pF的電容,人體的等效電 阻為一個1.5kΩ的電阻。 R1=1500? S1 Terminal A. High Voltage Pulse Generator. C1=100pF. S2. DUT sockel. short R2=500?. Terminal B. 圖 5-1: 典型的人體模式靜電放電等效電路。. 40.

(53) 5.2.2 機械模式(MM) MM的ESD是只機械本身累積了靜電,當此機器去碰觸到IC時,此靜 電便經由IC的pin放電,圖(5-2)指出機械模式靜電放電的等效電路 [17]。由於機械放電模式的等效電阻為零阻抗,故其放電的過程更短, 在幾毫微秒到幾十毫秒之內會有十幾安培的瞬間放電電流產生,因此機 械放電模式對IC的破壞力更大。其主要的被動元件是一個200pF的電容。 S1 Terminal A. High Voltage Pulse Generator. C1=200pF. S2. DUT sockel. short R2=500?. R1=10K ? to 10M ? Terminal B. 圖 5-2: 典型的機械模式靜電放電等效電路。. 41.

(54) 5.2.3 元件電荷模式(CDM) 靜電放電是元件電荷模式,其電荷來元件本身內部,也許是經由製 造等過程中所產生。一旦晶片的某一腳位接地,就可能導致其內部電荷 往外流動而傷害晶片。 正因元件電荷模式乃由元件本身內部所觸發,因此,很難以一等效 電路表示。因為電荷的貯存與晶片的尺寸大小有關,因而很難以一種等 效電路表示所有的晶片。人們通常以電流波形上升時間小於 400ps,如 圖(5-3)所示的波形(Tr 小於 400ps)來探討元件電荷模式[18]。. I. Ip. 90%. 50%. 50% Td U+. 10%. T. U-. Tr. 圖 5-3: 元件電荷模式的電流波形。 根據晶片封裝的型式,有兩種元件電荷模式:一種是無插座 (non-socket type)型式,另一種是有插座(socket type)型式。其主要 的差異來自於電荷產生的方式。無插座型式的電荷乃由感應電場所產 生,而有插座型式則是先將電荷由晶片的某一腳位灌入,隔數秒鐘後, 再由另一腳位接地,將電荷排除。故而有插座型式的元件電荷模式有點 類似之前的人體模式與機械模式,但其具有一段電荷儲存重組的時間, 不像前兩種, 電荷輸入與輸出晶片乃在很短的時間(電荷輸入腳位與接 地腳位同時接上)。. 42.

(55) 5.3 靜電放電放護設計概念 靜電放電防護電路(ESD protection circuits)是積體電路上專門用來 做靜電放電防護之用,此靜電放電防護電路提供了 ESD 電流路徑,以免 ESD 放電時電流流入 IC 內部電路而造成損傷。因 ESD 來自外界,所以 ESD 防護 電路都是做在 PAD 的旁邊。在輸出 PAD,其輸出級中大尺吋的 PMOS 及 NMOS 元件本身便可當作 ESD 防護元件來用,但是其佈局方式必須遵守 Design Rules 中有關的 ESD 佈局方面的規定。在輸入 PAD,因 CMOS 積體電路的輸 入 PAD 一般都是連接到 MOS 元件的閘極(gate),閘極氧化層是容易被 ESD 所打穿,因此在輸入墊的旁邊會做一組 ESD 防護電路來保護輸入級的元件。 在 VDD pad 與 VSS pad 的旁邊也要做 ESD 防護電路,因為 VDD 與 VSS 腳之 間也可能遭受 ESD 的放電。ESD 防護電路的安排必須全方位地考慮到 ESD 測 試的六種模式,因為一顆 IC 的 ESD failure threshold 是看整顆 IC 所有 腳中,各種測試模式下,最低 ESD 耐壓值為該顆 IC 的 ESD failure threshold。因此,一個全晶片 ESD 防護電路的安排要如圖(5-4)所示[19]。 在圖(5-4)中,Input pad 與 Output pad 要具有防護 PS,NS,PD 及 ND 四種 模式的靜電放電,另外,VDD 到 VSS 也要有 ESD 防護電路。 VDD ESD Protection Circuit. Internal Circuite. ESD Protection Circuit. PMOS. Input PAD. Output PAD ESD Protection Circuit. ESD Protection Circuit. NMOS. ESD Protection Circuit. VSS. 圖 5-4: Whole-Chip 靜電放電防護電路。 因 ESD 防護電路是為了防護 ESD 而加入的,故 ESD 防護電路在積體電 路正常操作情形下,該 ESD 防護電路是不動作的。. 43.

(56) 在一些前人設計的 ESD 防護電路中,尤其是在 Input pad,其 ESD 防護 電路只安排在 Input pad 與 VSS 之間,Input pad 到 VDD 之間沒有安排 ESD 防護電路,如圖(5-5)所示。當 ND 模式的 ESD 放電發生時,此負的 ESD 電 壓會先經由 Input 到 VSS 之間的 ESD 防護墊路跑到 VSS 電源線上,沿著 VSS 電源線到 VDD 與 VSS 之間的 ESD 防護電路,再經由此 VDD 與 VSS 之間的 ESD 防護電路傳到 VDD 電源線上,最後由 VDD pad 流出此 IC。ND 模式的靜電放 電在圖(5-5)中是藉由 Input 到 VSS 以及 VDD 與 VSS 之間的 ESD 防護電路來 旁通的 ESD 電流。有些人抄到了 Input 到 VSS 之間的 ESD 防護電路,這時, 在 ND 模式 ESD 測試下,內部電路常常死得很慘(無法自 Input pad 的Ⅰ~Ⅴ 變化觀測得到,必須再經 IC 性能測試分析才會發現),卻以為可耐很高的 ESD 電壓。 Unexpected Discharging Path. ESD Current Discharging Path Rdd. VDD PAD PMOS Input PAD 0V. -VP. ND-mode ESD Voltage. C (VDD-to-VSS). ESD Protection Circuit. ESD Protection Circuit. Internal NMOS Circuits Rss. Input Protection. VDD-to-VSS Protection. VSS PAD. 圖 5-5: 異常靜電放電損傷積體電路內部的原因示意圖。 隨著晶片的尺寸愈做愈大,環繞整個晶片的 VDD 與 VSS 電源線也愈拉 愈長,寄生的電容電阻效應便會顯現出來,當 IC 的佈局造成電源線的雜散 電容電阻效應如圖(5-5)所示時(Rss, Rdd,C),這些雜散電阻電容會延遲 ESD 電流經由 VDD 與 VSS 之間的 ESD 防護電路旁通而過。這時,來不及放掉的 ESD 電流便會藉著電源線的相連接而進入到 IC 內部電路中,IC 內部電路在 佈局時一般都以最小尺寸來做,也不會考慮 ESD 的佈局方式,因此 IC 內部 電路更易被此種 ESD 電流所損傷。因此,會造成異常的 ED 損傷現象,也就 是 ESD 防護電路都好好的,但內部電路已被破損傷許多,前面已提過這種 內部損傷是無法從單一輸入腳的Ⅰ~Ⅴ變化看得出來的。. 44.

(57) 因此,當晶片尺寸(die size)較大時,Input pad的ESD防護電路就必 須要如圖(5-4)所示,在Input pad 與VDD之間也要提供ESD防護電路來直接 旁通ESD電流,而不要藉由VDD與VSS之間的ESD防護電路來間接放電。. 5.3.1 靜電放電防護設計 除了元件電荷模式來自於晶片本身內部,另兩種靜電放電,其電荷 皆由晶片外部所產生。既然,電荷乃由晶片的腳位輸入內部,若欲保護 晶片內部免於受到靜電的傷害,我們必需將靜電保護電路置放在輸入/ 輸出(I/O) 的位置。藉由將靜電在輸入/輸出的晶片電路就排放掉,而 保護晶片本身內部免於受到靜電傷害。 以下列舉設計靜電放電防護的主要原則:[20] (1)在晶片正常操作情形下,靜電放電防護電路必需是關閉的,換言 之,不可因靜電放電防護電路的存在而導致過多的漏電流產生。 (2)在靜電放電的過程中,靜電放電防護電路必需提供足夠的放電路 徑。 (3)盡可能將靜電放電防護電路的佈線面積縮小。 (4)靜電放電防護電路不可導致晶片電路閉鎖。 (5)靜電放電防護電路盡可能與一般製程相容,而不需要額外的製程光 罩。 無庸置疑地,第一原則為靜電放電防護電路設計的必要條件。例 設,我們若以單一電阻來做為靜電放電防護電路,其排放靜電的能力勢 必很強。然則,此電阻的存在必然導致額外的漏電流產生;換言之,我 們不可僅以一電阻來當作靜電放電防護。 既然靜電放電防護電路必需設計在輸入/輸出電路之中,在靜電放 電防護設計之前,靜電放電發生在晶片的兩個腳位之間;假如,任意兩 個腳位之間,都有靜電放電防護電路存在,則積體電路晶片就能被其保 護。換言之,對於輸入/輸出電路,靜電放電防護設計者僅需觀看其與 晶片腳位相連接的電路。 45.

(58) 圖(5-6)乃一典型的輸入電路,有兩個基本的靜電放電防護元件存 在,其一為閘極接地的N型金氧半導體(GGNMOS, gate grounded NMOS), 另外有一個閘極接電源的P型金氧半導體(GPPMOS, gate powered PMOS)。在此電路中,共有三個腳位:輸入腳位、電源腳位與接地腳位, 圖中的電阻具有降低靜電放電突波對反相器的傷害。. VDD Parasitic BJT Parasitic Diode. GDPMOS. I/P GGNMOS. Parasitic BJT. Parasitic Diode. VSS. 圖 5-6: 典型的輸入電路。 關於輸入電路的應用,輸入腳位通常會接觸到反相器(inverter) 的閘極。為了避免反相器閘極被靜電放電所傷害,防護電路必需被設計 在晶片之中。例如,正向靜電放電發生在輸入腳位(I/P)與接地腳位(VSS) 之間,閘極接地的N型金氧半導體必需以電壓突然跳回(snapback)打開 寄生電晶體,來排放此靜電放電電荷,如圖(5-7)所示[21]。相反地, 當負向靜電放電發生在輸入腳位(I/P)與接地腳位(VSS)之間,寄生二極 體(parasitic diode)就可在順向操作下,排放靜電。. 46.

(59) Avalanche. LNPN. IB Igen. ISub. Vsub Rsub. 8 I12 (mA/μm). Source Saliciede region Drain 0V (Emitter) (Collector) 0V +V Gate IS ID n n IC. Vt2,It2. 6 4 2. Vsp. Vav 2 4 6 8 Drain Voltage (V) (b). P-Substrate. 0V (a). 圖 5-7: (a)N 型金氧半導體的剖面圖,包含旁路電晶體 NPN。(b)0.13 μm 製程下,高電流的電流對電壓曲線圖,包含 LNPN 打開電壓(Vav)、 突然跳回的操作電壓(Vsp)與熱能導致的第二次崩潰電流(It2)。 相似的分析,亦可用於閘極接電源的 P 型金氧半導體,但是值得注 意地,在早期的製程中,並不會發生電壓突然跳回的現象。既然,N 型 金氧半導體的閘極接地,在正常操作情形下,此防護元件處於關閉的條 件,故其符合靜電放電防護設計的第一大原則。. 47.

(60) 另一方面,輸出電路為了驅動下一級電路,往往採用較大的元件來 應用。而此大尺寸的元件亦可當作靜電放電防護電路,若其尺寸足以排 放靜電放電所產生的大電流,則以驅動元件作為靜電放電防護元件。如 圖(5-8)所示,並無額外的閘極接地的 N 型金氧半導體或閘極接電源的 P 型金氧半導體。 VDD. O/P. Core. VSS. 圖 5-8: 典型的輸出電路。 如上所述,任何符合設計靜電放電防護主要原則的元件,皆可當作 靜電放電防護元件。. 48.

(61) 圖(5-9)顯示另一種防護電路設計:二極體電路。因為二極體容忍 的反相崩潰電流太低,當正向靜電放電發生在輸入腳位與接地腳之間, 其靜電放電必需經由路徑1(Path1)來實施,而不可由路徑2(Path2)來排 放。 VDD Path1. O/P. Core. Path2 VSS. 圖 5-9: 典型的二極體電路。. 49.

(62) 5.4 靜電放電測試及判讀. 5.4.1 靜電放電測試組合 靜電的累積可能是正的或負的電荷,因此靜電放電測試對同一 IC 腳而言是具有正與負兩種極性。靜電放電可能出現在 IC 的任何兩隻腳 之間,然不相干的兩隻腳之間一般而言是不易被 ESD 所破壞,因為兩隻 腳不相干,唯一共同使用的是 VDD 與 VSS 電源相連接。ESD 發生在不相 干的兩支 IC 腳之間時,放電電流會經由內部電路連接線跑到 VDD 或 VSS 電源線上。再由 VDD 或 VSS 電源連接線到另一支 IC 腳,再由那支 IC 腳 流出 IC 之外。若每一 IC 的每兩角之間都要做測試,那麼一顆 40pin 的 40 IC 便要有 2×C2 (=1560)種排列組合的 ESD 測試,這太浪費時間。因此, 改良式的測試方法是美依輸入/輸出腳對 VDD 與 VSS 腳做正與負的 ESD 測試,再加上 VDD 腳對 VSS 腳做正與負的 ESD 測試,如此一顆 40pin 的 IC(38 支 I/O pin,1 支 VDD pin,1 支 VSS pin)只要測 154 種排列組合。 想一想,128 pin 的 IC 會有幾種組合? 圖(5-10)顯示 ESD 測試的幾種模式[19],對一支 Input 或 Output 腳而言,有四種 ESD 測試模式,分別為: (1) PS-mode:VSS 腳接地,正的 ESD 電壓出現在該 Input/Output 腳對 VSS 放電,此時 VDD 與其他腳皆浮接。 (2) NS-mode:VSS 腳接地,負得 ESD 電壓出現在 Input/Output 腳對 VSS 腳放電,此時 VDD 與其他腳皆浮接。 (3) PD-mode:VDD 腳接地,正的 ESD 電壓出現在該 Input/Output 腳對 VDD 腳放電,此時 VSS 與其他腳皆浮接。 (4) ND-mode:VDD 腳接地,負的 ESD 電壓出現在該 Input/Output 腳對 VDD 腳放電,此時 VDD 與其他腳皆浮接。除此之外,VDD 腳與 VSS 腳之間也要做 ESD 測試。 (5) VDD→VSS mode:由 VSS 腳接地,正的 ESD 電壓出現在 VDD 腳對 VSS 腳放電,其他腳皆浮接。 50.

(63) (6) VSS→VDD mode:由 VSS 腳接地,負的 ESD 電壓出現在 VDD 腳對 VSS 腳放電,其他腳皆浮接。. (1) PS-mode VESD. (2) NS-mode VESD. VDD. VDD. 0V. +V. -V. 0V. VSS. VSS. (3) PS-mode V ESD. (4) NS-mode V ESD. VDD. VDD. 0V. +V. -V. 0V. VSS. VSS. 51.

(64) V ESD. (5) VDD - VSS mode. V ESD. 0V. (6) VSS - VDD mode. 0V. +V. VDD. -V. VDD. VSS. VSS. 圖 5-10: ESD 測試的幾種模式。. 5.4.2 靜電放電防護的測試 在每一次測試模式下,每一支 IC 腳先被加大某一 ESD 電壓,此 ESD 電壓由小而逐漸增大。再同一 ESD 電壓下,IC 腳被放電三次,在觀看 此腳是否已被 ESD 所損壞,若 IC 尚未被損壞則調升 ESD 的電壓,再放 電三次。如此重覆下去,直到該 IC 腳已被 ESD 所損壞,此時造成 IC 腳 損壞的 ESD 測試電壓稱為 ESD failure threshold (靜電放電故障臨界 電壓)。如果每次調升的 ESD 測試電壓太小,則測試到 IC 腳損壞要經過 多次的 ESD 放電,增長測試時間;若每次調升的 ESD 測試電壓太大,則 難以較精確測出該 IC 腳的 ESD 耐壓能力。因此,有一測試經驗法則, 當 ESD 測試電壓低於 1 千伏特時,每次 ESD 電壓增加量為 50V;當 ESD 測試電壓高於 1 仟伏特時,每次 ESD 電壓增加量為 100V。而 ESD 測試 的起始電壓則從平均 ESD 故障電壓的 70%開始。例如某一 IC 的 ESD 耐 壓大概平均在 2000V(HBM)那麼起始測試電壓約為 1400V 開始。測試時, 1400V 的 ESD 電壓打到 IC 的某一腳去(相對的 VDD 或 VSS 腳要接地), 測三次 1400V 的 ESD 放電,若該 IC 腳尚未被破壞,則調升 ESD 電壓到 1500V,此 1500V 的 ESD 電壓再打到該 IC 腳三次,若該 IC 腳尚未被損 壞,則調升 ESD 電壓到 1600V,依此類推,直到該 IC 腳被靜電放電所 損壞。 我們來算一下,一顆 40pin 的 IC(38 支 I/O,1 支 VDD,1 支 VSS) 自 1400V(HBM)測到 2000V 所要測試的次數: 52.

(65) 每一次測試模式的測試次數=[(2000V-1400V/100V)+1]×3=21 次 每一支 Input/Output 腳的測試模式=4 種 38 支 Input/Output 腳的總測試次數=38 支 × 4 種 × 21 次=3192 次 VDD 對 VSS 腳的總測試次數=1 支 × 2 種 × 21=42 次 40 pin IC 的 ESD 總測試次數(1400V~2000V)=3234 次 由上述的簡單估算可知,40pin 的 IC,只從 1400V 測到 2000V,每 一次電調升 100V,則要 3234 次的 ESD 放電測試。而在實際情形,IC 腳 的耐壓度可能每一支都不相同,要真正測出每一支腳的 ESD 耐壓成喥, 則所需測試次數會遠超過上述的數字。因此適度放寬每次 ESD 電壓調昇 幅度(自 100V→250V)可以減少測試的次數及時間。 以上所談的 ESD 測試次數是指 HBM 測試,若該 IC 也要做 MM 的 ESD 測試,則還在再加上 MM 的 ESD 測試次數。 既然,有這麼多的靜電放電防護測試的製造廠商;而不同的廠商, 其所製造的機台勢必不同,如此,操作介面,必會因此而難以統一。然 而,假若我們知道測試的原理,則能幫我們在很短的時間內,便能熟悉 新的測試機臺。本節的重要性,便著重在如何使我們瞭解靜電放電防護 測試的基本原則。 要對積體電路晶片測試前,首先我們必須定義積體電路晶片的測試 腳位。一般而論,工程師們會將積體電路晶片的腳位,分為五大族群: 電源族群、接地族群、輸入族群、輸出族群與輸入輸出族群。 第二步驟,定義欲外加靜電放電的腳位與靜電放電過程中,欲接至 相對低電位的腳位。 第三步驟,制定欲外加的靜電放電模式:人體模式(HBM) 、機械模 式(MM) 或元件電荷模式(CDM)。 第四步驟,定義欲量測其電流對電壓的腳位。舉例說明,我們以丙 腳位為相對低電位,而對甲腳位施放靜電放電,但是我們猜測也許乙腳 位對丙腳位的電路路徑會受到靜電破壞,我們可以同時量測甲腳位對丙 腳位的電路路徑與乙腳位對丙腳位的電路路徑。 最後,我們必須制定積體電路晶片好壞的判定準則,這是一個非常 53.

(66) 重要卻富有爭議的主題。最好去判斷積體電路晶片好壞的方法,莫過於 直接測試晶片的正常工作特性。然而,若欲測試的主題,只是一個元件, 則無正常工作特性可提供測試。在此,我們摘錄一些常用來作晶片好壞 判斷的電流對電壓測試圖形。 (1)短路與斷路的測試。 (2)二極體測試(將積體電路晶片定義在某個電壓下,若其電流大於(或 小於)某個特定值,則將其視為壞的產品)。 (3)電流對電壓曲線的測試。 (3a)相對Ⅰ~Ⅴ漂移:當 IC 被 ESD 測試後,自 Input/Output 腳看 進 IC 內部的Ⅰ~Ⅴ曲線漂移量在 30%(40%或 50%),以作為晶 片判斷的標準。 (3b)絕對漏電流測試:在某一特定電壓下,晶片電流必須小於某一 特定值,其 Input/Output 腳的漏電電流超過 1μA(10μA)。漏 電電流隨所加的偏壓大小增加而增加,在測漏電電流時所加的 偏壓有人用 5.5V,也有人用 7V。 (3c)電流對電壓曲線的比較:在某一特定電壓下,靜電放電測試後 的晶片電流除以靜電放電測試前的晶片電流必須小於某一比 例值。 至於晶片要能通過多大的靜電放電測試電壓:一般而言,工業產品 必須能通過人體模式 2KV,機械模式 200V 與元件電荷模式 1KV。 除了人體模式、機械模式與元件電荷模式外,傳輸線脈波(TLP)亦 能當作了解元件特性的工具。觸發電壓(Vt1)、迴轉電壓(Vsp)、二次崩潰 電流(It2)、二次崩潰電壓(Vt2)與電晶體工作電阻(Ron)是靜電放電工程師 常用以探討元件特性的參數。 在產品被封裝之前,靜電放電工程師亦可用晶片模式(Wafer Level) 來測試晶片。有些工程師利用此種測試模式來降低產品製造所需的時 間。. 54.

數據

相關文件

附表 1-1:高低壓電力設備維護檢查表 附表 1-2:高低壓電力設備維護檢查表 附表 1-3:高低壓電力設備(1/13) 附表 2:發電機檢查紀錄表. 附表

The underlying idea was to use the power of sampling, in a fashion similar to the way it is used in empirical samples from large universes of data, in order to approximate the

develop a better understanding of the design and the features of the English Language curriculum with an emphasis on the senior secondary level;.. gain an insight into the

油壓開關之動作原理是(A)油壓 油壓與低壓之和 油壓與低 壓之差 高壓與低壓之差 低於設定值時,

Since the sink is aware of the location of the interested area, simple greedy geographic routing scheme is used to send a data request (in the form of

This design the quadrature voltage-controlled oscillator and measure center frequency, output power, phase noise and output waveform, these four parameters. In four parameters

Ethernet Module、RF Transceiver。Switching Power 為提供整個系統的電源,其輸入電 壓為 90V~264VAC,輸出 5VDC 為提供整個系統電源所需。RF Transceiver 所需的電 壓是 5VDC

This paper presents an integrated wireless network, rapid response to the three components of the Code (QRCode) and smart phones, build a low -cost "smart public bike