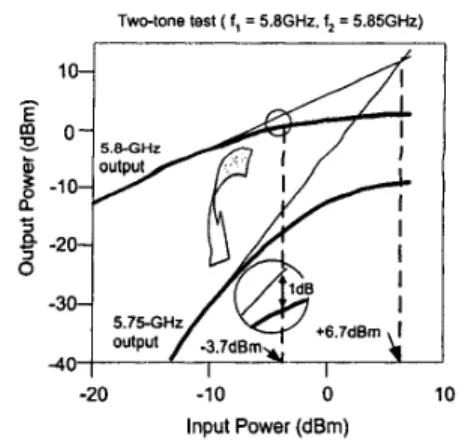

A 5.8-GHz two-stage high-linearity low-voltage low noise amplifier in a 0.35-/spl mu/m CMOS technology

全文

數據

相關文件

This column splitting results in a new sparse matrix and hence a new LDPC code of longer length. If column splitting is done properly, the extended code performs amazingly well

如圖1-16所示,NOT運算會改變邏輯準位。輸入為 HIGH (1) 時,輸出為LOW (0)。當輸入為LOW時,輸出

本模組的編碼法適合 Command mode/Data mode 切換先連續發射 10 次 High、Low 信號作為前導波形接著發射起始波形 600 微秒 High→600 微秒 Low→600 微秒 High→400 微秒

The four e/g-teaching profiles identified in this study are outlined as follows: parsimony (low e-teaching and medium, below- average g-teaching), conservation (low e-teaching and

Department of Physics and Institute of nanoscience, NCHU, Taiwan School of Physics and Engineering, Zhengzhou University, Henan.. International Laboratory for Quantum

Department of Physics and Taiwan SPIN Research Center, National Changhua University of Education, Changhua, Taiwan. The mixed state is a special phenomenon that the magnetic field

• cost-sensitive classifier: low cost but high error rate. • traditional classifier: low error rate but

• When the coherence bandwidth is low, but we need to use high data rate (high signal bandwidth). • Channel is unknown