國立交通大學

物理研究所

碩士論文

以表面電位顯微鏡觀測金屬-氧化層-半導體能帶

The Band Structure

of Metal-Oxide-Semiconductor Measured

by Kelvin Probe Force Microscopy

研 究 生:黃乾庭

指導教授:林登松 教授

以表面電位顯微鏡觀測金屬-氧化層-半導體能帶

學生:黃乾庭 指導老師:林登松教授 國立交通大學物理研究所碩士班 摘要 表面電位顯微鏡在偵測半導體元件之特性已經有很多的研究,因為它具有低 破壞性,高解析度,操作方便等諸多優點。藉由量測表面電位顯微鏡探針與半導 體表面的接觸電位差(contact potential difference),可以清楚的判定元件上各材質 的分佈位置。 本論文是探討 MOS 元件在奈米解析度下的二維電位分佈。為了觀測金屬、 氧化層、半導體之間的電位,首先要將樣品劈開,量測樣品的剖面。我們試了許 多劈開樣品的方式,最後發現在 Si(100)晶片上以與[110]平行或垂直的方向劈 開,可得到較平坦的剖面;在 Si(111)晶片上則要以與[1-10]夾 30 度或 60 度方向 劈開,得到較平坦的剖面。由表面電位顯微鏡得到 MOS 元件剖面的表面電位圖, 可清楚的定位元件上金屬、氧化層、半導體的位置。基於此,在 MOS 元件金屬 上外加一可變偏壓,可得金屬、氧化層、半導體隨外加偏壓改變的電位變化圖。 由此圖,可直接觀察出 MOS 元件的平帶電壓(flat-band voltage)、臨界電壓 (threshold voltage)、空乏區寬度大小(depletion region)等一些特性。The Band Structure

of Metal-Oxide-Semiconductor Measured

by Kelvin Probe Force Microscopy

Student:Chiang-Ting Huang Advisor:Deng-Sung Lin

Institute of Physics National Chiao Tung University

Abstract

Many researches have being conducted using Kelvin probe force microscopy (KFM) on semiconductor devices, because of its less destructive nature, high resolution quality, and easy-to-control advantages. By measuring the contact potential difference between the surface potential microscopy probe and the semiconductor surface, we can clearly distinct between the boundaries of the materials made up the device.

In this report, we will discuss the metal-oxide-semiconductor (MOS) device on nano scale resolutions, and its potential distributions in two-dimensions (2D). To observe the potentials between the metal, oxide, and semiconductors, we need to slice through a sample, and do the measurements on its cross sectional surface. We tried many ways of cutting the samples, finally find the best way of cutting the sample; with Si(100) on the [110] direction, cutting horizontally and vertically will end up with more flatter cross sectional surface; with the Si(111) sample, we need to cut it in 30 degrees or 60 degrees, along the [1,-1,0] direction, to get a flatter surface. The potential distribution obtained from the surface potential microscope on MOS device clearly shows the regions of the metal, oxide, and semiconductors of the device. Base on that, by adding external bias voltages on the device will give the potential changes on the metal, oxide, and semiconductors with respect to the voltage applied. From this, we can directly examine the characteristics such as the flat-band voltage, threshold voltage, and the depletion regions of the MOS device.

誌

謝

研究所兩年生活很快,腦中依稀存在一年級懵懵懂懂的臉孔,沒想到真的輪 到我畢業了。這兩年來學到了不少東西,也領悟許多求學的態度與方法,是學生 時代的一個美好回憶。首先要感謝我的指導教授林登松老師兩年來的指導,老師 認真嚴謹的態度一直是我效法的對象,同時也讓我學習到了處理事情的多方思考 邏輯,一生受用無窮。謝謝實驗室鎧銘學長在我徬惶不知所措時,及時給我新的 想法與意見,我想未來我們仍然是好夥伴;感謝世鑫學長在實驗上的幫助,每次 樣品的準備都要麻煩到你,謝謝!;感謝明峰學長在我挑燈夜戰時,給予我許多 寶貴的意見;謝謝一起奮鬥的仁陽、依亭、閔光,有了你們的鼓勵與陪伴才有今 天的我;謝謝實驗室學妹在實驗時給予的幫忙;謝謝宇強學長、紹奇,沒有你們 就沒有我最後的樣品;還要謝謝孟心飛老師與林聖迪老師在論文口試時所給予的 指導。最後,我要感謝一路支持我的家人,感謝弟弟郁文陪我度過這兩年,不論 精神上或學術上給我鼓勵與幫助;感謝爸爸媽媽這兩年來默默的支持,是我精神 上最大的泉源,讓我能順利完成此學業。謝謝大家!!

僅以此論文獻給我摯愛的父母

目錄

中文摘要...

I英文摘要...

II誌謝...

III目錄...

IV第一章 緒論

………...01 1.1 研究動機……….…..01 1.2 金屬-氧化層-半導體電容器(MOS)………...02 1.2.1 功函數差……….…...02 1.2.2 MOS 能帶與外加偏壓的關係……….…...03 1.2.3 平帶電壓(flat-band voltage)……….……...05 1.2.4 臨界電壓(threshold voltage)……….……….……..06 1.3 相關文獻………...08 1.3.1 以電容偵測器量測氧化層上的捕捉電荷(Trapped charge)………...08 1.3.2 表面電位顯微鏡的應用………..10第二章 實驗儀器與原理………...13

2.1 原子力顯微鏡(Atomic Force Microscopy,AFM)………...………….13

2.1.1 AFM 基本介紹………...13

2.1.2 回饋系統與影像產生原理………....…..15

2.2 表面電位顯微鏡(Kelvin Probe Force Microscopy,KFM)………...18

2.2.2 表面電位顯微鏡之操作架構……….20 2.3 原子力顯微鏡儀器簡介………..22

第三章 樣品準備與實驗裝置………26

3.1 樣品的製程………..26 3.2 切割樣品……….27 3.2.1 樣品的劈開方式……….27 3.2.2 樣品劈開後的表面形貌………28 3.2.2 Si(100),Si(111)與 GaAs(100)的劈開心得………...29 3.3 實驗裝置………..30第四章 實驗結果與分析………....32

4.1 表面形貌(Topography)與表面電位差(CPD)之關係………...32 4.2 MOS 元件 CPD 圖………..344.2.1 樣品(A)Ti – SiO2- P-type silicon………34

4.2.2 樣品(B) Ti-SiO2-n type Si ;(C) Al-SiO2-p type Si; (D) Al-SiO2-n type Si………...…………..36 4.2.3 計算氧化層總有效電荷………...…….40 4.3 MOS 元件加偏壓後的 CPD 圖……….….…....42 4.4 MOS 元件的電場分佈圖………...54

第五章 結論………..………. 56

附錄一 以 KFM 量側 InAs/GaAs QDs……….…..59

附錄二 以 KFM 量側 p-i-n 雷射……….……...61第一章 緒論

1.1 研究動機

金屬-氧化層-半導體(Metal-Oxide-Semiconductor,MOS,金氧半)在半導體元 件物理中佔有極重要地位,更為先進積體電路中最重要之金氧半場效電晶體 (MOSFET)的樞紐。近年來,積體電路製程發展的目標是將元件尺寸縮小至奈米 尺寸,隨之而來的問題有:閘極(Gate),源極(Source),汲極(Drain)所值入載子濃 度大小;高溫退火(annealing)雜質擴散造成的污染;氧化層與半導體介面態 (surface state)影響等等..,皆會影響元件運作的穩定與特性。因此希望能有一種 直觀的工具來偵測元件運作時的實際情況。 目前應用於量測MOS元件的工具大致有下列幾項:以高頻電容偵測器量測 氧化層厚度[1];利用展阻測量(Spreading Resistance Profiling,SRP) 及二次離子 質譜儀(Secondary Ion Mass Spectrometer,SIMS)偵測半導體雜質濃度;以電容偵 測器量測氧化層總有效電荷[2][3];利用掃描電容顯微鏡(Scanning Capacitance Microscopy)直接觀測MOSFET元件上閘極、源極、汲極、氧化層的相對位置[4] 等等。上述量測或觀察 MOS 元件的方法,有些是用來量測 MOS 元件製程的特性; 有些是直接觀察元件上材質的分佈,並無利用表面電位顯微鏡(Kelvin probe force microscopy,KFM)觀測外加偏壓的 MOS 元件電位。因此,我們想利用 KFM 觀 測 MOS 元件剖面,一方面可觀察氧化層-半導體之間的表面態;另一方面在金屬 與半導體間外加一偏壓,簡單的模擬 MOS 元件:閘極-二氧化矽-矽運作時之間 的能帶變化,從其中發現一些有趣的物理現象。

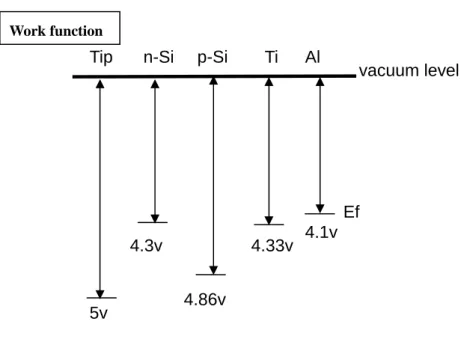

1.2 金屬-氧化層-半導體電容器

金屬-氧化層-半導體的表面結構是金氧半場效電晶體的基礎,其結構圖如 圖 1.1,我們把它視為一電容器。氧化層其實可採用任何一種絕緣層,但由於二 氧化矽與矽半導體的表面結構有許多優良的特性,因此我們以二氧化矽為代表。 圖 1.1 金屬-氧化層-半導體 電容器。 1.2.1 功函數差 金屬,二氧化矽,p 型矽半導體的能帶圖如圖 1.2(a)。其中,金屬的功函數φm 是將電子由費米能階移出金屬外到達真空能階所需的能量。在 MOS 結構中,如 圖二(b),我們必須採用修正的金屬-氧化層功函數 ' 。 是電子從金屬費米能 階到氧化層導帶的能量,相同的, 是電子從矽半導體的費米能階到氧化層導 帶的能量。 m φ ' m qφ ' s qφ 因此我們定義金屬與半導體在 MOS 結構下的功函數差φms為: ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ + + − = − = ) 2 ( ' ' ' ' B g m s m ms e E φ χ φ φ φ φ …………(1) , ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = i a t B n N V ln φ 其中 χ'是修正後矽的電子親合力, q qφB則為費米能階與基板本質能階的能量差。若為 n 型半導體則(1)式φB改為− φB (a)接觸前 (b)接觸後 圖 1.2 金屬-氧化層-p-type Si 能帶圖 1.2.2 MOS 能帶與外加偏壓的關係 以p型矽半導體為例,當我們外加負偏壓Vg<0 於金屬時,金屬的靜電位相對 於半導體的電子電位即較低,因此,金屬的電子位能將被抬升至原本費米能階上 方eV處。由於功函數不會因外加偏壓而改變,所以金屬費米能階往上抬升將會 造成氧化層能帶傾斜角度的改變。以圖 1.2(b)例子來說,當外加小幅負偏壓時, 金屬的費米能階往上抬升,如圖 1.3(a),氧化層能帶傾斜角度變小,半導體與氧 化層接面處(interface)能帶往下彎曲幅度也變小。當外加負偏壓增大,金屬費米 能階持續往上抬升,如圖 1.3(b)半導體與氧化層介面(interface)能帶彎曲方向變成 往上,氧化層能帶傾斜方向也相反。

(a)外加負偏壓 (b)負偏壓增大(堆積 accumulation) 圖 1.3 金屬外加負偏壓 就 p 型半導體來說,當一負偏壓加在金屬上時,半導體與氧化層介面(interface) 將感應出超量的正載子(電洞),此時,接近半導體表面的能帶將會往上彎曲,見 圖 1.3(b)。由我們已知半導體內的載子密度與能差Ei −Efi成指數關係,即 p i Efi Ef kT………..(2) e n p = ( − )/ 半導體表面能帶向上彎曲,使得Efi −Ei變大,半導體與氧化層接面處電洞濃度 提升,形成電洞聚積,此種情況稱之為聚積(accumulation)。 當外加一小量正偏壓Vg>0 於金屬上時,金屬的正電壓吸引一些負電荷到半 導體與氧化層的介面上,造成p型半導體上電洞濃度相對的減少,能帶向下彎曲, 而多數載子(電洞)形成空乏,此種情況稱之為空乏(depletion),如圖 1.4(a)。空乏 區的寬度可由下式表示: 2 / 1 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = a s s eN W ε ϕ …………....….(3) 其中εs為半導體的介電常數,ϕs為半導體表面電位與半導體內部電位之差, 是半導體載子濃度。 a N 當外加一更大的正偏壓時,能帶向下彎曲愈大。倘若基板的本質能階 向 下彎曲越過費米能階,圖 1.4(b),此時正電壓的金屬吸引著超量的負電荷, fi E

f fi E E − <0,則由 kT E E i p fi f e n n = ( − )/ ………….(4) 我們可知在半導體與氧化層介面上,電子濃度 大於本質濃度 ,亦大於電洞 濃度 ,即在介面處產生電子累積現象,形成所謂的 n 通道,此情況稱為反轉 (inversion)。 p n ni p p (a)空乏(depletion) (b)反轉(inversion) 圖 1.4 金屬外加正偏壓 1.2.3 平帶電壓(Flat-Band voltage) 如圖 1.2(b),無加偏的 MOS 元件平衡時半導體接近氧化層的能帶會有彎曲 的現象,所謂平帶電壓就是外加一偏壓抵銷此能帶彎曲。此時,金屬半導體與氧 化層之間並無任何的感應電荷。 影響平帶電壓的因素除了金屬與半導體的功函數差以外,尚有一些存於氧化 層的電荷或由氧化層與半導體之介面態所產生的電荷。大致來說有以下幾種:(1) 氧化層固定電荷 (fixed oxide charge)(2)氧化層捕獲電荷 (oxide trapped charge)(3)移動離子電荷 (mobile ion charge)(4)介面捕獲電荷 (interface trapped charge)。一般來說這些電荷總和是正電荷,在半導體會感應負電荷,平

f

Q Qot

m

ox it m ot f ms FB C Q Q Q Q V =φ − + + + ox o ms C Q − =φ ………(5) 其中Qo代表氧化層中的總有效電荷, ox ox ox d C = ε 表示氧化層的電容。 1.2.4 臨界電壓(Threshold voltage) 由圖 1.4(a),p 型半導體情況下,金屬外加一正偏壓時,存於半導體的多數 載子(電洞)將被排斥,在半導體與氧化層介面附近形成一空乏區,空乏區的寬度 隨著外加正偏壓的增加而增加。當反轉剛開始的時候,能帶向下彎曲為eφB, B s φ ϕ = 。等到正偏壓增大到使半導體表面電子與內部的電洞濃度相當時,能帶 又繼續向下彎曲了eφB,此時ϕs =2φB,此正偏壓稱為臨界電壓(Threshold voltage)。空乏區的寬度有最大值:由(3)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = a B s a s s eN eN W ε ϕ ε φ ……..(6) 此時 MOS 元件上的電荷分布如圖 1.5,其中 max W eN Qd =− a ,QmT +Qo =|Qd |……….(7) 圖 1.5 外加偏壓達臨界偏壓時的電荷分佈圖。

又正向偏壓VG =Vox +ϕs +φms, ox mT ox C Q V = 可推得臨界電壓VT: ms B ox mT T C Q V = +2φ +φ ,由(7)式 ms B ox d C Q Q φ φ + + − =| | 0 2 ,由(5)式 B FB ox d V C Q φ 2 + + = ………..(8)

1.3 相關文獻

此節首先介紹文獻中量測 MOS 元件的方法與量測的特性,接著介紹 KFM 在半導體元件上的應用。本實驗則是以 KFM 為工具,試著量出並解釋 MOS 元 件的一些特性。 1.3.1 以電容偵測器量測氧化層上的捕捉電荷(Trapped charge) H. C. Casey等[2],驗證離子晶格的GaN在介面上比共價晶格的GaAs有較小 的表面態。他們的樣品製作方式是:藍寶石(sapphire)基板上,以 6000 C長 19nm 的GaN,增加溫度至 10500 C,再以2.5µm /h的速度沉澱1.2µm的GaN。然後 3000 C 的溫度下,在GaN上長一層SiO2,最後再鍍 200nm的鋁薄膜當閘極。以電容偵測 器量出電容與閘極電壓之間的關係圖,見圖 1.6。圖 1.6 C-V 曲線(本圖取自 Appl. Phys. Lett. 68,1850(1996)) 由圖 1.6 得知VFB =−2.35v,帶入 1.2.3 (5)式 ox o ms FB C Q V =

φ

− 得氧化層總有效電荷 11 2 0 8.9 10 − × = cm QK. A. Abdulla等[3],是探討製程溫度對表面態的影響。樣品製作方式為: Si(100)基板上以不同溫度(200 and 6000C)長GaN薄膜,在自然的情況下GaN薄膜 上會形成小於 5nm的氧化層。氧化層在製程上有幾個重要的角色,例如:鈍化半 導體表面;讓半導體能選擇區域參雜雜質;為半導體元件絕緣的材料;保護半導 體元件免於環境的污染….等等。接著在氧化層上鍍鋁薄膜當閘級,以電容偵測 器偵測MOS元件的C-V圖,如圖 1.7。由圖 1.7 C-V曲線,得知 2000

C製程的樣品 平帶電壓(flat band voltage)與臨界電壓(threshold voltage)為 1.72v和-4.95v;6000

C 製程的樣品平帶電壓與臨界電壓為-0.65v和-4.01v。在由 1.2.3 (5)式: ox o ms FB C Q V =

φ

− 求出氧化層的總有效電荷,結果為 2000 C製程的樣品 ; 600 2 10 0 2.72 10 − × = cm Q 0 C製程的樣品 。可發現低溫成長的GaN具較小的氧化層總 有效電荷。 2 10 0 2.82 10 − × = cm Q 圖 1.7 以GaN當半導體製成的MOS元件之電容-電壓圖(a)GaN成長溫度 2000C(b)6000C(本圖取自Microelectronic Engineering 81,201(2005) )1.3.2 表面電位顯微鏡的應用

表面電位顯微鏡主要是利用材質間的功函數(work function)差異,量出各材 質與探針的功函數差,判斷其在元件上的分佈。O. Douheret 等[5]利用此特性作 了以下的實驗:以 KFM 觀察 cross-sectional 的 InGaAs/InP QWs。圖 1.8(a)兩條 比較亮的即是 InGaAs 量子井,其中 QW1 寬度 20nm;QW2 寬度 5nm。周圍較 暗的即是 InP。由圖 1.8(b)可看出 InGaAs 與 InP 的 CPD 差為 230mV。

圖 1.8 用 KFM 所量測的 InGaAs/InP QW 圖中有兩個 QWs(a)是 CPD 圖 ( )(b)是取單一條的電位圖。(本圖取自 Appl. Phys. Lett. 85,5245(2004)) mV CP=230 ∆ 我們也針對這個特性,作了 InAs/GaAs QDs 的 CPD 量測,見附錄一。 除了儀器直接量測的 CPD 圖外,把量到的 CPD 曲線對掃描位置 x 軸作一次 維分,得到電場對掃描位置的相對圖。利用電場的分佈來探討各材質的分佈位置 也是一個很有效的工具,此方法可以明顯的看出材質與材質的交接面。F. Ronin 等[6]以 KFM 來量測 p-i-n 雷射,所使用的樣品為 n-doped InP substrate;intrinsic InGaAsP 220nm;p-doped InP,把樣品剖開其地勢高低圖見圖 1.9。 圖 1.10 是量

測的 CPD 圖,由圖(a)可發現 n 的電位比 p 的電位高了 600mV,i 的區域並不明 顯。圖 1.10(b)是沿 A-A”作電位對位置的一次微分得到電場分佈圖,此圖有 peak 的地方即是材質間的交接面,可明顯的看出中間有兩個 peak,peak 與 peak 間 220nm 即是 intrinsic InGaAsP。此方法是利用各材質的電位曲率不同判斷出交接 面。

圖 1.9 AFM 量測樣品 p-i-n laser 的地勢高低圖(本圖取自 Appl. Phys. Lett. 76,2907(2000))

圖 1.10 用 KFM 量測 p-i-n 雷射的 CPD 圖(a)電位圖(b)由位置 A~A”的電場圖。(本 圖取自 Appl. Phys. Lett. 76,2907(2000))

接著,R. Shikler 等[7]以 KFM 量測作用中的 p-n 二極體。即是在樣品正反面 鍍金屬薄膜當電極,改變外加偏壓且同時量測 CPD 的變化。實驗方法如圖 1.11, 實驗結果如圖 1.12。很明顯的看到 CPD 值隨外加偏壓改變而升降,利用此種特 性,可以觀測許多的物理現象。例如,圖 1.12 外加偏壓為 1.66v 時,n 與 p 的電 位近乎相同,可知 1.66v 即是 p-n 二極體的自建電位差(built-in potential)與表面態 的總合。自建電位差可由理論計算求出,即可得到因表面態所影響的電位值。 圖 1.11 以 KFM 量測外加偏壓的 p-n 二極體(本圖取自 J. Appl. Phys. 86,107(1999)) 圖 1.12 p-n 二極體在外加九個不同偏壓時的電位分佈圖(本圖取自 J. Appl. Phys. 86,107(1999))

第二章 實驗儀器

2.1 原子力顯微鏡(Atomic Force Microscopy,AFM)

2.1.1 AFM 基本介紹

自 1986 年 G. Binnig,C.F. Quate 和 C. Gerber 發明掃描探針顯微術後,一系 列的掃描技術就陸續衍生出來,原子力顯微鏡(Atomic Force Microscopy,AFM) 即是其中的一種。AFM 是以探針原子與表面原子間的交互作用力來量測表面特 性。在實驗操作時,通常是保持一定作用力的大小,使探針與表面的間距固定。 如此一來,掃描時,利用掃描器垂直微調能力和回饋電路,所記錄的探針移動高 度即為樣品表面的地勢高低(topography)。 AFM 的微小探針通常是黏附在懸臂上,當探針尖端與樣品表面接近時,因 力場而產生作用力,造成懸臂的彎曲。此彎曲量 x 可由雷射聚焦在懸臂頂端後, 反射至光偵測器(PSPD),再由 PSPD 接收到的雷射光點位置變化換算成表面與探 針間的作用力 F=kx,如圖一所示。 圖 2.1 AFM 雷射光反射途徑與光偵測器。雷射光經懸臂反射至光偵測器上。

依操作模式可分為 (a)接觸式(Contact Mode) 當探針與表面相當接近時(大約幾埃的距離),探針所感受到的是排斥力(如圖 二),此為接觸模式。接觸模式下,探針直接接觸到樣品表面並使懸臂稍微彎曲, 我們只要利用回饋電路固定此彎曲量,便可得到表面的高低起伏。 (b)非接觸式(Non-contact Mode) 探針與表面維持一固定的距離(數十到數百埃),利用探針尖端原子與樣品表面 原子之間的長程吸引力(凡德瓦爾力)來運作。凡德瓦爾力對距離變化的敏感度很 小,所以必須使用調變技術來增強訊號雜訊比。雖然此方法解析度並沒有接觸式 的好,但卻改進了接觸式可能刮傷樣品或是損傷探針的缺點。 (c)輕敲式(Tapping Mode) 輕敲式是介於接觸與非接觸之間的模式,解析度比非接觸式好,又較接觸式不 會傷害樣品表面。其原理是較非接觸式靠近表面,且加大振幅,使探針在震盪至 波谷時輕敲樣品,由於樣品表面的高低起伏,使懸臂振幅改變,再利用回饋裝置 取得樣品高度影像。 圖 2.2 樣品表面與探針針尖之間的交互作用力圖。當樣品與針尖相距約幾埃的距 離,懸臂受力為排斥力,此為接觸模式;當樣品與針尖距離數十到數百埃時,懸 臂受力為吸引力,此為非接觸式。

2.1.2 回饋系統與影像產生原理 本實驗是以輕敲式(Tapping Mode)為主,以下詳細介紹輕敲式的影像產生原 理。探針遠離表面作自由震盪時,有一自然共振頻率ω0,在此ω0下振幅有極大 值。操作時探針被一震盪器驅動,並以一略小於ω0的頻率ω作震盪(如圖 2.3: kHz 72 . 259 = ω ),由簡單的模型可知 * * m k = ω 。探針靠近表面因作用力的關係使 改變。若作用力為吸引力則 變小, * k k* ω也跟著變小;相反的,若作用力為斥 力則 *和 k ω皆變大。 如圖 2.4,當探針接近表面並產生吸引力時,頻率曲線往左移,ω0左側的 頻率ω所對應到的振幅值隨之變大。因此只要控制此∆Α保持固定,即可使探針 和表面保持固定的吸引力,再藉由回饋系統,便可得到表面的形貌。 圖 2.3 懸臂振幅、相位與驅動頻率的關係圖。驅動器以ω頻率震盪時,探針的響 應頻率為 259.72kHz,此時振幅有最大值,相位為 0 度。(本圖取自 D3100 Manual)

圖 2.4 探針頻率曲線圖(本圖取自 D3100 Manual) 接下來介紹,如何偵測懸臂產生的微小位移。 光偵測器通常分為四部份,當雷射光反射至光偵測器時,藉由比較光在各區 域的強度,即可以精確的量出懸臂的位移。以圖 1.1 為例,當懸臂有 z 方向位移 時,雷射光點將會上下移動,此位移量可由(A+B)-(C+D)的訊號獲得;當懸臂有 t 方向的位移時,雷射光點會左右移動,位移量則由(A+D)-(B+C)的訊號獲得,其 中 A+B+C+D 的值是保持不變的。 光偵測器(PSPD)在接收到訊號差值後,將訊號值傳至鎖相放大器,鎖相放大 器濾出其與原先驅動懸臂震盪相同頻率的 AC 值,經過一 AC/DC 轉換器,輸出 一 DC 值,接著此 DC 值將與我們所設定的 set point 值產生一誤差值,此誤差 值將會送到 Z Piezo 作回饋控制。藉由 Z 軸的起伏,使懸臂震盪振幅保持一定, 將可得到樣品的高度變化圖,整個線路如圖 2.5。

2.2 表面電位顯微鏡(Kelvin probe force microscopy,KFM)

表面電位顯微鏡(KFM)是原子力顯微鏡(AFM)的一個應用。偵測時分為兩個 步驟。第一步驟是上一節所提到的:量測樣品表面的地勢高低;第二步驟是:探 針依據表面的地勢高低同時抬高一定的距離(如圖 2.6),再利用外加的 AC 和 DC 電壓與回饋的裝置,測量出探針與樣品表面的表面電位差,以下是詳細的介紹。 2.2.1 表面電位顯微鏡原理 產生靜電力的基本架構是:探針-空氣-樣品表面,把它當成一平行電容板的 模型。平行電容板的 energy U 為: 2 ) ( 2 1 V C U = ∆ ………..(1) 其中 是探針與樣品表面的電位差,C 為探針與樣品之間的電容值。探針與樣 品之間電容力與距離 z 的關係可表示為: V ∆ ( )2 2 1 ) ( V z C z U z F ∆ ∂ ∂ − = ∂ ∂ − = ……….(2) 探針與樣品表面的電位差包含 AC 和 DC 項 ∆V =∆Vdc +∆Vacsinω1t………...(3) 其中ω1是我們所給交流電壓的頻率,將(3)式帶入(2)式,可得: 2 1 ) sin ( 2 1 ) ( V V t z C z F ∆ dc +∆ ac ω ∂ ∂ − = t V z C t V V z C V V z C t V V t V V V z C t V t V V V z C ac ac dc ac dc ac dc ac ac dc ac ac dc dc 1 2 1 2 2 1 1 2 2 2 1 2 1 2 2 cos 4 1 sin ) 2 1 ( 2 1 ) sin 2 2 cos 2 1 2 1 ( 2 1 } ) (sin sin 2 { 2 1 ω ω ω ω ω ω ∆ ∂ ∂ + ∆ ∆ ∂ ∂ − ∆ + ∆ ∂ ∂ − = ∆ ∆ + ∆ − ∆ + ∆ ∂ ∂ − = ∆ + ∆ ∆ + ∆ ∂ ∂ − = ^^^^^^^^^^^^^^^^^^^^^ ^^^^^^^^^^^^^^^^^ ^^^^^^^^^^^^^^^^^ (A) (B) (C)上式,電容力由三項組合而成。(A)與交流頻率無關,(B)與交流頻率ω1有關,(C) 與兩倍的交流頻率2ω1有關。 表面電位顯微鏡與(B)項有關,利用鎖相放大器濾出ω1項的訊號值,懸臂的 振幅關係式為: ac dc V V z C A ∆ ∆ ∂ ∂ − = …………..(4) 其中∆Vdc是探針與樣品的表面電位差,用VCPD來表示∆Vdc。 e VCPD tip sample − − =φ φ …………..(5) 因此我們只要利用回饋電路,加一直流電壓 於探針上,使得後來的 CPD 值 ,A 即等於零。記錄 即可得到探針與樣品的表面電位差,關係式如 下: ext V 0 = CPD P V Vext ext sample tip CPD P V e V + − − =φ φ =VCPD +Vext….(6) 又 VPCPD =0 即 e V

Vext =− CPD =φtip −φsample ……….…(7) 因此我們儀器所量到的值Vext是探針的功函數減去樣品的功函數。

2.2.2 表面電位顯微鏡之操作架構 本實驗所使用的儀器,在量測表面電位時,是以 Lift Mode 的形式(如圖 2.6)。 Lift Mode 包含以下幾個步驟。 首先,懸臂經由一震盪器產生接近自然共振頻率ω的震動,量測樣品表面地 勢。接著,關閉作用於懸臂的回饋系統,並將懸臂檯高一固定的距離 d,依照先 前所記錄的地勢高低行走,此時樣品與探針的距離皆保持固定 d。同時,在懸臂 上外加一交流電壓Vacsinω1t(本實驗所使用的儀器,外加交流電壓的頻率ω1與ω 是相同的)與直流電壓Vext,整個系統如圖 2.7。 圖 2.6 Lift Mode 的步驟圖。第一步驟:量測表面地勢,第二步驟:探針依表面地 勢抬高依固定距離。(本圖取自 D3100 Manual)

圖 2.7 KFM 的線路圖。如同 2.2.1 節(4)式,鎖定ω1項的訊號,振幅的關係式 ac dc V V z C A ∆ ∆ ∂ ∂ − = 此時探針與樣品的 DC 電壓差為原本的∆Vdc再加上外加的直 流電壓 ,調整 使得 A=0,記錄 我們即可得到樣品與探針的接觸電位差

(Contact Potential Difference)。(本圖取自 D3100 Manual) ext

2.3 原子力顯微鏡儀器簡介

本實驗所使用的原子力顯微鏡機台為Digital Instruments的DimensionTM 3100。在組成上可分為四個架構:(a)NanoScope Ⅲa Controller (b)Dimension 3100 Controller (c)Computer (d)Dimension 3100 SPM,如圖 2.8 所示

(a) NanoScope Ⅲa Controller (d)Dimension 3100 SPM (b) Dimension 3100 Controller

(c) Computer

圖 2.8 D3100 的基本組成(本圖取自 D3100 Manual)

其中(a) NanoScope Ⅲa Controller 主要是控制顯微鏡掃描,(b) Dimension 3100 Controller 主要是控制機台真空、空氣補給和光學照明,(c)Computer 主要是用來 連接各機台,與軟體的控制,(d) Dimension 3100 SPM 是整個儀器的主體,將於 下述詳細介紹。

圖 2.9 Dimension SPM Head 的結構與雷射反射位置(本圖取自 D3100 Manual) Dimension SPM Head 有以下幾個結構

Preamp Board

Preamp Board 包含一個電流放大器,提供光偵測器與雷射光電源。且提供一 電壓±12v 來控制電流在一個安全的範圍。

Laser Diode Stage

雷射二極體發光後經由聚焦射到下方探針的懸臂,圖 2.9 上方的兩顆調節紐 即是控制發光二極體位置的 X 與 Y 方向,使得雷射光精準的打到探針懸臂背面 所鍍的反射面上。

Adjustable Detector Mirror

Photodetector 雷射光反射的終點是四個正方形的光偵測器,如圖 2.10,此四個光偵測器將 會隨著不同的量測模式,轉換不同的訊號。在所有的模式中,四個偵測器所接收 的總光強度是固定的。上兩個光偵測器與下兩個光偵測器所接受到光強度值的差 值是反應懸臂上下震盪,為 Contact mode 所直接使用的。若把此差值再輸入一 RMS 轉換器,則可轉換成 Tapping mode 所需要的訊號。相同的,左邊兩個光偵 測器與右邊兩個光偵測器所接收到的光強度差值,是反應懸臂所受的扭力,通常 使用在 Later Force Microscopy 上。

圖 2.10 四個矩形的光偵測器,與其反應的訊號(本圖取自 D3100 Manual) Scanner Piezo Tube

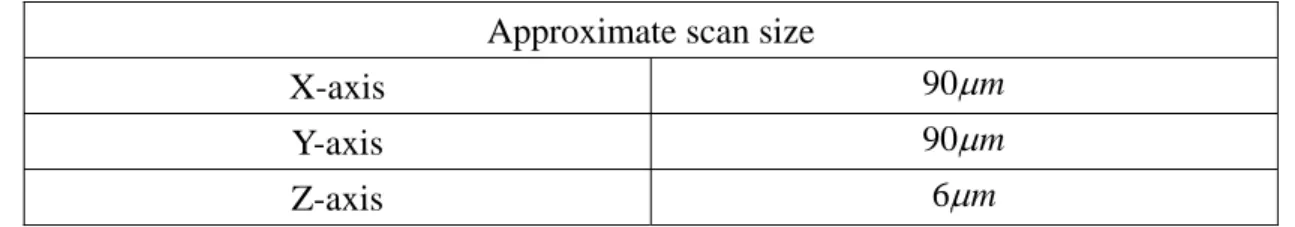

位於 Dimension SPM Head 的掃描器是由 5 片陶瓷壓電材料作成,如圖 2.11, 其中兩片控制 X 方向,兩片控制 Y 方向,最下方一片圓柱狀的則是控制 Z 方向。 各方向所能最大延伸的範圍如表 2.1。

Approximate scan size

X-axis 90µm

Y-axis 90µm

Z-axis 6µm

第三章 樣品準備與實驗裝置

本實驗的目的是藉由表面電位顯微鏡,觀測外加電壓下 MOS 元件的能帶變 化,因此我們需要在樣品的上下兩面鍍上電極,再外接電源供應器。並將樣品劈 開觀測樣品的剖面,以下是樣品準備與實驗方式的詳細介紹。3.1.樣品的製程

本實驗所使用的樣品是在 n-type( )與 p-type( ) Si 上以 Wet-Oxidation 長上一層氧化層,再以熱蒸鍍與電子槍蒸鍍方式在氧化層上方鍍 約 250nm 的金屬,樣品背面亦熱蒸鍍上約 20nm 的金屬當電極。共四組樣品 (A)Metal:Titanium;Oxide:SiO2(500nm);Silicon:p-type (B) Metal:Titanium; Oxide:SiO2(150nm);Silicon:n-type (C) Metal:Aluminum;Oxide:SiO2(500nm); Silicon:p-type(D) Metal:Aluminum;Oxide:SiO2(150nm);Silicon:n-type。14 10 7 . 1 × = d N Na =1015

Sample (A) Sample (B)

Sample (C) Sample (D)

圖 3.1 樣品圖(A)Ti – SiO2- p type silicon(B) Ti-SiO2-n type Si (C) Al-SiO2-p type Si (D) Al-SiO2-n type Si

3.2 切割樣品

3.2.1 樣品的劈開方式 樣品的切割分兩個步驟,劃線跟折。用鑽石筆劃割樣品表面,劃的長度約為 樣品長度的三分之一到二分之一(因為我們要觀察的區域是接近表層的,所以不 能全劃)。折的方面分為拉力面跟壓縮面,拉力面比較容易得接近表面平坦的小 塊區域,壓縮面則容易有一層層密集的 step 或是垂直表面的裂痕。見圖 3.4。 劃線區 壓縮面 拉力面(觀測區域) 圖 3.4 剖開後的樣品側面圖。左下方是鑽石筆劃割的地方,圖的下方是拉力面, 上方式壓縮面。可發現壓縮面的一層層密集 ,拉力面 右下 有較為平坦的區 域。 兩種 樣品下面墊一跟針或是尖細的棒子,將劃痕對準針,兩跟扁平夾壓著 sample 。 step ( ) 折的方法有 (1) 兩邊,等平衡後在慢慢順勢往下壓,如圖 3.5Force Force 樣品 劃線位置 針 圖 3.5 剖樣品的第一種方法 (2)在樣品表面劃一個深短的刻痕,夾子沿著刻痕方向夾緊,用另一跟尖嘴夾平 推樣品到斷裂。 圖 3.6 剖樣品的第二種方法 3.2.2 樣品劈開後的表面形貌 經由上述方法切割後的樣品有下列特徵:拉力面會有一塊表面較為平坦的地 區,可供觀察表面用。此區域通常出現在距離鑽石筆劃線處較遠的地方,如圖 3.7,將觀測區域(平坦區域)放大,發現平坦的表面仍有一些細紋,離切割處越遠, 細紋越少。因此,本方法所使用的樣品寬度最好大於 0.5 公分。此外,在純水中 處理樣品亦可將表面細紋的情況減低,因為純水能降低折樣品時,樣品所受的硬 力(stress field)。

放大 表面細紋 圖 3.7 切割後的樣品剖面。可發現越接近鑽石筆劃線處表面細紋越多。 3.2.3 Si(100),Si(111)與 GaAs(100)的劈開心得 我們試過幾種樣品的切割,以下是一些樣品的切割心得。 (1) Si(100)

Si(100)劃線方向與 flat 方向[110]平行或垂直,因為鍵結的關係,會延 dimer row 的方向裂(即平行或垂直 flat 方向)。 (2) Si(111) Si(111)劃線方向則是要與 flat 面[1-10]夾 30 度或 150 度,因為原子的排列方式是 類似菱形的 7x7。 (3) GaAs(100) GaAs(100)較脆,所以劃線時不能太用力,否則會整個裂成許多片,其餘與 Si(100) 相同。

3.3 實驗裝置

樣品剖開後分別在樣品表面和背面兩端金屬處用石墨膠黏上漆包線,接上電 源供應器,如圖 3.2,並將樣品放置可供樣品直立的裝置上。將剖好的樣品放於 KFM 觀測,掃描時探針與樣品的相對位置為圖 3.3。圖中較亮的區域是樣品,由 中央開始往上是金屬-氧化層-矽。右方黑色長條狀為探針,掃描方向是與樣品表 面夾 90 度。 圖 3.2 實驗裝置圖圖 3.3 實驗時探針,樣品的相對位置圖。圖右方黑色長條狀的是探針,圖較亮的 區域是樣品,由圖中間亮的地方開始往上是金屬-氧化層-矽。

第四章 實驗結果與分析

4.1 表面形貌(Topography)與表面電位差(CPD)之關係

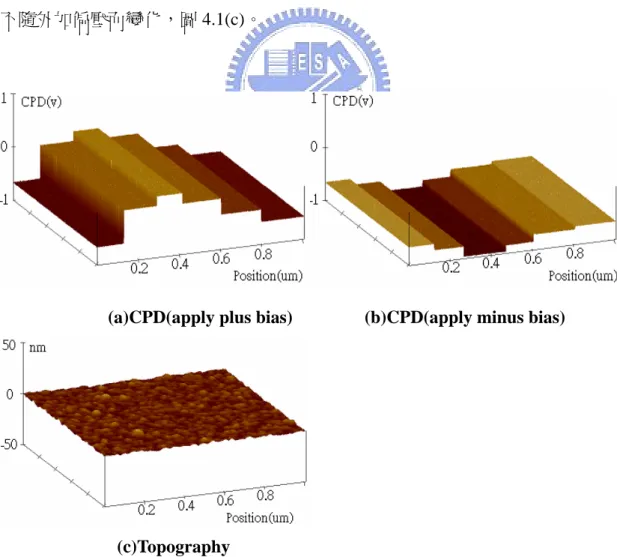

為了正確量測 Tip 和樣品之間的 CPD 差值,與證明靜電力和地勢的訊號是 無關的,首先做以下的量測。外加一可調整的正負偏壓到鉑(Pt)薄膜上(Si 基板蒸 鍍 50nm Pt 薄膜),用 KFM 同時量出 CPD 與 Topography 圖,見圖 4.1。圖 4.1(a) 是 Pt 薄膜加正偏壓,由位置 0 mµ 至 1 mµ 依序為 0v,0.62v,0.80v,0.61v,0.30v, 0.09v。圖 4.1(b)是 Pt 薄膜外加負偏壓,依序為-0.11v,-0.31v,-0.19v,-0.05v, 0v。可發現當無外加偏壓時,Tip 與 Pt 薄膜的 CPD 差值為-0.65v,已知 Pt 薄膜 的功函數(work function)為 5.65v,可知使用的 Tip (CoCr)功函數約為 5v。當外加 正偏壓時 CPD 值是增大的,負偏壓時是減小的。同時量測的 Topography 圖,並 不隨外加偏壓而變化,圖 4.1(c)。(a)CPD(apply plus bias) (b)CPD(apply minus bias)

(c)Topography

外加負偏壓的 CPD 圖,外加負偏壓越大,CPD 值越小。(c)Pt 薄膜的地勢高低圖, 不隨外加偏壓改變而變。 由第 2.2.1 節(6)式: ext sample tip CPD P V e V + − − =φ φ =VCPD +Vext 當外加偏壓Vmetal於樣品(金屬)時,相當於外加−Vmetal於探針上,因此上式可表示 為: metal ect sample tip CPD P V V e V + − − − =φ φ =VCPD +Vext −Vmetal

即 tip sample metal metal CPD ext V e V V V =− + =φ −φ +

4.2 MOS 元件 CPD 圖

4.2.1 樣品(A)Ti – SiO2-p type silicon 的 CPD 圖

圖 4.2 是(A)樣品的剖面,在無外加偏壓下所量測的圖形。(a)是樣品剖開後 表面形貌高低圖。剖開樣品時,金屬區域的斷面會有約 200nm 的突起,這並不 影響量測的 CPD 值,因為我們所使用的方法是 Lift Mode,在量測 CPD 值時, 探針與樣品皆會保持一定的距離(30nm)。

圖 4.2(b)是 MOS 元件無加任何偏壓下,平衡後的表面電位圖。圖中右邊較 亮的區域是 Ti 薄膜,左邊較暗處是 p-type Si,為了仔細觀察平衡時 MOS 元件的 能帶,取其中一條電位,見圖 4.3。

(a)Topography (b) CPD

圖 4.2 樣品 A 的剖面圖(a)地勢高低圖,由右邊看起是金屬-氧化層-矽,金屬的部 份凸起約 200nm。(b)CPD 圖,金屬的 CPD 值較 p-type 矽高。

Potential Distribution(P-type)(Metal:Ti) Distance (um) 0 1 2 3 4 CPD (v) 0.10 0.12 0.14 0.16 0.18 0.20 0.22 0.24 p-type Si SiO2 Ti 圖 4.3 樣品(A)無外加偏壓下的電位圖。由圖可發現 Ti 薄膜的表面電位比 p-type Si 高了 0.07v。 將樣品(A)以實際製程分三個區域,圖 4.3 由右邊看來 Ti 薄膜約 200nm;SiO2 約 500nm;接著是 p-type Si。可發現 Ti 薄膜的表面電位比 p-type Si 高了約 0.07V, 在 SiO2層電位是傾斜的,SiO2-Si 介面處因介面電荷或表面態而有稍微能帶彎曲 的現象。 由理論計算 Ti 薄膜與 p-type Si Bulk 功函數差為: v s m ms B 53 . 0 86 . 4 33 . 4 − =− = − =φ φ φ 而實驗所量到的表面電位差為: ,兩者的差異主要原因有:(1)半 導體的表面態,(2)存在樣品表面的外部電荷。因製程污染、切割樣品造成的缺 陷或是樣品受空氣氧化造成的表面態會捕捉一些電洞或電子在切割的表面上,這 些電洞或電子會在半導體上感應出一電荷,造成表面能帶的彎曲,形成實驗所量 到的數值與實際值不同。 v ms S 07 . 0 − = φ

4.2.2 樣品(B) Ti-SiO2-n type Si ;(C) Al-SiO2-p type Si ;(D) Al-SiO2-n type Si 的 CPD 圖 相同地,量出樣品(B)、(C)、(D)無加偏壓下的 CPD 圖,如圖 4.4。可發現探 針相對樣品的功函數差因 p-type、n-type、鈦或鋁有明顯的差異。圖 4.5 是各材質 Bulk 功函數相對圖,由 2.2.1(7)式,儀器所讀取的 CPD 訊號Vext為: ( ) e V

Vext CPD tip sample − − − = −

= φ φ ………(for feedback on tip)

Tip 與 n-type Si 的功函數相差較 p-type Si 大,因此 值較 p-type Si 大,在 CPD 圖形上顯示較高。同理,Al 的功函數皆較 n-type,p-type Si 小,與 Tip 的功函數 相差較大,CPD 圖形上為較高。而在(B)樣品中 Ti 與 n-type Si 功函數相差甚近, Ti 比 n-type Si 大了 0.03v,照理說 Ti 的 值應比 n-type Si 小,CPD 圖形應為較 低,但實驗所量測到卻是 Ti 的 值較高,這應是表面態所造成表面能帶彎曲的 影響,下面將會討論。 ext V ext V ext V CPD of Different Material Position (um) 0 1 2 3 4 CPD (v) -0.2 0.0 0.2 0.4 0.6 (D)n-type Si-SiO2- Al

(B)n-type Si-SiO2 -Ti

(A)p-type Si-SiO2-Ti

(C)p-type Si-SiO2-Al

圖 4.4 樣品(A)、(B)、(C)和(D)的 CPD 圖,由圖可知,就 p-type 與 n-type Si 而言, 探針相對於 p-type Si 功函數較小,p-type Si CPD 值較 n-type Si 低。就 Al 與 Ti

Tip Work function p-Si n-Si Ti Al vacuum level Ef 4.1v 4.3v 4.33v 4.86v 5v 圖 4.5 各材質的功函數圖。 我們只單純探討金屬與半導體表面態的關係,因此將圖 4.4 四條曲線 Si 部分 的功函數值設為與 Tip 相同,如圖 4.6。理論計算的金屬與半導體功函數差φms與 實驗所獲得的表面電位差φSms整理於表 4.1。 Distance (um) 0 1 2 3 4 CPD (v) -0.2 0.0 0.2 0.4 0.6 (C)p-type Al (A)p-type Ti (D)n-type Al (B)n-type Ti CPD of Different Material 0.63 0.36 0.07 0.03

(A)Ti -SiO2- p-type Si (B)Ti -SiO2- n-type Si (C)Al -SiO2- p-type Si (D)Al -SiO2- n-type Si ms S φ (v) -0.07 -0.03 -0.63 -0.36 ms φ (v) -0.53 +0.03 -0.76 -0.2 表 4.1 各樣品φSms與φms比較表。 由表 4.1 發現 p-type Si 的φms- <0,此表示 p-type Si 表面因表面態關係的 能帶彎曲方向是減低與金屬的功函數差。相反的,n-type Si 的 ms S φ ms φ - >0 表示 n-type Si 表面能帶彎曲方向是增加與金屬的功函數差。我們試著由圖 4.7 解釋 p-type Si 之現象。 ms S φ

Evac Evac Ec Efi Ef Ev Ef Ti SiO2 p-type Si (a) MOS 元件的能帶圖 Ef

(b) )Tip 與 Ti 薄膜之間的能帶圖 (c)Tip 與 p-type Si 之間的能帶圖

)受表面態影響後的 4.7 樣品(A)的能帶圖。(a)MOS 元件的能帶圖,CPD 值為 Ti 薄膜功函數減去 功函 : , 金 薄膜 之間的 值為 , 與 之間的能帶圖, 功函數大於 p 縱合 元件 2介面能帶往下彎曲 與 與 介面能帶往上彎曲,所得到的實驗數 ,可看出 抵銷了 許多 量側值由原本的 減為 。 (d MOS 元件能帶圖 圖

p-type Si 數 4.33v - 4.86v =-0.53v (b)Tip(CoCr)與樣品 屬(Ti )

能帶圖,CPD Tip 功函數減去 Ti 薄膜功函數:5v-4.33v=0.67v (c)Tip p-type

Si 可明顯的看到因 Tip p-type Si,因此 Si 與 Ti 介面

的能帶因表面態而往上彎曲,(d) (a)MOS Si 與 SiO (c) Tip Si 據能帶圖 (c) (a)的貢獻,造成 CPD -0.53v -0.07v Ef Ti SiO2 p-type Si Evac Ec Efi Ef Ev Ef

Tip(CoCr) air p-type S Ec Efi i Ev Ef Evac Tip(CoCr air Ef Evac Evac Evac Ti Evac

4.2.3 計算氧化層總有效電荷

在 MOS 元件上加一偏壓,抵消金屬與半導體的功函數差和表面態造成的能 帶彎曲,即可得到一平坦的能帶,如圖 4.8(c)、圖 4.10(c)、圖 4.12(b)、圖 4.14(c)。 每個樣品的平帶電壓為:(A)Ti-SiO2-p type Si 平帶電壓-0.71volt,(B)Ti-SiO2-n type Si 平帶電壓-0.34volt,(C) Al-SiO2-p type Si 平帶電壓-0.97volt,(D) Al-SiO2-n type Si 平帶電壓-1.69volt。 利用第一章(5)式: ox o ms FB C Q V =φ − 來計算氧化層的總有效電荷Qo。 (A) Titanium-SiO2-p type Si

已知:φBms =−0.53v,VFB =−0.71v, d C ox ox ε = ,d =500nm ox ox d Q C Q ε0 0 53 . 0 53 . 0 71 . 0 =− − =− − − 2 9 2 9 7 14 10 8 . 7 / 10 24 . 1 10 500 10 85 . 8 9 . 3 18 . 0 − − − − × = × = × × × × = coul cm cm Qo (B)Titanium-SiO2-n type Si 已知:φBms =0.03v,VFB =−0.34v, d Cox ox ε = ,d =100nm ox ox d Q C Q ε 0 0 03 . 0 03 . 0 34 . 0 = − = − − 2 10 2 8 7 14 10 8 / 10 28 . 1 10 100 10 85 . 8 9 . 3 37 . 0 − − − − × = × = × × × × = coul cm cm Qo (C) Aluminum-SiO2-p type Si 已知:φBms =−0.76v,VFB =−0.97v, d Cox ox ε = ,d =500nm

ox ox d Q C Q ε 0 0 76 . 0 76 . 0 97 . 0 =− − =− − − 2 9 2 9 7 14 10 9 / 10 45 . 1 10 500 10 85 . 8 9 . 3 21 . 0 − − − − × = × = × × × × = coul cm cm Qo (D) Aluminum-SiO2-n type Si 已知:φBms =−0.2v,VFB =−1.69v, d Cox ox ε = ,d =100nm ox ox d Q C Q ε 0 0 2 . 0 2 . 0 69 . 1 =− − =− − − 2 11 2 8 7 14 10 2 . 3 / 10 1 . 5 10 100 10 85 . 8 9 . 3 49 . 1 − − − − × = × = × × × × = coul cm cm Qo 將上列數據歸納於表 4.2 (A)Ti -SiO2- p-type Si (B)Ti -SiO2- n-type Si (C)Al -SiO2- p-type Si (D)Al -SiO2- n-type Si FB V (v) -0.71 -0.34 -0.97 -1.69 ) (cm−2 Qo 9 10 8 . 7 × 8×1010 9×109 3.2×1011 表 4.2 各樣品的平帶電壓與氧化層總效電荷 一般來說,SiO2裡所存在的總有效電荷約為 左右[8][9]。對照本實 驗所量得的數據,n-type Si 的兩個樣品(B)(D)是接近這個數據的,而 p-type Si 的 兩個樣品確有段差距。其原因是 n-type Si 是本實驗室自己製程的,因此確定載 子濃度是 ,而 p-type Si 是別實驗室提供的,並不確實知道載 子濃度,我們是假設 求得上述的値,所以會有誤差,下一章(第五 章)將會討論修正的方法。 2 11 10 cm− 3 14 10 7 . 1 × − = cm Nd 3 15 10 − = cm Na

4.3 MOS 元件加偏壓後的 CPD 圖 (a)Vg =−7v (b)Vg =−3.02v (c)Vg =−0.71v (d)Vg =0v (e)Vg =+0.29v (f)Vg =+1.2v (g)Vg =+1.5v (h)Vg =+2.1v

-0.70v,0v,+0.29v,+1.20v,+1.50v,+2.10v 的 CPD 圖。可以很明顯觀察到當 外加偏壓於金屬為負時,金屬的 CPD 值會慢慢減小;相反的,若外加偏壓為正 值,金屬的 CPD 值會變大。 圖 4.8(a)(b)是所謂的積聚現象,當積聚現象產生時,CPD 值對外加偏壓的敏 感度並不大。圖 4.8(e)(f)(g)是所謂的空乏現象,當 時,CPD 值對外加偏壓 非常的敏感。為了明確的觀察空乏區的寬度,取每一個 CPD 圖形的 profile 於圖 4.9。 0 > g V Potential Distribution(P-type)(Metal:Ti) Distance (um) 0 1 2 3 4 CP D (v) 0.0 0.5 1.0 1.5 2.0 Vg 2.70v 2.40v 2.10v 1.80v 1.50v 1.20v 0.91v 0.60v 0.29v 0v -0.33v -0.71v -1.05v -3.02v -5v SiO2 Ti p-type Si Depletion Region 1.5 mµ 1.8 3.3

圖 4.9 樣品(A) Ti-SiO2-p type Si 隨著外加偏壓變化的電位分佈圖

將樣品(A)以實際製程分為三個部分(圖 4.9):我們定義 Distance 0 mµ 是樣品 表面深入 4 mµ 的位置。從圖 4.9 右邊看起,金屬 Ti 薄膜約 200nm;氧化層 SiO2 約 500nm;後面接著是 p-type 的 Si。V 是外加於金屬的偏壓。大致可看出金屬

的能帶是平的,氧化層能帶是傾斜的,而在金屬與氧化層介面;氧化層與矽介面 皆有能帶彎曲的現象。隨著 增大, p-type Si 的主要載子(電洞)被排開半導體 表面,空乏區產生,能帶在距離為 1.8 g V m µ 時即不會彎曲,因此空乏區最大寬度約 是 1.5 mµ 。 空乏區最大寬度理論計算為: 由 1.2.4 節(6)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = a B s a s s eN eN W ε ϕ ε φ

已知:Si dielectric constant =11.7,Na =1015cm−3 ,φB =0.29v

得:W 0.86µm 10 10 6 . 1 28 . 0 10 85 . 8 7 . 11 4 1/2 15 19 14 max ⎟⎟ = ⎠ ⎞ ⎜⎜ ⎝ ⎛ × × × × × × = − − 當Vg大於 1.8v 時,能帶有上升較快的趨勢,推測是反轉產生,n 通道形成。 臨界電壓理論計算為: 由 1.2.4 節(8)式 FB B ox d T V C Q V = + +2φ 已知: VFB =−0.71v 2 8 5 15 19 max / 10 36 . 1 10 5 . 8 10 10 6 . 1 cm coul W eN Qd a − − − × = × × × × = = 2 9 8 14 / 10 9 . 6 10 5000 10 85 . 8 9 . 3 cm F d C ox ox − − − × = × × × = =ε 得 84 . 1 29 . 0 2 71 . 0 10 9 . 6 10 36 . 1 9 8 = × + − × × = −− T V v

(a)Vg=1.59v (b)Vg=0v

(c)Vg=-0.34v (d)Vg=-0.60v

(e)Vg=-0.90v (f)Vg=-1.50v

(g)Vg=-2.10v (h)Vg=-2.7v

圖 4.10(a)~(h)是樣品(B) Ti -SiO2- n-type Si 依序加偏壓 1.59v,0v,-0.34v,-0.60v, -0.90v,-1.50v,-2.10v,-2.70v 的 CPD 圖。與(A)樣品不同的地方是半導體的部

變化量並不敏感。當Vg <0時產生空乏現象,CPD 值對外加偏壓則非常的敏感。 Potential Distribution(N-type)(Metal:Ti) Distance (um) 0 1 2 3 4 CP D (v) -1.5 -1.0 -0.5 0.0 0.5 Vg 1.59v 0v -0.34v -0.60v -0.90v -1.20v -1.50v -1.80v -2.10v -2.40v -2.70v -3v SiO2 Ti n-type Si Depletion Region 1.9 mµ 3.5 1.6 圖 4.11 樣品(B)Ti-SiO2-n type Si 隨著外加偏壓變化的電位分佈圖 將樣品(B)以實際製程分為三個部分:Distance 0 mµ 是樣品表面深入 4 mµ 的 位置。從圖 4.11 右邊看起,金屬鈦薄膜約 300nm;SiO2約 150nm,接著是 n-type 的矽。當外加負偏壓越大,矽與氧化層介面能帶的彎曲增大,n-type Si 主要載子 (電子)被排離半導體表面,空乏區產生,由圖 4.11 看出當距離為 1.6 mµ 時,能帶 即不再彎曲,因此可推斷空乏區最大寬度約為 1.9 mµ 。 空乏區最大寬度理論計算為: 由 1.2.4 節(6)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = d B s d s s eN eN W ε ϕ ε φ

已知:Si dielectric constant =11.7,Nd =1.7×10−14cm−3 ,φB =0.27v 得: m W 2.03µ 10 7 . 1 10 6 . 1 27 . 0 10 85 . 8 7 . 11 4 1/2 14 19 14 max ⎟⎟ = ⎠ ⎞ ⎜⎜ ⎝ ⎛ × × × × × × × = − − 當 大約等於 0.90v 時,能帶有下降變快的趨勢,推測是反轉形成 p 通道產生。 臨界電壓的理論計算為: g V 由 1.2.4 節(8)式 FB B ox d T V C Q V =− + −2φ 已知: VFB =−0.34v 2 9 4 14 19 max / 10 52 . 5 10 03 . 2 10 7 . 1 10 6 . 1 cm coul W eN Qd d − − − × = × × × × × = = 2 8 8 14 / 10 45 . 3 10 1000 10 85 . 8 9 . 3 cm F d C ox ox − − − × = × × × = =ε 得 04 . 1 27 . 0 2 34 . 0 10 45 . 3 10 52 . 5 8 9 − = × − − × × − = −− T V v

(a)Vg =−1.49v (b)Vg =−0.97v

(c)Vg =0v (d)Vg =+0.60v

(e)Vg =+1.20v (f)Vg =+1.80v

圖 4.12(a)~(f)是樣品(C) Al -SiO2- p-type Si 依序加偏壓-1.49v,-0.97v,0v,1.2v, 1.8v 的 CPD 圖。與(A)樣品不同的地方是金屬由 Ti 換成 Al,可發現 CPD 值對 的變化樣品(C)比樣品(A)敏感很多,由圖 4.13 更可以明顯的觀察到。

g V

Potential Distribution(P-type)(Metal:Al) Distance (um) 0 1 2 3 4 CP D (v) 0.0 0.5 1.0 1.5 2.0 Vg 2.40v 2.10v 1.80v 1.50v 1.20v 0.90v 0.60v 0.30v 0v -0.5v -0.97v -1.49v 2.70v Al SiO2 p-type Si Depletion Region 1.7 圖 4.13 樣品(C) Al-SiO2-p type Si 隨外加偏壓變化的電位分佈圖 樣品(C)經實際製程可分為三部分(圖 4.13):Distance 0 mµ 是樣品表面深入 4 mµ 的位置。由圖 4.13 右邊看起,Al 薄膜 250nm;SiO2 500nm;p-type Si。與 圖 4.9 比較,發現 Al 薄膜當閘極的能帶隨外加偏壓變化較 Ti 薄膜明顯。由圖 4.13,可發現當Vg >0,空乏區產生時,距離為 1.7µm處的能帶即不彎曲,空乏 區最大寬度為 1.5 mµ 。 空乏區最大寬度理論計算為: 由 1.2.4 節(6)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = a B s a s s eN eN W ε ϕ ε φ

已知:Si dielectric constant =11.7, 15 3 , 10 − = cm

得:W 0.86µm 10 10 6 . 1 28 . 0 10 85 . 8 7 . 11 4 1/2 15 19 14 max ⎟⎟ = ⎠ ⎞ ⎜⎜ ⎝ ⎛ × × × × × × = − − 當 大於 1.20v 時,能帶有上升較快的趨勢,推測是反轉產生,n 通道形成。臨 界電壓理論計算為: g V 由 1.2.4 節(8)式 FB B ox d T V C Q V = + +2φ 已知: VFB =−0.97v 2 8 5 15 19 max / 10 36 . 1 10 5 . 8 10 10 6 . 1 cm coul W eN Qd a − − − × = × × × × = = 2 9 8 14 / 10 9 . 6 10 5000 10 85 . 8 9 . 3 cm F d C ox ox − − − × = × × × = =ε 得 58 . 1 29 . 0 2 97 . 0 10 9 . 6 10 36 . 1 9 8 = × + − × × = −− T V v

(a)Vg=+3.40v (b)Vg=0v

(c)Vg=-1.69v (d)Vg=-2v

(e)Vg=-2.39v (f)Vg=-2.80v

(g)Vg=-3.20v (h)Vg=-3.60v

圖 4.14(a)~(h)為樣品(D) Al -SiO2- n-type Si 依序外加偏壓+3.4v,0v,-1.69v,-2v, -2.39v,-2.80v,-3.20v,-3.60v 的 CPD 圖。

Potential Distribution(N-type)(Metal:Al) Distance (um) 0 1 2 3 4 CPD (v) -1.5 -1.0 -0.5 0.0 0.5 Vg 3.40v 0v -1.19v -1.69v -2.00v -2.39v -2.80v -3.20v -3.60v -4.00v -4.41v Al SiO2 Depletion Region n-type Si 1.8 3.55 1.75 mµ 圖 4.15 樣品(D) Al-SiO2-n type Si 隨外加偏壓變化的電位分佈圖 樣品(D)依實際製程可分為三部分:Distance 0 mµ 是樣品表面深入 4 mµ 的位 置。由圖 4.15 右邊看起,Al 薄膜 250nm;SiO2 150nm;n-type Si。由圖 4.15 可 看出當距離 1.8 mµ 時,能帶即不再彎曲,因此可推斷空乏區最大寬度約為 1.75 mµ 。 空乏區最大寬度理論計算為: 由 1.2.4 節(6)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = d B s d s s eN eN W ε ϕ ε φ

已知:Si dielectric constant =11.7,Nd =1.7×10−14cm−3 ,φB =0.27v 得: m W 2.03µ 10 7 . 1 10 6 . 1 27 . 0 10 85 . 8 7 . 11 4 1/2 14 19 14 max ⎟⎟ = ⎠ ⎞ ⎜⎜ ⎝ ⎛ × × × × × × × = − −

當 大約等於-2.80v 時,能帶有下降變快的趨勢,推測是反轉形成,p 通道產生。 臨界電壓的理論計算為: g V 由 1.2.4 節(8)式 FB B ox d T V C Q V =− + −2φ 已知: VFB =−1.69v 2 9 4 14 19 max / 10 52 . 5 10 03 . 2 10 7 . 1 10 6 . 1 cm coul W eN Qd d − − − × = × × × × × = = 2 8 8 14 / 10 45 . 3 10 1000 10 85 . 8 9 . 3 cm F d C ox ox − − − × = × × × = =ε 得 39 . 2 27 . 0 2 69 . 1 10 45 . 3 10 52 . 5 8 9 − = × − − × × − = −− v VT v

4.4 MOS 元件的電場分佈圖

接著,用電場圖來試著解釋 MOS 元件,以樣品(D) Al-SiO2-n type Si 為例, 取圖 4.14 中 Vg=0v、Vg=-1.19v、Vg=-2.00v、Vg=-2.39v、Vg=-2.8v、Vg=-3.2v、 Vg=-3.6v 的電位圖對掃描位置 x 軸作一次微分,在對掃描位置 x 軸作圖,如圖 4.16。可明確的看出 n-type Si 與 SiO2的交界面電場有明顯的變化,在 SiO2的範 圍內電場應為一定值,由圖 4.16 可發現 SiO2區域內電場有大約 150~200nm 的水 平段,應是氧化層的厚度。

外加負偏壓增大,Si 與 SiO2的交界面電場値由正的減小至 0,再減小至負的。 當至臨界電壓 Vg=-2.80v 時,可明顯發現電場下降値增大,即是反轉層(p 通道) 所造成的效應。

Electric Force Distribution(N-type)(Metal:Al) Distance (um) 1 2 3 4 Electric F ield (V/cm)*10^4 -50 -40 -30 -20 -10 0 10 Vg=-2.00v Vg=-2.39v Vg=-2.80v Vg=-3.60v Vg=0v Vg=-1.19v Al SiO2 n-type Si E1=1.9 E2=4.5 E3=7.4 3.55 3.7 E4=12.3 E5=15.3 Vg=-3.20v E1-E2=2.6 E2-E3=2.9 E4-E3=4.9 E4-E5=3 圖 4.16 樣品(D) Al-SiO2-n type Si 的電場分佈圖。由右邊看起:250nm Al 薄膜; 150nm SiO2;n-type Si。在位置 3.55 mµ 與 3.70 mµ 之間,電場是平的(即為 SiO2 區域)。由圖 E2-E1=2.6,E3-E2=2.9,E4-E3=4.9,E5-E4=3,由此我們發現 E4-E3=4.9 有個突然增大的電場値,因此判定-2.80v 左右為臨界電壓。

第五章 結論

表面電位顯微鏡應用於量測半導體元件特性上有多種的功能。不僅可量測雜 質濃度;氧化層厚度;氧化層捕捉電荷等等一些元件的特性,亦能直觀的分辨元 件上各材質的分佈,經由量測到的電位圖對掃描軸 x 軸作一次微分所得到的電場 分佈圖,更能清楚的觀測出材質間的交界面。基於此,我們試著以表面電位顯微 鏡量測運作中的 MOS 元件,一方面研究不同材質之間因製程或劈開樣品所造成 的表面態,一方面希望能實際觀測 MOS 元件運作時的能帶。 樣品的準備方式是,n-type( )與 p-type( ) Si 上以 Wet-Oxidation 長上一層氧化層,以熱蒸鍍與電子槍蒸鍍方式在氧化層上方蒸鍍 金屬薄膜。最後將樣品劈開觀測樣品剖面。共有四組樣品(A)Ti -SiO2-p-type silicon;(B) Ti-SiO2-n type Si; (C) Al-SiO2-p-type Si ;(D) Al-SiO2-n-type Si。得 到以下幾點結論: 14 10 7 . 1 × = d N Na =1015 1.劈開樣品的方法很重要,剖面的平坦與否會影響介面的捕捉電荷的多寡,因此 必須尋一種減低破壞樣品表面的方法。我們的方法是依循矽晶片(wafer)在不同方 向的鍵結位置,尋找長直的裂面,例如 Si(100)的晶片在 flat 方向[110]或與 flat 垂直的方向,矽與矽之間是形成整齊的 dimer row,所以我們沿這方向劈的話, 可得到一個較平坦的(011)剖面。相同的,Si(111)矽原子鍵結的方式是類似菱形的 7x7,因此我們在與其 flat 方向[1-10]夾 30 度或 60 度劈開,可得較平坦的剖面。 此外,我們發現在純水中進行劈開過程,可減少樣品表面的細紋,原因是水能減 低樣品劈開時所受的硬力(stress field)。 2. 電容偵測器偵測出 MOS 元件的 C-V 圖,可推出平帶電壓的大小,依平帶電 壓可推得氧化層上的總有效電荷。相同地,KFM 更能直接的依表面電位分佈圖 觀測出平帶電壓的位置,亦可推得氧化層上的總有效電荷。其値與理論值差異並不大,因此 KFM 亦能用來探討 MOS 元件氧化層成長的好壞。 3.由 CPD 圖之 line profile 與外加偏壓構成的圖,可由能帶的彎曲現象直接觀察 出空乏區的寬度。以下是實驗觀測値與理論計算值的比較表: (A)Ti -SiO2- p-type Si (B)Ti -SiO2- n-type Si (C)Al -SiO2- p-type Si (D)Al -SiO2- n-type Si max W ( mµ ) 觀測値 1.50 1.90 1.50 1.75 max W (µm) 理論值 0.86 2.03 0.86 2.03 誤差(%) 74 6.4 74 13.8 由上表可看出 p-type 的樣品(A)(C)所觀測的値與理論值相差比較大,其原因與 4.2.3 節討論氧化層總有效電荷一樣。因為我們 p-type Si 載子濃度是假設的 ( ),所以空乏區最大寬度與理論值相差會比較大。現在我們將用所觀測 到的最大空乏區寬度反推真實的 値。以(A)樣品為例: 15 10 = a N a N 已知:φm =4.33v,Wmax =1.5µm 令 Na =x 即 ) 10 5 . 1 ln( 0259 . 0 ) ln( 10 × × = = x n N V i a t B φ 又由 1.2.4 節(6)式 2 / 1 2 / 1 max ) 2 ( 2 2 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ = a B s a s s eN eN W

ε

ϕ

ε

φ

即 2 1 19 10 14 4 10 6 . 1 ) 10 5 . 1 ln( 0259 . 0 10 85 . 8 7 . 11 4 10 5 . 1 ⎟ ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎜ ⎝ ⎛ × × × × × × × = × − − − x x 解得: 14 3 10 36 . 3 × − = cm x將 14 3代回 4.2.3 節(A)樣品,重新計算氧化層總有效電荷結果為 10 36 . 3 × − = cm Na 2 9 " 10 1 . 9 × − = cm Qo 比原先假設 所計算的 更為接 近理論值 ,因此可證明我們的修正方向是正確的,亦可說明本實驗所得到的 最大空乏區寬度可用來逆推未知的載子濃度。 3 15 10 − = cm Na 2 9 10 8 . 7 × − = cm Qo 11 10 4.利用電位對探針掃描軸(x 軸)作一次微分所得的電場分佈圖,除了較 CPD 圖能 分辨出不同材質的交界面外,亦能觀察出臨界電壓( )的位置,以下是本實驗的 估計值和理論計算的比較: T V (A)Ti -SiO2- p-type Si (B)Ti -SiO2- n-type Si (C)Al -SiO2- p-type Si (D)Al -SiO2- n-type Si T V (v) 觀測値 1.80 -0.90 1.20 -2.80 T V (v) 理論值 1.84 -1.04 1.58 -2.39 我們取臨界電壓的方式是,當外加偏壓超過此偏壓時,電位或電場有顯著的上升 或下降,即定義此偏壓為臨界電壓。而由上表可知本實驗値與理論值有最大有相 差 0.4v,造成的誤差可能來自:我們偏壓改變量太大,造成可能只能找到臨界電 壓的附近。 5.影響本實驗的因素很多,包含探針針尖的粗細;探針的震盪頻率;樣品的切割 方式;空氣的氧化問題…等等。因此本實驗可改進的方式有:使用針尖較細的探 針,可使量測到材質的厚度較為真實。減低樣品因切割所造成的地勢高低差,可 使表面態狀況減至最低。使用真空的 KFM 系統,可使環境因素對於量測值的影 響減至最小。

附錄一 以 KFM 量側 InAs/GaAs QDs

圖一 樣品剖面圖。將樣品劈開,由右邊看起,首先是我們為了防止探針掉下所 長上的光阻層;在來是 GaAs 500nm;接著是 2.04ML InAs/30nm GaAs 30 layers, 也就是總共範圍約為 900nm;最後是 GaAs 基板。

圖二 樣品的 CPD 圖。由右邊看起,黑色區域為光阻區;接著較亮的區域 GaAs 500nm;在來比較暗ㄧ點區域是 InAs QDs;最後亮的區域是基板的 GaAs。

Potential Distribution Position (um) 0.0 0.5 1.0 1.5 2.0 2.5 3.0 CPD (v) -0.8 -0.6 -0.4 -0.2 0.0 0.2

GaAs InAs QDs GaAs

PR 圖三 樣品的 CPD porfile 圖。將圖二取一條 profile 得圖三,與圖一比較可發現與 實際製程的位置大約雷同。InAs QDs 部分的 CPD 比 GaAs 低了約 0.1V,我們以 圖四解釋。

Evac

Ec

0.71eV 0.693eVEc

Efi

Efi

0.2eVEv

Ev

GaAs

InAs

圖四 樣品的能帶圖。由查表可知無參入雜質的 GaAs Eg=1.43eV,InAs Eg=0.4eV,∆ Ec=0.693eV,由此可推得 GaAs 與 InAs 的 CPD 值差約為 0.693+0.2-0.71=0.183eV,與我們實驗値量出的 0.1eV 相差不大。

附錄二 以 KFM 量側 p-i-n 雷射

圖五 樣品的剖面圖。將樣品劈開,由右邊開始為光阻;p-type GaAs 200nm; AlGaAs 1000nm;InAs QDs 400nm;AlGaAs 1000nm;n-type GaAs 200nm;GaAs 基板。

圖六 p-i-n 雷射之 CPD 圖。圖中有明顯的兩塊長方形寬度大約 1 mµ 是 AlGaAs, 中間夾比較暗的是 InAs QDs,寬度約為 400nm,最左邊較暗處為 n-GaAs。

Potential Distribution Position (um) 0 1 2 3 4 CP D (v) -0.3 -0.2 -0.1 0.0 0.1

0.2 n-GaAs AlGaAs i-GaAs+InAs QDs AlGaAs p-GaAs

(a)

Electric Field Distribution

Position (um) 0 1 2 3 4 Elec tric F ield (V/c m)*1 0^ 4 -12 -10 -8 -6 -4 -2 0 2 4 6 AlGaAs AlGaAs

n-GaAs i-GaAs+InAs QDs p-GaAs

(b)

圖七 (a)圖為圖六 CPD 圖的一條 profile。(b)圖是(a)CPD 曲線對探針掃描軸作一 次微分所得的電場分佈圖,可發現各個材質交接面皆有一個 peak。

參考文獻

[1]L. Soliman , Materials Science in Semiconductor Processing 4 ,163(2001) [2]H. C. Casey , Appl. Phys. Lett. 68,1850(1996)

[3]K. A. Abdullah , Microelectronic Engineering 81,201(2005) [4]P. A. Rosenthal , Appl. Phys. Lett. 81,3993(2002)

[5]O. Douheret , Appl. Phys. Lett. 85,5245(2004) [6]F. Robin , Appl. Phys. Lett. 76,2907(2000) [7]R. Shikler ,J. Appl. Phys. 86,107(1999)

[8]A. Paskaleva ,Semicond. Sci. Technol. 8,1566(1993) [9]C. Witczak , ,J. Appl. Phys. 87,8206(2000)