國立交通大學

工業工程與管理學系

博士論文

液晶顯示模組裝配廠生產排程問題之研究

The Study on the Production Scheduling

Problems for Liquid Crystal Display Module

Assembly factories

學生:戴于婷

指導教授:鍾淑馨博士

液晶顯示模組裝配廠生產排程問題之研究

The Study on the Production Scheduling Problems for Liquid Crystal Display Module Assembly factories

研究生:戴于婷 Student: Yu-Ting Tai

指導教授:鍾淑馨 博士 Advisor: Dr. Shu-Hsing Chung

國 立 交 通 大 學

工業工程與管理學系

博士論文

A Dissertation Submitted to

Department of Industrial Engineering and Management College of Management

National Chiao Tung University in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in

Industrial Engineering and Management

July 2008

Hsinchu, Taiwan, Republic of China

液晶顯示模組裝配廠生產排程問題之研究

學生:戴于婷

指導教授:鍾淑馨博士

國立交通大學工業工程與管理系

摘

要

在液晶面板廠中,如何充分利用產能及滿足顧客交期來增加競爭力及獲利,為一重 要之研究課題;在液晶面板製造的最終模組裝配製造階段中,印刷電路板焊接作業為生 產過程中的瓶頸,其排程結果將影響整個模組裝配廠的生產績效,因此,本論文先針對 此瓶頸作業所衍生的平行機台排程問題進行探討。而在經過印刷電路板焊接作業後,工 件在出貨前還須經過老化測試作業,這是模組裝配廠中的批次機台,老化測試的排程問 題是一個多維度的排程問題,其考量了不同的到臨時間、不同的工件大小、有限的機台 產能以及批次相依的加工時間,不當的老化測試排程將影響出貨時程,因此,發展老化 測試排程的求解程序在模組裝配廠也是一重要的課題。本 論 文 首 先 解 決 印 刷 電 路 板 焊 接 排 程 問 題 (printed circuit board bonding

scheduling problem;PCBSP),其為順序相依設置時間的平行機台排程問題,工件在此 問題中分屬不同的產品族,由於模組裝配廠所製造的產品面臨契約與現貨並存的混合市

場,因此,工件在PCBSP 中依據利潤及客戶重要性等因素被賦予不同的權重,在此問

題中,本文於滿足契約數量及不違反交期及機器產能的限制下,以求得最大化總加權產

出作為PCBSP 的求解目標,這些工件一旦於瓶頸資源上完工,則需要加速出貨,因此,

在老化測試排程問題 (aging test scheduling problem;ATSP) 中則以最小化完工時間為

目標。

在本論文中,我們針對PCBSP 與 ATSP 兩個排程問題分別建立其混合整數規劃模

式,亦將 PCBSP 的子問題轉換為考量時間窗限制下之車輛路線問題(vehicle routing

problem with time window;VRPTW),並修改既有的網路演算法來發展新的啟發式解

法,同時也應用貪婪法則來解決其他的子問題;此外,針對ATSP,我們也設計一個複 合啟發式法則來決定批次個數,並將此個數視為一已知的參數帶入混合整數規劃模式 中,以降低原先模式求解的複雜度,而針對大型的ATSP,本文也提出三個啟發式解法 來求解;經由運算結果及績效比較中得知,本論文針對PCBSP 及 ATSP 所提出的啟發 式法則有很好的求解效果。 關鍵詞:平行機台排程、批次、加權產出、順序相依設置時間、模組裝配

The Study on the Production Scheduling Problems for

Liquid-Crystal-Display Module Assembly Factories

Student:Yu-Ting Tai Advisor: Dr. Shu-Hsing Chung

ABSTRACT

To be competitive, the thin film transistor liquid crystal display (TFT-LCD) companies need to utilize their capacity and to satisfy customers’due dates in order to increase their profitability. In the final stage of TFT-LCD, module assembly manufacturing process, the printed circuit board (PCB) bonding usually causes bottleneck in production; its schedule mainly affect the system performance of module assembly factories. Therefore, an essential scheduling problem is tackled for the bottleneck operation first; it is referred to as the printed circuit board bonding scheduling problem (PCBSP). Furthermore, following the PCB bonding operation, there exists an aging test operation, which is the only batch server in the whole process. The aging test scheduling problem (ATSP) is complicated because it is a multi-dimensional problem, which involves the constraints of unequal ready times, non-identical job sizes, limited machine capacity, and batch dependent processing times. Therefore, the development of efficient algorithms is also critical to form appropriate batches and to arrange a suitable schedule for those jobs which have been processed by the PCB bonding operation.

For the PCBSP, the jobs are clustered by their product types, which must be processed on identical parallel machines. They are also given various weights based on their profits and customer importance due to hybrid contracted and spot markets being in the module assembly industry. Furthermore, setup times for two consecutive jobs between different product types on the same machines are sequence-dependent. Thus, the objective for the PCBSP is to maximize the total weighted throughput subject to fulfilling contracted quantities without violating the due dates and machine capacity restrictions. Once those jobs are planned and processed in the bottleneck operation, they

should be accelerated their speed to complete and delivery. Consequently, the ATSP with a minimal makespan criterion is also considered.

In this dissertation, the PCBSP and ATSP are formulated as two mixed integer linear programming models. For the PCBSP, it can be viewed as a multi-level optimization problem, the sub-problem of PCBSP can be transformed into the vehicle routing problem with time window (VRPTW), a well-known network routing problem which has been investigated extensively. We present two new algorithms based on the network algorithms with some modifications to accommodate the PCBSP. Furthermore, the greedy concept is also applied to the other sub-problem of PCBSP. For the ATSP, an effective compound algorithm is proposed to determine the number of batches and to apply this number as one parameter in the MILP model in order to reduce the complexity of the problem. Three efficient heuristic algorithms are also provided for the large-scaled ATSP. Computational results and performance comparisons show that the proposed algorithms, which are used to solve the PCBSP and ATSP, are efficient and near-optimal.

Keywords : parallel machines scheduling, batch, weighted throughput, sequence

誌

謝

這本論文能順利地完成,要感謝的人真的太多了,都是因為大家的幫忙,我才能一 步一步地走完這個旅程。首先,要感謝我的指導老師 鍾淑馨教授, 鍾老師治學嚴謹, 做研究及教學都相當認真,對學生生活上的關懷更是無微不至,每每在我學業、家庭、 身體與工作產生衝突時,鍾老師總是給我滿滿的鼓勵與建議,讓我能在這條路上,將自 己的角色扮演好,做好每一件事,能有幸認識老師,並在研究的方法與態度上獲得老師 的啟發與影響真是我的福氣,在此向恩師致上崇高的敬意與謝意。另外,也要感謝 彭 文理教授,彭老師總是不厭其煩地回答我的問題,有老師的鼓勵,也讓我有更多跌倒了 再爬起來的勇氣,此外,口試期間,承蒙口試委員 張百棧院長、吳泰熙教授、陳正芳 教授及彭文理教授給予的寶貴建議,使本論文更加完備,在此致上深深的謝意。 博士班修業期間,感謝519 與 517 實驗室的學長姐與學弟妹的鼓勵與幫助,也感謝 建瑋同學,不僅在修業期間給我鼓勵,畢業後若有回新竹總是不忘看看老同學,為我加 油,也感謝春美學姊與俊穎,常提供給我寶貴的建議,讓我能學習更多,使我的論文更 完善,還有雅靜學妹,謝謝妳常常在我最無助的時候,給我一個親切的微笑,讓我能繼 續走下去,謝謝你們。 最後,要感謝我的爸爸及親愛的家人,爸爸從小總是對我有著深深的期許,真的很 高興自己做到了,沒有辜負他對我的期望,也感謝媽媽以及辛苦的公公婆婆,謝謝你們 在我唸書時幫我帶我兩個小孩,讓我能在新竹專心學業,無後顧之憂,當然,也要感謝 我的先生 建穎,還有我那兩個可愛的孩子,謝謝建穎總是幽默地在我身旁幫我加油打 氣,協助我渡過每一個困難,另外,也謝謝兩位小孩天真無邪的笑容常帶給我莫大的鼓 勵。在此向每位關心過我、鼓勵過我的人致上最深的謝意,也將這份成果獻給你們。 戴于婷 僅誌于國立交通大學 管理學院工業工程與管理學系 中華民國九十七年七月十一日Table of Contents

Abstract (Chinese) ... i

Abstract (English) ... ii

Acknowledgements...iv

Table of Contents ...v

List of Figures ...vii

List of Tables...viii

Notation ... x

1. Introduction... 1

1.1. Motivation... 1

1.2. Research Scope and Objectives ... 4

1.3. Organization of the Dissertation ... 5

2. Literature Review... 7

2.1. Existing Production Management Problems in TFT-LCD factories ... 7

2.2. Scheduling Problems with a Maximal Throughput Criterion ...10

2.3. Network Problems ...12

2.4. Batch Processing Machine Scheduling Problems...14

3. Algorithms for the Printed Circuit Board Bonding Scheduling Problem ...21

3.1. Introduction...21

3.2. Module Assembly Process and Problem Description ...22

3.2.1. Module Assembly Process...22

3.2.2. Printed Circuit Board Bonding Scheduling Problem...24

3.2.3. An Illustrative Example...25

3.3. An Integer Programming Formulation for the PCBSP...26

3.4. Algorithms for the PCBSP...29

3.4.1. Parallel Savings Algorithm ...29

3.4.2. Generalized Savings Algorithm ...30

3.4.3. New Algorithms ...30

3.4.3.1. Three-phase Modified Parallel Savings Algorithm...31

3.4.3.2. Three-phase Modified Generalized Savings Algorithm...36

3.5.1. Workload Level of Contract Jobs ...40

3.5.2. Tightness of Due Dates...41

3.5.3. Setup Time Variation ...42

3.5.4. Variation of (Contract/Spot) Weight Ratio ...42

3.6. Computational Results ...42

4. Solutions for the Aging Test Scheduling Problem ...48

4.1. Introduction...48

4.2. An Integer Programming Formulation...51

4.3. Compound MILP-based Algorithm ...56

4.4. Heuristic Algorithms for Large-scale Problems...59

4.4.1. Heuristic Algorithm 1 (H1)...60

4.4.2. Heuristic Algorithm 2 (H2)...62

4.4.3. Mixed-strategy Heuristic Algorithm (MixedH)...63

4.5. Computational Results and Comparisons ...64

4.5.1. Analysis of Results from Small and Moderate Size Problems ...64

4.5.2. Analysis of the Result Based on the Large Scaled Problem ...71

5. Conclusions and Future Research ...73

5.1. Conclusions ...73

5.2. Future Research ...75

List of Figures

Figure 1-1The TFT LCD process flow. ... 1

Figure 3-1The six steps in the module assembly process. ...23

Figure 3-2PCB bonding illustration. ...23

Figure 3-3COG structure. ...24

Figure 3-4TAB structure. ...24

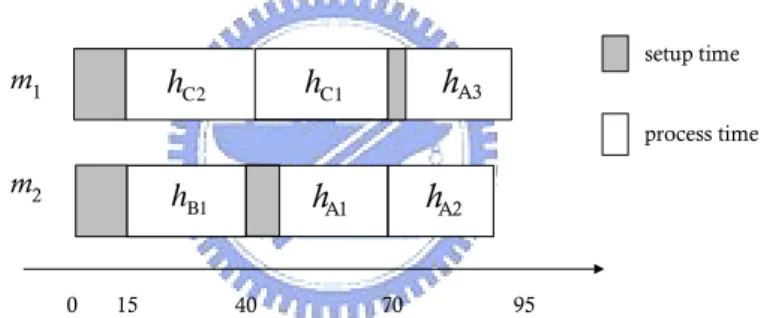

Figure 3-5Gantt chart for the example problem. ...36

Figure 4-1The six steps in the module assembly process. ...49

Figure 4-2The multiple dimensions of the aging test scheduling problem. ...50

Figure 4-3An optimal solution for the 7-job example with two aging test machines...56

List of Tables

Table 2-1 The literature related to production management problems in TFT-LCD

factories. ...8

Table 2-2The literature for the scheduling problems with a throughput maximization criterion. ...11

Table 2-3 The literature related to the batch processing machine scheduling problem with compatible product families. ...16

Table 3-1The job information for the 7-job example. ...26

Table 3-2 Setup times required for switching one product type to another for HA, B H , and HC. ...26

Table 3-3The savings values of each contract-jobs pair. ...35

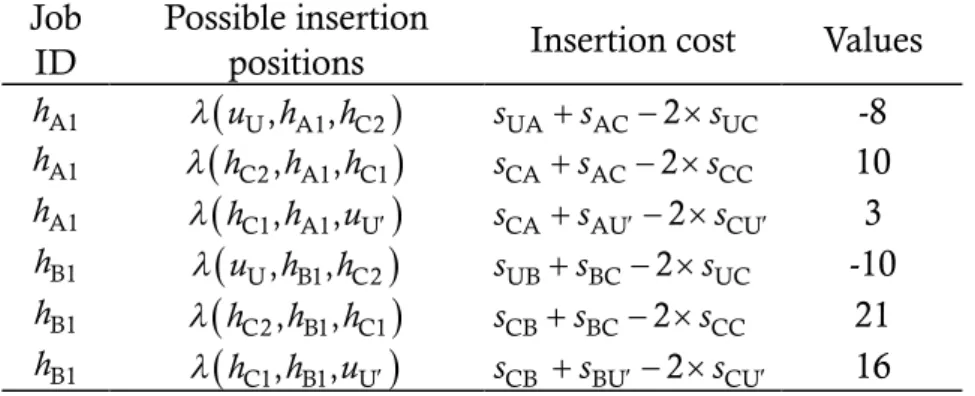

Table 3-4The insertion cost of each job at every possible position...38

Table 3-5Summarized information of 24 problems. ...41

Table 3-6 A comparison between the optimal solutions and two heuristic algorithms (underlines indicate the optimal solutions). ...43

Table 3-7The preliminary comparison with various parameter settings. ...44

Table 3-8 The comparisons with different parameter values of 1 when .1 0 5 and 1 1 5 . (underlines indicate the best solutions for each problem instance). ..44

Table 3-9Performance comparisons in the three algorithms. ...45

Table 3-10Results in means with different problem characteristic groups. ...46

Table 3-11Performance comparisons of the three algorithms (24 problems). ...47

Table 4-1Job sizes, ready times, and processing times of the seven independent jobs. ...55

Table 4-2The composite jobs for each estimated batch. ...59

Table 4-3Experimental factors for small and moderate sized problems. ...65

Table 4-4Run times and makespan results for 7-job problem instances...68

Table 4-5Run times and makespan results for 15-job problem instances. ...69

Table 4-7Comparisons of the five algorithms. ...71

Table A1Setup times matrix for 26 product types in problem 6 (unit: minutes)...82

Notation

Notations for the printed circuit board bonding scheduling problem:

Indices:

i : product type index, i0 1, , ,I ;

j : index of job for product type index i, j 0,1, , Ji;

k : machine index, k1,2,...,K;

k

m : the kth machine;

H : the set of jobs to be processed;

M : the set of machine containing identical parallel machines;

i

H : job cluster containing Ji jobs of product type i to be processed;

ij

h : index for jobs in cluster Hi;

Parameters:

K : the number of identical machines;

I : the number of job clusters in job set H;

i

J : the number of jobs in job cluster Hi;

ij

n : lot size of job hij;

i

p : the unit processing time for job hij;

ij

w : the nonnegative weight for job hij;

ij

d : the due date for job hij;

ii

s : the sequence dependent setup time between any two consecutive jobs;

Cap : the predetermined machine capacity expressed in terms of time;

contract i

J : the number of contract jobs in job cluster Hi;

ij

ij

r : the ready time for job hij;

ii

SA : the savings for the pairs of two jobs associated with product type Hi and

i H ; ij i j h h

PSA : the savings applied in the parallel savings algorithm for pairs of jobs hij and hi j;

ij i j

h h

GSA : the savings applied in the generalized savings algorithm for pairs of jobs

ij

h and hi j;

1 : the parameter represents weight of savings for calculating PSAh hij i j;

1 : the parameter represents weight of weighted throughput ratio for

calculating PSAh hij i j; 1

r : the parameter represents weight of time windows restrictions for

calculating

ij i j

h h

PSA ;

2 : the parameter represents weight of savings for calculating GSAh hij i j;

2 : the parameter represents weight of weighted throughput ratio for

calculating GSAh hij i j; 2

r : the parameter represents weight of time windows restrictions for

calculating ij i j h h GSA ; Decision variables: ijk

x : the variable indicating whether a specific job is scheduled on a machine,

with xijk 1 if job hij is scheduled on machine mk , and xijk 0

otherwise;

iji j k

y : the precedence variable defined on two jobs hij and hi jscheduled on

machine mk, with yiji j k1 if job hij precede job hi j(not necessarily

directly), and yiji j k0 otherwise;

iji j k

scheduled on machine mk, with ziji j k1 if job hij direct precede job

i j

h , and ziji j k0 otherwise. ijk

t : the starting time for job hij processed on machine mk;

Notations for the aging test scheduling problem:

Indices: j : job index, j 0,1, , N; b : batch index, b1,2, , B; k : machine index, k1,2,...,K; k m : the kth machine; Parameters:

N : the number of jobs;

B : the number of batches;

K : the number of machines;

j

p : the processing time for job j;

j

r : the ready time for job j;

j

s : the job size for job j;

S : the maximum number of pieces can be processed simultaneously on a

machine;

: a constant, which is chosen to be a sufficiently small value which cannot

affect the makespan in Model P; 1

Q : a constant and is greater than the total number of jobs (N) in Model P;

2

Q : a chosen constant as it is sufficiently large in value to satisfy ybb k0 or 1

in Model P;

: the parameter is used to examine whether there exists a job might be

: the parameter represents to accommodate the postponement idea of the DELAY heuristic algorithm ;

Decision variables:

jbk

x : the variable indicating whether a specific job is assigned to batch b and

scheduled on a machine mk, with xjbk 1 if job j is assigned to batch

b and scheduled on machine mk, and xjbk 0 otherwise;

bb k

y : the precedence variable defined on two batches b and bscheduled on

machine mk, with ybb k1 if batch b precede job b(not necessarily directly), and ybb k0 otherwise;

bk

z : the variable indicating whether a specific batch b is scheduled on a

machine mk, with zbk 1 if batch b is scheduled on machine mk, and

0

bk

z otherwise;

bk

t : the starting time of batch b to be processed on machine;

max

C : the makespan;

b

pt : the longest processing time of all the jobs processed simultaneously in the

bthbatch;

max

C : the lower bound of makespan in Model N;

BN : the number of lower bound batches obtained from Model N;

Z : the solution obtained from Model P;

*

Z : the solution of the compound MILP-based algorithm obtained within the

limited computational time;

t : the decision time point;

b

r : the batch ready times;

b

1. Introduction

1.1. Motivation

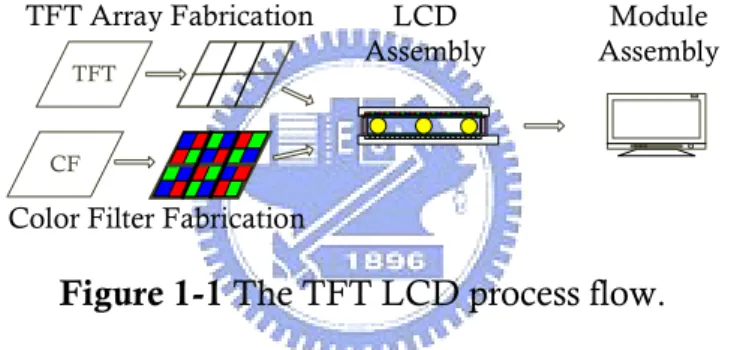

In recent years, applications of thin film transistor liquid crystal display (TFT-LCD) products have been increasing rapidly, for example, cellular phones, computer monitors, and LCD TVs. Not surprisingly, TFT-LCD manufacturing has attracted much attention. The TFT-LCD manufacture process consists of four major stages: TFT array fabrication, color filter (CF) fabrication, LCD assembly and module assembly, as depicted in Figure 1-1.

Module Assembly

CF TFT

Color Filter Fabrication

LCD Assembly TFT Array Fabrication

Figure 1-1The TFT LCD process flow.

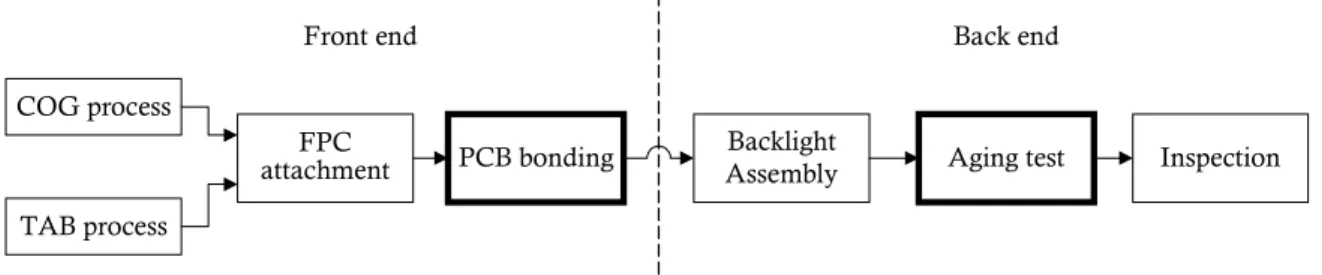

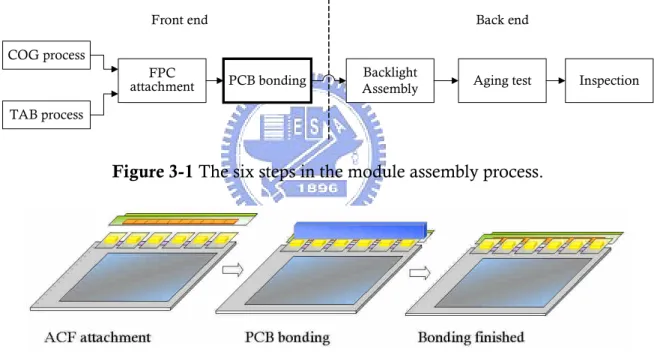

TFT array and color filter fabrications are similar to the semiconductor wafer fabrication, and their process steps are also characterized by re-entrant flow. The LCD assembly simultaneously attaches the TFT and color filter and fills the gap between them with liquid crystal. The final stage, module assembly, generally consists of two main segments, front end and back end. It contains the following six processes steps in which the customer-specified components are assembled into the cells: (1) the COG (chip on glass) / TAB (tape automated bonding) process, (2) the attachment of the flexible printed circuit (FPC) board, (3) the bonding of the printed circuit board (PCB), (4) the assembly of the backlight, (5) the aging test, and (6) the inspection, as shown in Figure 1-2.

COG process

FPC attachment TAB process

PCB bonding AssemblyBacklight Aging test Inspection

Front end Back end

Figure 1-2The six steps in the module assembly process.

In the module assembly stage, the printed circuit board (PCB) bonding operation usually causes bottleneck in production because it involves the most expensive equipment and its machine utilization is the highest in this stage. Setup times for two consecutive jobs of different product types on the same PCB bonding machine are long and sequentially dependent. Furthermore, in the module assembly manufacturing industry, there exists a hybrid market involving contract and spot markets. The contract jobs associated with contracted prices and due dates have been placed and booked an amount of capacity. Moreover, the other remaining capacity is to be sold into the spot market. The further spot prices are uncertain and high price volatility due to today’s fierce competitive environment. In this dissertation, jobs in module assembly factories are given different weights, which are determined by the factors such as job’s profit and customer importance. According to the essential concept of theory of constraints (TOC) [41], the performance of a system is determined by the bottleneck in the system. Thus, in this dissertation, a printed circuit board bonding scheduling problem (PCBSP) is first investigated and which selects a appropriate subset of jobs to maximize weighted throughput by considering sequence dependent setup times, job weights, and due dates.

After jobs are processed at the processing of the bottleneck operation (PCB bonding), they should be passed through two main operations, backlight assembly and

aging test (see Figure 1-2) in the module assembly process. In the backlight assembly operation, jobs can be processed smoothly because the non-critical operation has enough capacity and it is the serial server that is the same fashion as the PCB bonding operation. However, how to schedule the jobs processed at the aging test operation is much more complicated since this operation is a batch server which involvs parallel batch machines. Batches at the aging test operation need to be formed by collecting unequal ready-time jobs and non-identical size jobs with considerations of limited machine capacity (a maximum number of pieces can be processed simultaneously on a machine) and batch dependent ready times and processing times. Therefore, solving such multi-dimensional batch processing machines scheduling problem may cause a large makespan if an improper batch-formation strategy is applied. Moreover, Mönch

et al. [62] also pointed out “it is sometimes advantageous to process a non-full batch to avoid excessive delays in waiting for jobs with later ready times”.Therefore, an elaborate solution

procedure for the aging testing scheduling problem (ATSP) located at the end of module assembly process is necessary. In this dissertation, we not only focus on the investigation for the bottleneck operation by solving the PCBSP, but also expedite the jobs at the aging test operation to complete with a minimal makespan criterion in order to subordinate the scheduling results of the bottleneck operation. Consequently, it is essential that the development of efficient algorithms to solve the ATSP in module assembly factories.

Since the PCBSP and ATSP involve many real-world constraints, they are more difficult to solve than the classical parallel-machine scheduling problems considered by So [78], Shin and Leon [77], and Jeong et al. [47] and parallel-batch-processing machine scheduling problems considered by Lee and Uzsoy [51], and Chang et al. [14],

respectively. We believe that the development of the scheduling methods for the two scheduling problems can assist those involved in module assembly factories to make judicious scheduling decisions.

1.2. Research Scope and Objectives

In the dissertation, we first focus on the scheduling problem on the bottleneck resource in module assembly process factories; it is referred to as printed circuit board bonding scheduling problem (PCBSP). The PCBSP determines an appropriate subset of jobs to be processed and schedules jobs sequences with a weighted throughput criterion. Subsequently, we consider the batch scheduling problem for the aging test operation which locates at the end of module assembly processing steps. The investigation on the aging test scheduling problem (ATSP) with a minimal makespan criterion provides a schedule for those jobs, which have scheduled in the PCBSP.

The purposes of this dissertation are to develop exact solutions and efficient algorithms for the practical module assembly scheduling problems based on the existing network and batch formation technologies. Two research works will be accomplished in this dissertation:

1. With consideration of the characteristics of different job weights, sequence dependent setup times, due dates, product type dependent processing time, and machine capacity, a mixed integer linear programming model for the PCBSP is constructed to obtain the exact solution. Then, two three-phase algorithms, which based on the existing network algorithms and the greedy concept, are presented to solve the PCBSP efficiently.

2. With the considerations of unequal ready times, non-identical job sizes, limited machine capacity, and batch dependent processing times, a mixed integer linear programming is presented. In addition, an effective compound algorithm and three efficient heuristic algorithms are also provided.

1.3. Organization of the Dissertation

This dissertation focuses on developing the scheduling algorithms for module assembly manufacturing industries is organized as follows.

Chapter 1 provides the motivation of the research and defines the research domain and its objectives.

Chapter 2 presents a literature in the areas involving the existing production management problems in TFT-LCD factories, the scheduling problems with a weighted throughput criterion, network problems, and batch processing machine scheduling problems.

Chapter 3 considers the printed circuit board bonding scheduling problem (PCBSP) in the module assembly to maximize the weighted throughput subject to fulfilling contracted quantities without violating the due date and machine capacity restrictions. The PCBSP is formulated as a mixed integer linear programming model. Two modified algorithms are also proposed to solve the PCBSP efficiently.

Chapter 4 considers the aging test scheduling problem (ATSP) in the module assembly to minimize the makespan. The ATSP is formulated as a mixed integer linear programming model. An effective compound algorithm is proposed to determine the number of batches which is then used as one parameter in the MILP

model in order to reduce the complexity of the problem. Three efficient heuristic algorithms for solving the large-scale parallel batch processing machine scheduling problem are also provided.

Chapter 5 provides the conclusions and several further extensions. Conclusions will be drawn based on the results of the research.

2. Literature Review

The topic of the scheduling problems investigated in this dissertation for module assembly factories bases on ideas from four different research areas. Therefore, this literature review is divided into four areas which contribute to this dissertation regarding related existing production management problems in TFT-LCD factories, the scheduling problems with a weighted throughput criterion, essential network problems, and batch processing machine scheduling problem.

2.1. Existing Production Management Problems in TFT-LCD factories

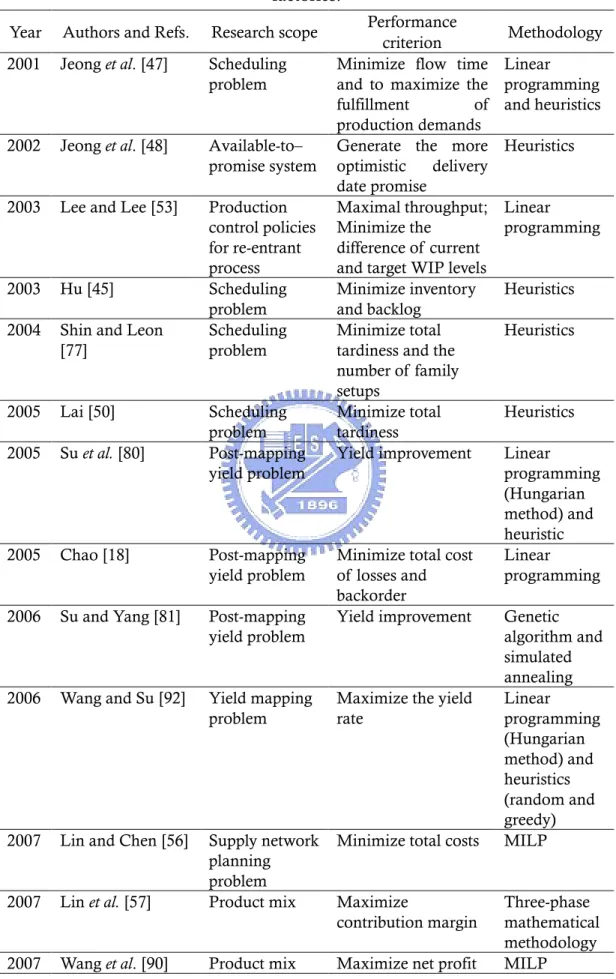

The amount of available literature which investigates related production management problems in TFT-LCD factories is limited. As can be seen in Table 2-1, those research papers can be classified into three categories according their research scopes: supply chain planning problems [48][56][57][90], post-mapping yield problems [18][80][81][92], and scheduling problems [45][47][50][53][77].

In first category, since four basic process stages are involved in the TFT-LCD industry, the supply chain planning problems in TFT-LCD have been receiving attention from academic researchers. Jeong et al. [48] have developed an available-to-promise (ATP) system for TFT-LCD manufacturing in global supply chain environment. The ATP system was used to estimate the promising delivery date for new orders and calculate the unused production capacity with given production schedules. They have also proposed a heuristic for scheduling TFT-LCD module assembly process using the unused capacity at the shop floor level. Lin and Chen [56] and Wang et al. [90] have provided a monolithic model of the multi-stage and

Table 2-1The literature related to production management problems in TFT-LCD factories.

Year Authors and Refs. Research scope Performance

criterion Methodology 2001 Jeong et al. [47] Scheduling

problem

Minimize flow time and to maximize the fulfillment of production demands

Linear programming and heuristics

2002 Jeong et al. [48] Available-to– promise system

Generate the more optimistic delivery date promise

Heuristics

2003 Lee and Lee [53] Production control policies for re-entrant process Maximal throughput; Minimize the difference of current and target WIP levels

Linear programming 2003 Hu [45] Scheduling problem Minimize inventory and backlog Heuristics

2004 Shin and Leon [77]

Scheduling problem

Minimize total tardiness and the number of family setups Heuristics 2005 Lai [50] Scheduling problem Minimize total tardiness Heuristics 2005 Su et al. [80] Post-mapping yield problem

Yield improvement Linear programming (Hungarian method) and heuristic 2005 Chao [18] Post-mapping yield problem

Minimize total cost of losses and backorder

Linear programming

2006 Su and Yang [81] Post-mapping yield problem

Yield improvement Genetic algorithm and simulated annealing 2006 Wang and Su [92] Yield mapping

problem

Maximize the yield rate Linear programming (Hungarian method) and heuristics (random and greedy) 2007 Lin and Chen [56] Supply network

planning problem

Minimize total costs MILP

2007 Lin et al. [57] Product mix Maximize

contribution margin

Three-phase mathematical methodology 2007 Wang et al. [90] Product mix Maximize net profit MILP

multi-site production planning problem and a MILP model to construct a product mix in TFT-LCD factories, respectively. Lin et al. [57] considered a capacity and product mix planning problem for TFT array multi-plant with a maximum contribution margin. They proposed a three-phase methodology which involves capacity configuration, capacity expansion, and capacity exploitation phases. However, in this dissertation, we devote to solving the scheduling problem which the long and middle-term production planning and product mix are given.

The second category, post-mapping yield problem has found by Su et al. [80][81], and Wang and Su [92]. They have solved the problem using a series of tools which involve linear programming, heuristics, and meta-heuristics (genetic algorithm and simulated annealing). They revealed that proposed approaches which can solve practical problems effectively and improve the yield rate in the LCD assembly process. Moreover, Chao [18] also provided a liner programming model in order to solve the mapping problem regarding the mapping between TFT and CF substrates.

Finally, the third category is the scheduling problems in TFT-LCD industries. Jeong et al. [47] presented mathematical models and proposed two heuristic algorithms to minimize flow time and to maximize the fulfillment of production demands in LCD assembly processes. Lee and Lee [53] have suggested three kinds of control policies: push, push-pull, and pull types. They have used the linear programming models to evaluate performances of the three kinds of control policies. It is also presented in their investigation that a pull type control policy gives stable throughput and delivery satisfaction at a small cost and with less production. Shin and Leon [77] discussed the liquid crystal display module stage scheduling problem. They

provided two heuristics based on the MULTI-FIT method and tabu search to minimize total tardiness and number of family setups. Hu [45] and Lai [50] proposed heuristic algorithms for the lot sizing scheduling problem in color filter factories. Hu [45] and Lai [50] solved their scheduling problems with criterion of minimizing the cost of inventory and backlog and minimizing tardiness, respectively. However, none of these investigations considered sequence dependent setup time and job weights simultaneously. This dissertation investigates the weighted throughput criterion of a module assembly factory which, till now, has been ignored.

2.2. Scheduling Problems with a Maximal Throughput Criterion

During the last decade, there have been many researchers who have investigated the identical parallel machine scheduling problem which is dependent on the completion time of all jobs. The objectives usually involve (see Cheng and Sin [19] for a comprehensive survey) completion time-based [61], due-date based [6][76], and flow-time based [24][43] performance measures, etc. However, So [78] points out that determining the best schedule to process all the jobs currently on hand is not practical. Instead, he suggests choosing one subset of jobs for which to construct daily work schedules according to the existing capacity and demand. However, the PCBSP we investigated in this dissertation select the appropriate job sets to maximize the weighted throughput by considering setup times and job weights.

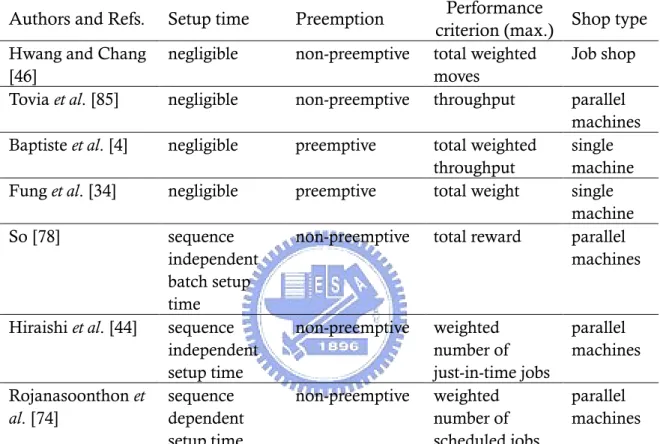

There are relatively few papers, as can be seen in Table 2-2, which addressed the scheduling problem with a throughput criterion. Hwang and Chang [46] and Tovia et

al. [85] have focused on the semiconductor manufacturing process and assumed that

relaxation-based hierarchical production scheduling engines to maximize total number of weighted moves in semiconductor manufacturing. Tovia et al. [85] have presented a mathematical programming model and a rule-based heuristic approach to

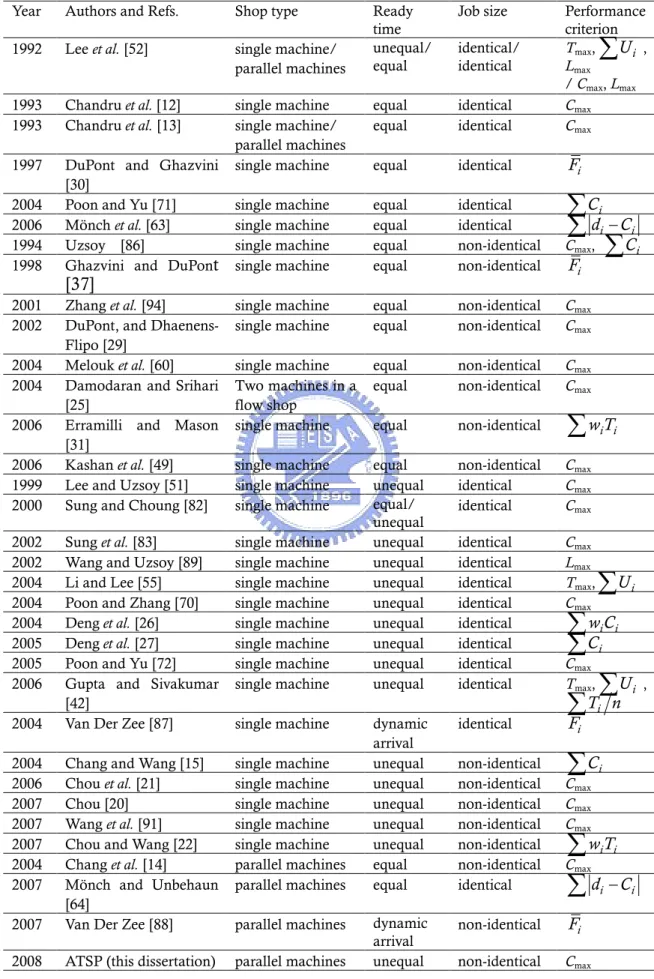

Table 2-2The literature for the scheduling problems with a throughput maximization criterion.

Authors and Refs. Setup time Preemption criterion (max.)Performance Shop type

Hwang and Chang [46]

negligible non-preemptive total weighted moves

Job shop Tovia et al. [85] negligible non-preemptive throughput parallel

machines Baptiste et al. [4] negligible preemptive total weighted

throughput

single machine Fung et al. [34] negligible preemptive total weight single

machine

So [78] sequence

independent batch setup time

non-preemptive total reward parallel machines

Hiraishi et al. [44] sequence independent setup time non-preemptive weighted number of just-in-time jobs parallel machines Rojanasoonthon et al. [74] sequence dependent setup time non-preemptive weighted number of scheduled jobs parallel machines

solve a throughput maximization problem in a semiconductor packaging factory. Furthermore, Baptiste et al. [4] and Fung et al. [34] have considered the preemptive scheduling problem with equal length processing and negligible setup time. However, setup times and non-preemptive scheduling characteristics of the front-end module assembly manufacturing process are essential and significant.

Allahverdi et al. [1] conducted an extensively survey for the scheduling problems which involve setup times. They pointed out that So [78] is the only one who has considered a total reward objective for parallel machine scheduling problems prior to

1999. So [78] considered an analogous version of the PCBSP and presented three heuristics to solve the problem approximately. He tackled a problem that existed in a minor setup time between jobs of the same family and a major setup time between jobs from different groups. According to the classification presented by Allahverdi et

al. [1], what So [78] considered classified to the sequence independent batch setup

times, which is the special case of sequence dependent setup time. Since 1999, with respect to the total weight of completed jobs, Hiraishi et al. [44] and Rojanasoonthon

et al. [74] have maximized the weighted number of just-in-time jobs and the weighted

number of scheduled jobs, respectively, as solutions to the scheduling problems they investigated. However, Hiraishi et al. [44] in their consideration of JIT job and Rojanasoonthon et al. [74] in their examination of strict order of priority in the job completion schedule, both limit and reduce the throughput of parallel machines.

2.3. Network Problems

Two classical network problems, the traveling salesman problem (TSP) [58] and the vehicle routing problem (VRP) [7][79], are among the most widely investigations combinatorial optimization problems. The TSP can be stated as follows: a salesman, starting in one city, wishes to visit other cities once and exactly once and return to the start with minimal total distance traveled. Furthermore, the VRP involves the design of a set of minimum-cost vehicle routes without violating the limited vehicle capacity, originating and terminating at a central depot, for a fleet of vehicles that serviced a set of customers with known demand [7][79]. There are many generalizations of the well-known TSP and VRP. Examples include the traveling salesman problem with time windows (TSPTW) [28][35], the traveling salesman problem with profits [32], the traveling salesman’s subtour problem [36], the prize-collecting traveling salesman

problem [3], the prize-collecting traveling salesman problem with time windows (TW-TSP) [5], the vehicle routing problem with time windows (VRPTW) [79], the orienteering problem (OP) [11][16][39][40], the multiple tour maximum collection problem (MTMCP) [10][11], and the team orienteering problem (TOP) [2][17][84].

It should be noted that jobs in PCBSP are taken the constraint of due dates into consideration and are processed on parallel machines. To solve the scheduling problem for PCBSP and arrange jobs’sequence, this dissertation adopts the basic technologies of vehicle routing problem with time windows (VRPTW). Hence, we further focus on the VRPTW in detail. The VRPTW is a well-known network routing problem which has been investigated extensively [8][9][79]. Bräysy and Gendreau [8] given a explicit definition regarding the VRPTW as follows: “The VRPTW can be

described as the problem of designing least cost routes from one depot to a set of geographically scattered points. The routes must be designed in such a way that each point is visited only once by exactly one vehicle within a given time interval, all routes start and end at the depot, and the total demands of all points on one particular route must not exceed the capacity of the vehicle.”

The VRPTW is NP-complete which is demonstrated by Lenstra and Rinnooy Kan [54]. A large amount of solution procedures, involving route-construction methods, route-improvement methods, and meta-heuristics, have been applied to the VRPTW. Bräysy and Gendreau [8][9] have provided complete surveys of research papers regarding the VRPTW.

VRPTW can be used to solve the scheduling problems in semiconductor manufacturing factories, such as the wafer probing factories [65][68] and IC final testing factories [69]. Pearn et al. [65][68] have transformed the wafer probing

scheduling problem (WPSP) into the vehicle routing problem with time windows (VRPTW). They gave an illustrative example to demonstrate the proposed transformation and used the existing VRPTW algorithms to solve the WPSP near-optimally. They also developed three modified algorithms to solve the WPSP. In the IC final testing factories, Pearn et al. [69] applied the network algorithms designed for the VRPTW to solve the IC final testing problem with the characteristic of reentry based on the stage-by-stage solution strategy and full-load policy applied to batch-processing stages, so that the capacity of critical resources testers would be efficiently utilized. In this dissertation, the author took the merits of the VRPTW and applied the VRPTW algorithms to the scheduling problems with different job weights, sequence dependence setup times, due dates in module assembly factories.

2.4. Batch Processing Machine Scheduling Problems

In this dissertation, the aging test scheduling problem (ATSP) considers a parallel batch processing machine scheduling problem on the aging test operation in the module assembly process. In recent years, much research has focused on providing solutions to the batch processing machine (BPM) scheduling problems on a single or parallel batch processing machines. A comprehensive literature and a classification scheme on batch processing machine scheduling problems are presented by Potts and Kovalyov [73]. For the batch processing machine scheduling problems in semiconductor manufacturing, Mathirajan and Sivakumar [59] have provided a complete survey.

There are two types of batch processing machine scheduling problem, which are named as incompatible product family and compatible problem family. The former is

that jobs with different product families are mutually incompatible for processing in the same batch; the latter is assumed that jobs belonging to different product families may be simultaneously processed. In this dissertation, the aging test scheduling problem we investigated considers the batch processing of compatible product families. In problems of this type, the batch processing time is computed by the longest job processing time in that batch.

The literature regarding the BPM scheduling problems on a single or parallel batch processing machines with compatible product families is shown in Table 2-3. As presented in Table 2-3, the first researchers to address the batch processing scheduling problem arising in a burn-in oven of the final test in the semiconductor industry are Lee et al. [52]. They used dynamic programming-based algorithms and heuristics for a number of performance measures, such as maximum tardiness (Tmax), the number of

tardy jobs (

Ui ), and maximum lateness time (Lmax) on a single batch processingmachine. They have also presented heuristics for the parallel batch processing

machine scheduling problem with the minimum makespan (Cmax) and maximum

lateness time (Lmax) criteria. They have explored the area of scheduling batch

processing machines and offered a classification of complexity for the investigated problems. Furthermore, Chandru et al. [12][13], DuPont and Ghazvini [30], Poon and Yu [71], Mönch et al. [63] provided the solutions for the single/parallel batch processing machine scheduling problems with identical job sizes. Although the single batch processing machine scheduling problem (Uzsoy [86], Ghazvini and DuPont [37], Zhang et al. [94], DuPont and Dhaenens- Flipo [29], Melouk et al. [60], Erramilli

Table 2-3The literature related to the batch processing machine scheduling problem with compatible product families.

Year Authors and Refs. Shop type Ready time

Job size Performance criterion 1992 Lee et al. [52] single machine/

parallel machines unequal/ equal identical/ identical Tmax,

Ui , Lmax / Cmax, Lmax1993 Chandru et al. [12] single machine equal identical Cmax

1993 Chandru et al. [13] single machine/ parallel machines

equal identical Cmax

1997 DuPont and Ghazvini [30]

single machine equal identical Fi

2004 Poon and Yu [71] single machine equal identical

Ci2006 Mönch et al. [63] single machine equal identical

di Ci1994 Uzsoy [86] single machine equal non-identical Cmax,

Ci1998 Ghazvini and DuPont

[37] single machine equal non-identical Fi

2001 Zhang et al. [94] single machine equal non-identical Cmax

2002 DuPont, and Dhaenens-Flipo [29]

single machine equal non-identical Cmax

2004 Melouk et al. [60] single machine equal non-identical Cmax

2004 Damodaran and Srihari [25]

Two machines in a flow shop

equal non-identical Cmax

2006 Erramilli and Mason [31]

single machine equal non-identical

w Ti i2006 Kashan et al. [49] single machine equal non-identical Cmax

1999 Lee and Uzsoy [51] single machine unequal identical Cmax

2000 Sung and Choung [82] single machine equal/

unequal identical Cmax 2002 Sung et al. [83] single machine unequal identical Cmax

2002 Wang and Uzsoy [89] single machine unequal identical Lmax

2004 Li and Lee [55] single machine unequal identical Tmax,

Ui2004 Poon and Zhang [70] single machine unequal identical Cmax

2004 Deng et al. [26] single machine unequal identical

w Ci i2005 Deng et al. [27] single machine unequal identical

Ci2005 Poon and Yu [72] single machine unequal identical Cmax

2006 Gupta and Sivakumar [42]

single machine unequal identical Tmax,

Ui ,

T ni2004 Van Der Zee [87] single machine dynamic arrival

identical Fi

2004 Chang and Wang [15] single machine unequal non-identical

Ci2006 Chou et al. [21] single machine unequal non-identical Cmax

2007 Chou [20] single machine unequal non-identical Cmax

2007 Wang et al. [91] single machine unequal non-identical Cmax

2007 Chou and Wang [22] single machine unequal non-identical

w Ti i2004 Chang et al. [14] parallel machines equal non-identical Cmax

2007 Mönch and Unbehaun [64]

parallel machines equal identical

di Ci2007 Van Der Zee [88] parallel machines dynamic

arrival non-identical Fi 2008 ATSP (this dissertation) parallel machines unequal non-identical Cmax

and Mason [31], Kashan et al. [49]) and the two batch processing machines in a flow shop (Damodaran and Srihari [25]) took the non-identical job sizes into consideration to reflect more practical situations, they have assumed that the ready times of jobs for batch processing machines are equal. This assumption prevents the developed procedures from being directly applied to the parallel batch processing machine scheduling problem investigated in this dissertation because the ATSP involves unequal ready times.

For the single batch processing machine scheduling problem with non-identical job sizes and equal ready times, Uzsoy [86] investigated this type problem to minimize the total completion times (

Ci ) of the jobs and makespan. He has also provided bin-packing-based heuristics for minimizing makespan and has used the branch and bound approach to minimize the total completion times. He also developed effective heuristics for the criteria of minimum makespan and minimum total completion time. Erramilli and Mason [31] have investigated the multiple orders per job (MOJ) problem on a single batch processing machine. They grouped different customer orders into jobs and combined jobs into batches and scheduled them on a single batch processing machine to minimize the total weighted tardiness (

w Ti i ) of orders. Damodaran and Srihari [25] have proposed two mathematical models with the minimum makespan criterion to schedule batches of jobs on two machines in a flow shop. Kashan et al. [49] has addressed the need to minimize makespan by employing two different genetic algorithms (GAs) for scheduling jobs with non-identical sizes on a single batch processing machine. Unfortunately, all the abovemodels do not consider the unequal ready time that is a common phenomenon in module assembly factories.

Although Lee and Uzsoy [51], Sung and Choung [82], Sung et al. [83], Wang and Uzsoy [89], Li and Lee [55], Poon and Zhang [70], Deng et al. [26], [27], Poon and Yu [72], Gupta and Sivakumar [42], and Van Der Zee [87] have considered the characteristic of unequal ready times, they limited their applications to a single batch processing machine and an identical job size. Lee and Uzsoy [51] have provided efficient heuristics to solve the scheduling problem arising in the final test phase of semiconductor manufacturing. To minimize the maximum completion time on a single batch processing machine with dynamic job arrivals, they designed three algorithms (GRLPT, DELAY, and UPDATE) to find the approximate solutions. Sung and Choung [82] have presented a branch-and-bound algorithm and several heuristics to solve the static and dynamic cases on a single batch processing machine. Their objective was also to minimize the makespan of all jobs. Sung et al. [83] have considered a single batch processing machine with job families and dynamic job arrivals. The performance measure used to evaluate a schedule is the minimum makespan. Van Der Zee [87] has also presented the dynamic control of a batch processing machine; his objective was to find the minimum average flow time per product in the presence of compatible product families.

Moreover, in recent years, a series of research papers regarding single batch processing machine scheduling problem with unequal ready times and non-identical job size are provided by Chang, Chou, and Wang [15][20][21][22][91]. First, Chang and Wang [15] investigated the single machine problem of scheduling semiconductor

burn-in operation with non-identical job sizes and unequal ready time. They provided an efficient heuristic algorithm and examine the effect of arrival time and processing time on minimizing the total completion time. Subsequently, Chou et al. [21] changed the objective into minimal makespan and proposed a merge-split procedure to improve the solution obtained by the longest processing time batch first fit (LPT-BFF). Furthermore, two hybrid genetic algorithms (GA) were also provided. Following that, Chou [20] presented a solution procedure to joint GA and DP (dynamic programming). Wang et al. [91] provided a mix integer programming model to describe problem complexity. Simultaneously, a hybrid forward/backward algorithm is also presented and the computational results showed good performances of this algorithm in term of solution quality within a modest computational time. Moreover, Chou and Wang [22] took the distinct due date into consideration and investigated the single machine scheduling problem with a minimal total weighted tardiness criterion. They proposed one MIP model and two hybrid heuristics involving a rule-based, GA, and DP algorithms. The computational results indicated GA-based algorithm outperformed the rule-based algorithm in terms of solution quality for small size problems.

More recently, the parallel batch processing machine scheduling problem with compatible product family characteristic is considered by Mönch and Unbehaun [64], Chang et al. [14], and Van Der Zee [88]. Mönch and Unbehaun [64] presented a parallel batch processing machine scheduling problem in which jobs have identical job sizes and equal ready times. The objective is to minimize the sum of the absolute deviations of completion times from the due date of all jobs. They proposed three heuristics based on exact algorithm, genetic algorithm, dynamic programming

techniques. Chang et al. [14] have provided a mathematical model and developed an algorithm based on simulated annealing (SA) approach to minimize makespan for the scheduling problem with equal ready times and non-identical job size. They have not included the unequal ready times in their model. Van Der Zee [88] extended the scheduling problem [87] involved single machine to parallel machines. The objective of the parallel batch scheduling problem is to minimize average flow time per product. He developed a new look-ahead strategy to solve this problem. However, the processing time in his model is assumed fixed. Their solution procedure cannot be applied to ATSP directly.

At the time this dissertation was being written, the author was not aware of any other studies of the parallel batch processing machine scheduling problem with unequal ready time, non-identical job size, and compatible product family characteristics. Therefore, this dissertation arises from the need in industry to consider jobs with these practical situations, which are processed on identical parallel batch processing machines.

3. Algorithms for the Printed Circuit Board Bonding

Scheduling Problem

In this chapter, we address the first scheduling problem, the printed circuit board bonding scheduling problem (PCBSP), which is a practical variant of the classical parallel machine scheduling problem. The objective for the PCBSP is to maximize the total weighted throughput subject to fulfilling contracted quantities without violating the due dates and machine capacity restrictions. In this chapter, we present two heuristic procedures to solve the PCBSP efficiently based on some basic technologies used for developing algorithms for machine scheduling. Furthermore, computational results and performance comparisons are also provided.

3.1. Introduction

Printed circuit board bonding is the bottleneck resource in the module assembly process. The performance of the system is determined by this bottleneck operation according to the essential concept of theory of constraints (TOC) [41]. In this chapter, we consider the PCBSP in a module assembly factory with considerations of sequence dependent setup times and multiple job weights. For the PCBSP we investigated, jobs are clustered by their product types, which must be processed on any parallel machines and be completed before the due dates. Setup times between two consecutive jobs of different product types on the same machine are sequentially dependent. The job processing time may vary, depending on the product type of the jobs processed on. Furthermore, the hybrid market consists of contract and spot markets in the TFT-LCD industry. Therefore, jobs are given different weights, which are determined by the factors such as job’s profit

and customer importance. Since the PCBSP involved multiple job weights, with constraints on sequence dependence setup times, product type dependent processing times, due dates and machine capacity, it is more difficult to solve than the classical parallel machine scheduling problems.

The PCBSP we investigated can be modeled as a multi-level optimization problem. At the first level, we schedule the contract jobs to minimize the total setup time without violating machine capacity and customer due dates restrictions, which can be solved using algorithms for the vehicle routing problem with time windows (VRPTW) [65][68][69]. At the second level, we apply a greedy concept to choose a subset of spot jobs then insert into the schedules constructed in the first level. In this dissertation, we use basic technologies for VRPTW algorithms including parallel, generalized savings algorithms and provide two modifications to solve the PCBSP efficiently. To further analyze the impact of the problem characteristics on the performance of those savings algorithms, we provide a set of test problems, considering the workload level of contract jobs, tightness of due dates, setup time variation, and variation of contract/spot weight ratio. Exact solutions are used here as convenient reference points for evaluating the accuracy and effectiveness of our heuristic algorithms. The computational experiments and comparisons demonstrate the performance of the three phases of the modified parallel savings algorithm outperform the other algorithms.

3.2. Module Assembly Process and Problem Description

3.2.1. Module Assembly Process

The TFT-LCD applications include monitors, notebook PCs, mobile phones, portable DVDs, LCD TVs, and many others. Such applications are hundreds of product

types of job processed with sizes ranging from 1.6 inches to 46 inches. The manufacturing process of the module assembly generally consists of two main segments, front end and back end. It contains the following six processes, (1) COG (chip on glass) / TAB (tape automated bonding) process, (2) Flexible printed circuit board (FPC) attachment, (3) Printed circuit board (PCB) bonding, (4) Back light assembly, (5) Aging test, (6) Inspection, as presented in Figure 3-1. In the module assembly process, the critical resource is PCB bonding, which has the longest setup time and using anisotropic conductive film (ACF) to connects the PCB and FPC, as illustrated in Figure 3-2.

COG process

FPC attachment TAB process

PCB bonding Backlight

Assembly Aging test Inspection

Front end Back end

Figure 3-1The six steps in the module assembly process.

Figure 3-2PCB bonding illustration.

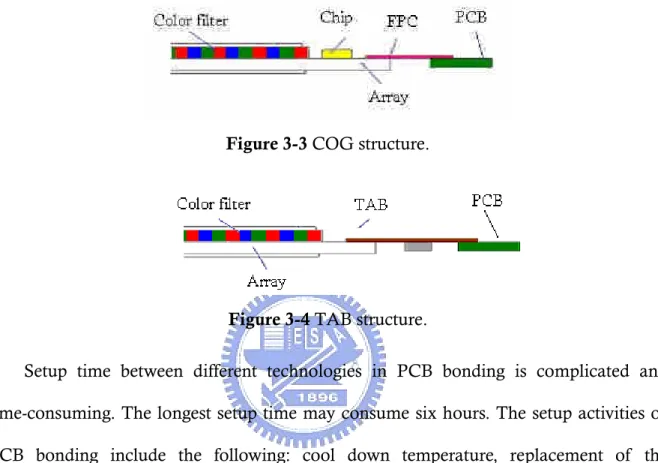

The processes of PCB bonding is determined by the types of mount technology of LCD drive IC and controller IC, namely, the COG (chip on glass) and TAB (tape automated bonding). The COG is a technology that mounts the LCD driver to the contact edge of the LCD glass, which is depicted in Figure 3-3. The TAB is the LCD driver or controller electronics are encapsulated in a thin film, like package, with metal leads extension from the IC chips, which is depicted as Figure 3-4. The process is also

called OLB (Outer Lead Bonding). In general, large size LCD applications (ranging from 15 inches to 46 inches) adopt the TAB structure and small size LCD applications (ranging from 1.6 inches to 6 inches) adopt the COG structure.

Figure 3-3COG structure.

Figure 3-4TAB structure.

Setup time between different technologies in PCB bonding is complicated and time-consuming. The longest setup time may consume six hours. The setup activities of PCB bonding include the following: cool down temperature, replacement of the appropriate mold, and the rising to a suitable temperature and voltage. Furthermore, setup times between two consecutive jobs of different product types on the same PCB bonding machine are sequentially dependent. In a similar product family, the setup activity may adjust the temperature and voltage. Different LCD panel sizes must replace the mold.

3.2.2. Printed Circuit Board Bonding Scheduling Problem

The scheduling problem in this chapter can be stated as follows. Let machine group

M = {mk| k = 1, 2, ... , K}, contain K machines, and product types H = {Hi| i = 1, 2, ... , I}, contain I clusters of jobs. Each job cluster Hi= {hij|j= 1, 2, ... , contract

i

contract i

J +1, …Ji}, representing the job set. Term contract i

J and Ji are the total number of

contract jobs and total number of jobs of product type Hi, respectively. Each job in their associated product type is a candidate to be processed without preemption on a set of parallel machines K.

Each job hij carries with its processing time denoted by pi, and weight denoted by ij

w , where i 1,2, ...,

I

and j 1,2, ...,

Ji

. For each job hij, rij represent the ready time of the job to be processed on a machine and eij represent the latest starting time to process job hij, which relates to the due dates dij and can be computed as eij dij pij.A setup time is incurred in the different product types. When job hij immediately

succeeds job hi jon machine mk , a setup time sii happens. The setup time is sequentially dependent on the product types of the jobs processed on the machine. The objective is to maximize the total weighted throughput without violating contracted due date and machine capacity, Cap.

3.2.3. An Illustrative Example

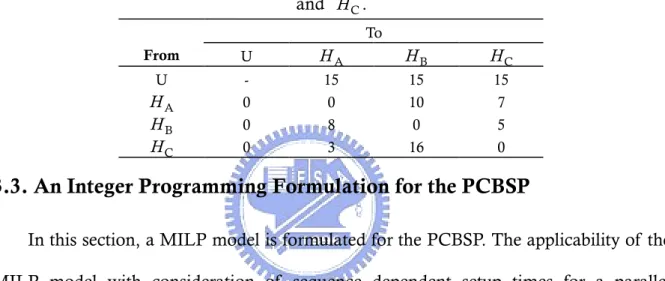

Consider the following example with two machines and seven jobs clustered into three product types. Table 3-1 displays the product type, processing time, job weight, due date, and contracted status for each job. Furthermore, the setup times are incurred for switching one product type to another for the three product types HA, HB, and HC. Table 3-2 shows the required setup times and the term U denotes that the machine is in idle status. The capacity is set to 95 for each machine in the illustrative example.

The objective in the illustrative example is to find a schedule for the subset of jobs, which satisfies the due date restrictions without violating the constraints of machine capacity, while maximizing the total weighted throughput.

Table 3-1The job information for the 7-job example. Job ID Product type Processing time Weight Due date Contract /Spot A1 h HA 21 50 80 C* A2 h HA 21 40 100 S** A3 h HA 21 40 100 S B1 h HB 25 60 93 C B2 h HB 25 50 100 S C1 h HC 28 63 100 C C2 h HC 28 63 60 C *Term C indicates the contract job. **Term S indicates the spot job.

Table 3-2Setup times required for switching one product type to another for HA, HB, and HC. To From U HA HB HC U - 15 15 15 A H 0 0 10 7 B H 0 8 0 5 C H 0 3 16 0

3.3. An Integer Programming Formulation for the PCBSP

In this section, a MILP model is formulated for the PCBSP. The applicability of the MILP model with consideration of sequence dependent setup times for a parallel machine scheduling problem has been demonstrated by Pearn et al. [66][67]. The objective function and some constraints of MILP model are modified to accommodate the PCBSP.

Let xijk be the variable indicating whether job hij is scheduled on machine mk, with xijk 1 if job hij is scheduled to be processed on machine mk, and xijk 0

otherwise. Let yiji j k be the precedence variable, where yiji j k should be set to 1 if job

i j

h is scheduled following job hij (not necessarily directly), and where yiji j k0

otherwise. Let ziji j k be the direct-precedence variable, with ziji j k1 if job hi jis scheduled immediately following job hij on machine mk, and ziji j k0 otherwise.

Further, the starting processing time tijk should be should not be less than the ready time, and not be greater than the latest starting time eij. The exact formulation for the PCBSP is as follows. Maximize

1 1 1 i J K I ijk ij k i j Z x w (3-1) subject to

1 =1, for 1, 2, ... , , 1, 2, ... , K contract ijk i k x i I j J (3-2)

1 1, for 1, 2, ... , , +1, +2, ... , K contract contract ijk i i i k x i I j J J J (3-3) Capacity constraints:

' ' ' 0 1 0 1 0 1 ( ) , for all i i Ji J J I I I ijk i iji j k ii i j i j i j x p z s Cap k (3-4)Due date constraints: , for all , , ijk ij ijk t r x i j k (3-5) , for all , , ijk ij ijk t e x i j k (3-6) Precedence constraints: ( 1) 0, for all , , ijk i ii i j k iji j k t p s t Q y i j k (3-7) ( 2) 0, for all , ,

ijk i ii i j k iji j k iji j k

t p s t Q y z i j k (3-8)

(yiji j k yi j ijk) Q x( ijk xi j k 2) 1, for all , ,i j k (3-9)

(yiji j k yi j ijk) Q x( ijk xi j k 2) 1, for all , ,i j k (3-10)

(yiji j k yi j ijk) Q x( ijk xi j k) 0, for all , ,i j k (3-11)

(yiji j k yi j ijk) Q x( i j k xijk 1) 0, for all , ,i j k (3-12)

(yiji j k yi j ijk) Q x( ijk xi j k 1) 0, for all , ,i j k (3-13)

for all , ,

iji j k iji j k

' ' 0 1 1, for all i ij i j J I ijk iji j k i j r r x z k (3-15) * * * * ( * * * * 2) ( 1) 2, for all , ,iji j k iji j k iji j k iji j k iji j k iji j k

y z Q y z Q y z i j k (3-16) Binary variables: {0, 1}, for all , , ijk x i j k (3-17) {0, 1}, for all , , iji j k y i j k (3-18) {0, 1}. for all , , iji j k z i j k (3-19)

The objective function (3-1) states that the total weighted throughput is to be maximized over all machines. Constraint (3-2) ensures that each contract job is scheduled on one machine exactly. Constraint (3-3) ensures that each spot job is scheduled at most one machine. Constraint (3-4) is the capacity constraint, which forces the sum of processing time and setup time for each machine within available capacity. Constraints (3-5) and (3-6) state that the starting time tijk for each job hij scheduled on machine

k

m should not be less than the earlier starting time rij and not be greater than the latest starting time eij. Constraints (3-7) and (3-8) are the starting time constraints. The time of the following job starts after the proceeding job and related setup is complete. As usual, Q is a ‘sufficiently large’positive number, so that constraints (3-9)-(3-13) are satisfied for

0

iji j k

y or 1. Constraints (3-9)-(3-13) are the precedence constraints and constraints

(3-14)-(3-16) are the direct constraints. These constraints state their sequence relation. In constraint (3-16), variable ziji j k* * states that there is a job hi j* * existing after job hij

when yiji j k1 and ziji j k0 . Constraints (3-17)-(3-19) indicate that xijk , yiji j k and

iji j k

z are binary integer variables. The total number of variables is 2 2

I

N K , and the total

number of equations is 3 (5 2) 2 (3 2) 2

I I I I