Proceedings of the 2001 IEEE

International Conference on Robotics & Automation Seoul, Korea. May 21-26, 2001

Modeling, Scheduling, and Prediction in Wafer Fabrication

Systems Using Queueing Petri Net and Genetic Algorithm

Hung-Wen, Li-Chen

Fu,

and Shih-Shmh Huang

Department of Computer Science and Information EngineeringNational Taiwan University, Taipei, Taiwan, R.O.C. Abstract--Wafer fabrication is one of the most competitive

manufacturing business in the world. In order to survive from such strongly competitive environment, finding an effective schedule which can result in higher machine utilization and throughput rate, shorter cycle time, and lower WIP (Work-In-Product) inventory becomes a major task. Besides that, in order to help customers to make ordering decisions as well as to let the manager control the processing conditions of the fab, we need to predict some pcrformance measures efficiently. In this paper, we propose a modeling tool named Queueing-Petri Net (Q-PN) which combines the characteristics of Queueing Theory and Petri Net. It can be used to model various detail of the manufacturing system a well as to get its performance evaluation very efficiently. Then, a general Q P N model is presented to simulate the semiconductor manufacturing system. Based on this model, we propose a Genetic Algorithm (CA) based scheduler and an analysis -based

predictor. In the CA scheduler, the chromosome represents

a combination of scheduling policies, including lot release policies, machine selection rules, dispatch rules and batch rules. So, when the CA finishes its optimization process, an

optimal scheduling policy is produced. As for the predictor,

because it inherits the analytical property of Queueing Theory from the Q-PN model, we can use it to predict those performance measures efficiently such as the exact due date of some particular lot.

1. Introduction

Wafer fabrication is the most costly phase of semi- conductor manufacturing [3]. A significant amount of risk is involved in the wafer fabrication because it requires huge investment costs and complex manu- facturing process. To survive from such competitive and risky environment, the company must not only reduce production cycle time and increase throughput rate but also meet customers’ due dates.

Recent papers by Uzsoy et al. [3,5] and Johri [4] highlight the difficulties in planning and scheduling of wafer fabrication facilities. These papers also survey the literature on releated topics. Effective shop-floor scheduling can be a major component of reduction in cycle time. The benefits of effective scheduling in- clude higher machine utilization, shorter cycle tine, higher throughput rate, and greater customer satisfac- tion. This is particularly true of semiconductor manu-facturing, with its rapidly changing markets and complex manufacturing processes [ 1,6,7,8]. Yet in many wafer fabrications the product spends much

more waiting time than actually being processed, so there is a large potential for reducing waiting time and a great benefit for doing so. It is well known in the scheduling literature that the general job shop prob- lem is NP-hard, which lead to no efficknt algorithm exists for solving the scheduling problems optimally in polynomial time for wafer fabrication, and there- fore it is the reason why we apply the genetic algo- rithm (GA) to approach the problem. GA is a search procedure that uses random choices 8 a guide tool through a coding in the parameter space [9- 131. While randomized, however, GAS are by no means a simple random-walk approach. They efficiently exploit hB- torical information to speculate on new search nodes with expected improved performance. That is, GA samples large search space randomly and efficiently to find a good solution in polynomial time, which however does not require enormous memory space as other traditional search algorithms such as A*. Many researchers have used GA to deal with job shop scheduling problem in traditional industries. Lee et al.

[ 121 focused on solving the scheduling problem in a flow line with variable lot sizes. Lee et al. [ 111 com- bined the machine learning and genetic algorithm in the job shop scheduling. Ulusoy et al. [13] have ad-

dressed on simulateneous scheduling of machines and automated guided vehicles (AGVs) using genetic alogrithm. In addition, Cheng et al. [lo] have sur- veyed relational topics on solving the job shop prob- lem using GA. They also discussed chromosome rep- resentation in details. Unlike the previous research, we use GA methodology to solve the more complex scheduling problem in wafer fabrication. However, since wafer fabrication is a complex discrete event system, schedulers cannot be easily realized on this kind of system, and thus how to model a complex wafer fab manufacturing system is a imperative task. In the modeling field, Petri Net (PN) has played an important role ; it has been developed into a powerful tool for discrete event systems, particularly in manu- facturing systems. PNs have gained more and more attentions in semiconductor manufacturing due to their graphical and mathematical advantages over tra- ditional tools to deal with discrete event dynamics and characteristics of complex systems [14-171. Zhou et al.

[ 151 reviewed applications of PNs in semiconductor manufacturing automation. It can also serve as a tuto- rial paper. The colored timed Petri net (CTPN) is used to model the furnace in the IC wafer fabrication [I71

and in the entire wafer fabrication manu-facturing system [14]. Jeng et al. [16] applied Petri net method- ologies to detailed modeling, qualitative analysis, and performance evaluation of the etching area in an IC wafer fabrication system located in the Science Based Industrial Park in Hsinchu, Taiwan.

In this paper, we propose a systematic color-timed Petri-Net (CTPN) model embedded with a genetic algorithm (GA) scheduler. The CTPN can be used to model the complex process flows in wafer fab efficiently and the detailed manufacturing charac- teristics. Also, new transitions are introduced in this paper, which significantly reduce the complexity of Petri-Net model. The GA scheduler can be used to dynamically search for an appropriate dispatching rule for each workstation or processing unit family through the CTPN model.

The organization of this paper is described as fol- lows. In Section 2, the definitions of the proposed color-timed Petri net (CTPN) are revealed here. And, the systematic method of CTPN model is discussed In Section 3 , a GA embedded search method over the CTPN model is employed. In Section 4, we demon- strate two example of using the proposed mechanism and analyze the performance. Finally, conclusions are provided in Section 5.

2. Wafer Processing Model

The o r h a r y PN do not include any concept of time and color. With this class of nets, it is possible only to describe the logical structure and behavior of the modeled system, but not its evolution over time and color. Responding to the need to model the manufacturing system in wafer fab, we add time and color attributes to the ordinary PN. In the proposed colored-timed Petri-Net (CTPN) model, we intro- duced three kinds of places, namely immediate (ordi- nary) places, timed places, and communication places, and five kinds of transitions, i.e., immediate (ordinary) transitions, colored transitions, mapping transitions, comparable transitions, and macro transitions. Also, we have introduced colored tokens in the CTPN model. For clarity, the tokens' color and transitions are described as follows.

Tokens

'

colorIn the CTPN model, the color of the tokens is &fined as a idigits number. The first two digits are defined as the product type, i.e., the route ID, and the last three digits are defined as the operation step that the product is performed now.

Immediate transitions

Immediate transitions are the same as the ordinary transitions. They can be used to model behaviors or events of resources in manufacturing systems. Colored transitions

There are a set of colored transitions T, and a set of color C in CTPN model. For all t E T, , which con- tains a color set

c(t)

.

We define that t E can be enabled with respect to the color c ifm ( p , c ) 2 I ( P , 4c),

vp

E P , C E C ( t ) ; whereP is the set of places in CTPN model.

m ( p , c ) is the number of tokens in p with respect to the color c.

~ ( p , t , c ) is the multiplicity of input arcs from p to

t with respect to the color c.

After the colored transition t is fired, the new marking

m'

becomes" ( p , c ) = m ( p , c ) + O ( p , t , c ) - I ( p , t , c ) .

In the CTPN model, the colored transition is drawn as

-.

Mapping transitions

The function of the mapping transitions is to transfer the token' s color c , to a predefmed color cz, i.e., after firing the mapping transitions, the color of the tokens that enable this type of transition is transferred to the predefined color of other kind. The other enabling and firing rules of the mapping transitions are the same as the ordinary transitions. In the CTPN model, the mapping transitions are drawn as m.

Comparable transitions

A comparable transition has two input arcs and two output arcs, which was drawn as m. One of the comparable transition' s output arcs is a regular arc; the other one is an inhibitor arc. Only one of the comparable transition' s output arcs can be enabled. The mechanism of the comparable transitions is that, the comparable transition compare the two token's color in the two input places, if the colors are the same, the regular output arc is active; otherwise, the inhibitor arc is active.

Macro transitions

Each macro transition contains a module of the model, and the module contains a set of subnets. In the CTPN model, the macro transitions are drawn as

.

.

In this paper, we used the proposed CTPN to model the whole wafer manufacturing systems which include the deposition, photolithography, etching, and diffu- sion areas. The wafer processing model we proposed is a general model, which does not focus on some special cases. In other words, when the equipment information is given, the wafer processing model is automatically generated by the model generator. Dif- ferent process flows of different products can be per- formed based on this model by changing the tokens' color, as long as these process flows were performed in the fab using the proposed CTPN model. The m- plementation of the model generator was discussed in Section 4, and the details of the proposed Wafer Processing Model including Routing Module and Elementary Module (see Figure 2) are described in the following sections.

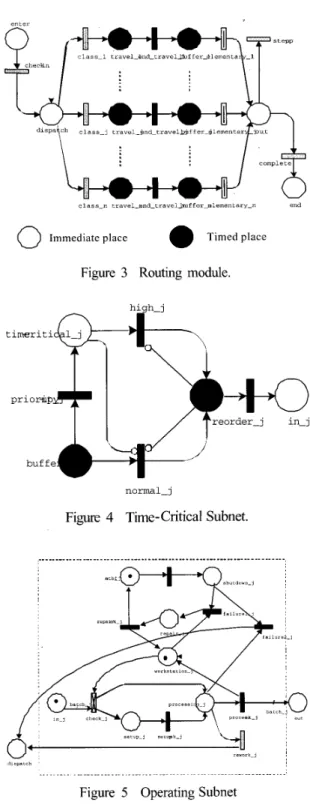

The purpose of the Routing Module is to model the logical process flow of the manufacturing systems. The basic concept of this module is described as fol-

lows. First, we divide all the machines in the fab into

n workstations (machine groups or processing unit family), each of which contains one or more identical machines (or processing units). At the beginning a token (lot) with the color xy000 enters the model, where xy is the route ID, and 000 is current operation step. Lots then checkin and the lots' color are changed to xy00 1, preparing to do the first operation. Each operation has its associated workstation to be per- formed, thus lots travel to and take operations in the proper workstation in the fab according to the prede- fined process flow. After the lot finishes the current operation, the lot' s color number will be increased by one, andJready to do the next operation. Step by step, after the lot fmishes all its operations, it enters the end place and finishes the work. The Routing Module which is shown in Figure 3 implements the idea above-mentioned. For clarity, we explain the nota- tions used in Figure 3 as follows:

The purpose of Operating Module is to model the detailed manufacturing system in a wafer fab, such as processing, setup, rework, scheduled machine main- tenance as well as unscheduled machine breakdown, and time-crit ical operation. We divide the Elementary Module into two subnets, which will be explained in details as follows.

Wafer Processing Model

U

Elementary Module I I

!

!

Routing Module1

Elementary Module1

Figure 2 Wafer processing model Time-Critical Subnet

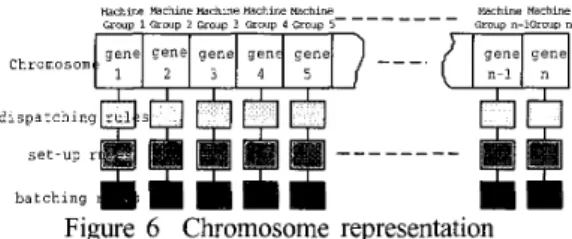

Time-Critical Subnet is shown in Figure 4. This subnet is used to avoid the rework in some time-critical operations. The idea of the Time-Critical Subnet is that if a lot is waiting for a time-critical q- eration, after waiting for some specific time period, the lot can get the higher priority and can be per- formed first. The notation used in Figure 4 is de- scribed below.

\

0

Immediate place TimedplaceFigure 3 Routing module.

high-j

t imeri ti

,

)

buffenormal-j

Figure 4 Time-Critical Subnet.

in-j

Figure 5 Operating Subnet Operating Subnet

Operating Subnet is shown in Figure 5. The pur- pose of this subnet is to model processing, machine setup, machine failure, and to check whether the lot needs to be reworked. Similarly, we explained the notation used in Figure 5 as follows.

For each rule, it is described as follows:

3. Wafer Fab Scheduler

In this paper, we allow our computation model to support the search algorithm over a color-timed place Petri-Net (CTPN) model, i.e., search can be performed in both axes of multiple resources and dif- ferent time segments. Here, we propose a new scheme to represent a schedule for the problem of production scheduling in wafer fab using GA embedded search over a CTPN model. The algorithm starts with an ini- tial set of random configurations called a population, which is a collection of chromosomes. The chromo- some here denotes a total scheduling solution for wa- fer fabrication. The size of the population is always fixed (N,,). Following this, a mating pool is estab- lished in which pairs of individuals from the popuh- tion are chosen. The probability of choosing a par- ticular individual for mating is proportional to its fa-

ness value. Chromosomes with higher fitness values have a greater chance of being selected for mating. Applying crossover (R,) to generate new offsprings. Mutation and inversion are also applied with a low probability. Next the offsprings generated are evalu- ated on the basis of fitness, and selecting some of the parents and some of the offsprings forms a new gen- eration. The above procedure is executed Ng times, where Ng is the number of generations. After a fixed number of generations

FE),

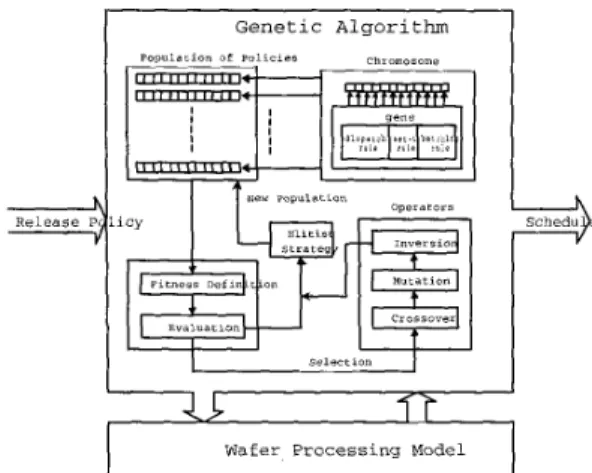

the fittest chromosome, i.e., the one with the highest fitness value is returned as the desired solution.Chromosome Representation

In this paper, we use priority rule-based representa- tion of chromosomes in the GA. This representation belongs to indirect approaches as described above, whch brings us the advantages such as the simplicity of the chromosome structure, simple GA operators, and shorter computation time. First, we define a gene place as follows:

4

: A gene place set is a subset of the place set, i.e.,P,

c P . A gene place p Ep,

is used to con- trol the scheduling in GA over CTPN model. The gene place in our CTPN model is denoted as the input buffer place of each machine group, that is, each machme group (identical machines) has a gene asso- ciated with it. A gene g = ( d , s , b ) is a three tuple where0 d : one type of dispatching rules.

0

s: one type of setup rules.0

b: one type of batching rules.The rules we selected for gene codes are listed in Ta- ble l.

Table 1 Gene codes

0

00

0 0 0FCFS: First Come First Serve.

MINS: Minimum Inventory at the Next Station

first. In this rule, a lot has a higher priority if its next operation workstation has a lower inventory.

SRPT: Shortest Remaining Processing Time first

EDD: Earliest Due Date first SSU: Same Set-Up first

WxT: Waiting for the arrival lot to complete the batch within x unit of lot inter-arrival time. When the batch is completed within this specific time period, the batch is started immediately. Otherwise, the partial batch is started right after one unit of lot inter-arrival time.

After genes are defined, the chromosome can be created. In this paper, the length of a chromosome is fixed, and is equivalent to the number of machine groups. The structure of the chromosome is depicted in Figure 6.

mchrne Machrne

Group n-1CrouD n

=&me WAC& MachineMachme Machine

C

" 1 Group 2 croup 3 Group 4 cmyp 5- - -

- -

- - ----

- -

- - - -- -

Figure 6 Chromosome representation Fitness FunctionIn this paper, we use three objective functions in our implementation. The fitness function is defined as follows:

f

(c> = Y.

.A

(c> + M'2.

f 2 ( 4 + w3 . h ( C >wherefi is the score for mean cycle time, f 2 is the score for throughput rate,

f 3 is the score for number of lots which meet

due date. Scheduler Builder

A schedule builder is dedicated to transform a chromosome to a feasible schedule, such that we can evaluate the aforementioned indirect chromosome representation. Based on the CTPN model, the evolu- tion of the system can be addressed by the change of marking in the net. Consequently, all possible kinds of behavior of the system can be completely tracked by the reachability graph of the net. In other words, we can track the WIP status from the CTPN model while the schedule was performed. Thus, given a CTPN model and a chromosome, the schedule builder can generate a feasible schedule in terms of the firing se-

quence of transitions in the CTPN model according to the chromosome. The firing squence of transitions

provides the order of the initiition of operations. The architecture of the scheduler was shown in Figure 7,

in which, we first select a lot release policy to control the timing for release of a lot (token) to the CTPN model. Second, apply the CA over the CTPN to find a good chromosome. Finally, use the schedule builder to transform the chromosome to a feasible schedule.

Genetic Algorithm

I

I

Selection

Figure 7 The architecture of the scheduler

4. Experiment Results

The simulation model we used in this paper is based on Wein's model [I]. It describes a fictitious wafer fab, but most of the parameters of the model are derived from data gathered at the Hewlett-Packard Technology Research Center Silicon fab (the TRC fab), which is a large R&D facility in Palo Alto, Cali- fornia. Unlike the model studied by Wein [l], we enlarge the capacity of the fab to increase the a m - plexity of the simulation. Moreover, we add the E-

work probability to the inspection machines, and de- fine the reworked step in each route. Batch processing machines are also included in our simulation model, so that the simulation model can be closed in real fab. We assume both of the workstations of TMNOX and PLM6 are batch-processing machines, and their batch size are 4 and 2, respectively. The entire fab contains 24 workstations (total 74 machines) in our simulation model, and three different process flows are defmed. Route I has 172 steps, and its total processing time is 494.6 hours. Route 2 has 139 steps, and its total prcc- essing time is 4 12.7 hours. Route 3 has 1 10 steps, and its total porcessing time is 346.7 hours.

Case 1: Three Orders for Total 100 Lots

The problem description is listed in Table 2 Table 2 Three orders Order ID Route Ouantitv (lots) Due Date

~ ~ ~~~~~

Order 01 Route 1 30 1999112118 08:OO

Older 02 Route 2 20 2000/01/03 08:OO

Order 03 Route 3 50 2000101113 08:OO

Current System Date: 1999/10/30

We evaluated the performance of the five schedul- ing policies, which are FCFS, SRPT, MINS, EDD, and GA. In addition, the four simple dispathcing rules plus SSU are also evaluated. For each scheduling pol- icy, we m 10 times of simulation and calculate mean value and standard deviation. The the compared E-

sults are listed in Table 3, where the three criteria are mean queueing time (MQT), throughput rate (TPR), and the rate of meeting due date (MDD).

Table 3 The compared result for case 1

Case 2: Four Orders for Total 80 Lots

Unlike the case 1, we have four orders in the case 2. Also, the route sequence we used as the input pattern in the case 2 is different from the case 1. Here we listed the four orders, and one compared result in Ta- ble 4, and Table 5, respectively.

Table 4 Four orders to be released into the fab Order ID Route Quantity (lots) Due Date Order 01 Route 2 20 1999112112 08:OO

Order 02 Route 3 20 1999/12/17 08:OO

Order 03 Route 1 10 1999/12/24 08:OO

Order 04 Route 3 30 200010 1104 08:OO

Current System Date: 1999110130

Table 5 The compared result for case 2

From Table 3 and Table 5, we found that the pro- posed GA scheduler performs much better than other conventional dispatching rules. It has a lower queue- ing time for lots spent in the fab, a higher throughput rate for a fab, and a higher rate for meeting the cus- tomers' due date. In addition, the experimental results show that the proposed GA scheduler has a lower variability on the total queueing time, throughput rate, and the rate of meeting due date, which increases the

accuracy of the simulation based prediction. As a re- sult, the proposed GA scheduler has a significant im- pact on wafer fab scheduling, by providing obvious improvements over the other conventional dispatching rules, even though the fab has a mixed production.

5. Conclusion

In this paper, we consider the wafer fab scheduling problem. We first proposed a systematic col- ored-timed Petri-Net (CTPN) model for a wafer fab. The entire CTPN model is composed of two modules, one is Routing Module, and the other is Elementary Module. The objective of the Routing Module is to model the logical process flow of the wafer fab manufacturing system. And, the Elementary Module is used to model the detailed manufacturing charac- teristics in wafer fab. In this paper, we also introduced many new transitions, which are useh1 to model some special issue and to significantly reduce the complex- ity of Petri-Net model in OUT study. In order to make better scheduling policies on wafer fab, we proposed a genetic algorithm scheduler, which dynamically searches for the appropriate dispatching rules for each machine group or processing unit family. Through the experiments, we found that the GA scheduler provides more superior performance than the conventional dispatching rules do. By using GA scheduler, we have a higher throughput rate for fabs, a shorter queueing time for lots spent in the fab, and a higher promising rate for meeting the customers’ due date.

Reference

Lawrence M. Wein, “Scheduling Semiconductor Wafer Fabrication,” IEEE Transactions on Semiconductor

Manufacturing, vol. 1, no. 3, pp. 115-130, 1988. Hong Chen, J. Michael Harrison, Avi Mandelbaum, Ann Van Ackere, and Lawrence M. Wein, “Empirical Evaluation of a Queueing Network Model for Semi- conductor Wafer Fabrication,” Operation Research, vol. 36, no. 2, pp. 202-215, 1988.

Reha Uzsoy, Chung-Yee Lee, Louis A. Martin-Vega, “ A Review of Production, Planning and Scheduling Models in the Semiconductor Industry Part$ ,,: System Characteristics, Performance Evaluation and Produc- tion Planning,” .IIE Transactions, vol. 24, no. 4. pp.

47-60, 1992. . ’

Pravin K. Johri, “Practical Issues in Scheduling and Dispatching in Semiconductor Wafer Fabrication,”

Journal ofManufacturing Systqms, vol: 12, no. 6, pp.

47445,1993.

Reha Uzsoy, Chung-Yee Lee, Louis A. Martin-Vega,

“ A . Review of Production Planning and Scheduling Models in the Semiconductor Industry Part C ” :

Shop-Floor Control,”. IIE Transactions, vol. 26, no. 5, pp. 44-55, 1994. ’

Shu Li, Tom Tang, and Donald W. Collins, “Minimum Inventory Variability Schedule with Applications in Semiconductor Fabrication,” IEEE Transactions on

Semiconductor Manufacturing, vol. 9, no. 1, pp.

171 Y. Narahari and L. M. Khan, “Modeling the Effect of Hot Lots in Semiconductor Manufacturing Systems,”

IEEE Transactions on Semiconductor Manufucturing,

vol. 10, no. 1,pp. 185-188,1997.

Yeong-Dae Kim, Dong-Ho Lee, and Jung-Ug Kim, “ A Simulation Study on Lot Release Control, Mask Scheduling, and Batch Scheduling in Semiconductor Wafer Fabrication Facilities,” Journal of Manufactur- ing Systems, vol. 17, no. 2, pp. 107-1 17, 1998.

[9] Sadiq M. Sait and Habib Youssef, VLSZ Physical a?-

sign Automation: Theory and Pratice, McGrawHill,

New York, 1995.

101 Runwei Cheng, Mitsuo Gen, and Yasuhiro Tsujimura, “ A Tutorial Survey of Job-Shop Scheduling Problems Using Genetic Algorithm, Part I: Representation,”

Computers and Industrial Engineering, vol. 30, no. 4,

pp. 983-997, 1996.

111 C. -Y. Lee, S. Piramuthu, and Y. -K. Tsai, “Job Shop Scheduling with a genetic algorithm and machine learning”, International Journal of Production Re- search, vol. 3 5 , 1 1 0 . 4 , ~ ~ . 1171-1191, 1997.

121 In Lee, Riyaz Sikora, and Michael J. Shaw, “ A Genetic AlgorithmBased Approach to Flexible Flow-Line Scheduling with Variable Lot Sizes”, IEEE Transac-

tions on Systems, Man, C y b e r n e t i c s q a r t B: Cyber- netics, vol. 27, no. 1, pp. 36-54,1997.

131 Gunduz Ulusoy, Funda Sivrikaya-Serifoglu, and Umit Bilge, “ A Genetic Algorithm Approach to the Simu 1- taneous Scheduling, of Machines and Automated Guided Vehicles,” Computer Operations Research, vol. 24, no. 4, pp. 335-351, 1997.

[14] M. H. Lin and L. C. Fu, “Modeling, Analysis, Simula- tion, and Control of Semiconductor Manufacturing Systems: A Generalized Stochastic Colored-Timed Petn.Net Approach,” IEEE fnternational Conference

on Systems Man, and Cybernetics, 1999.

[15] MengChu Zhou and Mu Der Jeng, “Modeling, Analy- sis, Simulation, Scheduling, and Control of Semicon- ductor Manufacturing Systems: A Petri Net Ap- proach,” lEEE Transactions on Semiconductor Manu-

facturing, vol. 11, no. 3, pp. 333-357,1998.

[16] Mu Der Jeng, Xiaolan Xie, and Shih Wei Chou, “Mod- eling, Qualitative Analysis, and Performance Evalua- tion of the Etching Area in an IC Wafer Fabrication System Using Petri Nets,” IEEE Transactions on

Semiconductor Manufacturing, vol. 11, no. 3, pp.

[17] Sheng-Ya Lin and Han-Pang Huang, “Modeling and Emulation of a Furnace in IC Fab Based on Col- ores-Timed Petri Net,” IEEE Transactions on

Senziconductor Manufacturing, vol. 11, no. 3 , pp.

410420,1998. 145-149,1996.

[8]