行政院國家科學委員會補助專題研究計畫成果報告

總計畫

計畫類別:□ 個別型計畫 ■ 整合型計畫 計畫編號:NSC-90-2215-E-009-111 執行期間: 90 年 8 月 1 日至 91 年 7 月 31 日 計畫主持人:吳錦川 國立交通大學電子所教授 共同主持人:吳重雨 國立交通大學電子所教授 吳介琮 國立交通大學電子所教授 計畫參與人員: 博士班 周忠昀、徐建昌、周儒明、 傅昶綜、蔡乙仲、范啟威、翟芸 碩士班 王文傑、康漢彰、陳宗明、蔡俊良、蔡淑惠、陳相志 成果報告類型(依經費核定清單規定繳交):□精簡報告 ■完整報告 本成果報告包括以下應繳交之附件: □赴國外出差或研習心得報告一份 □赴大陸地區出差或研習心得報告一份 □出席國際學術會議心得報告及發表之論文各一份 □國際合作研究計畫國外研究報告書一份 執行單位:國立交通大學電子研究所 中 華 民 國 92 年 1 月 10 日 子計畫一互補式金氧半射頻發收機前置電路模組設計IP建立及應用研究(III) 計畫編號:NSC-90-2215-E-009-108 執行日期:90年8月1日起至91年7月31日止 主持人:吳重雨 國立交通大學電子研究所 教授 計畫參與人員:周忠昀、王文傑、康漢彰、陳宗明、蔡俊良 一、摘要 本計畫擬以互補式金氧半製程,設 計低電壓以及低功率,適用於工作頻率 在幾十億赫茲的射頻前端積體電路。並 且,將設計應用在可攜式、多標準發收 機,並將電路建為 IP;這些積體電路 IP 核心電路將設計成可工作於各頻率範圍 的不同版本,以符合多標準發收機之要 求。 本 計 畫 以 TSMC 1P5M 0.25 μ m CMOS 設計並實現互補式金氧半射頻前 端 IP 核心電路,主要的 IP 核心電路如 下所示:(1) 低雜訊放大器(Low Noise Amplifiers)、(2)混波器(Mixers)、(3) 四 相位產生器(Quadrature Generators)、(4) 電 壓 控 制 振 盪 器 (Voltage Controlled Oscillators) 以 及 (5) 功 率 放 大 器 (Power Amplifiers)。 最後,這些互補式金氧半射頻前端 IP 電路,將整合並應用於在一單晶多標 準射頻前端發收機系統中。 關鍵詞:射頻前端發收機, 低雜訊 放大器, 混波器, 四相位產生器, 電壓 控制振盪器 Abstr act

This project is to design and implement a low-voltage, and low-power CMOS Radio- Frequency (RF) front-end integrated circuits (ICs). This RF Front-end IC will be implemented as an intellectual property (IP) cores which operate in the frequency range of Giga-Hertz, and the specifications of these IP cores will fit the requirements of multi-standard portable RF transceivers.

The CMOS RF front-end IP cores are designed and implemented in TSMC 0.25 μm standard CMOS process. The main IP circuits in this project consist of low noise amplifiers (LNAs), mixers, Quadrature generators, voltage- controlled oscillator (VCOs), and power amplifiers (PAs).

These IP cores circuits are tested and proven, and will finally be integrated and apply for a multi-standards RF transceiver prototype system on a single chip.

KeyWor ds: RF transceiver, low noise

amplifier, mixer, Quadrature generator, voltage- controlled oscillator, power amplifier

III 液晶監視器影像訊號擷取介面積體電路(III) 計畫編號:NSC-90-2215-E-009-109 執行日期:90年8月1日起至91年7月31日止 主持人:吳錦川 國立交通大學電子研究所 教授 計畫參與人員:蔡淑惠、陳相志 一、摘要 本計畫擬開發一個應用於高速串列 數位影像傳輸介面,使用最小轉換差動 信號的傳送器和接收器。 整個傳送器電路包含多相位之鎖相 迴路,十對一多工器及輸出驅動器。多 相 位 之 鎖 相 迴 路 的 輸 入 為 25MHz~165MHz,提供 10 個相位且輸 出頻率同樣為 25~165MHz 的時脈。 接收器部份,其輸入資料傳輸速率 範圍為 250 Mbs ~ 1.65 Gbs。而輸入時 脈 傳 輸 速 率 範 圍 為 25 MHz ~ 165 MHz。整體架構採用三倍頻取樣資料回 復演算法。 關鍵詞:傳送器、接收器、鎖相迴 路、多工器、驅動器、三倍頻 Abstr act

This plan is to develop a transmitter and receiver for a high-speed serial digital display interface

The transmitter consists of a multi-phase phase-locked loop (PLL), a 10-to-1 multiplexer and a data driver. The multi-phase PLL with input frequency range from 25MHz to 165MHz can offer ten-phase clock output that has

the same frequency with the input signal. In receiver part, The range of input

data transmission rate is 250 Mbs ~ 1.65 Gbs. And the range of input clock transmission rate is 25 MHz ~ 165MHz。 The overall system is based on three times oversampling data recovery algorithm.

KeyWor ds: transmitter 、 receiver 、

phase-locked loop (PLL)、multiplexer、 driver、three times oversampling

子計畫三 高速雙絞線網路發收機單晶片系統(III) 計畫編號:NSC-90-2215-E-009-110 執行日期:90年8月1日起至91年7月31日止 主持人:吳介琮 國立交通大學電子研究所 教授 計畫參與人員:徐建昌、周儒明、傅昶綜、蔡乙仲、范啟威、翟芸 一、摘要 本計畫將設計一個數位類比混合式 單晶片系統之發收機.此發收機將用於 雙絞線 250Mpbs 之資訊傳輸. 調變方式 是 根 據 Gigabit Ethernet 標 準 訂 定 的 125Mbaud 符元率 5 階之脈波振幅調變 (PAM). 較複雜之發收機功能, 如通道編碼和解碼, 等化, 以及時 序還原等, 將使用數位訊號處理之技術. 而類比電路, 如放大器, 數位類比轉化 器, 類比數位轉換器, 以及數位相位轉 換器等則是處於數位處理器和傳輸介質 之間的介面. 關鍵字:數位類比式混合式積體電 路,發收機,十億位元乙太網路,單晶片系 統 Abstr act

This project is to design a mixed-signaltransceiver system on a chip for 250 Mbpsdata transmission over an unshielded twistedpair (UTP) cable. Partially following the Gigabit Ethernet standard, a 5-level baseband pulse amplitude modulation (PAM) with 125 Mbaud symbol rate is assumed. Digital signal processing techniques are used in channelencoding/decoding, equalization, and timing recovery. Analog circuits, such as amplifiers, digital-to-analog converters, analog-to-digital converters, and digital-to-phase converters, provide the interface between the digita processor and the transmission media.

KeyWor ds: Mixed-Signal Integrated

Circuit,Transceiver, Gigabit Ethernet, System on A Chip

V 封面… … … .. I 子計畫一之中英文摘要… … … ...II 子計畫二之中英文摘要… … … ...III 子計畫三之中英文摘要… … … ...IV 目錄… … … ...V 子計畫一之報告內容… … … ....1 子計畫一之參考文獻… … … 3 子計畫二之報告內容… … … 4 子計畫二之參考文獻… … … 5 子計畫三之報告內容… … … 6 子計畫三之參考文獻… … … 8 子計畫一之報告內容

前言 近年來,由於無線行動通訊市場的 快速成長,帶動了對於低成本以及高性 能通訊積體電路晶片的大量需求。過 去 , 高 性 能 的 通 訊 用 電 路 大 多 使 用 Bipolar 的電路,並使用砷化鎵或矽化鍺 等較昂貴、整合不易的製程技術來實 現;而隨著 CMOS 製程的不斷進步,以 及金氧半電晶體效能的提升,電晶體操 作頻率(fT)的提高,再加上 CMOS 的 成本低廉,以及對於系統整合度高的優 點,使的如何利用 CMOS 來完成並實現 整個無線通訊系統於單一晶片,成為了 近年來熱門的一個研究領域[1]-[6]。 圖(一)為一個通訊系統所使用的射 頻發收機的簡單架構,主要可以分為兩 個部分,即接收機(Receiver)以及發射 機(Transmitter)。 接收機內部的主要模組電路包含了 低雜訊放大器(Low Noise Amplifiers)、 降 頻 混 波 電 路 (Down-conversion Mixers)、以及中頻率波器( IF Filters)。 低雜訊放大器將接收到的訊號放大的同 時,電路本身的雜訊能不被放大,使電 路的輸出端的訊雜比(SNR)提高,如 此 可 以 降 低 系 統 的 雜 訊 指 數 ( noise figure, NF),由於是在整個接收機的最 前端,對整個系統的 sensitivity 影響最 大,如何在提供足夠訊號增益時,降低 此 LNA 的 NF,為設計 LNA 的重要著 眼處。降頻混波器將載波的頻率降低以 利後級的率波器做頻道的選擇,為了避 免所要訊號頻道在降頻時受到其他的頻 道的干擾,降頻混波器的線性度很重 要 , 此 外 , 對 於 鏡 像 頻 率 ( image frequency)的雜訊抑制也是降頻混波器 設計的重要的考量。 ~ Antenna

LNA Mixer Filter

VCO PA Mixer Filter 圖一 射頻收發機架構 發射機內部的主要模組電路包含了升頻 混 波 器 ( 即 一 般 所 謂 的 調 變 器 , modulators ), 以 及 功 率 放 大 器 (Power Amplifier) 。 調 變 器 將 由 基 頻 (Base-Band)送來的 I-Q 訊號調變至載 波頻率後,經由功率放大器將訊號傳送 出。由於目前無線通訊系統的頻帶寬度 逐漸變寬,設計一個高線性度的功率放 大 器 , 避 免 訊 號 間 的 交 互 調 變 (inter-modulation),並且在高線度下能 夠提供高的功率效益,已減低功率消耗 為設計功率放大器的一個重要考量。要 能夠得到一個高性能的通訊系統,射頻 前端電路的優劣,將是個非常重要的決 定要素。 電路設計 詳細電路架構於子計畫中有仔細說明, 下面傞列出使用到的電路區塊名稱和電 路圖 1) 低 雜 訊 放 大 器 ( Low Noise Amplifier) INPUT M1 M2 Mb Qb M3 R1 R2 Rb Cd Ld Ls Lg OUT + OUT -VDD GND 2.4GHz 低雜訊放大器 2) 正 交 相 位 調 變 器 ( Quadrature Modulator)

3 M34 M35 M33 M36 M37 M38 M39 M40 VDD R1 R2 R3 R4 R5 R6 R7 R8 VDD VDD VDD VDD VDD VDD VDD VDD M10 M9 M11 M12 M14 M13 M15 M16 M18 M17 M19 M20 M22 M21 M23 M24 VB2 VDD Z1 Z2 VO1 VO2 VBX+v1 VBX-v1 VBX+v3 VBX-v3 VBY+v2 VBY-v2 VBY+v4 VBY-v4 VB1 M49 正交相位調變器 3) 電壓控制振盪器與電感電容負載的 全差動反相器 INV2 INV1 -R1 -R2 L1 C1 L2 C2 VI VQ VC I 兩級環狀震盪器方塊圖 L1 AM1 M1 M2 Vin1 Vin2 VCO1 VCO2 VDD VDD M6 M5 AM2 CC1 VC1 Type B combiner Type B combiner VB1 C B1 M47 M48 電感電容負載的全差動反相器 4) 四 相 位 產 生 器 ( Quadrature generator) 2.5V Bias Vtune in+ in-out180 out000 out090 out270 5) 功率放大器 C6 R5 bias2 M7 M5 Out+ RFC VDD2 M8 M6 Out-L5 C8 C10 C11 RFC C7 R6 L6 C9 M1c L4 M2c M3c VDD1 In+ R3 C3 C1 R1 bias1 M3 M1 C5 L3 In-R4 C4 C2 R2 M4 M2 L1 L2 兩級之功率放大器 結論 目前已完成的 IP 有:低雜訊放大 器、正交相位調變器、電壓控制振盪器、 四相位產生器以及功率放大器。低雜訊 放大器具有低雜訊、低功率消耗和高線 性度等特性。正交相位調變器使用了電 流重覆使用的原理,大幅度的降低功率 消耗,在電路的性能上,經過四個 corner 的模擬驗證後,皆能滿足需求。電壓控 制振盪器可產生一組相位精確正交的 LO 信號,其可調頻率範圍在 2.65GHz 到 2.15GHz 間,涵蓋 2.4GHz ISM 頻帶。 四 相 位 產 生 器 可 以 涵 蓋 整 個 2.4GHz ISM 頻帶並產生準確的 4 個正交相位的 輸出。功率放大器的設計中,一個兩級 串接的差動功率放大器被設計達到足夠 的輸出功率及優良的效率,具有偶次諧 波消除效果及對震盪器信號產生較小干 擾的優點。 計畫成果自評 目前已完成射頻前端電路各個 IP 模組的設計以及量測驗證無誤。初步的 結果證明這一些 IP 電路可適用於低功 率的無線通訊系統中。 參考文獻

[1] A. Rofougaran et al., “A 1GHz CMOS RF front-end IC for a direct-conversion wireless receiver,”IEEE J. Solid-State Circuits, vol. 31, pp. 880-889, July 1996.

Microelectronics, Prentice Hall, 1998.

[3] A. Abidi, et. Al., “The Future of

[4] CMOS Wireless Transceivers,” International Solid-State Circuits Conference, pp. 118-119, Feb. 1997.

[5] K. C. Tsai, and P. R. Gray, “A 1.9 GHz 1W CMOS Class E Power Amplifier for Wireless Communications,” 24th European Solid-State Circuits Conference, The Hague, Netherlands, Sept. 1998.

[6] K. C. Tsai, and P. R. Gray, “A 1.9 GHz 1W CMOS Class E Power Amplifier for Wireless Communications,” 24th European Solid-State Circuits Conference, The Hague, Netherlands, Sept. 1998.

[7] P. Gray, et. Al., “A 1.9-GHz Wide-Band IF Double Conversion

[8] CMOS Receiver for Cordless Telephone Applications,” IEEE J.

of Solid-State Circuits, pp.2071-2088, December 1997. 子計畫一之報告內容 研究方法與成果 詳細電路架構於子計畫中有仔細說明, 下面傞列出使用到的電路區塊名稱和電 路圖 傳送器設計原理與架構 1)傳輸器架構圖

5 P s e u d o R a n d o m G e n e r a t o r C l k I n 1 0 D a t a C a p t u r e L o g i c P L L D a t a I n 1 0 C l k [ 0 : 9 ] 1 0 : 1 D a t a M u x S w i n g C o n t r o l T x T x + T x -1 0 : -1 E m p h a s i s M u x C l k [ 0 : 9 ] o u t + o u t -e m u x o u t + e m u x o u t - C l k [ 0 : 9 ] 傳輸器基本架構圖 2)鎖相迴路架構圖 Ref. Clock Phase/Fr eq. Detector Char ge Pump Loop Filter Voltage Contr ol Oscillator Inter nal Clock Up Down ‧‧‧ clk[0:9] 十個相位的鎖相迴路時脈產生器 3) 十對一多工器電路 (a) (b) 圖三. 十對一多工器電路 4) 輸出振福調整電路 輸出振福調整電路 5) 傳輸線驅動器 傳輸線驅動器 接收器設計原理與架構 1)接收器架構圖 Demultiplexing Receiver DLL ( 6 stages ) PLL ( 12 stages ) Phase Selector Phase Shifter Control Logic Synchronizer Serializer 24 12 24 2 12 12 4 4 Dout Dout Din + Din -CLKin + CLKin

-Receiver Block diagram 2) Tracking mechanism

CLK1 CLK2 CLK3 CLK4 CLK5 CLK6 CLK7 CLK8 CLK9 CLK10 CLK11 CLK12

Lag Lag Lag Lag

Input Data Stream

CLK1 CLK2 CLK3 CLK4 CLK5 CLK6 CLK7 CLK8 CLK9 CLK10 CLK11 CLK12

Lead Lead Lead Lead

Input Data Stream

CLK1 CLK2 CLK3 CLK4 CLK5 CLK6 CLK7 CLK8 CLK9 CLK10 CLK11 CLK12

Lock Lock Lock Lock

Input Data Stream (a) (b) tracking mechanism 晶片怖局

Transmitter Chip Floorplane

Receiver Chip Floorplane 成果計畫自評

也部份完成當初的期望,整個 funtion 是 正常,只是可能因為一些小地方因為經 驗不足導致沒有辦法達到整個規格的要 求,經驗累積起來之後,再做相關的應用 電路,應該都不成問題. 參考文獻 [1] F. M. Gardner, “Charge-Pump Phase-Lock Loops,” IEEE Transactions on Communications, Vol. COM-28, pp. 1849-1858, November 1980.

[2] W.J. Dally, et al., “Transmitter Equalization for 4-Gbps Signaling, ” 1997 IEEE Micro, pp.48-56

[3] Ming-Ju Edward Lee, William Dally, Patrick Chiang, “A 90mW 4Gb/s Equalized I/O Circuit with Input Offset Cancellation, ” 2000 IEEE ISSCC, pp.252-253

[4] Alan Fiedler, Ross Mactaggart, James Welch, Shoba Krishnan, “A 1.0625Gbps Transceiver with 2x-Oversampling and Transmit Signal Pre-Emphasis, ” 1997 IEEE ISSCC, pp.238-239

[5] J. G. Maneatis, “Low-jitter process-independent DLL and PLL based on self-based techniques,” IEEE Journal of Solid-State Circuits, vol. 31, pp. 1723–1732, November 1996.

7

子計畫三之報告內容 Motivation and Objectives

Deep submicron CMOS technologies have Enabled cost-effective multi-million-transistor integrated circuits capable of powerful digital computing. As a results of such advances, high-performance digital communication systems, that employ sophisticated signal processing techniques to overcome transmission media imperfections and various interferences, have become a.ordable to the average consumers and filled the need for ever growing broadband services.

In a modern physical-layer transceiver, although most signal processing functions are performed in the digital domain, analog circuitry is always required for interfacing between the digital functional units and the transmission media. A good design methodology that enable both the analog and digital functional blocks to operate together monolithically is the key to realize a successful transceiver system on a chip (SOC).

This project is investigate the mixedsignal SOC design techniques for implementing a broad-band network transceiver. The transceiver will be designed for high-speed data transmission over an unshielded twisted pair (UTP) cable in the LAN environment following the Gigabit Ethernet standard [1]. In

addition, new mixed-signal circuit techniques will be investigated for transceiver functions such as automatic gain control, digital-toanalog converters, analog-to-digital converters, and timing recovery.

Accomplishments

Tr ansceiver Ar chitectur e

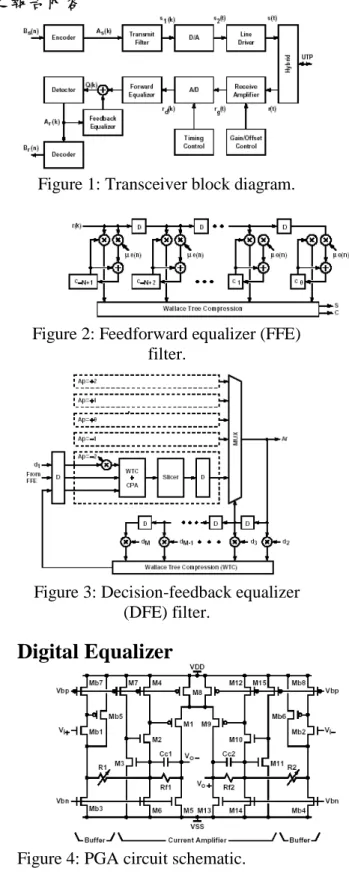

Figure 1: Transceiver block diagram.

Figure 2: Feedforward equalizer (FFE) filter.

Figure 3: Decision-feedback equalizer (DFE) filter.

Digital Equalizer

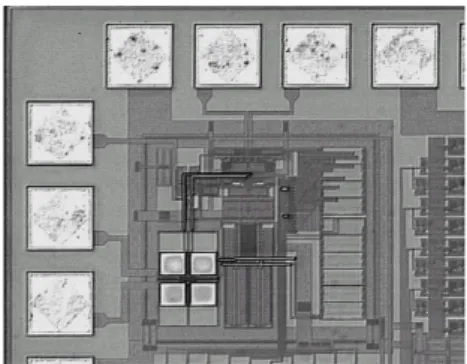

Figure 5: PGA chip microphotograph.

PGA

Figure 6: SHA block diagram.

SHA

Figure 7: SHA chip microphotograph.

Figure 8: DPC block diagram

DPC

Figure 9: DPC chip photograph.

Conclusions

In this project, we have studied the modern broad-band transceiver architectures, which utilize complex signal processing techniques and multiple adaptive control loops. A C++ mixed-signal simulation platform has been established for full transceiver simulation. Several key functional blocks have been studied and realized in silicon, which include a fully-digital cell-based 125 MHz adaptive equalizer, a 125 MHz constant bandwidth programmable-gain amplifier with high linearity, a 100 MHz low-distortion sample-andhold amplifier, and a 125 MHz 8-bit digitalto-phase converter. Those functional blocks have specifications better than the original transceiver requirements, and can be used in other high-performance applications such as software radios. A new low-voltage class-AB UTP driver and a new pipelined analog-to-digital converter are still under investigation.

9

Refer ences

[1] “Physical layer specification for 1000 Mb/s operation on four pairs of category 5 or better balanced twisted pair cable (1000BASE-T),” IEEE Draft P802.3ab.

[2] SystemC User’s Guide, Version 1.1 ed.

[3] Z.-M. Lee and J.-T. Wu, “A 125 MHz digital equalizer for high-speed ethernet,” in VLSI Design/CAD Symposium, August

2001.

[4] C.-C. Hsu and J.-T. Wu, “A 125 MHz .86 dB IM3 programmable-gain amli-fier,” in Symposium on VLSI Circuits Digest

of Technical Papers, June 2002, pp. 32–34.

[5] — — , “A 33-mW 12-bit 100-MHz sample-and-hold amplifier,” in IEEE Asia-Pacific Conference on ASIC, August 2002, pp. 169–172.

[6] K. Bult and A. Buchwald, “An embedded

240-mW 10-b 50-MS/s CMOS ADC in 1-mm2,” IEEE J. Solid-State Circuits,

vol. 32, no. 12, pp. 1887–1895, December 1997.