Wide Tunning Range 60 GHz VCO and 40 GHz DCO

Using Single Variable Inductor

Tai-You Lu, Chi-Yao Yu, Wei-Zen Chen, Senior Member, IEEE, and Chung-Yu Wu, Fellow, IEEE

Abstract—This paper presents a 60 GHz, 16% tuning range

VCO, and a 40 GHz, 18 bits, 14% tuning range DCO incorpo-rating variable inductor (VID) techniques. The variable inductor, consisting of a transformer and a variable resistor, is tunable by adjusting its resistor. By employing the proposed frequency tuning scheme, wide-tuning range as well as multi-band operation are achieved without sacrificing their operating frequencies. To verify the operation principles, the VCO and DCO are both fabricated in 90 nm CMOS technology. The tuning range of VCO is from 52.2 GHz to 61.3 GHz. The measured phase noise from a 61.3-GHz carrier is about 118.75 dBc/Hz at 10-MHz offset, and the output power is 6.6 dBm. It dissipates 8.7 mW from a 0.7-V supply, and the chip size is . On the other hand, the DCO is capable of covering frequency range from 37.6 GHz to 43.4 GHz. The measured phase noise from a 43 GHz carrier is about 109 dBc/Hz at 10-MHz offset, and the output power is 11 dBm. The DCO core dissipates 19 mW from a 1.2-V supply. Chip size is

.

Index Terms—Digital controlled oscillator (DCO),

millimeter-wave (MMW) band, ultra wide band (UWB), variable inductor (VID), voltage controlled oscillator (VCO).

I. INTRODUCTION

S

HORT RANGE multi-Gbps wireless interconnects have motivated marvelous research efforts recently [1]–[11]. At 60-GHz unlicensed frequency band, a 7-GHz wide spectrum is available for up to 6-Gbps UWB applications. With the rapid developments of the VLSI process, nano-meter CMOS are con-sidered as promising technologies to make RFICs for the broad-band wireless interconnects feasible and cost effective.In the RF transceiver front-end, LC voltage-controlled oscil-lators (VCOs) are extensively used in frequency synthesizers to provide local carriers for up and down frequency conversion. Thus its performance is essential to the wireless transceiver. Major design issues of the VCO are focused on oscillating fre-quency, phase noise, output power level, and frequency tuning range. For portable devices, its power dissipation is also of spe-cial concern.

Conventionally, millimeter-wave (MMW) band LC-VCOs employ accumulation-mode MOS (A-MOS) varactors for Manuscript received October 17, 2011; revised February 09, 2012; accepted March 06, 2012. Date of publication October 22, 2012; date of current version January 24, 2013. This work was supported in part by National Nano Device Laboratories (NDL), Ansoft Corporation, United Microelectronic Corporation (UMC), and National Science Council (NSC), Taiwan, R.O.C.. This paper was recommended by Associate Editor H. Luong.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan (e-mail: wzchen@alab.ee.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2012.2215795

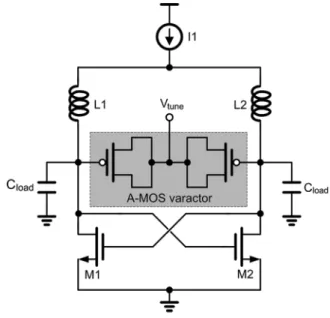

Fig. 1. The schematic of LC-VCO.

frequency tuning [12]–[17]. Fig. 1 shows a typical schematic of LC-VCO. The VCO oscillation frequency can be approximated as

(1) where , , and respectively represent the inductance, varactor capacitance, and loading capacitance at the resonator. Here the loading capacitance also includes the parasitic capac-itance contributed by the succeeding buffer stage. In order to achieve 60-GHz operating frequency, the varactor capacitance and the corresponding tuning range are severely limited due to . This issue becomes even more critical under low supply voltage, which is required for nanometer CMOS oper-ation.

It is well known that the phase noise performance of a VCO degrades when the VCO gain, , increases [19]. However, for a single band VCO, is proportional to its oscillating frequency for the same frequency tuning percentage. Consid-ering an oscillator with 10% frequency tuning range and 1-V tuning voltage, its is 180 MHz/V at oscillating frequency of 1.8 GHz, but increases to 6 GHz/V if its output frequency is raised to 60 GHz. Therefore, for broadband MMW applications, multi-band VCO is necessary to degenerate VCO gain and alleviate phase noise performance degradation. However, conventional capacitor bank for multi-band operation is hardly applicable in the 60-GHz case since the in the capacitor bank is too large to be tolerable. Some magnetic tuning methods have been reported [20]–[25] to increase the frequency tuning ranges 1549-8328/$31.00 © 2012 IEEE

Fig. 2. (a) The proposed variable inductor. (b) Equivalent circuit model.

of LC-tank VCOs though, their oscillation frequencies are far less than 60 GHz.

In this paper, a 60-GHz varactor-less VCO and an 18 bit, 40 GHz DCO for multi-band operations employing a novel variable inductor (VID) are proposed [26]. Based on magnetic tuning scheme, they achieve multi-band as well as broad-band operations without sacrificing their oscillation frequencies. Measurement results show that the VCO’s output frequency ranges from 52.2 GHz to 61.3 GHz. The corresponding tuning percentage is 16.07%. It manifests strong potential to be applied in the 60-GHz band UWB system. Also, the VCO is capable of operating under a supply voltage as low as 0.7 V, which is suitable for nano-meter CMOS technology. On the other hand, the measured output frequency of the 40 GHz DCO is distributed from 37.6 GHz to 43.4 GHz, corresponding to 14% tuning range. It can be applied in a dual-IF receiver for 60 GHz UWB system [27]–[29].

This paper is organized as follows. In Section II, the proposed VID and its tuning schemes are described. Section III presents the VCO and DCO design. The experimental results of the two oscillators are shown in Section IV. Finally, conclusion is drawn in Section V.

II. PRINCIPLE OF THEVARIABLEINDUCTOR(VID)

A. VID Schematic and Equivalent Circuit Model

Fig. 2(a) illustrates the schematic of the proposed VID, which consists of a transformer and a variable resistor . and respectively represent the self inductance of the primary and secondary coils of , is the coupling factor of the primary and secondary coils, and is the parasitic capacitor at the sec-ondary coil. The VID can be modeled as a variable inductor in parallel with a variable resistor , as is illustrated in Fig. 2(b). Both and are functions of and the radian frequency . It can be derived that

(2) and

(3) If the self resonant frequencies of and are larger than the

operating frequency , i.e., , increases with

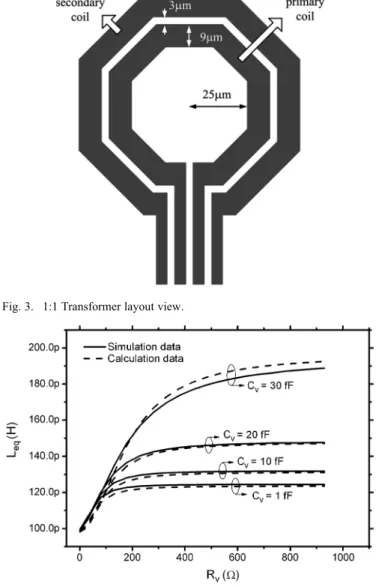

Fig. 3. 1:1 Transformer layout view.

Fig. 4. Simulated and calculated at 60 GHz.

the increment in . Thus, the minimum equivalent inductance is equal to , and can be calculated as

(4) Contrarily, the maximum equivalent inductance is equal to , and can be calculated as

(5) From (4) and (5), it can be seen that only depends on the parasitic capacitance , and its lower bound is (i.e., ). Under this circumstance, the lower bound of the inductance tuning ratio can be derived as

(6)

On the other hand, if , may become

non-monotonic against , and even become negative if is too large. When the VCO’s tuning characteristic is not monotonic, it will result in false locking of a PLL.

Fig. 5. Simulated and calculated at 60 GHz.

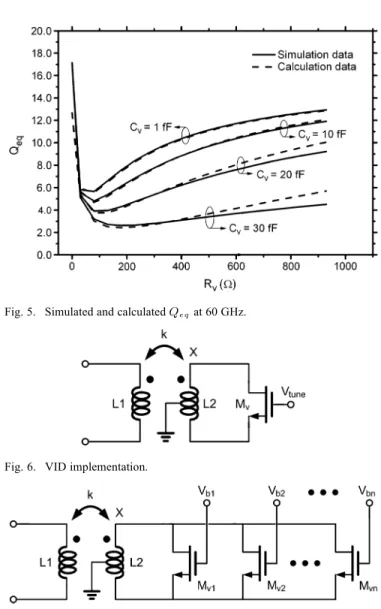

Fig. 6. VID implementation.

Fig. 7. Multi-band variable inductor.

Fig. 3 shows the layout of the transformer used in the simula-tions. The inner radius of the primary (secondary) coil is 25 (37 ); the metal width is 9 ; and the space between the first and second coils is 3 . By EM simulation, the self-res-onant frequency of the transformer is about 194 GHz. The self inductance of the primary (secondary) coil is about 123 pH (175 pH), and the coupling factor is about 0.45 at 60 GHz.

Fig. 4 shows the EM simulation results of against under different at 60 GHz. The derived in (2) is also shown for comparison. It can be seen that increases along with the increment in . And the inductance tuning ratio is larger than or equal to (i.e., 0.2) in all cases. Also, only depends on as predicted by (5). The proposed lumped circuit model in Fig. 2(a) can accurately represent VID’s inductance. In Fig. 4, it can also be seen that is proportional to when

is less than 100 . The linear range of can be derived from (2) and approximated as , where

(7) Under this circumstance, the tunable inductor within the linear region can be described as

(8) which is also independent of at the secondary coil.

The other important parameter of the proposed VID is its quality factor . By taking the parasitic resistors into account, the can be calculated as shown in the equation at the bottom of the page, where is the equivalent parasitic resistor of the primary coil. The detail derivation of (9) is shown in Appendix.

When and at around 60 GHz, the EM simulated

and calculated under different are plotted against , as is shown in Fig. 5. The frequency response of the quality factor has a V shape, which reveals that the VID has a better quality factor in the extreme cases where is nearly short or open cir-cuit. In either case the magnetic energy dissipated in the passive

can be minimized.

When the VID is integrated in an LC oscillator, its oscillation frequency can be approximated as

(10) where is the center frequency of the VCO, is the inductance at , and is the inductance tuning range. According to (10), the frequency tuning characteristic of an LC-VCO can be linearized by a linear control of VID.

B. VID Tuning by MOSFET Resistors (VID-I)

The proposed VID can be modified to achieve multi-band op-eration. Here in Fig. 6 is decomposed into several smaller devices in parallel, as is shown in Fig. 7. Each smaller device is separately controlled by voltages . As the device size of is equal to those of

in total, the parasitic capacitance at node in Fig. 7 is al-most the same as that in Fig. 6. Thus, multi-band operation can be achieved without severely affecting the inductance and the tuning percentage of the VID. This is a major advantage in con-trast to conventional capacitor-bank structure, where the par-asitic capacitor in general contributes significantly to the total capacitance at the oscillating node, and thus limits the tuning range. Also, the variable resistors occupy smaller silicon area compared to varactors or metal-insulator-metal capacitors, thus a small form factor can be benefited.

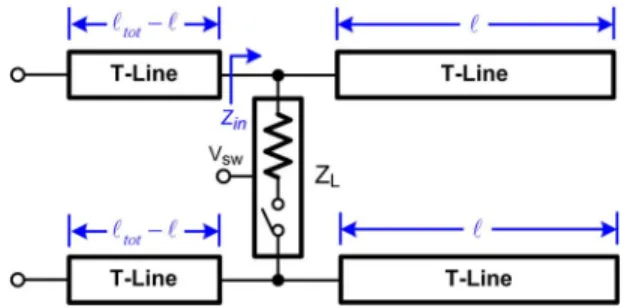

Fig. 8. A reconfigurable transmission line.

Fig. 9. VCO schematic.

C. VID Tuning by Reconfigurable Transmission Line (VID-II)

As is revealed in Fig. 4 and (8), a linear tuning of depends on a linear control of . For high resolution frequency tuning, it is difficult to be realized using parallel MOSFETs resistors. Although it can be achieved by adopting predistortion DAC to provide adequate dc bias for the switchable MOSFETs, a so-phisticated design may be required. Another potential solution is to reconfigure the switchable MOSFETs resistors in a series way, but large devices are required as is imposed by . It turns out that the self resonant frequency of the VID is severaly limited. In order to develop a linear tuning scheme for VID to facilitate all digital PLL application, a VID tuning by reconfig-urable transmission line is proposed.

Fig. 8 illustrates the schematic of tunable resistor, which is composed of a switch controlled by in parallel with an open stub transmission line . Assuming that the turn on resiatnce of the switch is , it can be shown that the input impedance looking into the open stub can be derived as

(11) where and respectively represent the characteristic impedance and phase velocity of the transmission line. If

Fig. 10. The simulated and of VID-I based on EM simulation.

Fig. 11. VCO small-signal model.

Fig. 12. The 4 bits linear VID.

, the real part of can be approximated as

(12) which is proportional to . Thus the real part of is tunable by positioning the switches to reconfigure the effective length of transmission line.

III. CIRCUITDESIGN

To verify the operation principle of the proposed VIDs, two experimental prototypes are implemented and demonstrated. In Section III-A, a 60 GHz VCO using a VID with MOSFET variable resistors is described. It features broadband as well as multi-band operations, and can be integrated in a PLL to degenerate VCO gain for lower phase noise performance. On the other hand, a 40 GHz DCO using a VID with reconfigurable transmission line is introduced in Section III-B. It shows higher resolution in frequency tuning and also facilitates integration in an all digital phase locked loop (ADPLL).

Fig. 13. (a) The EM simulated and calculated . (b) Equivalent induc-tance and quality factor of 4-bits VID-II based on EM simulation.

A. 60 GHz Multi-Band VCO

The detail schematic for 60 GHz, multi-band VCO is show in Fig. 9. In order to reduce the parasitic capacitance at the res-onator, the negative impedance converter is composed of and cross-coupled pair. is an output buffer to drive the 50- load for measurement, and is a dummy buffer to bal-ance the parasitic capacitbal-ance at the resonator.

The variable resistors consists of six binary-weighted

NMOSFETs controlled by digital codes ( – )

for band switching, and an NMOS controlled by for fine frequency tuning. Thus and are tunable by

adjusting or . The second coil is center

tapped to ground, so as to diminish dc power dissipation. For a better quality factor, the self resonant frequency at the secondary port caused by and the parasitic capacitance of MOSFETs should be designed to be higher than the operating frequency of the VID.

In the experimental prototype, a single-turn 1:1 transformer is adopted in the VID, as is shown in Fig. 3. To illustrate and

across different band of operations, and are wired together and controlled by . The simulated and of VID (VID-I) at 60-GHz are illustrated in Fig. 10. When changes from 0.3 to 1.2 V, the is tunable

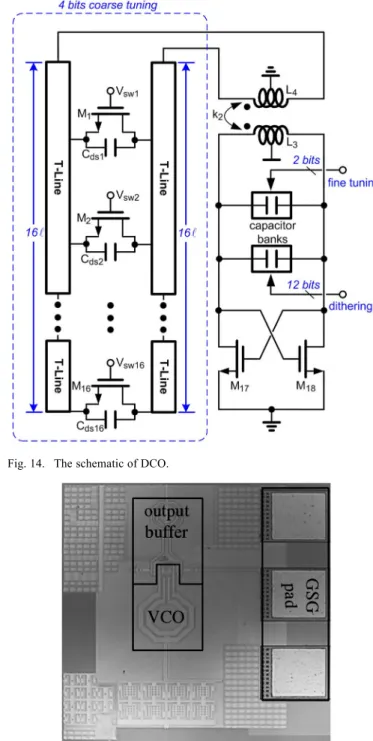

Fig. 14. The schematic of DCO.

Fig. 15. VCO chip micrograph.

from 142 to 103 pH (i.e., ), and the quality factor is changed from 11.35 to 3.6. The VID has a better quality factor when MOSFET resistors are nearly fully turned on or off, i.e., is minimum or maximum. This agrees pretty well with the calculated results shown in (9) and Fig. 5.

The equivalent small-signal model of the VCO is shown in Fig. 11. Here represents the total capacitance at the res-onator, including the parasitic capacitances of the cross-cou-pled pair , the output buffer , and the parasitic capacitance of the transformer . is the equivalent resis-tance looking into the primary coil of the VID, as is derived in (3). The negative resistance provided by the cross-coupled pair M1 and M2 is denoted as , which is approximately equal to , and is the small-signal transconductance

Fig. 16. Measured/simulated frequency tuning characteristic and output power of 60 GHz VCO.

of . must be smaller than to guarantee oscil-lation start-up. In this design, is chosen to be smaller than within the entire frequency range. The oscillating fre-quency of the VCO can be derived as

(13) , and the upper and lower bound of output fre-quencies are

(14) and

(15) Based on (14) and (15), the VCO frequency tuning percentage can be derived and is approximated by , which is deter-mined by the coupling factor of the transformer. Therefore, for a VCO with a given transformer to implement the VID, its frequency tuning range can be quickly estimated. In this design, the coupling factor of the transformer is around 0.45, it turns out that the frequency tuning range of the VCO is at least 10%.

B. A 40 GHz DCO With Linear Frequency Tuning

To further linearize the frequency tuning characteristic of VID, a 40 GHz DCO with reconfigurable transmission line is implemented. Fig. 12 shows the detail schematic of a 4-bits linearly controlled VID (VID-II) for coarse tuning. The trans-mission line is divided equally into 16 segments with 16 MOS switches attched on it. Thus the effective length of the open stub is programable by the switches, and the parasitic capacitance associated with the MOS switches can be absorbed along the transmission line. Based on (7) and (8), the frequency tuning

Fig. 17. Measured VCO tuning characteristics under different supply voltages.

Fig. 18. Measured frequency tuning characteristics of all bands of the 60 GHz VCO.

range of the DCO with linear frequency tuning can be derived as

(16) The physical length of the transmission line is 15 . By EM simulation, , and of the transformer are 100 pH, 129 pH and 0.6, while and are 46 and 0.08 respectively. It turns out that the corresponing frequency tuning range is at least 13% according to (16).

Fig. 13(a) shows the EM simulated and that derived by (12). Both illustrate linear characteristic along the tuning range. Fig. 13(b) shows the equivalent inductance and quality factor of the linearly controlled VID by EM simulation. The corre-sponding inductance is distributed from 58 pH to 82 pH, while Q is varied between 5.5 to 3.8 due to the change of real part of

.

Fig. 14 shows the detail schematic of the 40 GHz digitally controlled oscillator (DCO). The DCO has 4 bits for coarse tuning with VID-II, 2 bits for fine tuning with varactors, and 12 bits dithering though varactor controlled by a 2nd order

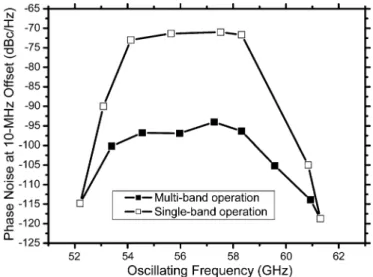

Fig. 19. Measured phase noise at 10-MHz offset in single-band and multi-band operation of the 60 GHz VCO.

modulator at 400 MHz. The corresponding minimum gain of the DCO is about 24 kHz/step.

IV. MEASUREMENTRESULTS

A. 60 GHz Single and Multi-Band VCO

Fig. 15 shows the chip micrograph of the 60 GHz VCO.

The core size is . The chip is measured on

a high-frequency probe station. With , the mea-sured and simulated frequency tuning characteristics are shown in Fig. 16. If the tuning voltages of and in Fig. 9 are tied together and varied from 0.3 to 1.2 V, the single band VCO frequency is changed from 52.2 to 61.32 GHz. The cor-responding tuning percentage is 16.07%. With a reduced tuning range of 0 V to 0.7 V, the tuning percentage becomes 13.98%. After the loss from the output buffer, probes, cables, adapters, and external mixer is deembedded, the measured single-ended output power are also shown in Fig. 16. Here the simulation sults are also shown for comparison. From the measurement re-sults, the VCO output power varies from 10 dBm to 4 dBm within the entire frequency tuning range.

The VCO can start oscillation as VDD is larger than 0.37 V. The measured frequency tuning ranges for VDD from 0.4 V to 0.9 V are shown in Fig. 17. When , the VCO has the maximum frequency tuning range from 54.07 to 64 GHz (i.e., 16.8% at 59 GHz). Under this circumstance, the parasitic capacitance introduced by negative impedance converter is min-imized.

Multi-band operation is achieved by digitally controlling – and fine-tuning separately. By the mixed-mode frequency tuning scheme, the VCO manifests 64 frequency bands incorporating binary weighted transistors – , as is shown in Fig. 18. The maximum is 720 MHz/V at band 8, which is reduced by 10 fold compared to that of a single-band operation. The uniformity of multi-band operations can be improved by more sophisticated transistor sizing instead of employing binary-weighted transistors.

Fig. 20. Measured output spectrums of the 60 GHz VCO at (a) 52.19 GHz (b) 54.55 GHz (c) 61.3 GHz.

The measured phase noise performance at 10-MHz offset within the entire frequency tuning range is plotted in Fig. 19. By multi-band operation, the phase noise performance ranges from 94 to 118.75 dBc/Hz, and the average phase noise is 102.44 dBc/Hz. If – and are tied together for a single-band frequency tuning, the measured phase noise is also shown for comparison. It can be observed that phase noise per-formance can be significantly improved by 10 to 30 dB em-ploying the proposed multi-band operation scheme.

Fig. 20(a)–(c) show the measured VCO output spectrums at different frequencies. When , the measured average power consumptions of the VCO core within the frequency tuning range is 8.7 mW. The buffer stage dissipates 5.6 mW.

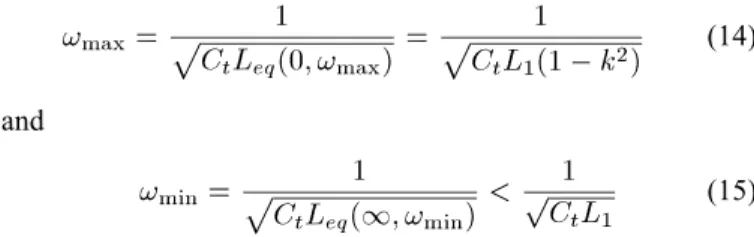

Fig. 21. DCO chip microphotograph.

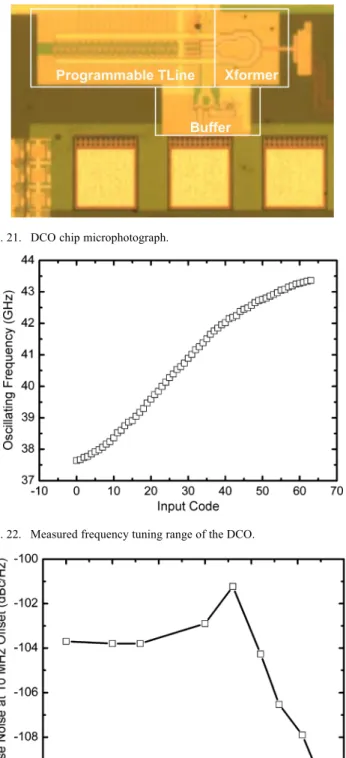

Fig. 22. Measured frequency tuning range of the DCO.

Fig. 23. Measured DCO phase noise at 10-MHz offset of the DCO.

B. A 40 GHz DCO With Linear Frequency Tuning

The chip micrograph of 40 GHz DCO is shown in Fig. 21. The

core size is . The DCO consumes 20 mA under

a 1.2 V power supply. Two on-chip DCO buffers are adopted to drive testing equipment and succeeding divider in a PLL respec-tively. They contribute a total capacitance of 90 fF. As the DCO has 4 bits for coarse tuning with VID-II, 2 bits for fine tuning with varactors, and 12 bits dithering though varactor controlled by modulator, the measured output frequency versus digital control codes (coarse fine) is shown in Fig. 22. The output

Fig. 24. Measured output spectrums of the 40 GHz DCO at: (a) 38 GHz; (b) 41.6 GHz; (c) 43.3 GHz.

frequency covers from 37.6 GHz to 43.4 GHz, which can be ap-plied in a dual-IF 60 GHz UWB system (38.8 GHz to 43.2 GHz). The proposed DCO has 14% tuning percentage. The measured fine tuning step using varactor bank is about 100 MHz/step. By dithering unit varactor through a 12 bit, 2nd order mod-ulator at 400 MHz, the corresponding minimum resolution is

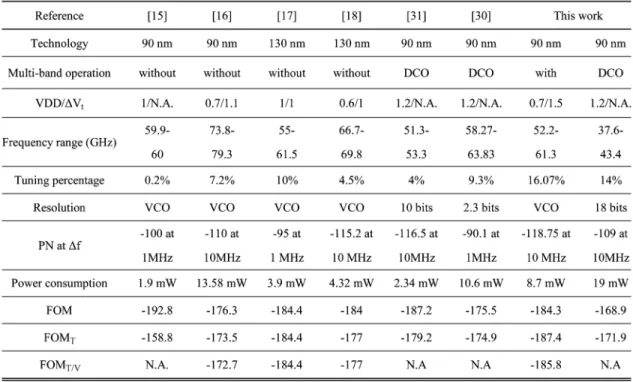

TABLE I PERFORMANCEBENCHMARK

about 24 kHz/step by simulation. Taking signal loss caused by experimental setup into account (including the loss of probes, cables and adapters), the output power varies from 15 dBm to 11 dBm due to the variation of quality factor within the entire frequency tuning range. The measured phase noise per-formance at 10-MHz offset within the entire frequency tuning range is plotted in Fig. 23. Fig. 24 shows the measured VCO output spectrums at different frequencies.

The performance benchmark of the proposed oscillators and the prior art in the literature are summarized in Table I. Three different figures of merits are illustrated to investigate their ad-vantages. They are

(17) (18)

(19) where is the phase noise at the offset frequency , is the oscillating frequency, is the power consumption, is the frequency tuning percentage, and is tuning voltage range. For over 50-GHz operating frequency, the proposed VCO has the widest frequency tuning range, the best and . On the other hand, the proposed DCO has the widest tuning range for over 40 GHz operation frequency, while also manifests the finest frequency resolution of 24 kHz. Compared to the FoM of VCO, it suggests that the Q-factor of DCO tank is compromised with resolution and tuning range.

Fig. 25. The modified lump model of the VID.

V. CONCLUSION

Novel variable inductors for VCO and DCO are proposed in this paper. By using the proposed frequency tuning scheme, both VCO and DCO are capable of operating at MMW fre-quency band while manifesting wider tuning range than those VCOs with varactors for frequency tuning. In addition, multi-band operation can be achieved without sacrificing its oscil-lating frequency or consuming large chip area. Both the VCO and DCO are capable of operating at supply voltage as low as 0.7 V. They manifest strong potential to be applied in the 60-GHz UWB system.

APPENDIX

Fig. 25 shows the modified lumped model of the VID to an-alyze its equivalent quality factor . and respectively represent the parasitic resistors at the primary and secondary coils. The input impedance can be calculated as

where

(21) In general, is much smaller than . Thus, when

, can be simplified as

(22) The equivalent quality factor of the VID can be calculated as shown in the equation at the top of the page.

REFERENCES

[1] C. H. Doan, S. Emami, A. M. Niknejad, and R. W. Brodersen, “Mil-limeter-wave CMOS design,” IEEE J. Solid-State Circuit, vol. 40, no. 1, pp. 144–155, Jan. 2005.

[2] B. Razavi, “A 60-GHz CMOS receiver front-end,” IEEE J. Solid-State

Circuit, vol. 41, no. 1, pp. 17–22, Jan. 2006.

[3] B. Razavi, “CMOS transceivers for the 60-GHz band,” in IEEE Radio

Freq. Integr. Circuit Symp. Dig., San Francisco, CA, Jun. 2006, pp.

11–13.

[4] T. Yao, M. Gordon, K. Yau, M. T. Yang, and S. P. Voinigescu, “60-GHz PA and LNA in 90-nm RF-CMOS,” in IEEE Radio Freq. Integr. Circuit

Symp. Dig., San Francisco, CA, Jun. 2006, pp. 147–150.

[5] S. Emami, C. H. Doan, A. M. Niknejad, and R. W. Bronderson, “A 60-GHz down-converting CMOS single-gate mixer,” in IEEE Radio

Freq. Integr. Circuit Symp. Dig., Long Beach, CA, Jun. 2005, pp.

163–166.

[6] A. Hajimire, “mm-wave silicon ICs: Challenges and opportunities,” in IEEE Custom Integr. Circuits Conf. (CICC) Dig., Sep. 2007, pp. 741–747.

[7] B. Razavi, “A millimeter-wave CMOS heterodyne receiver with on-chip LO and divider,” IEEE J. Solid-State Circuit, vol. 43, no. 2, pp. 477–485, Feb. 2008.

[8] C. S. Wang, J. W. Huang, S. H. Wen, S. H. Yeh, and C. K. Wang, “A CMOS RF front-end with on-chip antenna for V-band broadband wireless communications,” in Proc. Eur. Solid-State Circuit Conf., Sep. 2007, pp. 143–146.

[9] S. Emami, C. H. Doan, A. M. Niknejad, and R. W. Brodersen, “A highly integrated 60 GHz CMOS front-end receiver,” in IEEE Int.

Solid-State Circuit Conf. Dig., Feb. 2007, pp. 190–191.

[10] A. Parsa and B. Razavi, “A 60 GHz CMOS receiver using a 30 GHz LO,” in IEEE Int. Solid-State Circuit Conf. Dig., Feb. 2008, pp. 190–191.

[11] T. Mitomo, R. Fujimoto, N. Ono, R. Tachibana, H. Hoshino, Y. Yoshi-hara, Y. Tsutsumi, and I. Seto, “A 60-GHz CMOS receiver with fre-quency synthesizer,” IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 1030–1037, Apr. 2008.

[12] H. Wang, “A 50 GHz VCO in 0.25 CMOS,” in IEEE Int.

Solid-Satate Circuits Conf. Dig. Tech. Papers, Feb. 2001, pp. 372–373.

[13] M. Teibout, “A 51 GHz VCO in 0.13 CMOS,” in IEEE Int.

Solid-Satate Circuits Conf. Dig. Tech. Papers, Feb. 2002, pp. 300–301.

[14] C. Cao and K. K. O, “Millimeter-wave voltage-controlled oscillators in 0.13- technology,” IEEE J. Solid-State Circuits, vol. 41, no. 6, pp. 1297–1304, Jun. 2006.

[15] D. Huang, W. Hant, N.-Y. Wang, T. W. Ku, Q. Gu, R. Wong, and M.-C. F. Chang, “A 60 GHz CMOS VCO using on-chip resonator with embedded artificial dielectric for size, loss and noise reduction,” in IEEE Int. Solid-Satate Circuits Conf. Dig. Tech. Papers, Feb. 2006, pp. 314–315.

[16] K. Ishibashi, M. Motoyoshi, N. Kobayashi, and M. Fujishima, “76 GHz CMOS voltage-controlled oscillator with 7% frequency tuning range,” in Symp. VLSI Circuit Dig. Tech. Papers, Jun. 2007, pp. 176–177. [17] J. Borremans, M. Dehan, K. Scheir, M. Kuijk, and P. Wambacq, “VCO

design for 60 GHz applications using differential shielded inductors in 0.13 CMOS,” in IEEE Radio Freq. Integr. Circuit Symp. Dig., Atlanta, GA, Jun. 2008, pp. 135–138.

[18] H. K. Chen, H. J. Chen, D. C. Chang, Y. Z. Juang, and S. S. Lu, “A 0.6 V, 4.32 mW, 68 GHz low phase noise VCO with intrinsic-tuned technique in 0.13 CMOS,” IEEE Microw. Wireless Compon. Lett., vol. 18, no. 7, pp. 467–469, Jul. 2008.

[19] N. H. W. Fong, J. O. Plouchart, N. Zamdmer, D. Liu, L. F. Wagner, C. Plett, and N. G. Tarr, “Design of wind-band CMOS VCO for multiband Wirless LAN application,” IEEE J. Solid-State Circuit, vol. 38, no. 8, pp. 1333–1342, Aug. 2003.

[20] M. Demirkan, S. P. Bruss, and R. R. Spencer, “Design of wide tuning-range CMOS VCOs using switched coupled-inductors,” IEEE J.

Solid-State Circuits, vol. 43, no. 5, pp. 1156–1163, May 2008.

[21] L. Geynet, E. D. Foucauld, P. Vincent, and G. Jacquemod, “Fully-in-tegrated multi-standard VCOs with switched LC tank and power con-trolled by body voltage in 130 nm CMOS/SOI,” in Proc. IEEE Radio

Freq. Integr. Circuit Symp., 2006.

[22] S. Rong and H. C. Luong, “Analysis and design of transformer-based dual-band VCO for software-defined radios,” IEEE Trans. Circuits

Syst. I, Reg. Papers, vol. 59, no. 3, pp. 449–462, Mar. 2012.

[23] G. Liu, R. Berenguer, and Y. Xu, “A MM-wave configurable VCO using MCPW-based tunable inductor in 65-nm CMOS,”

IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 58, no. 12,

pp. 842–846, Dec. 2011.

[24] J. Yang, C.-Y. Kim, D.-W. Kim, and S. Hong, “Design of a 24-GHz CMOS VCO with an asymmetric-width transformer,” IEEE Trans.

Cir-cuits Syst. II, Exp. Briefs, vol. 57, no. 3, pp. 173–177, Mar. 2010.

[25] A. Tanabe, K. Hijioka, H. Nagase, and Y. Hayashi, “A novel variable inductor using a bridge circuit and its application to a 5–20 GHz tunable LC-VCO,” IEEE J. Solid-State Circuits, vol. 46, no. 4, pp. 883–893, Apr. 2011.

[26] C.-Y. Yu, W.-Z. Chen, C.-Y. Wu, and T.-Y. Lu, “A 60-GHz, 14% tuning range, multi-band VCO with a single variable inductor,” in IEEE

Asian Solid-State Circuits Conf. Dig. Tech. Papers, Nov. 2008, pp.

129–132.

[27] I. Bashir, R. B. Staszewski, O. Eliezer, B. Banerjee, and P. T. Balsara, “A novel approach for mitigation of RF oscillator pulling in a polar transmitter,” IEEE J. Solid-State Circuits, vol. 46, no. 2, pp. 403–415, Feb. 2011.

[28] J. Zhang, K. Waheed, and R. B. Staszewski, “A technique to reduce phase/frequency modulation bandwidth in a polar RF transmitter,”

IEEE Trans. Circuit Syst. I, Reg. Papers, vol. 57, no. 8, pp. 2010–2207,

Aug. 2010.

[29] R. B. Staszewski, R. Staszewski, J. L. Wallberg, T. Jung, C.-M. Hung, J. Koh, D. Leipold, K. Maggio, and P. T. Balsara, “SoC with an integrated DSP and a 2.4-GHz RF transmitter,”

IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13,

no. 11, pp. 1253–1265, Nov. 2005.

[30] T. LaRocca, J. Liu, F. Wang, D. Murphy, and F. Chang, “CMOS digital controlled oscillator with embedded DiCAD resonator for 58–64 GHz linear frequency tuning and low phase noise,” in Proc. IEEE Int. Micro.

Symp., Jul. 2009, pp. 685–688.

[31] R. Genesi, F. M. De Paola, and D. Manstretta, “A 53 GHz DCO for mm-wave WPAN,” in Proc. IEEE Custom Integr. Circuits Conf., Sep. 2008, pp. 571–574.

Tai-You Lu was born in Taipei, Taiwan, in 1980. He

received the B.S. degrees in electrical engineering from National Cheng-Kung University, Tainan, Taiwan, in 2003, and the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2011.

He has been with MediaTek Inc., Taiwan, since 2011, where he is working on analog IC design. His current research focused on mixed-signal integrated circuit for wireless and wireline communication sys-tems.

Dr. Lu is a member of Phi-Tau-Phi honorary scholar society.

Chi-Yao Yu (M’10) was born in Taipei, Taiwan, in

1978. He received the M.S. degree in communica-tion engineering from Nacommunica-tional Tsing Hua Univer-sity, Hsinchu, Taiwan, in 2002, and the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, in 2008.

He has been with MediaTek Inc., Taiwan, since 2008, where he is working on analog and RF IC design for wireless communications. His current research interest is ultra-high dynamic range receiver for cellular system.

Wei-Zen Chen received the B.S., M.S., and Ph.D.

degree in electronics engineering from National Chiao-Tung University, Hsin-Chu, Taiwan, in 1992, 1994, and 1999, respectively.

He was with ITRI/ERSO in 1999 involved in the development of CMOS RF ICs for cellular and wire-less LAN applications. From 1999 to 2002, he was an assistant Professor at the Department of Electrical Engineering, National Central University, Chung-Li, Taiwan. Since 2002, he joined the Department of Electronics Engineering, National Chiao-Tung Uni-versity, where he is now a full Professor. His research focuses on mixed-signal integrated circuit for wireless and wireline communication systems, with special emphasis on Serdes, high speed interface, optical communication, wireless PAN, LAN, and body area network applications.

Dr. Chen was the deputy executive director of National SoC (NSoC) Program in Taiwan from 2009–2011, and is the principal investigator of National Project on Intelligent Electronics (NPIE) in Taiwan since 2011. He also serves as IEEE Solid-State Circuit Society Taipei Chapter chairman starting from 2008. He was the technical program vice chair of 2008 VLSI/CAD design symposium, tech-nical program chair of 2012 symposium on engineering, medical, and biology applications (SEMBA), and the guest editor of International Journal of Elec-trical Engineering (IJEE). He is a member of Phi-Tau-Phi honorary scholar so-ciety, and also served as technical program committee member of IEEE Custom Integrated Circuits Conference (CICC), IEEE Asian Solid-State Circuit Confer-ence (A-SSCC), IEEE RFIT, and IEEE ASICON.

Chung-Yu Wu (S’76–M’76–SM’96–F’98) was

born in 1950. He received the M.S. and Ph.D. degrees from the Department of Electronics Engi-neering, National Chiao Tung University, Hsinchu, Taiwan, in 1976 and 1980, respectively. In addition, he conducted visiting research at UC Berkeley in Summer 2002.

Since 1980, he has served as a consultant to high-tech industry and research organizations and has built up strong research collaborations with high-tech in-dustries. From 1980 to 1983, he was an Associate Professor at National Chiao Tung University. During 1984 to 1986, he was a Visiting Associate Professor in the Department of Electrical Engineering, Port-land State University, PortPort-land, OR. Since 1987, he has been a Professor at Na-tional Chiao Tung University. From 1991 to 1995, he was rotated to serve as the Director of the Division of Engineering and Applied Science on the National Science Council, Taiwan. From 1996 to 1998, he was honored as the Centen-nial Honorary Chair Professor at National Chiao Tung University. Currently, he is the Chair Professor at National Chiao Tung University. He has published more than 300 technical papers in international transactions/journals and con-ferences. He also has 38 patents including 19 U.S. patents. His research inter-ests are biomedical electronics, nanoelectronics and VLSI including circuits and systems in low-power/low-voltage mixed-signal design, neural vision sensors, neuromorphic network, and RF circuits.

Dr. Wu is a member of Eta Kappa Nu and Phi Tau Phi Honorary Scholastic Societies. He was a recipient of IEEE Fellow Award in 1998 and Third Millen-nium Medal in 2000. In Taiwan, he received numerous research awards from Ministry of Education, National Science Council, and professional foundations.