A Balanced Scheduling Algorithm for High-speed ATM Switch

全文

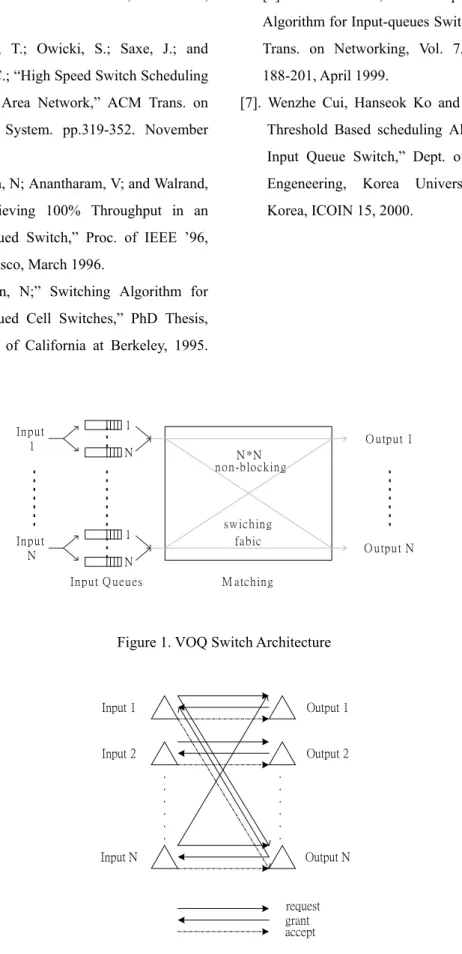

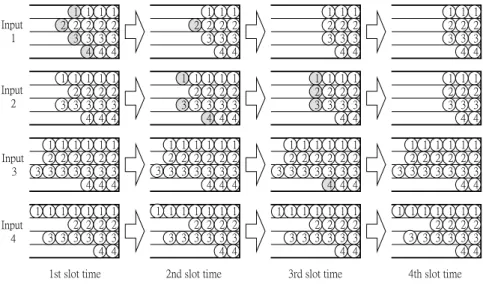

(2) 最 後 一 種 方 法 是 VOQ, 在 一 個 N*N. accept. 在 PIM 排序演算法中, grant 和. switch VOQ 中, 每個獨立的 output 都有其相. accept 的挑選都是決定於亂數產生的機率.. 對的 input 並維持一個分割為 N 個 FIFO 的. 而 RRM 和 iSlip 的演算法中, grant 和 accept. queues 作為緩衝器, 如 Figure 1. 利用此方. 的選取是藉由輪循式 (round-robin) 的選擇. 法不僅解決了 HOL blocking 的問題, 而且. 順 序 . 在 RRM, 每 一 個 output 根 據 固 定. switch 不需額外的提升速度亦可達到最高的. round-robin 的 順 序 通 知 下 一 個 出 現 的. 效能. 現在 VOQ 已被證明出可增加 input. request, 然後移動 round-robin 的指標到另. queuing switch 的效能達 100%.. 一個被通知的 request, 同理, 每個 input 亦 是採用同樣的方式來接受 grant. 然而, 在. 許多藉由或應用 VOQ 的 switch 的排序演 算法已被提出 [2],[4],[5]. 這些演算法提 供了不同的實用功能, 其中以分散式排序法 (distributed scheduling algorithm)最為重 要. 在這個方法中, N*N switch 被模擬為 N 個 inputs 和 outputs, 每個部分包含 N 個節 點 (node). 利用上述的模型, 我們希望算出 一個最好配對 (matching) 細胞的方法, 以便. iSlip, 對每一個 output 而言, round-robin 的指標並不會改變, 除非該相關的 grant 已被 接受, 才會循環到下一個. 簡而言之, 在 RRM, output 不等 input 傳來的 accept 訊號即 round-robin 移動到下一個位置. 相反的, 在 iSlip, output 會一直等到 input 回覆 accept 才 round-robin 到下一個點. 在上述的演算法 中, 只有 iSlip 可達到 100%的 throughput.. 滿足 (1)資料被傳送時能夠達到機率較小的 碰撞 (2)資料可以同時被服務. 在過去的文 獻中有四個主要的演算法已被提出, 分別是 PIM[3], RRM[5], iSlip[6], T-RRM[7]. 這些 演算法得服務方式都是由三種階段 (phase) 的順序來完成, 分別是 : 要求(request), 允 許(grant), 接受(accept), 如 Figure 2 所. 由 於 PIM, RRM, iSlip 都 沒 有 考 慮 到 queue 本身的狀態. 例如 : 可能某一 port 內 queue 的長度很長 (即想傳送到該目的地的 cells 很多), 但因為 round-robin 的指標需 要繞一圈才能再度到同一位置且一單位時間 內只能傳送一個 cell (即一次服務一個人),. 示.. 這樣會導致延遲 (delay) 過長. 因此 T-RRM 1. Request phase : 每一個 input 廣播它們 要求傳送的資料到 output.. 被提出於在 VOQ 排序 cells 的長度. 在 T-RRM 演算法中, 依舊使用 round-robin 來決定. 2. Grant phase : 每一個 output 從上述接. cell 交 換 的 順 序 , 也 同 樣 利 用 request,. 收到的 requests 中, 獨立的挑選一個要. grant, accept 三種 phases 作為傳輸, 且與. 求, 然後傳送 grant 回該 input.. iSlip 相 同 , 都 可 達 到 100% throughput.. 3. Accept phase : 而後, 每一個 input 挑. T-RRM 主要的想法是 : 如果一個 queue 有過. 選一個 grant 作為接受. 當一個 input. 多的 cells 以致於超過門檻 (threshold) 限. 接受一個由 output 傳來 grant, 該 input. 制時, 這時在該 VOQ 大於 threshold port 中. 必須傳送一個 cell 至 output.. 的 cell 會先被傳送到目的地. 而我們所提出 的 B-VOQ 在 traffic load 變大之時, 可能所. 在眾多的演算法中, 通常只有不同於如 何在 output 中從眾多的 request 挑選一個作 為 grant 和如何在 input 中選擇 grant 當作. 有 VOQ 中的 cell 長度皆以超過 threshold, 除 了考量是否大於 threshold 外, 在其中選擇長 度最長的先服務, 以達到每個 VOQ 長度的平.

(3) cell 數目過多, 使得某些超過 queue 容量的. 衡.. cell 被拋棄(drop), 欲傳送的資料因而遺失. 本篇論文的組成架構如下, 在第二章節 我們將會介紹 B-VOQ 演算法並且假設了一個. 關於 B-VOQ 的 pseudo-code 描述如下:. 簡單的例子來描述 T-RRM 是如何運作. 在第. /* i : number of input ports; j : number of output ports; cell_num : the number of cell in VOQ ; TMport : how many ports own the same cell numbers which is the greatest one */. 三章節我們將模擬結果分析來比較文獻中所 提的演算法與 B-VOQ 演算法的效能差異. 第四 章是我們的結論.. 2. B-VOQ Algorithm 就像 RRM, iSlip, T-RRM, B-VOQ 也使用 round-robin 來決定 cell 的排序, 且同樣基 於三個 phase 作為傳遞方式. 在描述 B-VOQ 之前, 我們先對 marked port 下定義. 如果有 一個 input 被挑選為藉由 crossbar switch 傳送 cell 到某一 output, 且該相關 VOQ 長度 大於 threshold, 我們把該 input 和 output 標示起來稱為 marked port. 當 marked port 內 的 cells 數 目 被 服 務 為 小 於 或 等 於 threshold 時, 我們再把該 input 和 output 取消標示,使其變為 unmarked port. B-VOQ 的主要構想是 : 如果 cell 量來的 很多時, 相對的導致許多 VOQ 超過 threshold, 我們把這些相關的 input 和 output 標示為 marked port, 且將該 VOQ 收集起來, 並計算 這些 VOQ 內的 cells 數量. 擁有長度最長的 VOQ 會在該 slot time 先被傳送. 待下一 slot time, 再重新判斷每一 VOQ 內的 queue 長度是 否超過 threshold, 選擇超過 threshold 且在 VOQ 中長度最長的先處理. 如果此時產生擁有 相同 cell 個數且都超過 threshold 的 VOQ, 這 時即採取 round-robin 的方式作為傳遞 cell 的優先順序. 假設 cell 數較少, 以致於此時 並無大於 threshold 的 VOQ, 則利用一般 round-robin 的方式對 cell 做遞減. 該方法 最大的優點在於可以平衡 VOQ 內 cell 的長度. 當 traffic load 很大時, 採用 T-RRM 演算法 會產生 queue 的不平衡, 導致有些 VOQ 內的. for(all i) request(i ){ /* Request phase */ if(marked_input[i]= = Yes){ /* is it a marked input ? */ sort;/* calculate the cell numbers of marked input*/ find max cell number; /* find max cell number in VOQ*/ if(TMport>=2) { Torr_priority[j]=(i+1); /* select a request over threshold based on the round-robin of output j */ } accept(i,j);/* use the same matching in this time slot */ if(cell_num[i,j]<=threshold) marked_input[i] =No;/* unmark the input */ } else for(all j){ if(cell_num[i,j]>0){ /*queued cells for output j ?*/ request(i,j);/* request to output j */ } for(all j) grant(j){ /* Grant phase */ if(num_request[j]>0){ /*received any request ?*/ i=orr_select(j); /* select a request based on the round-robin of output j */ grant_request(i,j); /*grant request j back to input i */ } } for(all i) accept(i){ /* accept phase */ if(num_grant[i] >0){ /* received any request? */ j=irr_select(i); /*select a request based on round-robin of input i? */ accept_grant(i,j); /* accept the grant j */ irr_priority[i]=(j+1); /* set the highest priority of round-robin of input i higher than granted output */ orr_priority[j]=(i+1); /* set the highest priority of round-robin of output j higher than granted input */ if(cell_num[i,j]>threshold){ /* queued cells more than threshold ? */ marked_input[i]I=Yes; /* mark input I as marked input */ }.

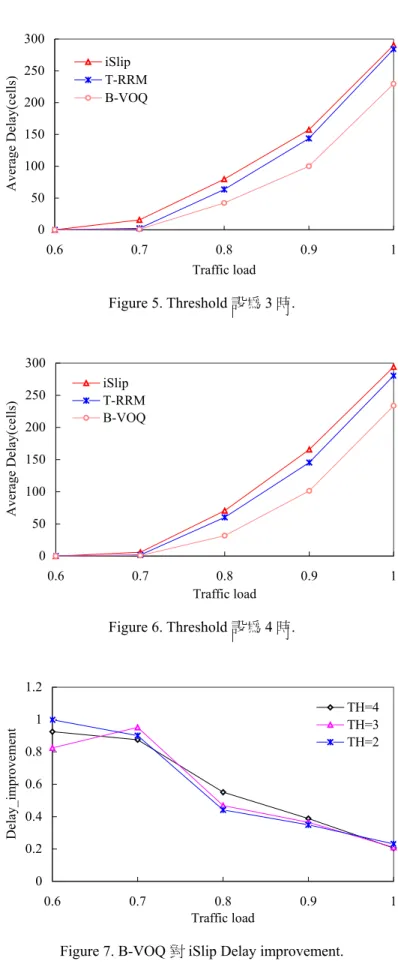

(4) }. 的 input 3 先服務, 最後 output 4 經過判斷. }. 都沒有超過 threshold 故以 round-robin 的方. 三種 phase 傳遞方式敘述如下 :. 式處理, 所以先選 input 1. 由上述, 得知. 1. Request : unmarked input 傳送 request. (1,4), (3,2), (3,3), (4,1) 內的 cell 數在 第一個 slot time 會分別減 1. 在第二個. 到 output. 2. Grant : 當一 unmarked output 收到任何. slot time 時, L = {{4, 5, 4, 2}{5, 4, 5,. request, 它會根據 round-robin 的方式. 3},{6, 5, 6, 3},{6, 4, 6, 2}}, 這時再經. 來傳送通知訊號.. 計算後 input 1, input 2, input 3, input 4. 3. Accept : 如果一個 input 接收到 grant,. 傳送到 output 1 的 cell 個數分別為 4, 5, 6,. 該 input 會傳送 cell 到 output. 更進一. 6 (個), 由於 cell 個數皆超過 threshold, 且. 步 的 說 , 如 果 input queue 有 超 過. input 3 和 input 4 的 cell 個數皆為 6, 所以. threshold 的 cells 在排隊等待傳送時,. 使用 round-robin 的方式選擇 input 3 來服務.. 該 input queue 和 output queue 將會被. 在第二個 slot time, (1,2), (2,4), (3,1),. 標示成為 marked port, 直到 VOQ 內的. (3,3) 內的 cell 數會分別減 1. 此後在每個. cell 數小於或等於 threshold 才恢復成. slot time, cell 的遞減方式皆以此類推. 由. 為 unmarked port.. Figure 3a 使用 T-RRM 和 Figure 3b 使用 B-VOQ 的方式比較後發現 Figure 3b 在 VOQ 的 cell. Figure 3b 呈現 B-VOQ 如何運作在一個 threshold 設為 3 的 4*4switch 的範例.我們. 個數會比 Figure 3a 的平衡.故可了解我們所 提的方法有較好的效能.. 利用一個二維陣列 L 來表示 input 內 VOQ 的 cell 個數. 坐標 (x, y) 分別表示 input 和 output.. 在 第 一 個. slot. time,. L. 3. Simulation result. =. {{4,5,4,3},{5,4,5,3},{6,6,7,3},{7,4,6,2. 為了證明 B-VOQ 演算法和其他演算法相. }},即 input 1, input 2, input 3, input 4. 比較有明顯改善的 average delay, 我們將. 傳送到 output 1 的 cell 個數分別為 4, 5, 6,. B-VOQ 模擬在一個 16*16 switch. 由於 PIM 和. 7 (個); 傳送到 output2 的 cell 個數分別為. RRM 在 先 前 的 文 獻 已 經 被 證 明 出 無 法 達 到. 5, 4, 6, 4 (個), output 3, output 4 的 cell. 100%的 throughput, 所以在 simulation 中,. 個數如上所述. 經過 cell 個數的計算後, 在. 我 們 將 只 比 較 iSlip, T-RRM 與 B-VOQ 的. output 1 得到 cell 個數大於 threshold 有. delay. 在所有的模擬中, 我們假設 input 和. input 1, input 2, input 3, input 4 分別. output 的 連 結 速 度 都 是 一 樣 的 , 且 根 據. 為 4, 5, 6, 7 (個), 根據擁有最多 cell 個. Bermoulli traffic, input 流 量 對 每 一 個. 數的 port 會先被服務, 所以先挑選 input 4.. input port 接收以及傳送到 output 的 cell. 接 下 來 output 2 一 樣 去 判 斷 是 否 超 過. 是均勻分布的. 根據這個典型的網路交通流. threshold, 會得到 input 1, input 2, input. 量模擬, 我們將執行 50000 個 time slots 來. 3, input 4 皆超過 threshold, 經過計算後,. 比較在不同 traffic load 的 delay 與各個演. 選擇其中 cell 個數最多的 input 3 作為服務. 算法的關係.. 對象. 同樣的對 output 3 而言 input 1, input. 經過證明, 己得知只有 iSlip 和 T-RRM. 2, input 3, input 4VOQ 中的 cell 個數亦超. 可達到 100%throughput, 且根據文獻[7],且. 過 threshold, 所以一樣選擇 cell 個數最多. 在 iSlip 與 T-RRM 相較下, T-RRM 會獲得較低.

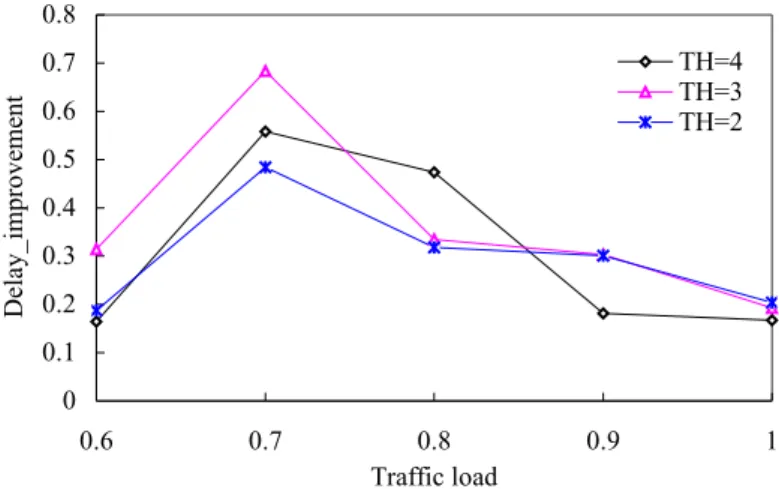

(5) 的 average delay, 因此, 我們將比較 B-VOQ. 加時 B-VOQ 和上述兩者相比較皆會有較佳的. 分 別 對. average delay.. iSlip. 與. T-RRM. 的. delay_. improvement. 由 Figure 7 說明 B-VOQ 對 iSlip 的. delay_improvement (iSlip vs B-VOQ) = (delayiSlip – delay. B-VOQ. )/delayiSlip.. delay_improvement, 我們發現 threshold 設. delay_improvement (T-RRM vs B-VOQ) =. 為 2, 3, 4, 且 traffic load 分別為 0.6, 0.7,. (delayT-RRM – delay. 0.8 時, 在 delay_improvement 將產生 99.89%,. B-VOQ. )/delayT-RRM.. 我們先模擬 iSlip, T-RRM, B-VOQ 在不. 95.21%, 55.05% 的最佳改善率.. 同的 traffic load 及 threshold 下的 average Figure 8 顯 示 B-VOQ 對 T-RRM 的. delay. 結果如 Figure 4-6 所示.. delay_improvement, 我們亦可發現 traffic Figure 4 顯示出 threshold 設為 2 時, 當. load. 為. 0.7. 時 將 擁 有 最 好 的. traffic load 小 於 0.5, iSlip 與 T-RRM,. delay_improvement, 此外, 在 traffic load. B-VOQ 的 delay 沒有顯著的差異. 當 traffic. 為 0.8 且 threshold 設在 4 時, 亦有較佳的改. load 越來越大時 iSlip 與 T-RRM 的差距會在. 善率.. 0.6 慢慢分開,在 0.7 時最為明顯, 但這二個 方法與 B-VOQ 的 delay 差距將會隋著 traffic. 4. Conclusion. load 變大而越來越明顯. 當 traffic load 為 1.0 時, 該現象最為明顯.. 在這篇論文中, 我們提出一種簡單的方 法 B-VOQ 用來減少 cell 在 input queue 中所. 由 Figure 5 顯示出 threshold 設為 3 時, 當 traffic load 小於 0.5, iSlip 與 T-RRM, B-VOQ 的 average delay 幾乎沒有差異. 同樣 地, 當 traffic load 越來越大時 iSlip 與 T-RRM 的差距會在 0.7 慢慢分開, 而在 0.9 時 又漸漸不明顯. 但這二個方法與 B-VOQ 的 delay 差距將會隋著 traffic load 變大而越 來越明顯. 當 traffic load 為 1.0 時, 該差 距最大. 因此, 我們的演算法與先前文獻中所. 需的延遲時間, 在 B-VOQ 中, 每一組搭配好的 input 和 output 每經過一個 slot time 便 會重新計算每一 VOQ 的 cell 的個數, 如果 cell 個數大於 threshold, 則該 input 和 output 將會被標示, 且這些 VOQ 內擁有最多 的 cell 個 數 將 會 先 被 服 務 , 否 則 即 用 round-robin 的傳輸方式. B-VOQ 的模擬結果 顯示出當 traffic load 大於 0.6 時, 相較於 T-RRM, 它可以減少 16-68%的 average delay.. 提的方法相比較下, 在 average delay 上會有 較好的表現.. REFERENCES 在 Figure 6 顯示出當 threshold 設為 4 時, 依舊可以發現 B-VOQ 有較好的 average delay. 因此, 由 Figures 4-6 中可發現不管 T-RRM 的 threshold 設為多少,所不同的只在 於和 iSlip 的 average delay 在多少 traffic load 時會有明顯的分別.當 traffic load 增. [1]. Karol, M.; Hluchyj, M.; and Morgan, S.; “Input output queuing on a space division switch,” IEEE Trans. Communications, vol.35, no.12,pp.1347-1356, 1988. [2]. Ajmone Marsan, M.G.; Bianco, A.; and Leonardi E.;” RPA: A Simple, Efficient, and Flexible Policy for Input buffered switch,”.

(6) IEEE Communication Letters, l93-:83-86,. [6]. N. McKeown, “The iSlip Scheduling. May 1997.. Algorithm for Input-queues Switches,” IEEE. [3]. Andeson, T.; Owicki, S.; Saxe, J.; and Thacker, C.; “High Speed Switch Scheduling. Trans. on Networking, Vol. 7, No.2, pp. 188-201, April 1999.. for Local Area Network,” ACM Trans. on. [7]. Wenzhe Cui, Hanseok Ko and Sunshin,”A. Computer System. pp.319-352. November. Threshold Based scheduling Algorithm for. 1993.. Input Queue Switch,” Dept. of Electronic. [4]. McKeown, N; Anantharam, V; and Walrand, J; “ Achieving 100% Throughput in an. Engeneering,. Korea. Korea, ICOIN 15, 2000.. Input-Queued Switch,” Proc. of IEEE ’96, San Francisco, March 1996. [5]. McKeown, N;” Switching Algorithm for Input-Queued Cell Switches,” PhD Thesis, University of California at Berkeley, 1995.. Input 1. Input N. 1 O utput 1. N. N *N non-blocking. sw iching fabic. 1. O utput N. N Input Q ueues. M atching. Figure 1. VOQ Switch Architecture. Input 1. Output 1. Input 2. Output 2 . . . . . .. Input N. . . . . . .. Output N. request grant accept. Figure 2. Distributed Scheduling Algorithm. University,. Seoul,.

(7) Input 1. 1 1 1 1 2 2 2 2 2 3 3 3 3 4 4 4. 1 1 1 2 2 2 2 3 3 3 4 4. 1 1 1 2 2 2 3 3 3 4 4. 1 1 1 2 2 2 3 3 3 4 4. Input 2. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4 4. 1 1 1 1 2 2 2 2 3 3 3 3 4 4. 1 1 1 2 2 2 3 3 3 4 4. Input 3. 1 1 1 1 2 2 2 2 3 3 3 3 3 4. 1 2 3 4. 1 2 3 4. Input 4. 1 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4 1st slot time. 1 1 1 1 2 2 2 2 3 3 3 3 3 4. 1 2 3 4. 1 1 1 1 2 2 2 2 3 3 3 3 3 4. 1 2 3 4. 1 2 3 4. 1 2 3 4. 1 1 1 1 1 1 2 2 2 2 2 2 3 3 3 3 3 3 3 4 4. 1 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4. 1 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4. 1 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4. 2nd slot time. 3rd slot time. 4th slot time. Figure 3a. T-RRM for 4*4 Switch. Input 1. 1 1 1 1 2 2 2 2 2 3 3 3 3 4 4 4. 1 1 1 1 2 2 2 2 2 3 3 3 3 4 4. 1 1 1 1 2 2 2 2 3 3 3 3 4 4. 1 1 1 1 2 2 2 2 3 3 3 3 4 4. Input 2. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4. 1 1 1 1 2 2 2 2 3 3 3 3 4 4. 1 2 3 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4. 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4. 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4. 2nd slot time. 3rd slot time. Input 3. 1 1 1 1 2 2 2 2 3 3 3 3 3 4. 1 2 3 4. Input 4. 1 1 1 1 1 1 1 2 2 2 2 3 3 3 3 3 3 4 4 1st slot time. 1 2 3 4. 1 1 1 1 1 2 2 2 2 3 3 3 3 3 4 4. 1 2 3 4. 4th slot time. Figure 3b. B-VOQ for 4*4 Switch. Average delay(cells). 300 iSlip T-RRM B-VOQ. 250 200 150 100 50 0 0.6. 0.7. 0.8 Traffic load. Figure 4. Threshold 設為 2 時.. 0.9. 1.

(8) Average Delay(cells). 300 iSlip T-RRM B-VOQ. 250 200 150 100 50 0 0.6. 0.7. 0.8 Traffic load. 0.9. 1. 0.9. 1. Figure 5. Threshold 設為 3 時.. Average Delay(cells). 300 iSlip T-RRM B-VOQ. 250 200 150 100 50 0 0.6. 0.7. 0.8 Traffic load. Figure 6. Threshold 設為 4 時.. 1.2 TH=4 TH=3 TH=2. Delay_improvement. 1 0.8 0.6 0.4 0.2 0 0.6. 0.7. 0.8 Traffic load. 0.9. Figure 7. B-VOQ 對 iSlip Delay improvement.. 1.

(9) 0.8 TH=4 TH=3 TH=2. Delay_improvement. 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 0.6. 0.7. 0.8 Traffic load. 0.9. Figure 8. B-VOQ 對 T-RRM Delay improvement.. 1.

(10)

數據

相關文件

Ethernet Switch 每個 Port 必須 能模擬 CSMA/CD 的 Protocol. Ethernet Switch 需將廣播或群 播轉送至其他 Port 上(除了發送 的

• An algorithm is any well-defined computational procedure that takes some value, or set of values, as input and produces some value, or set of values, as output.. • An algorithm is

然後利用 parametric model 來 evaluate 任何的 input image 是否為人臉的 image。我們用 PCA 來做這件事情,我們可以想像所有的 image 都是 high dimensional vector,然後 PCA 會把它

➢The input code determines the generator output. ➢Understand the meaning of each dimension to control

• However, inv(A) may return a weird result even if A is ill-conditioned, indicates how much the output value of the function can change for a small change in the

Sequence-to-sequence learning: both input and output are both sequences with different lengths..

Input domain: word, word sequence, audio signal, click logs Output domain: single label, sequence tags, tree structure, probability

(b) Write a program (Turing machine, Lisp, C, or other programs) to simulate this expression, the input of the program is these six Boolean variables, the output of the program