Effect of annealing temperature on physical and electrical properties of Bi 3.25 La 0.75

Ti 3 O 12 thin films on Al 2 O 3 -buffered Si

Chia-Liang Sun, San-Yuan Chen, Shi-Bai Chen, and Albert Chin

Citation: Applied Physics Letters 80, 1984 (2002); doi: 10.1063/1.1459115 View online: http://dx.doi.org/10.1063/1.1459115

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/80/11?ver=pdfcov

Published by the AIP Publishing

Articles you may be interested in

( Na 0.5 Bi 0.5 ) 0.87 Pb 0.13 Ti O 3 thin films on different substrates for ferroelectric memory applications

Appl. Phys. Lett. 91, 192910 (2007); 10.1063/1.2811957

( Bi , La ) 4 Ti 3 O 12 (BLT) thin films grown from nanocrystalline perovskite nuclei for ferroelectric memory devices

Appl. Phys. Lett. 85, 4118 (2004); 10.1063/1.1812840

Investigation of hydrogen-induced degradation in Pb ( Zr x Ti 1x ) O 3 thin film capacitors for the application of memory devices

J. Appl. Phys. 92, 2724 (2002); 10.1063/1.1499976

Fatigue-free samarium-modified bismuth titanate ( Bi 4x Sm x Ti 3 O 12 ) film capacitors having large spontaneous polarizations

Appl. Phys. Lett. 79, 3137 (2001); 10.1063/1.1415353

Bi 3.25 La 0.75 Ti 3 O 12 thin films prepared on Si (100) by metalorganic decomposition method

Appl. Phys. Lett. 78, 1733 (2001); 10.1063/1.1355012

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 140.113.38.11 On: Thu, 01 May 2014 06:24:26

Effect of annealing temperature on physical and electrical properties

of Bi

3.25La

0.75Ti

3O

12thin films on Al

2O

3-buffered Si

Chia-Liang Sun and San-Yuan Chena)

Department of Materials Science and Engineering, National Chiao Tung University, 300 Hsinchu, Taiwan, Republic of China

Shi-Bai Chen and Albert Chin

Department of Electronics Engineering, National Chiao Tung University, 300 Hsinchu, Taiwan, Republic of China

共Received 10 October 2001; accepted for publication 11 January 2002兲

The effect of annealing temperature, especially at high temperatures, on the physical and electrical properties of Bi3.25La0.75Ti3O12共BLT兲 thin films on Al2O3 共10 nm兲/Si has been investigated. The

width of memory window in capacitance–voltage curves for BLT/Al2O3/Si capacitors annealed at

temperature range of 700 °C–950 °C increases with increasing annealing temperature. At the highest annealing temperature of 950 °C, a large ferroelectric memory window of 13 V is obtained under

⫾15 V sweep voltage, and this large ferroelectric memory window should be related to the reduced

leakage current. Owing to the excellent electrical properties, the high-temperature stable BLT/Al2O3/Si capacitor is compatible with current very large scale integrated technology process.

© 2002 American Institute of Physics. 关DOI: 10.1063/1.1459115兴

Ferroelectric random access memories have attracted much attention recently because of the lower writing voltage and faster switching speed than those of Flash memory.1– 4 To further improve the cell size and device performance, one transistor 共1T兲 ferroelectric metal–oxide–semiconductor

field-effect transistor 共FeMOSFET兲 type memory is

desirable.5– 8Unfortunately, the progress of 1T FeMOSFET memory is obstructed by the interface reaction between ferroelectric materials and Si that greatly degrades the device characteristics.8,9 Recently, we have developed 1T memory using Pb共Zr,Ti兲O3共PZT兲4and Al2O3共Refs. 10 and 11兲 stack

gate dielectrics on Si and good memory characteristics are obtained. However, high-temperature stable ferroelectric ma-terials on Si are still necessary for the process integration with current very large scale integrated共VLSI兲 technology.12 Since further ferroelectric performance improvement and VLSI process integration are required, bismuth layer-structured ferroelectric Bi4Ti3O12has been paid attention due

to its higher Curie temperature of 675 °C than that of SrBi2Ta2O9 共SBT兲.13 Recently, lanthanum-substituted

bis-muth titanate关Bi3.25La0.75Ti3O12共BLT兲兴 were widely studied

because of its enhanced nonfatigue behavior that is superior to PZT and comparable with SBT.14In this letter, our recent results will be reported on the effect of annealing tempera-ture on the physical properties of BLT thin films and the memory properties of BLT/Al2O3/Si capacitor. Our results

suggest that 1T BLT/Al2O3/Si FeMOS capacitor annealed at

high temperatures exhibits large memory window due to very low leakage current.

4 in. 共100兲 Si wafers with ⬃10 ⍀ cm resistivity were used in this study. For the FeMOS structure, a 10 nm thick Al2O3 gate dielectric was first formed on Si and the detailed

formation procedure was reported previously.10,11Then, BLT

films were deposited on Al2O3/Si by chemical solution

deposition using spin coating at 4000 rpm for 30 s.8An ex-cess of 10% Bi precursor was added to compensate for the Bi loss during annealing. After each coating, the deposited films were pyrolyzed for several minutes and the formed multilayer films were further annealed at the high tempera-tures of 700 °C, 850 °C, and 950 °C under an oxygen ambi-ent. Au and Al were used as upper electrode and bottom electrode and the capacitor area is 5⫻10⫺4 cm2. The phase

and microstructure of BLT were observed by x-ray diffrac-tion 共XRD兲 and scanning electron microscopy 共SEM兲. The elemental depth profiles were examined using secondary ion mass spectroscopy 共SIMS兲. The electrical properties were characterized by capacitance–voltage (C – V) and current density–voltage (J – V) measurements.

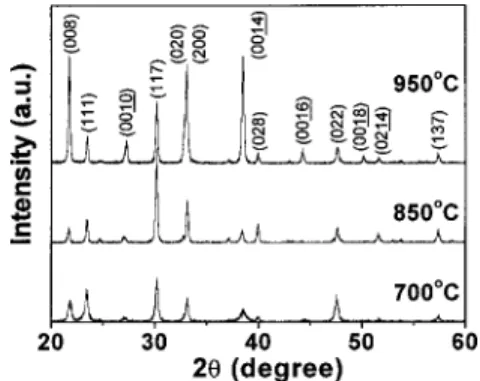

Figure 1 shows the XRD patterns of BLT films annealed at different temperatures. It was observed that all BLT films are polycrystalline and high quality ferroelectric BLT could be obtained at the annealing temperatures of 700 °C–950 °C. For the BLT films annealed at 700 °C, the XRD pattern is similar to that of Bi4Ti3O12powder and no preferred

orien-tation was identified. In the case of BLT films annealed at

a兲Electronic mail: sychen@cc.nctu.edu.tw FIG. 1. XRD patterns of BLT films annealed at 700 °C, 850 °C, and 950 °C.

APPLIED PHYSICS LETTERS VOLUME 80, NUMBER 11 18 MARCH 2002

1984

0003-6951/2002/80(11)/1984/3/$19.00 © 2002 American Institute of Physics

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 140.113.38.11 On: Thu, 01 May 2014 06:24:26

850 °C, the intensity of共117兲 main peak increases. However, as the BLT films were annealed at 950 °C, the 共008兲 peak becomes the strongest one, indicating that the preferred orientation15 is different from that of the 700 °C and 850 °C annealed samples.

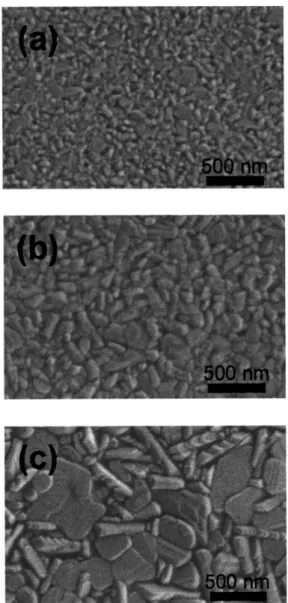

The surface morphology of BLT films annealed at 700 °C, 850 °C, and 950 °C was examined by SEM and is illustrated in Figs. 2共a兲, 2共b兲, and 2共c兲, respectively. The grain sizes of BLT films become larger as the annealing tem-perature increases. In addition to the rod-like grain shown in Figs. 2共a兲 and 2共b兲, the apparently large planar grains were observed for the BLT films annealed at 950 °C. The planar grains may correspond to the preferred orientation of XRD patterns shown in Fig. 1共c兲.

SIMS was used to investigate the elemental diffusion from BLT thin films through Al2O3 because Bi diffusion

could cause the degradation of device performance.16Figure 3 shows the SIMS profile of BLT/Al2O3/Si annealed at

950 °C and no significant Bi diffusion was observed. This result demonstrates that Al2O3 dielectric would be a suitable

material as the buffer layer between the BLT films and Si substrate in 1T FeMOS capacitor structure.

The C – V characteristics of BLT/Al2O3/Si capacitors

were measured at 1 MHz. Figure 4 shows the typical C – V curves and the memory windows of BLT/Al2O3/Si annealed

at 700 °C, 850 °C, and 950 °C. The well-behaved C – V curves without distortion were obtained and this could be associated with the little diffusion observed in SIMS profile. As shown in Fig. 4, the positive memory window value is related to a clockwise hysteresis loop attributed to the ferro-electric behavior,6,17 while the negative memory window value corresponds to the counter-clockwise hysteresis loop caused by the charge injection phenomenon. For the sample annealed at 700 °C, both ferroelectric and charge injection modes were observed. In sharp contrast, only ferroelectric mode was observed for the samples annealed at 850 °C and 950 °C and the memory window values become larger at higher write voltages up to⫾15 V. A large memory window of 13 V was obtained for the 950 °C-annealed samples. Ad-ditionally, a memory window of ⬃2 V could be obtained under ⫾5 V sweep voltage in both samples annealed at 850 °C and 950 °C and this suggests the possibility for low-voltage operation.

We have also investigated the current–voltage character-istics because the leakage current is one of the most impor-tant properties for memory capacitor. Figure 5 shows J – V curves of BLT/Al2O3/Si capacitors annealed at different

temperatures. The leakage current density of BLT/Al2O3/Si

annealed at 700 °C is 4.7⫻10⫺7 A/cm2at⫺100 kV/cm that is comparable to that of vanadium-doped Bi4Ti3O12共Ref. 18兲

but it increases rapidly at high voltages. On the other hand, for BLT/Al2O3/Si annealed at 850 °C and 950 °C, the

leak-age current reduces⬃3 orders of magnitude at ⫺100 kV/cm. The low leakage current is also smaller than our previous

FIG. 2. SEM images of BLT films annealed at共a兲 700 °C, 共b兲 850 °C, and

共c兲 950 °C.

FIG. 3. SIMS spectra of BLT/Al2O3/Si annealed at 950 °C.

FIG. 4. Memory windows of BLT/Al2O3/Si capacitors annealed at 700 °C, 850 °C, and 950 °C. The inserted C – V curves are the BLT/Al2O3/Si ca-pacitors annealed at 950 °C with program/erase voltages of⫾15 V.

1985

Appl. Phys. Lett., Vol. 80, No. 11, 18 March 2002 Sunet al.

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 140.113.38.11 On: Thu, 01 May 2014 06:24:26

data of PZT/Al2O3/Si FeMOS.5– 8In addition, no dielectric breakdown up to ⫺40 V also implies that the BLT films annealed at high temperatures have better dielectric integrity than that annealed at 700 °C. This smaller leakage current and larger breakdown voltage may be related to the micro-structure of BLT films shown in Figs. 2共b兲 and 2共c兲. The much reduced leakage current of BLT annealed at high tem-peratures is a strong advantage because this is directly cor-related with the applied switching energy and scaling trend in VLSI technology.

In conclusion, we have studied the annealing tempera-ture dependent characteristics of BLT/Al2O3/Si. At the

an-nealing temperature of 950 °C, the large memory window of 13 V is obtained under ⫾15 V sweep voltage. The leakage current density is also reduced by three orders of magnitude lower than that annealed at 700 °C. Although future work is underway to investigate the possible mechanism of the

en-hanced electrical properties, the high annealing temperature makes the stack gate BLT/Al2O3/Si process compatible with

current VLSI technology.

This work has been supported by the NSC88-2218-009-011 and NSC90-2215-E-009-061 of Taiwan.

1J. F. Scott and C. A. Paz De Araujo, Science 246, 1400共1989兲. 2

C. A. Paz De Araujo, J. D. Cuchiaro, L. D. McMillan, M. C. Scott, and J. F. Scott, Nature共London兲 374, 627 共1995兲.

3S. Y. Chen and V. C. Lee, J. Appl. Phys. 87, 8024共2000兲. 4S. Y. Chen and C. L. Sun, J. Appl. Phys. 90, 2970共2001兲.

5A. Chin, M. Y. Yang, S. B. Chen, C. L. Sun, and S. Y. Chen, Proceedings

of the 59th Device Research Conference 共DRC兲 共Notre Dame, Indiana,

2001兲, p. 18.

6M. Y. Yang, S. B. Chen, A. Chin, C. L. Sun, B. C. Lan, and S. Y. Chen,

Tech. Dig. - Int. Electron Devices Meet., 36-0.3.1共2001兲.

7

A. Chin, M. Y. Yang, C. L. Sun, and S. Y. Chen, IEEE Electron Device Lett. 22, 336共2001兲.

8C. L. Sun, S. Y. Chen, M. Y. Yang, and A. Chin, J. Electrochem. Soc. 148,

F203共2001兲.

9Y. Shichi, S. Tanimoto, T. Goto, K. Kuroiwa, and Y. Tarui, Jpn. J. Appl.

Phys., Part 1 33, 5172共1994兲.

10A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, Proceedings of the

Symposium on VLSI Technology, Kyoto, Japan, 1999, p. 133.

11A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, Proceedings

of the Symposium on VLSI Technology, Honolulu, HI, 2000, p. 16.

12

Y. Taur and T. H. Ning, Fundamental Modern VLSI Devices共Cambridge University Press, Cambridge, UK, 1998兲, p. 286.

13Y. Noguchi, M. Miyayama, and T. Kudo, Appl. Phys. Lett. 77, 3639

共2000兲.

14

B. H. Park, B. S. Kang, S. D. Du, T. W. Noh, J. Lee, and W. Jo, Nature

共London兲 401, 682 共1999兲.

15X. Du and I.-W. Chen, J. Am. Chem. Soc. 81, 3253共1998兲.

16S. T. Tay, X. H. Jiang, C. H. A. Huan, A. T. S. Wee, and R. Liu, J. Appl.

Phys. 88, 5928共2000兲.

17

Y. Fujisaki, T. Kijima, and H. Ishiwara, Appl. Phys. Lett. 78, 1285共2001兲.

18Y. Noguchi and M. Miyayama, Appl. Phys. Lett. 78, 1903共2001兲.

FIG. 5. J – V characteristics of BLT/Al2O3/Si capacitors annealed at 700 °C, 850 °C, and 950 °C.

1986 Appl. Phys. Lett., Vol. 80, No. 11, 18 March 2002 Sunet al.

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 140.113.38.11 On: Thu, 01 May 2014 06:24:26