亞 東 技 術 學 院 * 作者為亞東技術學院電子工程系助理教授。 ** 作者為亞東技術學院電子工程系學生。

Sub-1-V 低電壓帶隙參考電壓電路之實作

李民慶

*葉庭嘉

**嚴紹祖

**摘要

CMOS 帶隙參考電壓電路,擁有低功率、低溫 度係數與供應電壓獨立之特性,已成多數混合訊號 積體電路中提供參考偏壓電源之核心架構主流,為 更進一步提升整體效率;本文針對組成一改良型低 電壓帶隙參考電壓電路之架構單元:參考電壓源、 運算放大器、核心帶隙參考電壓電路及分壓回授電 路之設計加以分析討論,最後利用 TSMC 0.35μm 2P4M 製 程技 術 模 擬 , 設 計 完 成 一 晶 片 面 積 為 0.700

0.550mm2,功率消耗約 0.153mW,供應電 壓可從 1.9V 至 3.3V,溫度係數 16ppm/C,PSRR 為 63dB,輸出參考電壓可穩定在 0.6V 之低電壓帶 隙參考電壓電路。 關鍵詞:溫度係數、帶隙參考電壓電路、單增益頻 寬、PTAT 電壓。壹、 前言

在目前的電子產品中,不論是消耗性或是可攜 式電子產品,都朝向攜帶方便、短小輕薄應用功能 多元化的趨勢,其相對的製程也就需要越來越小, 但應用功能多元化所需外接電源與 IC 內部電路所 需外接之電壓不盡相同,故需要低電壓帶隙參考電 壓電路,以提供混合訊號積體電路各種不同參考偏 壓之功能。 通常傳統之 CMOS 帶隙參考電壓電路(BGVR) 係利用一 BJT 之基-射接面電壓V

BE(負溫度係數) 與兩 BJT 之基-射電壓差

V

BE(正溫度係數)產生 互補作用,進而產生具零溫度係數之參考電壓源, 近年來 CMOS BGVR 電路,因為消耗功率的降 低,整體效能之提昇,故低電壓帶隙參考電壓電 路,成為低功率參考電壓電路的主流,本文首先針 對組成一改良低電壓帶隙參考電壓電路架構之各 單元加以分析與設計。貳、 低電壓帶隙參考電壓電路

設計一參考電壓電路主要的目的是,使產生之 參考電壓與供應電壓源及環境溫度成獨立關係,如 圖 1 所示一傳統帶隙參考電壓電路,此帶隙參考電 壓利用兩 BJT 間之基-射電壓差

V

BE,其具正溫 度 係 數 生 成 PTAT(Proportional To Absolute Temperature)電壓,與 BJT(Q2)之基-射極V

BE,具 負溫度係數,兩者互相補償,以得到一穩定參考電 壓源Vbg。 VDD MP17 R1 R3 R2 Q2 Q1 Vbg C1I

IC2 圖 1 傳統帶隙參考電壓電路由圖 1 可推導Vbg電壓如下: 根據 KVL 定律得知

V

BE1

I

C2R

2

V

BE2 (2-1) 2 2 2 1V

I

R

V

V

BE

BE

BE

C

n R V I R I V n V T C C BE Tln ln 2 2 2 2 (2-2)n

V

R

R

V

V

R

R

I

V

bg C(

)

BE BE(

1

)

Tln

2 3 2 2 3 2 2

(2-3) 其中V

BE為一個負溫度係數以及V

T為一個正溫度 係數之參數,n 為兩 BJT 之寬長比倍率[8]。 本文主要是設計一個輸出電壓可穩定在 0.6V 且與環境、溫度和供應電源無關之低電壓帶隙參考 電 壓 電 路 (A Low Voltage Bandgap References Voltage Circuits) , 以 供 一 低 壓 降 穩 壓 器 (Low Dropout Regulator, LDO)使用。如圖 2 為一個改良 型的低電壓帶隙參考電壓電路,會選用此架構的原 因是,其功率消耗比傳統式參考電壓電路來的小, 且其參考電壓值可藉由電阻值而改變,如此可以改 善傳統帶隙參考電壓電路輸出電壓固定在 1.2 V, 而無法低於 1 V 的問題,此電路的正溫度係數 +0.087mV/˚K 和負溫度係數為-1.875mV/˚K,正、 負 TC 值取決於台積電(TSMC) 0.35μm 製程的參 數,如下列之推導,下(2-4)式為負溫度係數的表示 式: K mV K mV T q E V m V T VEB EB T g / 875 . 1 300 18 . 1 25 ) 5 . 1 4 ( 68 . 0 / ) 4 ( (2-4) 其中Eg eV eV J q C 19 19 10 602 . 1 , 10 6 . 1 1 , 18 . 1 正溫度係數的表示式如下列(2-5)式所示: K mV q K T VT / 087 . 0 10 602 . 1 10 38 . 1 19 23 (2-5) VDD M22 Vref M20 M21 R5 R6 R2 R1 R4 R3 Q1 Q2 OP 3 I A1 I 1 I I2 B1 I圖 2 低電壓帶隙參考電壓電路 上圖之改良型低電壓帶隙參考電壓電路,其中 上 面 三 顆 MOS 為 電 流 鏡 的 結 構 , 使 得 電 流 3 1 A1 2 B1 I =I +I =I +I ,產生 OPA 放大器的正負端輸入 電壓讓 OPA 動作,而調整電阻可以改變輸出電壓 值,輸出電壓為VREF=I R ,如下(2-7)式[3]。而3 3 6 1 ~ R R 電阻在設計時應要注意等比值設計,像是 1 R 跟R3、R2跟R4、R5跟R6這些等比值設計, 之後在佈局時才能有好的匹配,這也是設計電路時 要做的取捨,此電路的輸出電壓才能更穩定。以下 為低電壓帶隙參考電壓源的輸出電壓之推導: 1 2 1 1 3

I

I

AI

I

BI

1 1 1 2 1 1 1 2I

R

V

V

V

I

R

V

EB

EB

EB

EB

其中

V

EB

I

1R

1, 1 1 1 ln R n V R V I EB T E (2-6) 且R

2

R

5,R

4

R

6,可得到電流 1 4 2 2 1 6 5 2 3 ) ln( R n V R R V R V R R V I EB EB EB T 最後導得V

ref如下: 1 4 2 2 3 3 3 ) ln( R n V R R V R R I V EB T ref (2-7) 為提昇低電壓帶隙參考電壓電路之整體效 能,得到高準確之輸出參考電壓,減少製程變異對 其影響,運算放大器(OPA)之設計舉足輕重,故對 於 OPA 之各種特性參數需加以考量。參、 運算(誤差)放大器之設計

為使低電壓帶隙參考電壓電路具有高精確穩 定之輸出,本文使用具高增益、高輸入共模範圍之 PMOS 雙級式運算放大器(OPA)架構,如圖 3 所 示,第一級由擁有抗雜訊的能力之 MP4、MP5 和 MN1 、 MN2 電 流 鏡 負 載 組 成 差 動 對 輸 入 級 (Differential Pair),與第二級的 MP3、MN3 共源級 放大級提供高增益和高振幅,組成雙級式運算放大 器,另外在第一級輸出和第二級的迴授路徑之間, 加入一個 PMOS 米勒補償電容,作為頻率補償保 證運算放大器在不同負迴授量之下,電路均能穩定 操作[5]。Vin1- Vin2+ Vout

MP1 MP2 MP4 MP5 MN1 MN2 MP3 MN3 CL=0.5pF VDD Iref C c 圖 3 PMOS 雙級式運算放大器 針對 PMOS 雙級式 OPA 架構,歸納其中所需 要設計考量的參數如下: 1. 低頻增益 (DC Gain) 低頻增益是指整個運算放大器的放大倍率,一 般都以 dB 來表示[8],

First - Stage Gain:AV1gm,p4(ro,p5//ro,n2) (3-1) Second - Stage Gain:AV2gm,n3(ro,p3//ro,n3) (3-2) 2. 單增益頻寬 (Unit Gain Bandwidth)

即運算放大器能正常處理之訊號的頻帶寬度, 簡單說就是在此段頻率工作時訊號有放大的效果, 通常頻率響應中,運算放大器之極點或是零點對其 影響非常的重大。 C n m n ds p ds n ds p ds V V C g g g g g A A GB 3 , 3 , 3 , 2 , 5 , 2 1 ) )( ( ) ( (3-3)

3. 輸入共模範圍 (Input Common Mode Range) 若要讓 OPA 能當作放大器使用時,必須讓所 有 MOS 都維持在飽和區,當輸入範圍越小,可能 導致 OPA 的功能運作不正常,反之越大,更可確 保 OPA 的運作正常[8]。以下式(3-4)為輸入的最小 值,式(3-5)為輸入的最大值: 4 , 1 , 1 , min , 1 thn dsn tpp in

V

V

V

V

(3-4) 4 , 2 , max , 1 DD dsp sgn inV

V

V

V

(3-5) 由(3-4)式和(3-5)式可得輸入共模範圍: 4 , 2 , 4 , 1 , 1 ,n dsn tpp ICM DD sdp Sgn thV

V

V

V

V

V

V

(3-6) 4. 相位邊限 (Phase Margin) 相位邊限(PM)為當增益大小在 0 dB 時,相位 距離 180 度還有多少的角度,作為判斷系統是否穩 定的重要因素,測量相位邊限為極重要的設計考 量,OPA 之頻率響應最主要是由電路之整體增益 函數之極點(Pole)和零點(Zero)所影響導致的,當第 一個主極點(Dominant Pole)出現時會使低頻增益 衰減 20dB,而相位也會由 0 變為45,若第 2 個 Pole 出現的位置大於 10 倍頻時,相位會由90繼 續往下掉,使相位會成為 135 ,由圖 4 所示,若 持續往下掉至 180 後,使電路變為正回授,電路 將 震 盪 。 一 般 較 穩 定 的 放 大 器 設 計 範 圍 為 60 ~ 45 ,低於 45 度或高於 60 度時,則會影響 OPA 之 Settling Time。0 0 20 logA dB( ) 20 logAV t f 90o 180o 45o 135o 低頻增益 Phase Margin 2 p f fz 1 p f 圖 4 相位邊限示意圖

一般單級 OPA 放大器並不會震盪,但是它的 電壓增益並不高,所以加上第二級之共源級放大器 雖可提高電壓增益,但造成 PM 下降,可能導致運 算放大器震盪無法收斂,使得電路不穩定,故需在 第一級輸出與第二級輸出之間加上米勒電容作為 補償,將主極點往低頻移動,第一非主極點往高頻 移動,產生極點分離(Pole Splitting)的效果,以達 到補償的目的,如圖 5 所示。 F (HZ) Av(dB) 圖 5 補償後 Pole 的變化

肆、 參考電流源電路

電流參考電路定義為與供應電壓及環境溫度 成 獨 立 關 係 的 電 流 偏 壓 電 路 , 本 文 將 使 用 到 Low-Voltage Current Mirror 電路來實現參考電流源 電路。 如圖 6 所示其中 M1、M6、M7、M8、M9、 M14 為電路操作之適當偏壓。 M1 M2 M3 M4 M5 M11 M10 M13 M12 M14 M8 M7 M9 M6 M15 M16 M17 M18 VDD VDD VDD R B I A I 圖 6 參考電流源電路 另外因為電流鏡使得兩邊電流相等,假設 2 3 , 3( ) ) ( 2 1 t n GS ox n A V V L W C I (4-1) 2 2 , 2( ) ) ( 2 1 t n GS ox n B V V L W C I (4-2) B AI

I

,從克希荷夫電壓定律得知: B B n GS n GSV

I

R

V

, 2

, 3

(4-3) B B ox n A ox n B I R L W C I L W C I 3 2 ( ) 2 ) ( 2 (4-4) 2 2 3 2 3 1 ) ( ) ( ) ( 2 L W L W R L W C I B o x n B (4-5) 從上式(4-5)發現當R

B越大電流越小,反之電流則 越大。 1 ) ( ) ( ) ( 2 2 2 3 3 L W L W I L W C R B ox n B (4-6) 1 ) ( ) ( 2 2 3 3 L W L W R g B m (4-7) 由上式(4-8)發現 M3 之 gm 與供應電壓及環境 溫度成獨立關係,所以它能夠用來當作穩定的電流 源[8]。 一般來說偏壓電路在啟動時有可能讓所有電 晶體的電流都為零,導致整個電路無法動作,為了 防止這種情況不會發生,偏壓電路一般都會使用啟 動電路(Start up),以提供電路的工作點,跳開原 點,若整體電路正常動作時,啟動電路就會關閉, 圖 6 之 M15~M18 形成 Start Up 電路[9]。伍、 晶片佈局考量

在晶片佈局(Layout)考量上面,類比部分和數 位部份的畫法不盡相同,數位電路部份,以面積做為優先考量,故均以最小尺寸來做設計以及佈局, 且不需考慮到雜訊以及匹配的問題,其最大原因為 數位電路的 Noise Margin 約為一半的供應電壓 源,所以雜訊免疫能力很高,而元件之間的對稱問 題,也不用考慮,而類比電路中對於 OPA 的差動 對輸入元件通常是用 common centroid 的方式來達 成對稱的目的,並且當差動對的 MOS 同時遇到雜 訊的影響時,會讓雜訊變成共模訊號,此時的運算 放大器並不會放大共模訊號,並減少雜訊對 OPA 的影響,不僅僅是差動對的 MOS,只要是類比部 分的 MOS 都必須按照此模式來規劃,另外在佈局 好的 MOS 外圍加上一圈 guard ring,可大量減少外 部雜訊對類比部份電路之影響,以達到電路穩定的 效果。 從 0.35μm 製程參數裡面可以找到電阻的相關 參數,當然每個製程參數的數值不盡相同,所以當 設計者以及佈局者也必須了解到製程參數的影 響,通常在佈局電阻時,設 W=1,因此剩下調整 L 為多少由設計者自行決定,從中也發現到電阻值越 小,其串聯起來,產生的電阻值較趨近於原來的設 計值,雖然有這個好處,但是相對的面積也會增加 許多,因此須斟酌考量。此外也需要考慮到交叉對 稱性的問題,還有串聯顆數和各個電阻的間距都要 注意,因為在佈局電阻時,一樣會有雜訊的問題, 所以在電阻加上 RP Dummy 減少雜訊的干擾,另 外 Poly 所佔的面積很大,導致有寄生電阻的影響, 所以在佈局電阻時要特別注意不匹配造成電路的 影響[10]。 電源線在 VDD 與 GND 的連線路徑上,因為 連接路徑必須承受整體電路的電流,使得必須把連 線路徑加粗,以提升路徑上可承受電流的程度,避 免連線路徑因電流過大,燒斷連線,形成斷路。從 另一方面考量,因為加粗電源線,使得路徑上的寄 生電容變大,當電源線有雜訊時,可以透過此寄生 電容達到減少雜訊對於電路的影響。 在 OPA 的輸出端以及 R2 電阻這兩端點接上一 顆電容,加上電容的主要目的是抵抗供應電壓源的 雜訊,因為考量到當雜訊跑到供應電壓源裡面,會 造成 VDD 不穩定的因素[1]。 最後在供應電壓源 VDD 以及 GND 加上一顆 反耦合電容(交連電容),反耦合電容主要的目的是 因為供應電壓源 VDD 以及 GND 可能會有高頻率 的雜訊,為了不讓高頻的雜訊干擾內部電路,所以 接上反耦合電容讓高頻雜訊引導到 GND,不至於 影響到電路本身的操作,此外將佈局剩餘的面積放 上反耦合電容,一方面可以不讓雜訊進入電路裡, 另一方面還可以填補面積,一舉兩得。 VDD M22 Vref M20 M21 R5 R6 R2 R1 R4 R3 Q1(8)Q2 I I Vin1- Vin2+ MP1 MP2 MP4 MP5 MN1 MN2 MP3 MN3 M1 M2 M3 M4 M5 M11 M10 M13 M12 M14 M8 M7 M9 M6 M15 M16 M17 M18 R Ca M17 M18 Cc 圖 7 整體低電壓帶隙參考電壓電路 另圖中尚含有一 RC 低通濾波器,用此電路主 要是因為抵抗來自電源電壓或是電阻的熱雜訊,並 且加上一個啟動電路,當供應電源開啟時加入一個 驅動電路離開退化偏壓點之機制來解決[1]。 圖 8 為低電壓帶隙參考電壓電路之佈局圖。 Chip Size:0.700

0.550 2 mm Power Dissipation:0.153mW 圖 8 整體低電壓帶隙參考電壓電路之佈局圖陸、 實驗結果

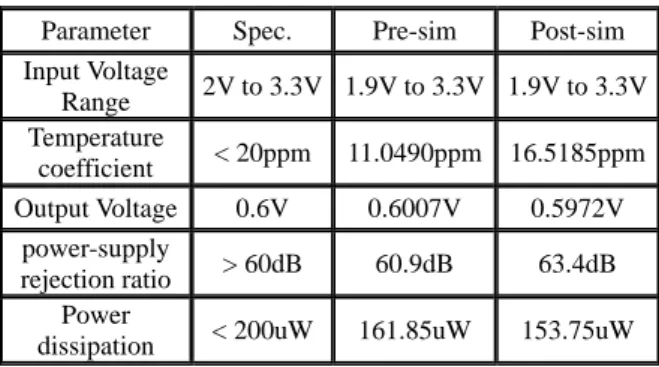

本文利用 TSMC 0.35 m CMOS 製程模擬分 析上節設計之 Sub-1-V 低電壓帶隙參考電壓電 路,針對五種 Coner 製程技術,經前模擬(Pre-sim) 與後模擬(Post-sim)之比較結果。 由圖 9 與 10 可知,整體電路溫度操作範圍從 C 40 到140C,此改良型低電壓帶隙參考電壓皆 可穩定在 0.6V,參考電壓之變化均小於 2mV 以 下,溫度係數均小於18ppm/C。 圖 9 Pre-sim 帶隙參考電壓對溫度變化 (VREF 0.6V,TT(11.04ppm)、FF(9.86ppm)、 FS(11.07ppm)、SF(11.46ppm)、SS(11.50ppm)) 圖 10 Post-sim 帶隙參考電壓對溫度變化 (VREF 0.6V,TT(16.51ppm)、FF(14.70ppm)、 FS(16.67ppm)、SF(14.64ppm)、SS(17.38ppm)) 五種 Coner 情況之供應電壓範圍: 由圖 11 與 12 可知,本文之改良型低電壓帶隙 參考電壓電路,分別在 Pre-sim 與 Post-sim,於不 同的五個 Coner 製程技術,輸入供應電壓之操作範 圍,可從 1.9V 至 3.3V,輸出參考電壓皆可穩定在 0.6V。 圖 11 輸入供應電壓範圍(Pre-sim) 圖 12 輸入供應電壓範圍(Post-sim) 電源拒斥比(PSRR): 接著測量此低電壓帶隙參考電壓電路對供應 電壓之電源雜訊免疫能力,若 PSRR 越高,則代表 抵抗電源雜訊的能力好,反之則代表越差。由圖 13 顯示,當供應電壓為 3.3V,且此電源電壓加入 頻率為 200KHz 之 AC 訊號,它的 PSRR 分別在 Pre-sim 為 63.4dB 與 Post-sim 為 60.9dB。 圖 13 低電壓帶隙參考電壓電路之 PSRR ( Post-sim:63.4dB、Pre-sim:60.9dB)柒、 結論

最後將本文所完成之 Sub-1-V 低電壓帶隙參 考電壓電路之預計規格與 Pre-sim、Post-sim 結果 及五種 Conner 之特性參數,分別整理在表 1 及表 2。 由表中可知本實作之 Sub-1-V 低電壓帶隙參 考電壓電路,在供應電壓由 1.9V 至 3.3V 之間,均 可穩定輸出參考電壓在 0.6V,功率消耗均小於 0.2mW,操作溫度從 oC 40 至 oC 140 ,得到之參考 電壓之變化均小於 2mV 以下,溫度係數均小於 18ppm/C。 表 1 預計規格與 Pre-sim, Post-sim 模擬結果比較 Parameter Spec. Pre-sim Post-sim Input Voltage Range 2V to 3.3V 1.9V to 3.3V 1.9V to 3.3V Temperature coefficient < 20ppm 11.0490ppm 16.5185ppm Output Voltage 0.6V 0.6007V 0.5972V power-supply rejection ratio > 60dB 60.9dB 63.4dB Powerdissipation < 200uW 161.85uW 153.75uW

表 2 CMOS 低電壓帶隙參考電壓電路特性參數

Spec FF TT FS SF SS

Input Voltage

Range 1.9 to3.3 1.9 to3.3 1.9 to3.3 1.9 to3.3 1.9 to3.3 temperature coefficient (ppm) 14.7018 16.5185 16.678 14.6416 17.3888 Output Voltage(V) 0.5970 0.5972 0.5971 0.5973 0.5974 Power dissipation (uW) at 166.553 153.755 152.305 155.383 144.226 PSRR (dB) 62.8 63.4 63.5 63.0 63.6 在本文之低電壓帶隙參考電壓電路中所有電 阻還尚可利用交換式電容來替代,但換此架構又有 可能會使晶片的面積變大或是消耗過多的功率,亦 或是要如何抵抗交換雜訊對低電壓參考電路的影 響,以及進一步減少不必要的電流消耗等,均是未 來值得深入探討的問題。

參考文獻

[1] Ka Nang Leung, and Philip K. T. Mok, “A Sub-1-V 15-ppm/ C CMOS Bandgap Voltage Reference Without Requiring Low Threshold Voltage Device,” IEEE, APRIL 2002 JOURNAL.

[2] Ka Nang Leung,Philip K. T. Mok, “Design Considerations of Recent Advanced Low-Voltage Low-Temperature-Coefficient CMOS Bandgap Voltage Reference,” IEEE , 2004 CONFERENCE.

[3] XU Meihua WU Jian , RAN Feng, LI Tiezhu, “Design of a Low Voltage Bandgap Reference Circuit for OLED-On-Silicon, ” IEEE ,2008 CONFERENCE.

[4] Donald A. Neamen, “Microelectronics:Circuit Analysis and Design, ” McGraw-Hill, 2007. [5] Adel S. Sedra & Kenneth C. Smith,

Microelectronic Circuits, 台北圖書有限公司, 2004.

[6] Allen Holberg, CMOS Analog Circuit Design, 台商圖書有限公司, 2004.

[7] Behzad Razavi, Design of Analog CMOS Integrated Circuits, International edition, McGraw-Hill, 2001.

[8] Hong-Yi Huang, Lab for Analog Integrated Circuits Design, 2003.

[9] Hong-Yi Huang, Analysis of Mixed-Signal IC Layout, 2006.

[10] 林正松, The Art Of Analog Layout, 矽拓科技 有限公司, 2002.

* Department of Electronic Engineering, Oriental Institute of Technology

Implementation of A Sub-1-V Low Voltage Bandgap Reference Circuits

Min-Chin Lee

*Ting-Chia Yeh

*Shao-Zu Yen

*Abstract

CMOS Bandgap Reference Circuit is main bias voltage source of mixed–mode Integrated Circuit system, due to its low power dissipation, low temperature coefficient and independent of supply voltage characteristics. In this paper, the main components within improved low voltage Bandgap reference circuits consist of the bias current source, OP Amp, the core cell of reference voltage circuit and divider feedback circuit are analyzed and discussed in detail. The sub-1-V low voltage Bandgap reference circuit has been fabricated with a standard TSMC 0.35μm 2P4M process. Experimental results show that the chip area is 0.700

0.550mm2, can operate with supply voltage from 1.9V to 3.3V,power dissipation about 0.153mW, and full range temperature stability from40Cto140Cwith temperature coefficient less 18ppm/C, PSRR is 63 dB, output voltage variation less 2mV, and output reference voltage stable at 0.6V.