國 立 交 通 大 學

電機與控制工程研究所

碩 士 論 文

使用有限區間二次倒回最佳化控制

之全橋式 D 類放大器

A Full-Bridge Class-D Amplifier Using

Finite Receding Horizon Quadratic Optimal Control

研 究 生: 林 岑 思

指導教授: 胡 竹 生 博士

使用線性區間二次倒回最佳化控制之全橋式 D 類放大器

A Full-Bridge Class-D Amplifier Using

Finite Receding Horizon Quadratic Optimal Control

研 究 生:林 岑 思

Student:Chen-Si, Lin

指導教授:胡 竹 生 博士 Advisor:Prof. Jwu-Sheng, Hu

國立交通大學

電機與控制工程學系

碩 士 論 文

A Thesis

Submitted to Institute of Electrical and Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical and Control Engineering

July 2005

Hsinchu, Taiwan, Republic of China

使用有限區間二次倒回最佳化控制

之全橋式 D 類放大器

研究生:林 岑 思

指導教授:胡 竹 生 博士

國立交通大學電機與控制工程研究所碩士班

摘 要

本論文以 Finite Receding Horizon Quadratic Optimal Control 為基礎設計 D 類音頻 放大器。D 類音頻放大器,相對於 A 類或 AB 類放大器,有效率高、功率級設計較易 的優勢。在數位訊號處理上有一個重要的量化誤差問題,所以在本論文中以量化誤差 為目標,訂定出其成本函數,然後使用有限區間二次倒回最佳化控制的方法去最小化 量化失真。以回授迴圈的方式實現一個 Multi-Step Optimal Converter,它以更一般的方 法來嵌入 Sigma-Delta Modulation 並且提供更好的效能。D 類放大器常以 Pulse-Width Modulator 產生切換式控制訊號,但產生的諧波問題較為嚴重。相對的,Multi-Step Optimal Converter 回授量化誤差,經過迴圈轉移函數,改變量化誤差能量分佈,得到 更高的訊號雜訊比。本論文將設計與實現穩定數位的 Multi-Step Optimal Converter、 USB 介面與切換式功率放大器,完成一全數位式音頻放大器。

A Full-Bridge Class-D Amplifier Using

Finite Receding Horizon Quadratic Optimal Control

Student: Chen-Si Lin Advisor: Prof. Jwu-Sheng Hu

Institute of Electrical and Control Engineering

National Chiao-Tung University

ABSTRACT

The objective of this thesis is to design a Class D audio amplifier based on Finite Receding Horizon Quadratic Optimal Control. Comparing to the traditional Class A or Class AB amplifiers, audio amplifiers based on Class D topology are more efficient in terms of energy conversion and have low cost. An important aspect of digital signal processing is the impact of quantization errors. In this thesis, we focus on the topic about quantization errors and define a cost function, which is utilized to minimize a measure of the quantization distortion by using finite receding horizon quadratic optimal control. We propose a Multi-Step Optimal Converter, which can be implemented as a feedback loop. It embeds Sigma-Delta Modulation in a more general setting and typically provides better performance. Class D amplifiers commonly rely on Pulse-Width Modulation to generate the output switching waveforms which gives rise to more serious problems in unwanted harmonics . On the other hand, using Multi-Step Optimal Converter, it is possible to design the loop filter so that the harmonic distortion is reduced. This thesis will analyze and implement a stable digital Multi-Step Optimal Converter, USB interfaces, and a switching power stage to complete a full digital audio amplifier.

誌 謝

漫長的學生生涯即將隨著本論文的完成,暫時的劃下句點,或許往後仍有機會再 度成為學生。回首過去,在一路上幫忙我的人實在是族繁不急備載,在此首先感謝在 我過去的十八年學生生活裡面,曾經幫助我以及輔助過我的人,當然還有感謝上天讓 我一路走來很平順,使我可以如願的取得碩士學位。 很榮幸地我可以成為胡竹生教授所領導的實驗室的一份子,感謝老師兩年多來的 指導與栽培,讓我不只學習到學術上的專業知識,也了解到做事該有的態度以及研究 生就是該對自己負責,在此致上最崇高的謝意與敬意。 在 x-lab 的日子裡,因為有眾多的學長姐、同學以及學弟妹的相輔相成,才能使 我順利的畢業,也因為有大家,讓我的研究生生活充滿歡笑與樂趣。感謝本論文的先 驅順智學長,感謝他在下班之餘還要被我打攪;感謝宗敏學長不只在我課業上的輔助, 偶而還要當我的心理顧問;感謝生活智慧王的 Angel,解決了我很多生活上的問題; 還有機器人魔人立偉學長、史上最強的博士价呈、常找我去健身房的劉大人、超像吸 毒犯的天才鳥哥、常請我吃東西的康康、常幫我們訂便當的億如、吃素卻可以長得很 高的俊德、愛打棒球的家瑋、愛學我說話的興哥、皮膚有變好趨勢的士奇、有老師架 式的群棋、硬體天王的晏榮以及愛運動又可以吃很少的鏗元,另外也感謝學弟妹們, 朱木、螞蟻、恆嘉、佩靜、鳥蕙、耀賢和詠融,謝謝你們的陪伴以及協助。 最後我要感謝我的家人,對於我一路上的支持與鼓勵。感謝我的父母在我求學的 過程,提供了我良好的學習環境,以及生活上的衣食無缺;當我在碩二下生病的那段 日子,感謝你們對我無微不至的照顧與呵護,使我可以迅速的恢復並且回到學校完成 我的學業。感謝我的兩位哥哥對於我這個問題妹妹的照顧,謝謝你們對我在學業上的 指導以及當我的精神指標。僅以本論文向家人獻上最誠摯的謝意。目 錄

摘 要...i ABSTRACT ...ii 誌 謝...iii 目 錄...iv 表 列...vi 圖 列...vii 第一章 序論 ... 1 1.1 簡介 ... 1 1.2 目標 ... 3 1.3 章節概要 ... 4 第二章 訊號調變 ... 5 2.1 Pulse-Width Modulator ... 5 2.2 Sigma-Delta Modulator ... 62.3 Receding Horizon Quadratic Control with Constraint ... 9

第三章 設計 MULTI-STEP OPTIMAL CONVERTER... 11

3.1 架構分析 ... 11

3.1.1 Define Quantizer ... 12

3.1.2 Finite Horizon Formulation ... 12

3.1.3 Solution and Implementation of the MSOC ... 14

3.2 Relationship to the Noise Shaping Quantizer ... 18

3.3 設計範例... 21

第四章 量化器的設計實例與分析... 29

4.1 Horizon One and 1.5-Bit ... 29

4.2 Horizon Two and One - Bit ... 30

4.3 Horizon Two and 1.5 - Bit... 32

第五章 實現 ... 34 5.1 USB 介面... 35 5.1.1 硬體介紹... 37 5.1.2 軟體介紹... 38 5.1.3 USB 實作... 40 5.2 FPGA ... 46

5.2.1 硬體介紹:Altera FLEX10K Emulation Board ... 47

5.2.2 軟體介紹:Quartus II ... 47

5.3 Power Stage ... 55

5.3.1 硬體介紹:Digital Amplifier Power Stage TAS5121... 55

5.3.2 Power Stage 實作... 56

5.4 實作結果 ... 58

第六章 結論 ... 65

6.1 研究成果... 65

表 列

表 3.3.1. 二階,N=1,1-BIT的 MSOC 輸出比較結果 ... 23

表 3.3.2. 二階,N=2,1-BIT的 MSOC 輸出比較結果 ... 25

表 5.1.1.USB 四種傳輸模式比較 ... 36

圖 列

圖 1.1 類比音響系統 ... 1

圖 1.2 D 類放大器 ... 2

圖 1.3 全數位化音頻擴大器 ... 3

圖 2.1 PULSE-WIDTH MODULATOR示意圖 ... 5

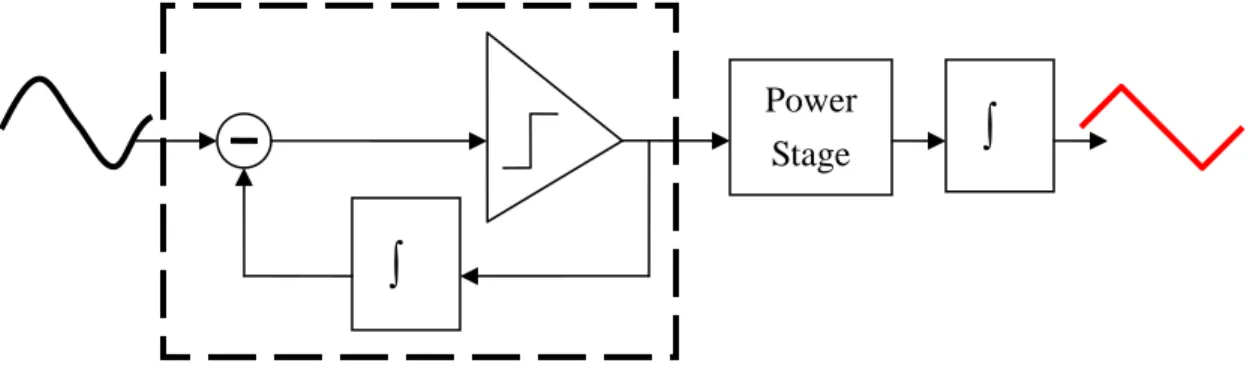

圖 2.2 DELTA MODULATOR與POWER STAGE架構圖... 6

圖 2.3 一階類比 SIGMA-DELTA MODULATOR... 7

圖 2.4 一階數位 SIGMA-DELTA MODULATOR... 7

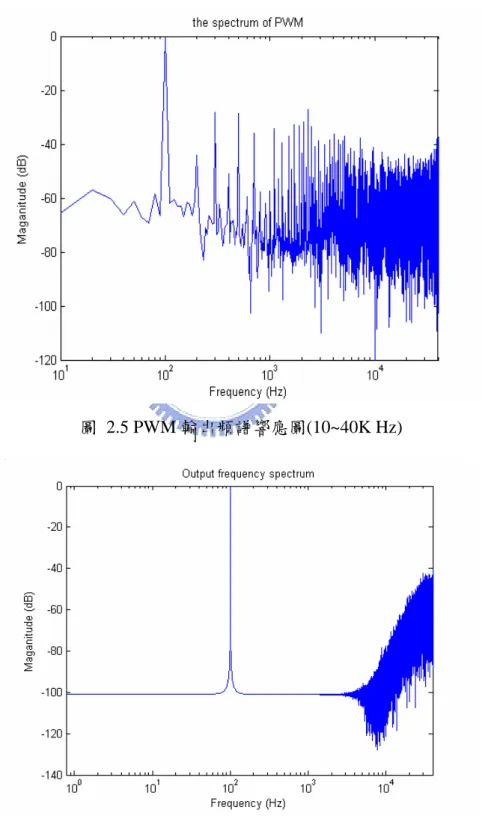

圖 2.5 PWM 輸出頻譜響應圖(0~40KHZ) ... 8

圖 2.6 SIGMA-DELTA MODULATION輸出頻譜響應圖(0~40KHZ) ... 8

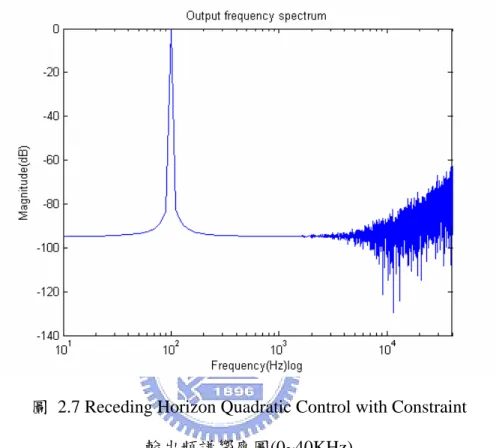

圖 2.7 RECEDING HORIZON QUDRATIC CONTROL WITH CONSTRAINT輸出頻譜響 應圖(0~40KHZ) ... 10

圖 3.1 GENERAL SINGLE-STAGE SIGMA-DELTA CONVERTER ... 11

圖 3.2 MOVING HORIZON PRINCIPLE,N=3... 17

圖 3.3 以回授的方式(FEEDBACK LOOP)實現 MSOC... 18

圖 3.4 NOISE SHAPING QUANTIZER... 18

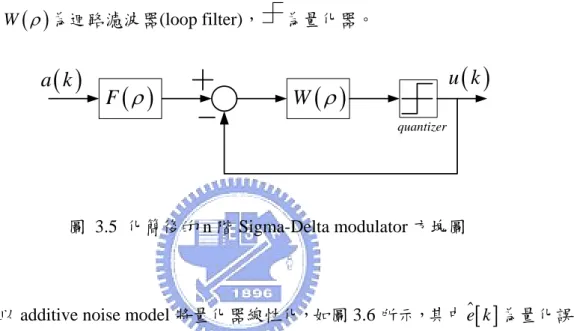

圖 3.5 化簡後的N階 SIGMA-DELTA MODULATOR方塊圖... 19

圖 3.6 以ADDITIVE NOISE MODEL線性化N階 SIGMA-DELTA MODULATOR... 19

圖 3.7 NOISE SHAPING QUANTIZER,REDRAWN... 20

圖 3.8 2-ORDER,N=1 的 MSOC 架構圖 ... 22 圖 3.9 輸入為 1KHZ的弦波訊號頻率響應圖... 23 圖 3.10 2-ORDER,N=2 的 MSOC 架構圖... 24 圖 3.11 輸入為 1KHZ的弦波訊號頻率響應圖 ... 25 圖 3.12 ERROR VARIANCE比較關係圖... 26 圖 3.12 SNR 比較關係圖 ... 27 圖 3.13 THD+N 比較關係圖 ... 27 圖 3.14 輸入不同振幅的訊號之 SNR 比較關係圖... 28 圖 3.15 輸入不同振幅的訊號之 THD+N 比較關係圖 ... 28 圖 4.1 一維量化器 ... 29 圖 4.2 一維量化器之架構圖 ... 29 圖 4.3 N=2 的 1-BIT量化器之區域分割... 31 圖 4.4 N=2 的 1-BIT量化器之架構圖... 31 圖 4.5 N=2 的 1.5-BIT量化器之區域分割... 33 圖 4.6 N=2 的 1.5-BIT量化器之架構圖... 33 圖 5.1 全數位化的音頻擴大器系統方塊圖 ... 34 圖 5.2 USB 基本架構 ... 35

圖 5.3 DMA-CYPRESS USBAN2131 控制單板... 37

圖 5.4 KEIL UVISION2 使用介面 ... 38

圖 5.5 EZ-USB 使用介面 ... 39

圖 5.6 USBAUDIO DESCRIPTOR架構圖... 41

圖 5.7 USB 單板以 USB AUDIO CLASS描述元裝置列舉 ... 42

圖 5.8 主程式流程圖 ... 43

圖 5.9 中斷服務程式流程圖 ... 44

圖 5.10 USB 傳送資料速度與 FPGA 消秏資料速度... 45

圖 5.11 FPGA 之基本架構圖... 46

圖 5.12 ALTERA FLEX10KEMULATION BOARD... 47

圖 5.13 QUARTUS II4.1 使用介面... 48

圖 5.14 FIFO 內部基本方塊圖 ... 49

圖 5.15 BUFFER方塊的I/O... 50

圖 5.16 空、滿的BUFFER方塊示意圖... 50

圖 5.17 二階、N=2 之 MSOC 實現方塊圖... 51

圖 5.18 1 CHANNEL MSOCI/O 的方塊圖 ... 52

圖 5.19 FPGA 實現 2 CHANNEL MSOC 之 VHDL 架構圖 ... 53

圖 5.20 QUARTUS II 之 COMPILER REPORT... 54

圖 5.21 TITAS5121 接腳圖... 56

圖 5.22 TAS5121 特性圖 ... 57

圖 5.23 2-ORDER,N=1,1.5-BIT的 MSOC 之 FPGA 的輸出訊號圖 ... 58

圖 5.24 2-ORDER,N=2,1-BIT的 MSOC 之 FPGA 的輸出訊號圖 ... 59

圖 5.25 2-ORDER,N=2,1.5-BIT的 MSOC 之 FPGA 的輸出訊號圖 ... 60

圖 5.26 SNR ... 61

圖 5.27 THD+N ... 63

圖 5.28 在 MODELSIM中BEHAVIOR的 ERROR VARIANCE比較關係圖... 64

第一章 序論

1.1 簡介

隨著科技日新月異,電子產品的迅速發展、資訊網路的發達,可攜式產品的重要性 越來越高,而可攜式產品越來越重視效率以及耗功的問題,D 類音訊放大器在可攜式產 品的應用上,例如手機、PDA 以及 mp3 上已經有取代 AB 類放大器的趨勢。 而目前的音響系統,大部分都是以數位儲存媒體作為音源(數位輸入),透過數位類 比轉換器(Digital to Analog Converter),將數位訊號轉換為類比訊號,將類比訊號輸入類 比功率放大器,驅動喇叭,此類比功率放大器,可分為 A 類、B 類或 AB 類。系統如 下圖 1.1 所示。 圖 1.1. 類比音響系統 D 類放大放器最早是由 Baxandall 在 1959 年所提出,利用 PWM 調變,將輸入訊號 調變為開關控制訊號,以控制切換式功率放大器的導通與關閉,達到訊號放大的目的 [1]。D 類放大器的效率一般可達 90%[2],而 A 類放大器因為有偏壓電流,使得的最大 效率只有 25%,而 AB 類放大器一般效率在 40~60%之間。因此在輸出相同的功率下, D 類放大器較節省能源,另外體積小以及效率高,並且還可大幅減少散熱片所佔面積甚 至取消散熱片。D 類放大器之所以效率高乃是因為在 H-Bridge 中,實際上的 MOSFET 在狀態 為’ON’時, 為極小,因此它上面幾乎沒有壓降;在狀態’OFF’時, 值很大, 因此幾乎沒有電流流過。所以從電源向負載提供了幾乎等量的功率,而相對的,AB 類 放大器僅有極小的功率被 MOSFET 消耗,效率則非常低。下圖為 D 類放大器的示意圖, 其中 MOSFET 以開關來表示。 DS(on) R RDS(on) Vcc DS(on) R DS(on) R DS(off) R DS(off) R LOAD R LOAD I LOAD I LOAD I 圖 1.2 D 類放大器 將音響放大器全數位化,不需要經過數位類比轉換器,減少數位類比轉換過程造成 的失真,將調變(Modulation)後的訊號送至 D 類放大器藉以提高功率,再驅動喇叭。而 因為 IC 製程的進步,元件的動態響應也越來越好,電晶體的切換速度越來越快,D 類 數位放大器(Class D Amplifier)的切換速度也能提升到 CD 取樣頻率,甚至 8 倍、64 倍 以上。因此要將音樂全數位化,硬體限制的問題,從不可能達成變成可能實現。下圖 1.3 為全數位化的音頻擴大器系統。

圖 1.3 全數位化音頻擴大器系統

1.2 目標

本論文提的全數位化音響放大器,以數位儲存媒體作為音源(數位輸入),將數位訊 號調變為 one-bit 或是 1.5-bit 的數位訊號,再將此數位訊號以全橋式 D 類數位功率放大 器(Full Bridge Class-D Amplifier)放大,驅動喇叭。

研究目標,設計實現一個全數位化的音響放大器,利用 pulse 訊號,驅動音箱,聽 到音樂。關鍵在設計一個能將 multi-bit 數位訊調變成為 one-bit 或是 1.5-bit 數位訊號的 調變器(modulator),這樣的 modulator,應用在音頻領域,目前主要有 PWM(Pulse Width Modulation)與 SDM(Sigma Delta Modulation)。本論文將討論另一種 Modulation,是利用 Finite Receding Horizon Quadratic Optimal Control 的方法來對資料作 Modulate,將之稱 為 Multi- Step Optimal Converter(MSOC),而事實上 SDM 是它的一種特例。

Sigma Delta Modulation 是廣為人知的架構,但是它的設計的瓶頸在高階時,如何 求得穩定且符合規格要求的係數,而設計這些係數往往不是很容易的,所以在此採用 Finite Receding Horizon Quadratic Optimal Control 的方法,它比較有彈性,可以根據不 同的要求而定義出想要的成本函數(Cost Function),進而去求得輸出,而在濾波器的設 計上,採用最簡單的積分器,使得係數都很簡單。本論文引用[3],設計穩定且符合需

求的 MSOC,實現全數位化的音響放大器。

1.3 章節概要

本論文的章節組織如下:

第二章將說明將 multi-bit 數位訊調變成為 1bit 數位訊號的 PWM、SDM 與 Receding Horizon Quadratic Control with Constraint 的調變原理、差別。第三章將分析 Multi-Step Optimal Converter 的系統,並說明它與雜訊整形量化器(Noise Shaping Quantizer)間的關 係,並提出幾個實驗範例。第四章為設計量化器(Quantizer)的實例說明。第五章說明如 何實現全數位化的音響系統。第六章心得總結以及對本系統的未來展望。

第二章 訊號調變

應用在音頻領域,將 multi-bit 數位訊號調變為 single bit 或是 1.5-bit 數位訊號的 Modulation,目前主要有 PWM 與 SDM 二種方法,以及本論文將使用的 Receding Horizon Quadratic Control with Constraint,以下分別介紹其調變原理與差異。

2.1 Pulse-Width Modulator

PWM 切換控制方塊如圖 2.1,其中三角波可以為正、上升、下降三角波等三種。 Vinput Vswitch Vt 圖 2.1 Pulse-Width Modulator 示意圖 切換開關的控制信號 Vswitch 是由輸入訊號(參考波)Vinput 與頻率為 f 的三角波(載s 波)Vt 比較而得,當輸入訊號 Vinput的電壓大於三角波 Vt 時,則輸出為高凖位,使開關 導通;反之則為低準位,使開關截止,而開關的切換頻率為 f 。固定切換頻率,調整s 脈波寬度,以改變輸出電壓的大小。PWM 輸出電壓的平均值之大小,正比於開關之導 通截止時間[4]。 數位 PWM 與類比 PWM 原理相同。輸入的數位訊號,在有限的取樣頻率下,依取 樣(Sampling)方法的不同,有 Uniform Sampling 與 Direct Interpolation Sampling 等型態。 Natural Sampling 是以無限高的取樣頻率作 Sampling,即為類比訊號。數位 PWM 的三角波的切換頻率為 f ,而為了達到 n-bit 的解析度(resolution),內部時脈必須為s 2n f 。s 假設今天輸入為取樣頻率 44.1KHz 的音樂訊號,而三角波作 32 倍的過度取樣,所以 44.1 32 s f = K× Hz ,若要達到 16-bit 的解析度,則內部所需時脈為 約等於 ,在實現上不僅是 timing constraint 無法達到,同時還會增加功率消耗的問題。 16 44.1K× ×32 2 92GHz

2.2 Sigma-Delta Modulator

切換式電源轉換器的損失包含有:導通損失、切換損失以及週邊控制電路之耗損。 近年來,先進國家對於電器產品之低功率損耗要求日益嚴格,還針對待機時之功率耗損 訂定標準規範。因此,許多降低切換頻率以及功率損耗的技術也就孕育而生。而無須濾 波器的 D 類放大器解決了這項問題,此放大器可以充分的利用揚聲器的自身電感及低 頻響應特性,無須在訊號調變送入 D 類放大器後再加濾波器,但是基於 PWM 的 D 類 放大器,因為它的總諧波失真(Total Harmonics Distortion)較高,所以只能提供有限的頻 寬,無法支援多音調振鈴及 MP3 播放。爲了解決此頻率響應的問題,採用 Sigma-Delta 的調變方法並且無需要濾波器的 D 類放大器因此產生,它不但可以提供較廣的頻寬同 時也可以降低切換頻率,甚至不需要後級的濾波器。Delta Modulator 最早由 Frank de Jager[5]於 1952 年提出的架構,應用在通訊領域。

Power

Stage

∫

∫

上圖 2.2 為 Delta Modulator 與 power stage 的架構圖。圖中的 為 one-bit 量化器, 產生 1 或是-1 的切換訊號,積分則為類似三角波,與輸入訊號比較。當輸入訊號大於 三角波,即誤差大於零,量化為高準位(1),積分後三角波增大;輸入訊號小於三角波, 即誤差小於零,量化為低準位(-1),積分後三角波變小。如此的切換動作,使得三角波 得以近似輸入訊號。將切換訊號透過 power stage 功率放大後,積分為近似輸入訊號的 三角波,輸出,達到放大的目的。

Sigma-Delta Modulation 架構由 Inose 於 1962 年提出[6],從 Delta Modulator 演變而 來,將 Delta Modulator 在 power stage 的類比積分器,換到 signal stage,成為一個 signal 積分器,使系統整體的轉移函數不變。下圖 2.3 可以看到一階類比的 Sigma-Delta Modulation,而數位的 Sigma-Delta Modulation 則是將積分器代換為數位累加器,如圖 2.4 為一階數位的 Sigma-Delta Modulation。 D/A

∫

r

Analog signaly

Digital signal 圖 2.3 一階類比 Sigma-Delta Modulatorr

y

Digital signal Digital signal 1 z− 圖 2.4 一階數位 Sigma-Delta Modulator數位 Sigma-Delta Modulation 通常可以依二個重要特徵–階數、取樣頻率,作為比 較、評估的基準。隨著超大型積體電路製程不斷的改良,電路的操作速度不斷的提昇且 供應電壓逐漸地下降,可將 Sigma-Delta Modulation 應用在較高頻寬的系統。

圖 2.5 PWM 輸出頻譜響應圖(10~40K Hz)

上圖 2.5 為 PWM 的輸出頻譜響應圖,其 switching frequency 為 44.1K*16Hz,解析 度為 3bit;圖 2.6 為四階、oversampling 為 16 倍的 Sigma-Delta modulation 的輸出頻譜 響應圖,比較此二圖可以明顯的發現,PWM 的 Harmonics 問題很嚴重,而 Sigma-Delta Modulation 則能將 noise 推到約 5KHz 以上的頻帶,因此在 5KHz 內的雜訊比 PWM 小 很多。

2.3 Receding Horizon Quadratic Control with Constraint

於 2002 年由 Daniel E. Quevedo 等人提出了一種從有限制條件的最佳化控制 (constrained optimal control)為觀點的方法[7],此方法可以依據不同的需求而訂定出個別 的 Cost Function,例如:切換次數、量化誤差、狀態的大小或是參考輸入等,所以它比 Sigma-Delta Modulation 的設計更具彈性。 首先考慮一個系統其輸入為u k

( )

,以及它的狀態向量為( )

n x k ∈ ,在此假設 n=1, 可得到下列的狀態方程式: x k(

+ =1)

Ax k( )

+Bu k( )

, u k( )

∈U (2-1) where is a set representing input constraints.U選擇 Finite Horizon Quadratic Cost Function 如下

( ) ( )

(

)

(

) (

)

{

( ) ( )

( ) ( )

}

N V x k ,u k =xT k+1 Px k+ +1 xT k Qx k +uT k Ru k (2-2) 其中Q≥0,P>0 and R>0 將(2-1)式帶入(2-2)式可得:( ) ( )

(

)

(

( )

)

( ) ( )

( ) (

N V x k ,u k =VN x k +uT k Wu k +2uT k Fx k)

(2-3) 其中 W =B QBT +R, F =B QAT , VN(

x k( )

)

為與u k( )

無關的項。 設( )

1/ 2( )

u k =W u k 代入(2-3)可化為( ) ( )

(

)

(

( )

)

( ) ( )

( )

1/ 2( )

N V x k ,u k =VN x k +uT k u k +2uT k W− Fx k (2-4) 將(2-4)對u k( )

微分,可求得最佳解:( )

(

)

1/ 2( )

u x k = −W− Fx k 再將此最佳解經過量化,即可得到開關的切換訊號,如下所示( )

(

)

1/ 2(

1/ 2( )

)

N U u∗ x k =W− q −W− Fx k (2-5)圖 2.7 Receding Horizon Quadratic Control with Constraint 輸出頻譜響應圖(0~40KHz)

上圖 2.7 為 Receding Horizon Quadratic Control with Constraint 輸出頻譜響應,與 PWM 比起來,它的 Nosie Shaping 效果較佳且 Harmonics 問題較小。此方法在高階的穩 定性上仍有待證明,因為此最佳化方法的回授為非線性,無法依據線性系統中的穩定性 原則來判定。

第三章 設計 Multi-Step Optimal Converter

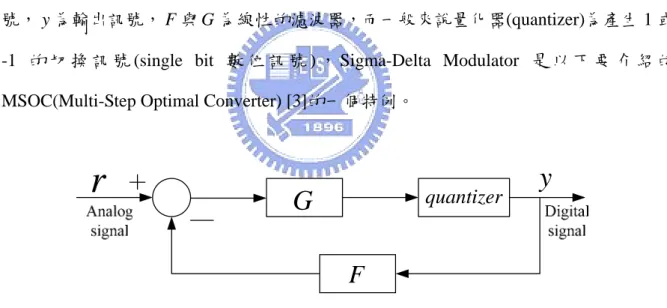

在數位的聲音處理上,面臨著一個重要的問題--量化誤差(quantization errors),將 multi-bit 數位訊號調變為 single bit 數位訊號的 modulation 時,難免會產生量化誤差,因 此經過量化後的資訊一定會有所損失,當訊號經由還原後會與原本的訊號有所差異,所 以一個好的轉換器(converter)是要使產生的訊號與原訊號最相似為原則,例如以均方誤 差(meansquare error)去量測時,當然對於處理聲音的轉換器來說,它的目標是要滿足人 類的聽覺。 Sigma-Delta Modulation 是一個廣為人知的轉換器,架構如圖 3.1 所示,r 為輸入訊 號, 為輸出訊號, 與G為線性的濾波器,而一般來說量化器(quantizer)為產生 1 或 -1 的 切 換 訊 號 (single bit 數 位 訊 號 ) , Sigma-Delta Modulator 是 以 下 要 介 紹 的 MSOC(Multi-Step Optimal Converter) [3]的一個特例。

y F

G

quantizer

y

r

F

圖 3.1 General single-stage Sigma-Delta Converter

3.1 架構分析

整體架構大致上可以分為量化器(quantizer)、Finite Horizon Formulation 以及 Solution and Closed Loop Implementation 來闡述。

3.1.1 Define Quantizer

首先,定義 Nearest Neighbor Vector Quantizer[8],如下:

Definition 1:給定一個可數的集合﹝不一定有限﹞,包函不相等的向量

{

1, 2,...}

,B

n

B= b b ⊂ the nearest neighbor quantizer is defined as a mapping which assigns to each vector

: nB

B

q →B

B

n

c∈ the closest element of B (as measured by the Euclidean norm), 換言之:qB

( )

c = ∈b B if and only if c satisfies :c b− ≤ −c bi , ∀ ∈bi B (3-1) 較詳細的 vector quantizers 還有其特性可以參考[9]。這個量化器(quantizer)可以用來解決 Audio quantization 的問題。考慮一個經過取樣的聲音訊號序列,

{

a k( )

}

,t∈ ,這個序 列的訊號必需被量化成{ }

u t( )

,t∈ ,其中u t( )

的每個值,被限制在一個有限的集合,{

1,..., nU}

U = s s 此序列的訊號將被量化為最接近集合U裡的元素,當時間t=k時。 u k( )

=qU(

a k( )

)

. (3-2)3.1.2 Finite Horizon Formulation

我們的目的在於最佳化失真誤差(distortion errors)到一個適當的值,所以使轉換誤 差(conversion errors)通過一個穩定的、因果的、線性的以及非時變的濾波器 ,此濾波 器可以透過下列式子來表示: H H( )ρ = +D C(ρI−A)−1B, (3-3) 1 , , , n n n n A∈ × B∈ × C∈ × D∈ v k( ) v k( 1) 其中 1 1 ×1, ,其中

{

v k( )}

是任意的序列。 此濾波器可以是典型的低通濾波器(low pass filter)並且使用過度取樣轉換(oversampled conversion),在聲音的應用上,選擇H為人耳的感知聲學模型( psycho-acoustic model )。設計一個理想的量化器(quantizer)使經過濾波器後的誤差(filtered error)最小化,可將此 概念經由下列式子表示之:

( ) ( )

(

)

( ) ( ) e t H ρ a t −u t 其中a t( )

為原輸入訊號,u t( )

為量化後的訊號,在此將e t( )

表示為狀態空間系統的輸 出,而此狀態空間系統的表示式如下所示:(

)

( )

(

( ) ( )

)

( )

( )

(

( ) ( )

)

1 , x t Ax t B a t u t e t Cx t D a t u t + = + − = + − (3-4) 其中{

C A B, ,}

與方程式(3-3)裡的相同,而 為濾波器的狀態, 為狀態的維度 (dimension),也就是濾波器 的階數(order)。 n x∈ n∈ H根據設計的目的,以二次成本函數(quadratic cost function)為設計準則,並在有限 的區間N內;在時間t=k時,將下列之二次成本函數最小化則可求得解:

( )

( )

( )

( )

1 2 , k N N t k V u k e t + − = =∑

(3-5) 其中 u k( )

=⎡⎣u k( ) (

u k+1)

u k(

+ −N 1)

⎤⎦ ∈T UN (3-6) N U 集合 N 且定義為: U ⊂ UN U× × 。3.1.3 Solution and Implementation of the MSOC

最佳化的控制問題在上一小節已經描述過了,將方程式(3-5)求其最小的值可以得其 解:( )

( )( )

( )

* arg min . N N u k U u k V u k ∈ = (3-7)其 中 是 非 凸 集 合 (non-convex set) , 所 以 此 問 題 是 一 個 非 凸 最 佳 化 (non-convex optimization)問題。 N U 定理一:假設UN =

{

v v1, 2,...,vr}

,其中 ,由方程式(3-7)、(3-3)、(3-5)以及(3-6) 可以得到最佳化序列 如下:( )

N U r= n( )

* u k *( )

1(

( )

( )

)

, N U u k =ψ−q ψa k + Γx k (3-8) 其中:( )

( )

(

)

(

)

1 1 1 1 1 0 0 1 1 , , 0 1 N 1 N a k C a k CA h a k a k N CA − h − h ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎢ + ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ =⎢ ⎥ Γ = Ψ = ⎢ ⎥ ⎢ ⎥ ⎢ + − ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ 1 , 1, 2, , 1. i i h =CA B− i= … N−非線性的 是Nearest Neighbor Vector Quantizer在3.1.1 Definition 1中描述過, 被 映射(mapping)到另一個集合上:

( )

N U q ⋅ UN{

1, 2,}

N N r U v v …v ⊂ (3-9) 其中:, N. i i i v = Ψv v ∈U 證明: 設 e k

( )

=⎣⎡e k( ) (

e k+1)

e(

k+ −N 1)

⎤⎦ T 將(3-4)式代入上述向量中可得( )

( )

( )

( )

e k = Ψa k − Ψu k + Γx k (3-5)式可以表示為( )

( )

( ) ( )

( )

( )

( )

(

)

(

( )

( )

( )

)

( ) ( )

(

)

( )

( )

( )

(

( )

( )

)

, 2 , (3-10) T N T T T T T N V u k e k e k a k u k x k a k u k x k V x k a k u k u k u k a k x k = = Ψ − Ψ + Γ Ψ − Ψ + Γ = + Ψ Ψ − Ψ Ψ + Γ 其中( ) ( )

(

,)

N V x k a k 為與u k( )

無關的項。 設µ( )

k = Ψ ku( )

,在(3-9)式中定義了將 N映射到 U U 上,代入(3-10)式可得 N( )

( )

N(

( ) ( )

,)

T( ) ( )

2 T( )

(

( )

( )

)

N V u k =V x k a k +µ k µ k − µ k Ψa k +Γx k , (3-11) 將(3-7)式重新改寫如下( )

(

( )

)

( )

(

)

( ) ( )

( )

(

( )

( )

)

* 1 arg min 2 N N U T T N u k J k J k k k k a k x k µ µ µ µ µ µ − ∈ = Ψ − Ψ + Γ 水平集合( level sets)JN是以Ψa k( )

+ Γx k( )

為中心的球面所構成的集合,且此集合在N 裡,因此可以得到

( )

(

)

(

( )

( )

)

arg min N N N U U J k q a k x k µ∈ µ = Ψ + Γ 由此可以證實(3-8)式。在(3-8)式中的 N( )

U q ⋅ 是一個N-維度的向量量化器(quantizer),而 隨著horizon length N的增加,實現上的複雜度也跟隨著增加,所以在各方面的應用上變 得有些不實際;但是相對的,當N越大時,所得到的效能(performance)也比較好,因為 在處理的過程中考慮了較多的資料(data)。MSOC在N=1時,它等於是Sigma-Delta Modulator,所以Sigma-Delta Modulator是MSOC的一個特例。 在時間t=k時,為了提高性能(performance),u*( )

k 只有第一個元素(element)將被 使用來做為回授(feedback)以及輸出,如下所示:( )

[

]

( )

[

]

(

( )

( )

)

* * 1 1 0 0 1 0 0 N (3-12) U u k u k q a k x k − = Ψ Ψ + Γ 在(3-12)式中, *( )

u k 作為轉換器(converter)的輸出,於是將( )

*(

u k ←u k)

;而 *( )

u k 還 需要用來更新(update)狀態x k( )

,所以需要做回授(feedback),更新狀態如下所示: x k(

+ =1)

Ax k( )

+B a k(

( )

−u*( )

k)

. (3-13) 在下一個取樣時間點,新的狀態將被使用做為最小化成本(minimize the cost)VN(

u k(

+1)

)

,得到 。如圖3.2所示,為N=3的Moving Horizon。當取樣時間點向前移動,也 就是 遞增時, 也隨著向前移動,而

(

1 u k+)

k VN( )

⋅ VN( )

⋅ 移動的方法即是透過狀態x( )

⋅ 。因為隨 著更新(update)後的狀態x( )

⋅ ,過去的 *( )

u ⋅ 會被傳遞,如此重複遞回下去。( )

x k( )

* u k k 1 k+ k+2 k+3 l(

1)

x k+(

)

* 1 u k+ 1 k+ k+2 k+3 k+4 l(

2)

x k+(

)

* 2 u k+ l 2 k+ k+3 k+4 k+5圖 3.2 Moving horizon principle, N=3

根據(3-12)式,必須要有現在的狀態(state)x k

( )

的資訊,可將(3-4)式改寫成 x k( ) (

= ρI−A)

−1B a k(

( ) ( )

−u k)

, (3-14) 將(3-14)式代入(3-12)式中可以得到:( )

[

]

1(

(

(

)

1[

]

)

( ) (

)

1( )

)

1 0 0 N 1 0 0 U u k = Ψ−q Ψ + Γ ρI−A − B a k − Γ ρI−A − Bu k (3-15) 將a k( )

以a k( )

表示,(3-15)式可以改寫為:

( )

[

1 0 0]

1 N(

( ) ( )

( ) ( )

)

U u k = Ψ−q Η ρ a k −F ρ u k (3-16) 其中( )

N-1(

)

1(

)

1 1 T I A B, F I A B ρ ⎡ ρ ρ ⎤ ρ − ρ − Η = Ψ⎣ ⎦ + Γ − = Γ − 圖3.3表示了(3-16)式的架構[3],是以回授的方式表示,其中粗線表示是向量的訊號路徑。 Η N( )

U q ⋅[

]

1 1 0 0 Ψ− F( )

a k u k( )

圖 3.3 以回授的方式(feedback loop)實現MSOC3.2

Relationship to the Noise Shaping Quantizer

圖 3.4 是一個常見的雜訊整形量化器(noise shaping quantizer),包含了濾波器

( )

Y ρ ,此濾波器將u k( )

與w k( )

的差異回授(feeds back)。( )

U q ⋅( )

Y ρ( )

u k( )

a k w k( )

圖 3.4 Noise Shaping Quantizer

u k

( )

=a k( )

+ −(

1 Y( )

ρ)

(

u k( )

−w k( )

)

, (3-17) 通常1 Y−( )

ρ 為一個高通濾波器,它的目的是要把u k( )

中發生的某些頻率的量化雜訊整 型(shape),也就是說它將雜訊頻譜(spectrum)推到人耳比較聽不見的頻帶去,使輸出更 為人耳所能接受。 將 n 階的 Sigma-Delta Modulator 化簡為如圖 3.5 所示[10],其中F( )

ρ 為訊號的轉 移函數,W( )

ρ 為迴路濾波器(loop filter), 為量化器。( )

u k

( )

a k

( )

F

ρ

W

( )

ρ

quantizer 圖 3.5 化簡後的 n 階 Sigma-Delta modulator 方塊圖將圖 3.5 以 additive noise model 將量化器線性化,如圖 3.6 所示,其中e k 為量化誤差,

[ ]

而量化誤差的轉移函數即為 Sigma-Delta Modulator 的雜訊轉移函數(Noise Transform Function),其轉移函數如(3-18)式所示:( )

a k

( )

F

ρ

W

( )

ρ

( )

u k

( )

e k

圖 3.6 以 additive noise model 線性化 n 階 Sigma-Delta Modulator

( )

( )

1 NTF 1 W ρ ρ = + (3-18)而在(3-17)式中,也可得到雜訊轉移函數:NTF

( )

ρ = −1 Y( )

ρ ;而又可將(3-17)式改寫 成:( )

( ) ( )

( )

( ) ( )

1 1 1 Y w k a k u k Y Y ρ ρ ρ = − − − (3-19) 經由上列式子可將圖 3.4 的回授路徑改為如圖 3.7 所示。( )

1 1 Y− ρ( )

a k( )

U q ⋅( )

( )

1 Y Y ρ ρ −( )

u k( )

w k圖 3.7 Noise Shaping Quantizer ,redrawn

將圖 3.7 與圖 3.3 比較,在 N=1 時後的圖 3.3 的架構相當於圖 3.7,則可以得到

( )

1( )

1 Y ρ ρ Η = − (3-20) 而因為NTF( )

ρ = −1 Y( )

ρ ,由(3-18)式以及(3-20)式可以得到:( )

( )

( )

( )

1 1 NTF 1 1 W Y ρ ρ ρ ρ − = = − = Η + (3-21) 由此在設計 MSOC 的Η( )

ρ 此濾波器時,即可以[3]的設計原則來設計。3.3

設計範例

根據3.1節的架構分析,以下將設計二個MSOC的實例以供參考。首先先定義四個 量測上的標準。

訊號雜訊比(Signal to Noise Ratio)

2 10 2 10 log ( x) e SNR σ σ = 其中σx是訊號的能量,σe是雜訊的能量。 總諧波失真(Total Harmonic Distortion)[11]

2 2 2 2 3 2 1 % 100 (3-22) n S S S THD S + + + = ×

其中S1為基頻(fundamental frequency) , S2 Sn為諧波頻率(harmonic frequencise) 。

如果失真的量很小,則可以將(3-22)改寫為 2 2 2 2 3 2 2 2 1 2 3 % 100 n n S S S THD S S S S + + + = × + + + + 2

總諧波失真加雜訊(Total Harmonic Distortion plus Noise)

2 2 2 2 3 1 %THD N 100 S S Sn N S + + + + + = × 2 (3-23)

其中N為非諧波訊號(non-harmonically related signals)以外的雜訊來源。

2 2 2 2 2 3 2 2 2 2 1 2 3 % 100 n n S S S N THD N S S S S N + + + + + = × + + + + + 2

感知誤差的取樣標準差 (the sample variance of the perceived error)[4]

( )

( )

2(

( ) ( ) ( )

(

)

)

2 2 1 1 1 Tf 1 Tf i i f f V e i H a i u T = T = ρ = −∑

∑

i 在以下的範例中,因為失真並不算很小,所以皆採用原式。 範例一: Sampling Frequency=1.4994MHz,Oversampling 為 34 倍。 首先設計Η( )

ρ 為純二階積分器,( )

(

1)

2 1 1 z ρ − Η = − 。 N=1,量化器(quantizer)為 1-bit。 以下是此 2-order,N=1 的 MSOC 架構圖。 1 z z− 2 a a1 1 z z− 1 z− 1 b 2 b( )

a k 2 I I1( )

u k 圖 3.8 2-order,N=1的MSOC架構圖 因為目前是採用二階的濾波器,所以在設計上並不需要特別設計係數即可穩定, 所以上圖中的a1=a2 = =b1 b2 = ,此架構即為二階的Sigma-Delta Modulator。 1 下列表格為不同頻率的數位訊號輸入,將輸出的 single bit 數位訊號取 FFT 後,藉 由上述的量測標準,比較可得。圖 3.9 為輸入 1K Hz 的數位弦波訊號所得到的輸出頻率 響應圖。表 3.3.1 二階,N=1,1-bit 的 MSOC 輸出比較結果 %THD SNR(dB) %THD+N Switching Number(times/100ms) Error variance 1K Hz 0.0184 87.90 0.18 68440 1.1056 2K Hz 0.0294 84.1152 0.28 68508 1.1402 5K Hz 0.1092 76.9934 0.63 68222 1.2044 10K Hz 0.0927 71.2661 1.22 67783 1.3286 圖 3.9 輸入為1K Hz的弦波訊號頻率響應圖 設計取樣頻率為1.4994MHz的二階、N=1的MSOC,能將量化誤差轉移到5KHz以 上的高頻區域,降低5KHz以內的雜訊大小。

範例二: Sampling Frequency=1.4994MHz,Oversampling 為 34 倍。 首先設計Η

( )

ρ 為純二階積分器,( )

(

1)

2 1 1 z ρ − Η = − 。 N=2,量化器(quantizer)為 1-bit。 以下是此2-order,N=2的MSOC架構圖。 1 z z− 1 z z− 1 z− 1( )

a k 2 I I1(

1)

u k− 1 z z− 1 z z− 1 z− 2 2 I I1 1 z−( )

2 U q ⋅(

)

1 1 d k−(

)

2 1 d k− 圖 3.10 2-order,N=2的MSOC架構圖 圖中的 2( )

U q ⋅ 為1-bit量化器,但是它有兩個input,在下一章節中將會介紹此向量 量化器(vector quantizer)的設計方法與內部結構。 由 上 圖 可 以 看 到 在 輸 入 訊 號 部 分 為 u k( )

與 u k(

−1)

, 而 在 (3-6) 式 中 ,因為在實際的系統中,是無法得到未來的輸入的,所以在實現 上是以delay的方式來表示。( )

( ) (

1)

T u k =⎡⎣u k u k+ ⎤⎦ 下表格與上一個範例一樣,皆為輸入不同頻率的弦波信號所產生的輸出比較表, 而圖 3.11 為輸入 1K Hz 的數位弦波訊號所得到的輸出頻率響應圖。表 3.3.2 二階,N=2,1-bit 的 MSOC 輸出比較結果 %THD SNR(dB) %THD+N Switching Number(times/100ms) Error variance 1K Hz 0.0167 88.2974 0.17 71550 0.6390 2K Hz 0.0291 84.2978 0.27 71760 0.6393 5K Hz 0.1124 77.0909 0.63 71757 0.6601 10K Hz 0.0913 71.2923 1.22 72085 0.6842 44.1K*34 Hz (Hz) 圖 3.11 輸入為1K Hz的弦波訊號頻率響應圖 比較表格3.3.1與3.3.2發現,在%THD、SNR與%THD+N沒有相差很大,但是在N=2 時是有稍微好一些的;而在切換次數上(switch number),N=2略大於N=1;在感知誤差 的取樣標準差上,N=2明顯的比N=1小。

比較圖3.9與3.11,可以發現圖3.11中的量化誤差轉移的效果稍微好一些,約將量化 誤差轉移到6KHz以上的高頻區域,降低6KHz以內的雜訊大小。 而在二階,1.5-bit的N=1與N=2的部份,分別與範例一與範例二的架構圖一樣,但 是在於 2

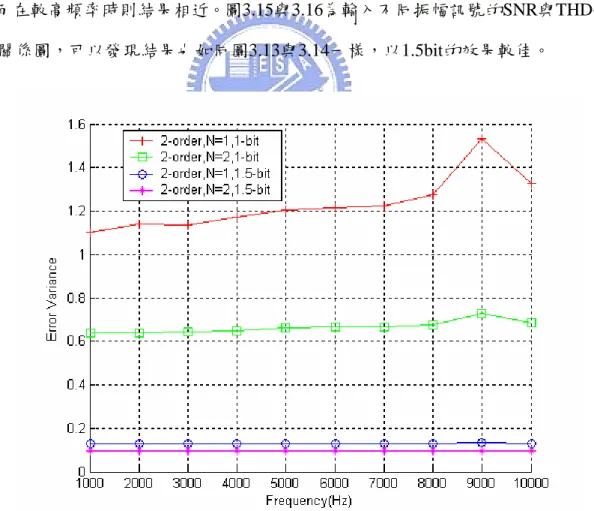

( )

部份,N=1為1.5bit的Quantizer,而N=2的部份為1.5-bit的Vector Quantizer。 U q ⋅ 下 圖 3.12 、 3.13 以 及 3.14 為 比 較 2-order,N=1,1-bit 、 2-order,N=1,1.5-bit 、 2-order,N=2,1-bit以及2-order,N=2,1.5-bit的Error Variance、SNR及THD+N關係圖。由圖 中可以發現N=2的Error Variance比N=1的小,又1.5-bit的Error Variance比1-bit的小。在此 2-order,N=2,1.5-bit有最小的Error Variance;在SNR與THD+N的部份,當N=1與N=2的表 現上差異不大,而在1.5-bit與1-bit的結果上,發現當在較低頻率時候,1.5-bit的效果較 好,而在較高頻率時則結果相近。圖3.15與3.16為輸入不同振幅訊號的SNR與THD+N的 比較關係圖,可以發現結果也如同圖3.13與3.14一樣,以1.5bit的效果較佳。圖 3.13 SNR比較關係圖

圖 3.15 輸入不同振幅的訊號之SNR比較關係圖

第四章 量化器的設計實例與分析

在圖3.10中出現向量的量化器,而其中量化器又包含了one bit與1.5-bit,所以在此 節中將介紹在實作上所需要用到的各種量化器。

4.1 Horizon One and 1.5-Bit

選擇N=1且輸出為1.5-bit的量化器(quantizer),在(3-9)中 ,在此使用 二階的MSOC, , N i i i v = Ψv v ∈U

{

1 , 0 , -1 ,}

=1 U = Ψ ,可以將之映射到U ={

1 , 0 , -1}

,因為 1 U∈ , 所以可將 軸上的輸入分為三個值,可以由圖4.1中看到此量化器(quantizer)的分割 情形,而圖中的深灰色區段表示量化後的輸出為1;灰色表示為0;淺灰色表示為-1。而 圖4.2可以看到此量化器(quantizer)的架構圖。( )

1 d k( )

1 d k 1 0 1 −( )

1 0.5 0 d k + =( )

1 0.5 0 d k − = 圖 4.1 一維量化器 0.5 0.5 ( ) U q ⋅ ( ) U q ⋅ ( ) 1 d k u k( ) 圖 4.2 一維量化器之架構圖4.2 Horizon Two and One - Bit

選擇N=2且輸出為1-bit,U ={

1 , 1− ,可以得到:}

2 1 , 1 , 1 , ,1 1 1 1 1 U = ⎨⎧ −⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥− ⎫⎬ − − ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎩ ⎭ 將之映射到 2 1 1 1 1 , , , 3 1 3 1 U = ⎨⎧ −⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥− ⎫⎬ − − ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎩ ⎭ 向量量化器(vector quantizer) 2( )

Uq ⋅ 依據nearest neighbor rule(3-1),分割了輸入空間 成四個區域。但是在(3-12)式中,我們僅對u 2

( )

* 的第一個元素有興趣,所以只有兩個 區域是有意義的。將(3-16)是寫成如下: k( )

[

1 0 0]

N(

( )

)

U u k = q d k (4-1) 其中 d k ,在圖3.10中可以看到。 由圖4.3可以看到如何分割此兩個有意義的區域。由圖中可以看到U 中的四個轉換後的2 參考點(紅點),而根據nearest neighbor quantizer的方法,此座標平面上的任何點與此四 個參考點分別比較距離,也就是比較平方差,選取與之平方差最小的參考點為其量化 後的值,但是因為我們只在意( )

( )

( )

1 2 d k d k d k ⎡ ⎤ ⎢ ⎥ ⎣ ⎦ = 的d k1( )

,所以最後只會將座標平面分為 兩個區域 與 ,其中 為圖中淺灰色的區域; 為深灰色區域,因為在此是1-bit 的量化器,所以 1 D D2 D1 D2 經由下列式子實現( )

(

(

1( )

2( )

)

(

1( )

2( )

)

(

1( )

2( )

)

)

u k =qU qU d k +2d k − +2 qU d k +2d k + +2 qU d k +d k (4-2)( )

1( )

( )

2 d k d k ⎡ ⎤ ⎢ ⎥ ⎣ ⎦ =( )

( )

( )

1 2 1 , if 1 , if d k D u k d k D + ∈ ⎧⎪ = ⎨− ∈ ⎪⎩其中if

( )

⋅ ≥0 , then qU = +1 ;( )

⋅ <0 , then qU = −1. 而由圖 4.4 可以看到此量化器的架構圖。 圖 4.3 N=2 的 1-bit 量化器之區域分割( )

2 d k( )

1 d k 2 2 2( )

U q ⋅( )

U q ⋅( )

U q ⋅ qU( )

⋅( )

u k 圖 4.4 N=2 的 1-bit 量化器之架構圖4.3 Horizon Two and 1.5 - Bit

選擇 N=2 且輸出為 1.5-bit,U ={

1 , 0 , 1− ,}

可以得到 2 1 1 1 1 0 1 -1 0 0 將之映射到 , , , , , , , , , 1 1 1 1 0 0 0 1 -1 U = ⎨⎧ −⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥− ⎫⎬ − − ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎩ ⎭ 2 1 1 1 1 0 1 -1 0 0 , , , , , , , , 3 1 1 3 0 2 -2 1 -1 U = ⎨⎧ −⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤ ⎡ ⎤⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥− ⎫⎬ − − ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎣ ⎦ ⎩ ⎭ 向量量化器(vector quantizer) 2( )

U q ⋅ 分割了輸入空間 成九個區域,因為在此為 1.5-bit 的量化器(quantizer),又因為只取 2( )

* u k 中的第一個元素,所以將座標平面分成三個區 域,由圖 4.5 中可以看到九個轉換後的參考點(紅點),以及分割的三個區塊分別為 ,其中 為圖中淺灰色區塊; 為深灰色區塊; 為灰色區塊。而可以得 到輸出為 1 D、D2與D3 D1 D2 D3 1 2 3 1, if ( ) ( ) 1, if ( ) 0, if ( ) d k D u k d k D d k D − ∈ ⎧ ⎪ = +⎨ ∈ ⎪ ∈ ⎩ 經由下列式子實現( )

{

(

( )

( )

)

(

( )

( )

)

( )

( )

(

)

(

( )

)

1 2 1 2 1 2 1 2 2 0.5 2 4.5 0.5 U U U U U u k sign q q d k d k q d k d k q d k d k q d k ⎡ = ⎣ + − + + − + + − + −( )

( )

(

)

( )

( )

(

)

(

( )

( )

)

( )

( )

(

)

(

( )

)

1 2 1 2 1 2 1 2 1 1 2 2 0.5 2 4.5 0.5 U U U U U U q d k d k q q d k d k q d k d k q d k d k q d k ⎤ + + − ⎦ ⎡ + ⎣ + + + + + + + + + +( )

( )

(

1 2)

}

+qU d k +d k + ⎦1 ⎤ (4-3)其中if

( )

⋅ =0 , then sign( )

⋅ =0 ; if( )

⋅ >0 , then sign( )

⋅ = +1 ; if( )

⋅ <0 , then sign(

⋅ = −)

1. 由(4-3)式發現,由於分割區域所呈現的狀態較複雜,在實現上會使用到較多硬體,在此 我採用了圖中有標示的十個方程式去趨近。而圖 4.6 可以看到實現此量化器的架構圖。1

D

2

D

3

D

1

2 3 41

2 3 1d

2d

1 2 2 4.5 0 d + d − = 1 2 2 0.5 0 d + d + = 1 2 2 4.5 0 d + d + = 1 2 2 0.5 0 d + d − = 1 0.5 0 d − = 1 0.5 0 d + = 1 2 1 0 d +d − = 1 2 1 0 d +d + = 1 2 2 0 d + − =d 1 2 2 0 d + − =d 圖 4.5 N=2 的 1.5-bit 量化器之區域分割 2 0.5 ( ) U q ⋅ ( ) U q ⋅ ( ) 1 d k ( ) 2 d k ( ) u k 4.5 0.5 2 1 4.5 ( ) U q ⋅ ( ) U q ⋅ ( ) U q ⋅ ( ) U q ⋅ ( ) U q ⋅ ( ) U q ⋅ ( ) sign⋅ 2 1 ( ) U q ⋅ ( ) U q ⋅ 0.5 0.5 ( ) U q ⋅ ( ) U q ⋅ 圖 4.6 N=2 的 1.5-bit 量化器之架構圖第五章 實現

要實現一個全數位化的音頻擴大器,其架構如圖 1.2 所示,而圖中的『Modulator』 與『Amplifier』方塊,要能即時(real time)地接收由 PC 端送出的 16bits 數位音樂訊號, 並將其調變為 one bit 或是 1.5-bit 的數位訊號,經由功率放大後將其輸出。因此,利用 USB 作為與 PC 端的介面、FPGA 實現數位的 Multi-Step Optimal Converter(MSOC)以及 power MOS 實作一個高速的切換式 power stage,三個部分來實現全數位化的音頻放大 器。圖 5.1 顯示了實現此全數位化的音訊擴大器的方塊圖。

圖 5.1 全數位化的音頻擴大器系統方塊圖

以 FPGA 實現 1499.4KHz 的數位 two-step 的 MSOC,輸入訊號為雙聲道 16-bits、 44.1KHz 的 PCM 音樂訊號,經過調變後輸出為 one-bit 或是 1.5-bit 的數位訊號。因此此 雙聲道 44.1KHz、16-bits 的音樂訊號必須及時的從 PC 端送出,而 USB 就是 PC 端與 FPGA 之間的介面。但是因為 FPGA 的輸出電壓為 3.3V 的數位訊號,此電壓不足以推 動喇叭,所以需將輸出訊號經過一個 power stage 做功率放大,再將此輸出推動喇叭。

5.1 USB 介面

USB 為 Universal Series Bus(萬用串列匯流埠)的縮寫。因為 USB 允許把外界的設備 與 PC 連接,不需重新配置規劃系統,且有隨插即用的功能,所以在此選用 USB 當做 介面。USB 界面使用 7-bit 的定址欄位,扣掉 USB 主機預設給第一次接上的周邊設備 使用,還剩 127 個位址可以使用,因此一部電腦最多可以連接 127 個 USB 裝置。 Host Host hub Devic Devic Hub Devic Hub埠 圖 5.2 USB 基本架構 一般 USB 系統的基本架構可以分為三個主要部份[12]: 1. USB 主機控制器(Host controller)/根集線器(Root Hub) 2. USB 集線器(Hub)

3. USB 裝置(Device)

所有在 USB 系統上的溝通都是在軟體控制下由 PC 主機啟動的,而主機的硬體函括了 主機控制器與根集線器。但是光靠根集線器不可能同時連接上 127 個周邊,所以 USB 系統還支援額外的集線器,而 USB 裝置就是泛指 USB 的各類型的周邊,而整個 USB 連接裝置的方式是類似於金字塔型的架構。圖 5.2 顯示了 USB 的基本架構圖,其中 USB

Host 端的角色是 master,所有 Device 都聽 Host 端控制。

USB 的 傳 輸 類 型 共 有 四 種 : 控 制 傳 輸 (Control Transfer) 、 中 斷 傳 輸 (Interrupt Transfer)、巨量傳輸(Bulk Transfer)及等時傳輸(Isochronous Transfer)[13]。

‧ 控制傳輸:用來配置以及送出命令給裝置的,為雙向傳輸。控制型傳輸包含三種控 制傳輸型態:控制讀取、控制寫入與無資料控制。運用 CRC(Cyclic Redundancy Check) 來檢查資料之正確性,若此錯誤無法恢復,則要求重新傳送。 ‧ 中斷傳輸:在 USB1.1 中定義為雙向傳輸。由於 USB 不支援硬體的中斷方式運行, 所以必須靠主機以週期性的方式來輪詢(Polling),故於 USB 的中斷傳輸意即是一種 輪詢的過程。對於 12Mbps 的裝置而言,可以訂定 1ms 至 255ms 之間的輪詢週期, 所以最快的輪詢速度為 1kHz。適用設備為鍵盤、搖桿或滑鼠。 ‧ 巨量傳輸:一種突發性的傳輸模式,可為雙向或是單向的傳輸。適用於傳送大量的 資料,且沒有固定的傳輸速率,適用設備為印表機或掃描器等。 ‧ 等時傳輸:用來傳送高頻寬、以及對時間有嚴格要求的資料,可為單向或雙向的傳 輸。此種傳輸需要維持一定的傳輸速度,且不具有錯誤檢測的能力。它事先與主機 協議好固定的頻寬,以確保發送端及接收端的傳送速度。適用設備為 USB 麥克風、 喇叭或是 MPEG-1 的裝置。 表 5.1.1 USB 四種傳輸模式比較 封包大小(Byte) 時間 資料檢查 應用 巨量傳輸 8、16、32、64 盡快完成 有 儲存裝置、印表機 中斷傳輸 1~64 1~255ms 有 滑鼠、鍵盤 等時傳輸 1~1024 1ms 沒有 影像、聲音 控制傳輸 盡快完成 有 命令

5.1.1 硬體介紹

Cypress AN2131Q USB 專用晶片(與 8051 Core 相容) 台灣長高科技公司 DMA- Cypress USB AN2131 控制單板 .符合 USB1.1 版,12Mbps 高速傳輸博定標準 .提供 31 個可使用的端點 .支援等時、巨量、控制和中斷四種傳輸模式 .可另外接 D0~D7 資料匯流排與 A0~A15 位址匯流排 .ROM 可擴充至 32K RAM .提供偵錯與發展的環境(Keil C Compiler)

.使用與 8051 Core 相容的 Cypress AN2131Q USB 專用晶片。包含 8051 與 相容的 P0、P1 與 P3 週邊 port,可直接執行一般 8051 的 I/O 控制。

5.1.2 軟體介紹

1.Keil Vision 2µ

圖 5.4 Keil Vision 2µ 使用介面

經由此 Keil Vision 2µ 的發展軟體,執行 AN2131Q USB 晶片程式編輯、編 譯動作,進而產生.hex 檔,在此為將 C code 編成 for Cypress AN2131Q USB 專用 晶片的 hex 檔。

2.EZ-USB

圖 5.5 EZ-USB 使用介面

當正確的進入 EZ-USB Control panel 後,即可進行對 DMA-USB 2131 控制 單板測試,下載(download)以及燒錄 EEPROM 等等的動作。在此為以 EZ-USB 將編譯完成的.hex 檔 download 到控制單板,重新裝置列舉後,單板由 Cypress EZ-USB (2131Q)的 USB 裝置,轉型為一個.hex 檔指定式樣的 USB 裝置。

5.1.3 USB 實作

可以將工作分為二部分,USB 描述元–讓 PC 的作業系統能使用此 USB 裝置;8051 I/O 控制程式–將資料傳送給 FPGA。 1.USB 描述元 在 USB 規格中定義了一些裝置群組,有 Audio、Communication、Display、 以及 Printer 等等,而在此是要即時地傳送 44.1KHz、16-bits 的音樂資料,所以 裝置群組應為 Audio 類型,且傳輸模式為等時傳輸。而等時傳輸,時間的最小單 位是 1ms,即最快每 1ms 將資料送出一次,因此,每一次的資料應該為 44 或 45 筆 16bit 的資料。將控制單板宣告為 USB audio 裝置,需要寫 USB 描述元。USB 描述元是記 錄關於裝置的各種訊息與其相關設定。宣告一個 USB audio 描述元,其架構圖如 圖 5.6 所示。其每個 Descriptor 都是填寫一份表格[14]。

USB audio 描述元完成後,接上 PC 端,會辨識新連接的 USB 描述元,新增 加一個可用硬體–USB audio 音效裝置。此時,啟動應用程式,音樂訊號就會從 PC 送到 USB 的端點暫存區。只要是符合 USB Class 規定的裝置,其驅動程式已 包含在作業系統,而不用另外再寫其驅動程式,應用程式就可以直接使用裝置。 在圖 5.7 中可以看到在 PC 端上的硬體裝置管理員新增 EZ-USB 2131 ,以及將此 控制單板裝置列舉的狀況。

Device Descriptor

Configuration Descriptor

Audio Streaming Interface Descriptors

String Descriptors

Audio Control Interface Descriptors

Standard AC Interface Descriptor

-Classspecific AC Interface Descriptor Input Terminal Descriptor

Output Terminal Descriptor

Standard AS Interface Descriptor (Alternate Setting 0) Standard AS Interf ace Descriptor (Alternate Setting 1) Class-specific AS General Interface Descriptor

Standard Endpoint Descriptor

Class-specific Isochronous Audio Data Endpoint Descriptor Format Type Descriptor

Manufacturer String Descriptor Product String Descriptor

圖 5.7 USB 單板以 USB audio Class 描述元裝置列舉

2.8051 I/O 控制程式

等時傳輸最快以每 1ms 的速度傳輸一次資料,資料傳完後,會發出一次等 時中斷。而利用等時中斷機制,來知道端點暫存區是否有資料可以輸出到 I/O PORT。端點暫存區有個 count 機制,記錄目前暫存區內有多少 Byte 資料,每當 暫存區被讀出 1Byte 資料,count 會減 1。利用 count 機制,來知道端點暫存區是 否已經空了,如果空了,即可結束搬運。

Cypress USB 專用晶片與 8051 Core 相容,是 Enhanced 8051。寫 C code 指 定端點暫存區,利用等時中斷與暫存區的 count 機制,將資料搬移到指定 I/O PORT。8051 是八位元單晶片,所以必須利用二個 OUTPUT PORT 送出 16bit 的 音樂資料,分別輸出 high byte 與 low byte。規劃第三個 PORT 的二個腳位,當做 單版與 FPGA 的控制訊號(ch1/ch2 write enable),這樣就能夠在單版上的 I/O PORT 得到 44.1KHz、16bit 的 PCM 音樂訊號。圖 5.8 可以看到此主程式的流程 圖[15];圖 5.9 為中斷服務程式流程圖[15]。

設定 USB 在一般工作模式

初始化副程式:

1.設定 PORTA、B、C 為 OUTPUT PORT 2.Enable PORTA、B、C

3.reset PORTA、B、C 腳位到初始值 4.設定端點 8 暫存區大小

5.指定端點 8 發出 Sof(等時)中斷 6.Enable Sof(等時)中斷

load USB Descriptors

Enable 必要的其他中斷: SUDAV 中斷 SUTOK(執照封包)中斷 SUSP(中止)中斷 URES(重置)中斷 Enable USB 中斷 while(1) 真 圖 5.8 主程式流程圖

讀端點8暫存區,輸出 1 個 Byte 到 PORT A 讀端點8暫存區,輸出 1 個 Byte 到 PORT B 輸出 0x02 到 PORT C 讀端點8暫存區,輸出 1 個 Byte 到 PORT A 讀端點8暫存區,輸出 1 個 Byte 到 PORT B 輸出 0x01 到 PORT C 是 否 讀端點8 的ByteCount 暫 存器判斷端點 8 暫存區是 否為空 Sof(等時)中斷是否發生 否 是 設 PORTA、B、C 腳位到初始值 清除 Sof 中斷 Enable Sof中斷 圖 5.9 中斷服務程式流程圖

由下表 5.1.2 可以看到分別為 USB Device 接收由 PC 端傳送的音訊資料、8051 的 OUTPUT PORTA 與 PORTB,以及 USB Device 傳送資料到 FPGA 的情形。USB 等時傳 輸時間最小單位為 1ms,由圖 5.10 可知,在此設定此傳輸時間為 1ms,而 USB Device 傳輸完資料的時間約為 0.8ms,此資料速率與 FPGA 需要的 44.1KHz 數位訊號並不相 符,所以資料在 USB 端送往 FPGA 處理時,需要先經由一個 buffer,而此 buffer 在此 為 FIFO 的型態。 表 5.1.2 USB 音效裝置輸出資料的時間關係 等時傳輸 第1~9ms 第10ms USB Device 收到資料 USB Device 傳送資料 (1 Channel)

左聲道 low byte, 左聲道 high byte, 右聲道 low byte, 右聲道 high byte

*44 *45 PORTB PORTA *44=0.7876ms 17.9us *44 *45 *45=0.8055ms 17.9us 圖 5.10 USB 傳送資料速度與 FPGA 消秏資料速度 0.786ms 17.9us 22.6us 1ms … USB Device … 傳送資料速度 44.1KHz 消秏資料速度

5.2 FPGA

FPGA 全名為 Field Programmable Gate Array,是由許多各邏輯單元胞(Logic Cell) 經由可程式的垂直通道(Vertical Channel)以水平通道(Horizontal Channel)的連線所構 成,圖 5.11 可以看到其基本架構。FPGA 根據其物理架構可分為兩類,一為 SRAM 型, 一為 Anti-fuse 型。在此選用 SRAM 型,因為它具有可重複程式化的優點,適合用來作 邏輯設計的測試與功能性驗證。 Input/Output Pin Logic Cell Programmable Interconnect 圖 5.11 FPGA 之基本架構圖

5.2.1 硬體介紹:Altera FLEX10K Emulation Board

ALTERA 10K-ARC240 .10K Gates

.work frequency over then 30MHz .supply voltage 5V regulated to 3.3V .3.3V 的 I/O

.with EPPROM

圖 5.12 Altera FLEX10K Emulation Board

5.2.2 軟體介紹:Quartus II

Quartus II 4.1:一個發展 FPGA 的環境,能夠編譯 VHDL code、simulation 看時序 圖檢驗 logic、規劃 FPGA 的輸入輸出腳位、將編譯好的 code 程式化 FPGA 或 EPPROM。 在 FPGA 的實現上採用此軟體,而沒有使用較早期的 MAX+PLUS II,乃因 Quartus II 的 complier 比 MAX+PLUS II 的更進化,因為它能提供一個 timing 效率更高的 P&R

(Placement and Routing),但也因為如此,所以它在 complier 後會使用到較多的 resource, 所以 resource usage 會較 MAX+PLUS II compiler 後的多一些。下圖可以看到此軟體的使 用介面。

圖 5.13 Quartus II 4.1 使用介面

5.2.3 FPGA 實作

1. buffer 方塊

圖 5.1 因為 USB 送出資料的速度,與 FPGA 需要的 44.1KHz 數位訊號,速 率不相配,因此 FPGA 除了 MSOC 方塊之外,需要設計一個16 bit 的 FIFO(First In First Out)作資料緩衝。

16 ×

的指標有二個,一為資料寫入指標,另一為資料讀出指標。資料寫入指標每寫入 一筆資料後其值應自動加一,以便下次資料寫入時能依序地將資料寫入。FIFO 電路有資料先進先出的特性,資料在 FIFO 中應該由排隊的方式來寫入與讀取。 當資料自 FIFO 讀出時,其讀出指標應自動加一,以便下次能依序將資料讀出。 FIFO 的輸入輸出腳位,應有資料 input port、資料 output port、wr_enable、 rd_enable、full、empty 與 reset[16]。由圖 5.14 可以看到此 FIFO 的內部基本方塊, 其中資料寫入與資料讀出部份皆為 16-bits 的資料;而控制電路部份,Full 與 Empty 分別控制資料寫入指標計數器與資料讀出指標計數器。

圖 5.14 FIFO 內部基本方塊圖

圖 5.15 為此 Buffer 的 I/O 方塊圖,而圖 5.16 為此資料暫存器組中的資料 Full 與 Empty 的狀況。

圖 5.15 Buffer 方塊的 I/O Rd_ptr Wr_ptr EMPTY 16 0 … Rd_ptr Wr_ptr FULL 16 … 1 0 1 Rd_enable=1 Wr_enable=1 圖 5.16 空、滿的 buffer 方塊示意圖

2. MSOC 方塊 由(3-12)式可知

( )

[

]

1(

( )

( )

)

1 0 0 N U u k = Ψ−q Ψa k + Γx k ,以及(3-13)式(

)

( )

(

( )

*( )

1)

. x k+ = Ax k +B a k −u k ,實現上大致可以分為下列五個步驟: .step1 從 FIFO 將輸入資料a k( )

取進來 .step2 將a k( )

經過一個 Delay .step3 計算Ψa k( )

+ Γx k(

)

.step4 將 step3 的輸出經過 Vector Quantizer

.step5 更新x k