逢 甲 大 學

資 訊 工 程 學 系

專 題 報 告

◎USB介面之加解密卡製作◎

學 生: 王銘清 (四乙)

林國棟 (四乙)

指

導

教

授 : 陳德生

中華民國九十一年十二月

目錄

一. 簡介---1

-動機---1

-目標---3

二. 發展環境和平台介紹---4

三. 系統架構簡介---7

-系統架構---7

-硬體電路架構---8

-軟體架構---11

-USB 發展板部份---12

-Driver 的部份---13

四. 產品的應用---16

-USB device 操作範例---18

五. VHDL 簡介---22

- VHDL 的發展---22

- VHDL 的優點---23

- VHDL 重要詞彙---25

六. USB 簡介---28

- USB 的傳輸類型---29

-為何選用 USB 傳輸介面---30

七. DES 加/解密介紹---32

- DES 演算法---32

- DES 的細節說明---33

-替換盒---36

- f 函數---38

-子金匙---40

八. 專題經驗---43

九. 心得---45

十. 參考資料---50

圖表目錄

表 2.1 USB 界面 I/O 控制實驗卡說明---4

圖 2.2 USB 界面 I/O 控制實驗卡---5

表 2.3 EXCALIBUR 板規格說明---5

圖 2.4 EXCALIBUR 板實體---6

圖 3.1 實作架構圖---8

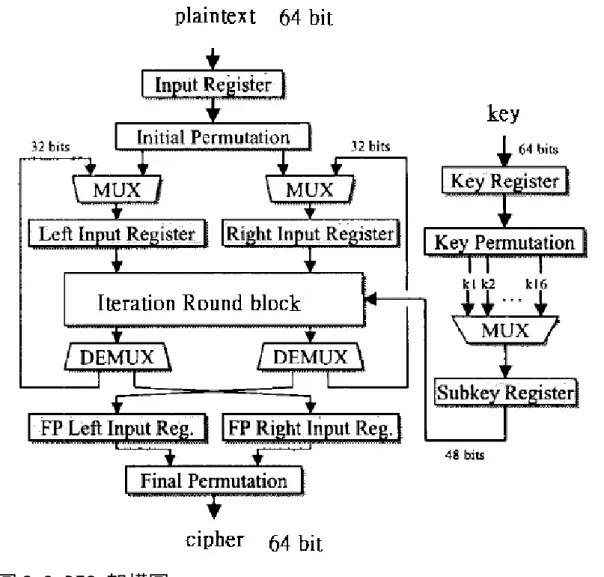

圖 3.2 DES 架構圖---9

圖 3.3 DES 流程圖---10

圖 3.4 軟體關係架構圖---11

圖 3.5 Driver Wizard---13

圖 3.6 Generate Driver Code---14

圖 4.1 產品操作介面---16

圖 4.8 明/密文檔比較---21

圖 7.1 DES 加/解密架構圖---34

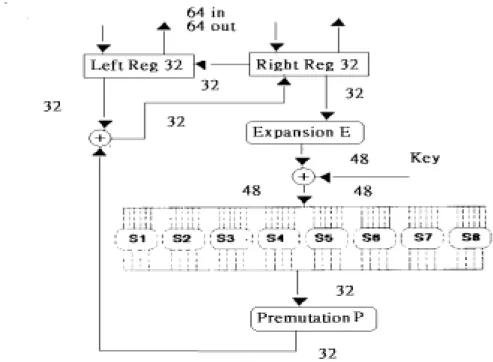

圖 7.8 f 函數計算過程架構---39

一、簡介

動機

在大學三年的課程之中,學習了不少有關硬體與軟體領域的知識 技能,而在學生吸收多方面廣泛的領域之後,發現自己對硬體與軟體 都有不少的興趣,於是想找一個專題能夠對學生在這兩方面的訓練有 所幫助。而學校之中的資源充足,又有指導教授與學長的經驗傳授, 加上學生對網路有興趣,所以想了解一下有關加/解密方面的知識, 所以在請教過指導老師之後,決定了做這個專題的研究。 日常生活中隨處可見有關加/解密的應用,商業機密文件、摩斯 電碼、軍用情報系統、網路系統皆有加/解密的使用,但一般人對於 加/解密通常以只想到軟體來實作,但是如果沒有良好的硬體做為基 礎,再優良的軟體功能也只能事倍功半,所以假如我們改良了硬體的 功能而能夠分擔軟體上的負擔,是否就能增進整體的效能,也因此產 生了可否在硬體上實作加/解密的疑問。 近來利用 PDA、NoteBook、PC 網路進行電子交易、溝通行為漸漸 普遍,我們知道在網路上進行傳輸的是所謂電子文件,現行法上並無 法符合有關「書面」要式行為要求,所以電子文件並無法突破現有法 律規定之限制障礙。而為解決這個問題,世界各國均訂定電子交易法、電子簽章法賦予法律效力。為因應國際趨勢,行政院亦積極進行 電子簽章法之研擬,而也已經三讀審查通過,完成我國電子簽章法立 法制定程序。 然而這一切都是在說明資訊安全的重要,今天我們以為了達到使 用方便且易攜帶為前提去架構我們的計劃。所以我們的目標是以 USB 的介面為前提,發展加/解密的硬體電路,實作美國國家標準局公佈 為 資 料 加 密 標 準 的 一 種 區 塊 加 密 法 — DES (Data Encryption Standard),加上應用程式的配合達到資訊安全課題中檔案的加/解密 提昇檔案的安全性與機密性。

目的

對此次計劃我們可以對我們的檔案、文件、mail…等等做加密的 動作,而當需要開啟該文件時只要將隨插即用的 USB 插入,就可即時 的解密,進而達到保護文件的功能,如此一來,就算丟了 PDA 或 notebook 也不用擔心裡面的資料會被別人一覽無遺,而且我們的加/ 解密的 KEY 將會以 ROM 的方式燒在我們設計的硬體裡面,並且提供方 法可更改 Key。 設計的加/解密硬體電路,供 PC 上較需保密或機密性較高、又或 較具個人隱私的檔案做保護,即使檔案落入他人手中,也無法窺視到 其檔案中的內容。這個硬體電路我們以 USB 為傳輸介面,並自行設計 DES(Data Encryption Standard 美國國家標準局公佈為資料加密標 準的一種區塊加密法(Block Cipher))的硬體電路,自行開發韌體和 趨動程式,並且自行設計一套檔案加/解密的系統。在這套系統中我 們提供金匙的存取,及 signal DES 的模式以 ECB (Electronic Code Book)模式來進行任何檔案的加/解密動作,以達到個人檔案、隱私、 機密資料的保護。並且加上 USB 傳輸介面的優點--隨插即用、可連接 多個裝置、節省能源…等等,可以讓我們的作品具有方便攜帶、安裝, 簡易使用的特性。二. 發展環境和平台介紹

此次計劃中我們主要的硬體發展平台是以長高科技的”USB 界面 I/O 控制實驗卡”和 ALTERA 的 EXCALIBUR development board,這二 張發展板為發展平台。

1.USB 界面 I/O 控制實驗卡

長 高 科 技 的 ”USB 界 面 I/O 控 制 實 驗 卡 ” 為 USB1.1(full speed),大致說明如下: 表 2.1 USB 界面 I/O 控制實驗卡說明 DMA-USB FX-CY7C64613-128 發展系統 • 使用 CY7C64613,128-Pin FX USB 專用晶片。 • 包含與 8051 相容的 P0,P1,P2 與 P4 週邊 Port。 • 外接與 8051,40-Pin 相容的擴充接腳,可直接執行一般 8051 的 I / O 控制。 提供 GPIF 介面。 • 可擴充至 32 K RAM。 • 可另外接 D0~D7 資料匯流排與 A0~A15 位址匯流排。

圖 2.2 USB 界面 I/O 控制實驗卡

2. ALTERA EXCALIBUR Development Board

我們用到的是下面所列的這一型 APEX20K200,484Pin 型。

Device EP20K200

Maximum System Gates 526,000

Logic Elements 8,320

Maximum RAM bits 106,496

Phase-Locked Loops (PLLs) 1

Speed Grade -3, -2, -1

Maximum User I/O Pins 382

Package (mm) Maximum User I/O Pins

484-Pin FineLine BGA Package

23 x 23 382

圖 2.4 EXCALIBUR 板實體

在這塊板子上我們只用它的 FPGA (APEX20K),並沒有用到 Nios 的 processor 與其它周邊,其中 USB 發展板和 FPGA 之間的連共用了 22 Pins。

硬體電路設計部份主要是以 VHDL 語言為主,而整個發展平台以 ALTERA Quartus II 2.0 和 MAX+plus II 10.1 為主。而硬體描述語 言所寫的電路行為,我們用 VHDL 來描述硬體電路,用 Java 做驗證。 關於 USB development board 的 firmware 是以 Keil C 為發展軟體。 該加/解密電路的設計主要是應用在一般 PC 平台,所以在趨動程 式部份以 WinDriver 為發展軟體,在應用程式方面以 Microsoft Vsual C 與 Borland C++ Builder 為主要發展軟體,當然還有其它的 軟體,而作業系統為 Microsoft Windows 98。

三.系統架構簡介

系統架構

大致上我們將整個計劃由 USB 發展板和 PC 之間切為兩部分,一 部分是 DES 硬體電路的發展加上 USB 韌體的撰寫,另一部份是軟體部 份,由應用程式和趨動程式所架構。

硬體電路架構

首先就 FPGA 上的電路做一一介紹:

圖 3.1 實作架構圖

上圖這個電路是我們的構想,大致上分五個元件,有主要的控制 器與二塊 RAM、一塊 ROM 和 DES 的電路。控制器--控制整個電路的運 作,它會送訊號給其它四個元件,當然其它模組也會回傳某些控制訊 號。例如對於 input RAM,控制器必須告訴它—目前須要將資料載入 到那個位址,必需要告訴它目前是做寫入還是讀取資料,必須告訴 DES 現在資料己載入可以開始運作,也回傳給控制模組 DES 的 ready

8 6 8 8 8 8 DES Module FSM CONTROLLER Key ROM USB Board Data_out RAM Data_in RAM

和 busy 的訊號,它需要與 USB 的 8051 送出的 rd、start 訊號線以 handshaking 模式做資料傳輸,而輸出端的序列傳輸一樣也是以一條 rd and start 與 USB 做 handshaking 的傳輸。而二塊 RAM 其大小為 64 位元組,儲存要加/解密的資料和加/解密完的資料。

主要是 DES 的模組,詳細的 DES 架構圖如下圖:

由控制電路去控制 DES 所需完成的 16 個 round,與 triple DES 裡 DES 所需跑的次數,以及 KEY 的載入。中間所繪的 Iteration Round block 是指 DES 必須完成的 16 回合,而其中的一個回合請看下圖:

圖 3.3 DES 流程圖

軟體架構

這部份包含兩個部份,其一為 WinDriver 與 Application,而中 間的的關係架構圖如下:

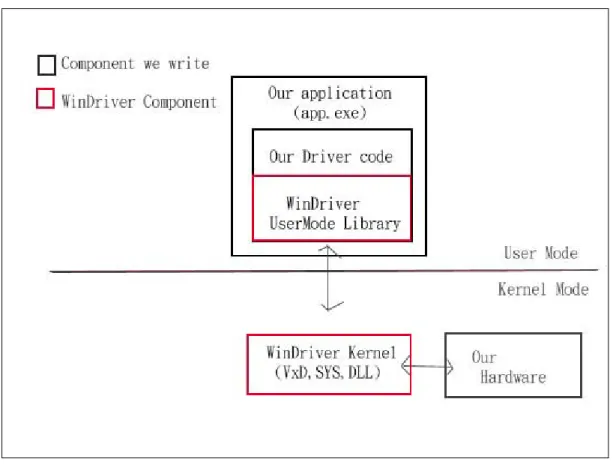

圖 3.4 軟體關係架構圖

我們的 AP 是架構在 WinDriver 的 Library 上,AP 呼叫 Library 中 的 function , 而 Library 再 透 過 Kernel Mode 中 的 WinDriver-Kernel 來存取我們的 Hardware 資源,大致上就如圖中所 示。

USB 發展板部份

在 I/O 部份,由於我們是使用 cypress CY7C64613 128pin FX USB 的晶片,其中包含 8051 microcontroller 與 PA,PB,PC 與 PD 四 組 I/O Port。我們利用 PA、PD 做為資料傳輸的 databus,PC 傳送控 制訊號、指令、與 handshaking 訊號。

在 USB 功能上,我們一共使用了 3 個 bulk endpoint 來完成我們 系統所需的功能,其中包含 2 個 bulk input endpoint 和 1 個 bulk output endpoint,當然還包含 0 endpoint (control)。在 input endpoint 中設定為加密的資料傳輸,而 output endpoint 裡包含從 DES 電路讀取加/解密完的資料。

所以一個完整的加/解密動作為(在硬體部份),首先由 endpoint 寫入資料到 USB,再送出控制訊號,讓 DES 電路讀取密文或明文存在 移位暫存器裡,同時載入要加/解密的 KEY,經由 DES 的 16 個 Round 完成加/解密動作,再由 DES 控制器送出 handshaking 訊號給 USB, 再經由 in 端的 endpoint 讀取加/解密完的資料。

Driver 的部份

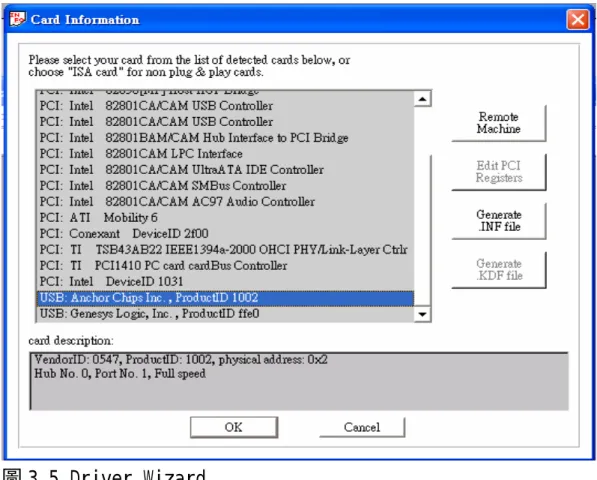

我們使用的是 Jungo 公司出品的 WinDriver 來撰寫我們的 USB driver,一開始我們會先利用 WinDriver 中的 Driver Wizard 來偵測 我們的 USB device(如圖 3.5)。

圖 3.5 Driver Wizard

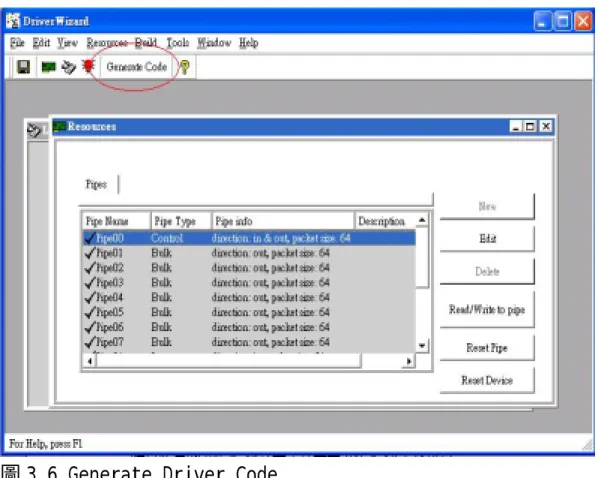

找到我們的 USB device 時,再針對它產生 INF 檔,然後當 Windows 發現新硬體時以產生的 INF 檔做安裝,安裝完後,按圖二中紅色橢圓 形圈起來的按鈕,就可以針對這個 Device 產生它的一些基本 Function code 及一個簡單的範例程式。

圖 3.6 Generate Driver Code

接下來就是利用 WinDriver 所產生的一些基本 Function(像是傳 data 或是收 data),針對你的應用以 Win32 compiler(像是 BCB、VC) 來寫一個應用程式,讓 User 透過應用程式來使用我們的硬體做 file 的加/解密動作。

我們的 Driver 最主要是用 WinDriver 對我們 USB 所開出來的 5 個 endpoint 所產生的五個 pipe function code:

A. USB_LocateAndOpenDevice( ) B. USB_WritePipe02( )

C. USB_WritePipe03( ) D. USB_ReadPipe82( )

A function- 是 用 來 找 到 我 們 USB device 並 且 取 USB device 的 handle。

B function-是用來對 Pipe02 做寫入的動作,Pipe02 是用來做加密的管 道。

C function-是用來對 Pipe03 做寫入的動作,Pipe03 是用來做解密的管 道。

D function-是用來做讀資料的動作,不管是加密後的資料或是解密後 的資料。

四. 產品應用

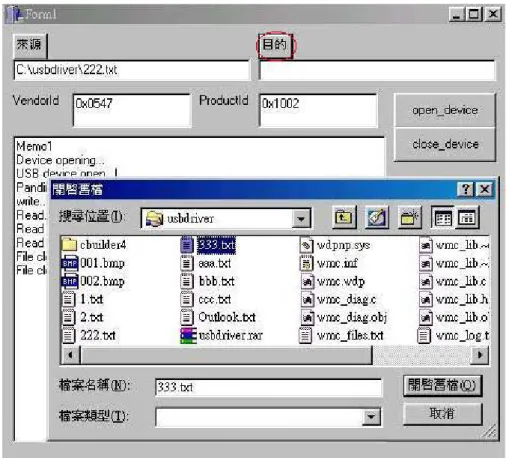

我們做出來的產品目前只是個雛型,而我們的目標是希望到時能 下線實做晶片,並且包裝成和鑰匙一樣大小,如此一來攜帶方便,做 到保密的機動性,不管身在何處都可方便的使用。 在這裡針對我們所寫的應用加以介紹,而使用者可利用我們的 API 自行開發出不同的應用: 圖 4.1 產品操作介面上圖就是我們應用程式的操作介面,首先必須先開啟我們的 USB device,當你按下按鈕”來源”時,會出現一個視窗讓你去瀏覽、選 擇你硬碟裡的檔案,你所選到的檔案路徑會放到”來源”下面的空白 欄位,而按下按鈕”目的”時,你所選到的檔案路徑會放到”目的” 下面的空白欄位,選好兩個欄位後,按下”加密”按鈕,就會把”來 源”欄位裡的檔案,透過我們的 USB device 加密後,存到”目的” 欄位下的檔案,若是按下”解密”的按鈕,那就是把”來源”欄位裡 的檔案,透過我們 USB device 做解密存到”目的”欄位下的檔案。 之後我們可以比對原始檔案與解密後的檔案是否相同,結束之後要記 得將我們的 USB device 關閉。

USB device 操作範例

圖 4.2 選擇來源檔與目的檔

圖 4.4 選擇要解密之來源檔與解密後之目的檔

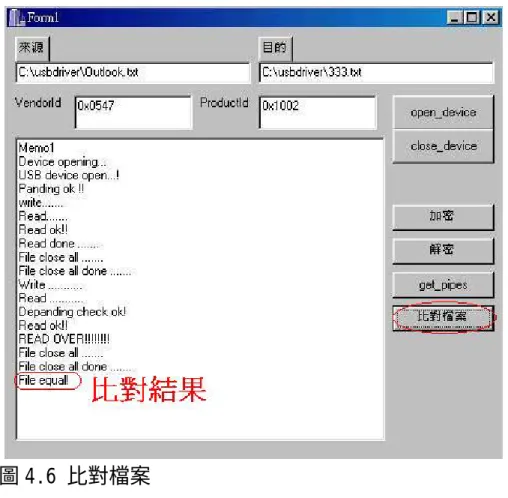

圖 4.6 比對檔案

而在下面的這張圖中共有三個視窗,其表示的意義為:第一個視 窗為加密的明文,而第二個視窗表示為加密的密文,也是解密的明 文,第三個視窗則為解密的密文。所以我們可以看到第一個文章和最 後一篇文章的內容相同,而且其它人無法從密文得到任何可用的訊 息,這個就是我們所做的一個示範,當然 DES 並不只有這個應用,使 用者也可自行開發。 圖 4.8 明/密文檔比較

五、VHDL介紹

VHDL的發展

在 1970 年代至 1980 年代期間,美國國防部,為方便管理有關武 器承包商的電子電路技術文件,使其遵循統一的設計描述介面,以便 在將來若有新技術推出後,仍能重複再使用原設計,因而發展了名為 VHSIC (Very High Speed Integrated Circuit)的計劃。可惜的是, 由於當時的文件格式,僅能以 gate level 的方式描述電路,一旦面 對數萬邏輯閘以上的設計時,那是件複雜且困難的事情。於是,一種 改良的電路描述方式—“VHSIC 硬體描述語言”(VHSIC Hardware Description Language)便在 1982 年正式誕生;這也就是習稱的 VHDL。其後,並於 1986 被 「國際電機電子工程協會」 (International Electrical& Electronic Engineering, IEEE)收納為其標準之一; 文件編號為 IEEE standard 1076。 VHDL 電路設計語言規範的目的,即是要提供一個高階且快速的設 計工具,含蓋了電路的描述,電路之合成與電路之模擬等三大電路設 計工作。由於 VHDL 電路設計語言所能函蓋的範圍相當廣,它能適應 於各種不同階層的設計工程師的需求。從 ASIC 的設計到 PCB 系統的 設計,VHDL 電路描述語言,均能派上用場。所以 VHDL 電路設計語言

實為硬體設計工程師之必備工具。然而類比電路( Analog Circuit) 與混合訊號(mixed)電路的規範,亦是 VHDL 電路描述語言所欲涵蓋 的,然而這些部份的 VHDL 規範之標準仍在制定中。

VHDL的優點

選用 VHDL 電路設計語言當作電路設計的工具,可以由下面的幾 點來分別予以說明: (1) 功能強大: VHDL 包含了電路描述,電路合成與電路模擬等功能。就垂直整 合而言,自 ASIC 設計到電路板設計,甚或大型系統之設計,VHDL 電路設計語言均能派上用場。 (2) 設計靈活( Flexibility ): VHDL 電路設計語言,將電子電路的設計方式,改變成以行為化 描述的方式來設計。因此具有設計快速、更改及維護容易、犯錯機率 降低及除錯容易等優點。除了這些之外,由於 VHDL 具有可流通性, 故設計的內容,易為其他人所了解而採用。而使得 VHDL 的設計整 合性極佳。加之以模組化電路設計的趨勢,許多由 VHDL 所設計的 模組電路,更易於做重新再組合的動作,使得設計的快速性產生了加成的效果。

(3) 各種不同的描述風格( Design Description Style ):

VHDL 電路設計語言,提供許多不同的描述風格,來適應大小, 複雜性不同的電路設計。如:一個 2 bits 的比較器可分別用連線關係 ( Netlist ):

u1:XOR2 PORT MAP ( a ( 0 ),b ( 0 ),x ( 0 ) ); u2:XOR2 PORT MAP ( a ( 1 ),b ( 1 ),x ( 1 ) ); u:NOR2 PORT MAP ( x ( 0 ),x ( 1 ),eq ); 順序性敘述(sequential statements): if a = b then eq <= ‘1’; else eq <= ‘0’; end if; 共時行敘述(concurrent statements): eq<=’1’WHEN a=b ELSE ‘0’;

布林方程式(booleen equaton):

eq <= (a(0) XOR b(0) NOR (a(1) XOR b(1));

(4) 可流通性或可攜性( Portability ):

攜性能力,可以使你的設計可以利用不同編譯軟體來編譯,可以利用 不同模擬器來模擬以及可以適用於任何種類的邏輯元件與半導體製 程技術。

VHDL重要詞彙

單體( ENTITY): 單體是一個設計中最基本的一部份,也是不可缺少的一部份,在 單體的這一部分中,通常描述電路設計中的輸出、入訊號的宣告。而 ENTITY 也是 VHDL 的保留字。 架構(ARCHITECTURE ): 架構是描述電路行為特性的主要部份。如以電路圖的設計方法論 之,架構部分相當於電路圖設計中的 schematics,用來描述各個元件 間的互相連結情形。而 VHDL 語言中的描述輸出入埠的單體就相當 於電路圖中的 symbols。套件( PACKAGE ): 在 VHDL 語言的設計中,可以將一些次程式(subprograms)、程序 ( procedure )及一些常用的資料型態,放在一個套件中,則此套件即形 成了一個工具箱,如果在設計中有應用到套件中的程式時,只要將此 套件名稱寫在程式的最開頭部份,則在程式中的任何地方,均可以使 用此套件中所定義的物件或次程式。VHDL 語言中的套件程式部份可 以單獨形成一個檔案並可以分別單獨來編譯,以利整合設計的進行。 屬性( ATTRIBUTE ): 用來描述各種資料物件( data object )的特性,就稱為該資料物件 的屬性,例如陣列的位元數,訊號的變化…等。 傳遞( GENERIC ): 在 VHDL 的語法上時,表用來傳遞一些特性參數給單體電路使 用。例如可以將 NAND 閘的上升時間與下降時間宣告為 NAND 電路 單體的 Generic,如此當我們在使用 NAND 這一個模組時,即可以隨 時來設定它的上升時間與下降時間。

資料型態( DATA TYPES ): VHDL 語言中所使用的任何的資料物件,如常數、變數、訊號…等, 均要定義其資料型別之後才能使用。而且操作與運算中,各個資料物 件的資料型別也必須相容,才能合乎 VHDL 語言中的語法。 次程式( SUB-PROGRAMS ): 在 VHDL 語言中,有兩種次程式來使主程式的結構更加的簡潔清楚, 它們是函式( FUNCTIONS ) 與程序( PROCEDURES ),函式使用在其 只有一個輸出變數時,而程序則無此限制。 行程( PROCESS ): Process 為 VHDL 語言中,用來描述行為化電路描述的最基本單元, 而在 process 內所寫的程式,是有先後次序關係的,我們稱這些為 sequential statements。 構形( CONFIGURATIONS ): 在 VHDL 語言中,可以容許一個單體電路內能有一個以上的構成情 形。而程式設計者可以使用 CONFIGURATION 指令來說明該單體電 路的構造情形。

六、USB 簡介

USB 一共分兩個制式:1.1 版本和 2.0 版本。USB 1.1 於 1998 年 9 月根據 USB1.0 (1996 年 1 月)規格修訂而成。當初以所要設計 USB 有 8 個目的:

1. 要容易使用 (Plug & Play)

2. 低成本,速度為 12Mb/s 或以下 3. 支援即時聲音和影像資料傳送 4. 通訊協定要有彈性,可以同時混合多款傳送模式 5. 可配合不同 PC 電腦組合 6. 可用於多款不同類型的產品 7. 可支援未來新制式 8. 可嵌入產品之內 USB 2.0 是 USB 1.1 的伸延,將資料的吞吐量由原本最高的 12Mb/s (1.5MB/s) 爆 45 倍至 480Mb/s (60MB/s) 。USB 2.0 可以同時兼容 USB 1.1,不過速度當然 "Downgrade" 到 USB 1.1 的規格。

USB 的傳輸類型

(1) 控制型傳輸(Control Transfer) 屬於雙向傳輸,用來支援介於主機與裝置之間的配置,命令或狀 態的通訊。控制型傳輸包含了三種的控制傳輸型態:控制讀取、控制 寫入以及無資料控制。 (2) 中斷型傳輸(Interrupt Transfer) 屬於單向傳輸並且僅從裝置輸入到 PC 主機,作 IN 的傳送模式, (但在規格 1.1 及 2.0 中,已定為雙向傳輸,增加了 OUT 的傳送模式) 。 而由於 USB 不支援硬體的中斷,所以必須靠 PC 主機以週期性的方式 加以輪詢,以便知道是否有裝置需要傳送資料給 PC。 (3) 巨量型傳輸(Bulk Transfer) 屬於單向或雙向的傳輸,顧名思意,這類型的傳輸是用來傳送大 量的資料。雖然這些大量的資料須準確的傳輸,但是卻並無傳輸速度 上的限制(即沒有固定的傳輸速率) 。 (4) 即時型傳輸(Isochronous Transfer) 可以是單向或雙向的傳輸。此種傳輸需要維持一定的傳輸速度, 且可以默許錯誤的發生。它採用了事先與 PC 協定好的固定頻寬,以 確保發送端與接收端的速度互相吻合。為何選用 USB 傳輸介面

USB 為 Universal Series Bus(萬用串列匯流埠)的縮寫,是一種 全球通用的資訊產品串列式標準界面,目前主要用於 PC 與其周邊設 備之連接。USB 除支援慢速的資料傳輸(如滑鼠、鍵盤、遊戲搖桿 等),也支援快速的數位壓縮影音資訊傳輸。 由於一般消費者抱怨 PC 與其週邊裝備,連接方式愈來愈複雜且 困難,90 年代初期由 PC 大廠倡議制訂一種以 PC 為主軸之標準界面, 以便簡化現有 PC 與周邊設備多種連接界面問題。

USB 目前版本標準定義了傳輸速度有 480 Mbps(高速,High Speed)、 12 Mbps(全速,Full Speed)及 1.5Mbps(低速,Low Speed)三種,標準 USB 線纜組(A to B Cable Assembly)的 Type A 連接器固定連接 Host (主機)端、Type B 連接器則連至 Device (裝備)端,構成一主從架構連 結。透過 USB 集線器(Hub)和電腦內部的根集線器(Root Hub)則可以 形成一個星狀網路,並且隨著集線器的數量增加而使得網路的規模隨 之增大,理論上 USB 可以允許多達 127 個周邊設備串接到一個外接 USB 埠上。 USB 目標在提供一種以消費者角度思考之簡單便宜的標準界 面,利用一條傳輸線纜串接各類週邊設備,解決目前 PC 後面一大堆 線亂繞的困境,且利用界面通訊協定自動偵測安裝,能夠不重新開機

或複雜設定安裝的狀態下,隨時安插使用各式的週邊設備。 總結來說,USB 之便利性有: (1) 即插即用(Plug-and-Play)的特性並具自動偵測的功能,所以無需考 慮到系統資源是否有衝突的情況。 (2) 可擴充至 127 個外部裝置,足以因應各種類型的裝置同時連接的 困擾。

(3) 熱插拔(Hot Attach & Detch) ,也就是週邊裝置的插入與拔取無須 再關閉電源,節省了關機再裝設的時間。

(4) 安裝簡易,無需拆卸 PC 機殼,使用更為簡易。

七. DES 加/解密介紹

DES 演算法

DES(data encryption standard)說明:

DES(Data Encryption Standard ) 是在 1970 年代中期由美國 IBM 公司發展出來的,且被美國國家標準局公佈為資料加密標準的一種區 塊加密法(Block Cipher)。直到今日,儘管 DES 己歷經歷了二三十個 年頭,但在已知的文獻中還是無法完全地,徹底地把 DES 給破解掉。 換句話說,DES 這套加密方法至今仍被公認是很安全的。 DES 屬於區塊加密法,而區塊加密法就是對一定大小的明文或密 文來做加密或解密動作。而在 DES 這個加密系統中其每次加密或解密 的區塊大小均為 64 位元,所以 DES 沒有密文擴充的問題。就一般資 料而言,無論明文或密文其資料大小通常都大於 64 位元。這是我們 只要將明/密文中每 64 位完當成一個區塊而加以切割,再對每一個區 塊加密或解密即可。但是對明文做區塊切割時,可能最後一個區塊大 小會小於 64 位元。此時,我們要在此區塊之後附加”0”位元,移到 此區大小成為 64 位元為止。 另一方面,DES 所用的加密或解密金匙(Key)64 位元大小,但因 其中有個位元是用來做錯誤更正(Error Correction),所以 64 位元 中真是金匙效用的只有 56 位元。而 DES 加密與解密所用的演算法除 了子金匙的順序不同之外,其他的部份則是完全相同的。

DES 的細節說明:

圖 7.1 是 DES 全部 16 個回合(Round)的加/解密架構圖,其最上 方的 64 位元輸入區塊資料,可能是明文,也可能是密文,端視使用 者要做加密或解密而定。而加密與解密的不同處,只在於圖 7.1 最右 邊的 16 個子金匙之使用順序不同,加密之子金匙順序為 K1 K2 K3 K4……K16,而解密之子金匙正好相反,為 K16 K15 K14……K1。 首先,加/解密輸入區塊依表 7.2 之表之重排次序,進行初始排 列動作,攪亂資料之原來順序後,再分為 L0 與 R0 兩個 32 位元的區 塊。接著,R0 與第一個子金匙 K1 一同經過 f 函數運算,而得到的 32 位元輸出再與 L0 做位元間的互斥或(XOR)運算。其結果成為下一個回 合的 R1,R0 則成為下一回合的 L1,如此連續運作 16 回合。圖 7.1 DES 加/解密架構圖

我們可以下列兩個式子來表示其運算過程:

Ri = Li-1 xor f(Ri-1 , Ki )

Li = Ri-1 , i = 1,2,3,…16

而 最 後 所 得 到 的 R16 與 L16 不 須 再 互 換 , 直 接 連 結 (Concatenation) 成 64 位元的區塊,再依表 7.3 之重排依序做一終 結排列動作,得到 64 位元的輸出。

表 7.3

子金匙

表 7.4、7.5、7.6、7.7 是整個子金匙產生的依據。子金匙產生 過程中的輸入,為使用者所持有的 64 位元母金匙。而加密或解密時, 使用者先將母金匙輸入至子金匙產生流程中即可。首先經過金匙排列 (如表 7.6),將母金匙的 8 個除錯位元剔除掉,而留下真正的 56 位 元母金匙。接著,兵分兩路為兩個 28 位元的區塊 C0 及 D0,再分割 經過一個左旋函數(如表 7.5),得到 C1 與 D1,連結成 56 位元資料, 再依金匙排列 B(如表 7.7) 做重排動作,便可輸出子金匙 K1,而 K2 至 K16 之做法依此類推。其中較需注意的是,金匙排列到 A 的輸入為 64 位元,輸出為 56 位元;而金匙排列 B 則分別為 56 位元與 48 位元, 這些情況可由表 7.4,表 7.6 及表 7.7 中很清楚地看出來。圖 7.4

表 7.6 表 7.7

f 函數

f 函數是整個 DES 加密法中最重要的部份,而其中的重點又在替 換盒(substitution boxes)上。圖 7.8 是 f 函數的計算過程架構。F 函數有兩個輸入資料:一為 32 位元的中間密文 R,另一部份是 48 位 元的子金匙 K。32 位元的中間密文 R 先經過擴增排列 E(如表 5.9)後, 即擴增至 48 位元。接著,再與另一輸入資料,即 48 位元的子金匙 K 做互斥或 XOR 運算。所得的結果,再平均分配給 8 給替換盒 S1,S2, S3…S8。圖 7.8 f 函數計算過程架構

替換盒

每個替換盒的輸出與輸入分別為 6 位元與 4 位元。所以經過 8 個 替換盒的替換之後,總輸出資料則成 4 * 8=32 位元。最後再經匯減 排列 P(如表 7.10)縮減成 32 位元的結果,這也就是 f 函數的輸出了。 而以上 8 個神祕的替換盒是如何運作的,請參照表 7.11 和 7.12。 替換盒的替換方式很有意思,它把 6 位元輸入最左與最右 2 個位元取 出來當表 7.11 的列數,所以表 7.11 中每個替換盒共有 2 4 =16 行。 舉 例 如 下 : 假 設 第 一 個 替 換 盒 S1 的 6 個 輸 入 位 元 資 料 為 數 列 (011001)2,其中右邊為低位元。則我們就選 S1 的第(01)2 =1 列及 第(1100)2 = 12 行之內容,也就是 9=(1001)2 為輸出資料。 表 7.10八、專題經驗

1. 以 WinDriver 產生的 C++ Builder project,因為是自動產生, 並無操作介面(form),所以執行後會有操作上的問題。需要另外再產 生一個 new project 後,設計 Form 再把所需的內容函式 copy 過來應 用即可。

2. WMC_HANDLE TForm1::WMC_LocateAndOpenDevice(BOOL fUseDefault),此函式為開啟 device 所必須,不然無法 handle 此 USB device。

3. 因為 project 有太多的共用變數,所以要另外寫一個額外定義的 function.h 檔,include 進去 project 內。

4. 在使用 USB 發展板時,須先將所需的韌體 download 到此發展版 中,再來要進行韌體的測試,以確認韌體 download 無誤,才可到欲 進行 Demo 的機器上進行 Driver 的產生、編輯和測試的動作。 5. Memo 的顯示問題,由於需要將整個流程中的訊息顯示出來,memo 的顯示顯的格外重要,而其格式須將其強制轉型(IntToStr),才不會 有 error 的發生。另外 memo 顯示訊息的 size 有一定的限制,所以太 多無謂的訊息會導致程式無法順利執行完畢,即使程式是正確無誤 的。

6. 在操作 USB device 測試時,因為 debug 未完全成功,使得錯誤一 再的產生,而重複的測試也使得測試檔案所讀取的資料,佔用相當大 的記憶體,結果每次測試沒幾次就會當機,而記憶體釋放的技巧,在 這次專題實作上,運用的恰到好處。 7. 為了使此專題能夠在別台機器上 Demo,測試執行檔是必然的,測 試之後得知,安裝的機器必須安裝此 USB device 之驅動程式,也必 須安裝 WinDriver 軟體,才可成功的進行 Demo。

九、心得

By 王銘清

這次的專題實驗總算也完成了,總覺得這次專題會完成是半推半 就出來的,從暑假到現在,大部分的時間是花在做測試,並非花在此 次專題的研究方向,而其目的,大概是為了讓我們摸熟架構吧。老實 說,老師為何要選這個題目” USB 介面之加解密卡製作”,作為我 們的畢業專題,我們也是毫無頭緒,因為對於自己的能力到達哪個地 步,以及各題目的大約內容都無所了解,只是在自己的直覺上認為專 題這門科目就有如在過去幾年所得到的知識,並利用得到的知識做出 實際的東西。 一開始,助教給了我們一些相關的書籍資料,當然就是要我們在 短時間內,能 K 懂多少就 K 懂多少,每次 Meeting 之後也會叫我們做 一些相關的測試,從韌體的修改到 Driver 的撰寫,都是從測試做起, 再慢慢轉向實驗的目的。但由於我們的時間分配不當,使我們這組專 題的整體進度到開學時還沒有任何的頭緒,原本做了要放棄改到下學 期發表的決定,但這時我們又趕了一點進度,於是在與老師和助教溝 通之後,決定趕在這學期發表前完成。 之後,在 Driver 撰寫的部分進行蠻順利的,遇到的問題也都在的時候,曾經還一度為了 VHDL 的撰寫問題停頓了一段時間,後來也 算順利的完成了,只不過在 VHDL 這部分上,的確遭遇到蠻多的小問 題。因為使用的軟體是 ALTERA Quartus II 2.0,其使用方法大部分 與原本較常使用的 MAX+plus II 10.1 相似,但是在燒錄的部分,pin 腳的對應方式不同,必須用 assign 的方式對應 pin 腳,且在 assign 之前必須已經 compiler 成功才不會出錯,但卻經常把操作的順序顛 倒,使得問題時常不由而生,連錯誤都不知道錯在哪,嚴重影響 debug 的速度。 這次專題實驗的經驗,可以說算是相當豐富,USB 從一竅不通, 到現在知道他的架構以及傳輸模式,對於其傳輸也有了大致上的認 識,如何宣告交易,交易如何開始、結束,在傳輸中,資料是處於何 種狀態,系統訊號的意義。還有就是,原來 Driver 的產生並不困難, 困難的是如何去操控它,以達到你所需要的功能。 另外就是,這學期因為忙著趕畢業專題的進度,才讓我有充分利 用到空閒時間的感覺,讓我比較懂得如何去分配時間,能有較多的時 間去應付課業,也能有足夠的時間來研討專題。製作專題的過程中有 一點是很重要的,就是要常跟組員討論溝通,因為有些東西或許兩個 人都不懂,但各有各的想法,這時候如果能提出來互相討論,意見互 相溝通一下,往往能得到另外一種的新想法。所以說互動跟彼此有沒

有心想要認真去做非常重要。因為我們的共同研討時間幾乎只有晚 上,使得彼此時常因為時間的無法配合,而無法一起研討專題的內 容,經常只有其中一人與助教研討,所以雙方面的協調在此次專題顯 的很重要。

By 林國棟

呼!終於,在經過了幾個月時間的摸索、一次又一次的嘗試失敗 後,我們的專題總算是如期的出爐了,這其中真是幾經波折阿。 第一次接觸 USB 發展板,第一次寫 DRIVER,第一次使用 WinDriver、Cypress、Quartus…等軟體;就因為是那麼多的第一次, 所以剛開始做這個專題的時候總是一直碰壁,像 WinDriver 產生出來 的函式如何使用,及程式碼的編輯和重新學習軟體所提供的特殊功能 等工作,都是下了一番功夫後才漸漸熟悉。另外硬體部分也是須先花 一段時間了解其結構後,才算真正開始了這個專題的實作。 一點一點的累積進度,甚至於遇到難以解決的問題,而停擺了三 四天的情形週而復始著。直到現在,完成作品後的感覺很興奮也很充 實;因為我們學到了如何去操作使用 USB 產品,甚至更改其 DRIVER 等技術,更明白了 USB 的方便性及實用性。另外,對於 DES 演算法 的了解也可以說是這個專題所贈與的附屬產物吧!總而言之,專題完 成了,心中的大石也落下了,肚子裡也更多了一些料了,這大概是每 個同學做完專題後的心聲了吧!我也不例外。 最後,當然了,這個專題之所以能完成不能不感激和我同組的組 員,以及帶著我們一起做專題的學長,沒有他們的幫助和貢獻心力的話,一個人一定是弄不出東西來的;所以做完專題的同時,心中除了 喜悅,也抱持了感謝的心情,沒有大家的努力也就沒有這個專題了。

十、參考資料

一. 近代密碼學及其應用-賴溪松、韓亮、張真誠著 1999 松崗出版 二. USB 系統架構-陳振榮 譯 1999 碁峰資訊出版

三. USB 週邊裝置設計與應用-許永和編著 1998 全華出版 四. 使用 VHDL 電路設計語言之數位電路設計-林傳生 2000 五. PCI 系統架構-Tom Shanley & Don Anderson 2000

六 . http://www.ccisa.org.tw/ 文 章 收 錄 / 資 安 會 論 文 / 第 12 屆 /ISC2002/ISC2002 論文集/6PDF_Session3/3C/3ISC073.pdf 七. http://www.vhdl-online.de/~vhdl/