國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

光通訊接收端轉阻放大器之設計與製作

Design and Implementation of Transimpedance Amplifier for

Optical Communication Receiver

研 究 生:盧建君

指導教授:蔡嘉明 博士

光通訊接收端轉阻放大器之設計與製作

Design and Implementation of Transimpedance Amplifier

for Optical Communication Receiver

研 究 生:盧建君 Student:Jiann-Jiun Lu

指導教授:蔡嘉明 博士 Advisor:Dr. Chia-Ming Tsai

國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of Master of Science

in

Electronics Engineering December 2007

Hsinchu, Taiwan, Republic of China

光通訊接收端轉阻放大器之設計與製作

學生 : 盧建君 指導教授 : 蔡嘉明 博士

國立交通大學

電子工程學系 電子研究所碩士班

摘要

對於光纖系統而言,在訊號輸入端由檢光二極體元件和靜電放電防護電路所造成的電容 負載效應是光接收轉阻放大器設計上所面臨的最主要問題,其對頻寬與雜訊等重要接收 性能有關鍵性的影響。為求解決此問題,我們同時採用自我補償架構與負阻抗補償技 術,前者著重於降低輸入端之電容負載效應,後者則透過控制輸出端之阻抗特性來提高 放大器之電壓增益,進而降低其等效輸入阻抗而達到改善頻寬的目的,除此之外,設計 上再搭配適當的頻寬延伸技術,包含直流位準偏移技術與電感補償技術,可以進一步的 提昇電路效能。藉由0.18 微米 CMOS 製程與寄生電容約 0.72pF 的檢光二極體實現一個 5Gb/s 的光接收轉阻放大器,所量測到的結果顯示,當加入 0.5pF 寄生電容的靜電防護 電路時,使用1.8 伏特供應電壓的轉阻放大器靈敏度只從-17.6dBm 下降至-17.2dBm,頻 寬也只從3GHz 下降至 2.7GHz,驗證了此設計可達到高輸入電容容忍度。在 10Gb/s 的 轉阻放大器設計中,透過雙級差動式架構來提升放大器之電壓增益與供應電源雜訊的抵 抗能力,設計上也採用直流位準偏移與電感補償等技術來提升頻寬。最後,藉由 90 奈 米 CMOS 製程與寄生電容約 0.15pF 的檢光二極體實現一個 10Gb/s 的光接收轉阻放大 器,量測結果顯示,使用1.2 伏特供應電壓的轉阻放大器具有 62dBΩ 的增益、8GHz 的 頻寬與-16.3dBm 的靈敏度。Design and Implementation of Transimpedance Amplifier for

Optical Communication Receiver

Student : Jiann-Jiun Lu Advisor : Dr. Chia-Ming Tsai

Department of Electronics Engineering

National Chiao Tung University

Abstract

The input capacitances due to the photodiode and the ESD protection circuit cause serious degradation on both the receiver bandwidth and the sensitivity in optical receiver. To solve this problem, we combine the self-compensated architecture and the NIC technology. The former significantly reduces the loading effect caused by the input capacitances, and the latter effectively increases the voltage gain of the amplifier by controlling the output impedance of the amplifier. Moreover, the design combined with appropriate bandwidth enhancement techniques, including shunt peaking and DC offset voltage technique, can boost the performance. A 5Gb/s transimpedance amplifier is implemented by 0.18um CMOS technology at 1.8V with 0.72pF photodiode capacitance. Due to the 0.5pF ESD protection circuit, the measurement results show slightly degraded sensitivity from -17.6dBm to -17.2dBm. The bandwidth is also slightly degraded from 3GHz to 2.7GHz. A 10Gb/s transimpedance amplifier is implemented by 90nm CMOS technology at 1.2V with 0.15pF photodiode capacitance, we use a two-stage differential architecture to increase the voltage gain and improve power noise rejection. Shunt peaking and DC offset voltage technique is

also employed to enhance BW. The measurement results show that the gain of TIA is 62dBΩ, -3dB bandwidth is 8GHz and sensitivity of -16.3dBm.

誌謝

在碩士的求學生涯中,能夠完成這篇論文,心中充滿著許多感激。首先我要對我的 論文指導教授蔡嘉明博士致上最誠摯的謝意與敬意。每當我在學習與研究的過程中遇到 瓶頸時,都能適時的引導我,並且指示正確的學習與研究方向,這不僅讓我在專業的知 識與素養獲得提升,更重要的是,也理解到做研究時所應有的正確態度與方法。同時也 感謝吳介琮教授、黃弘一教授和黃立仁博士等口試委員們來參加口試,以及給予寶貴的 意見使我的論文能夠更完整。 接著,我要感謝實驗室的好伙伴宜興、茂成和向益,一起努力做研究和量測,讓我 能互相勉勵求進步。我還要感謝我有一群好朋友致良、漢健、康康、俊傑、弘章、嘉儀、 國光、Spice、俊男、阿樸、俊宜,能和我ㄧ起渡過這美好與辛苦的碩士生涯,此外,我 還要感謝同一個實驗室的庭禎學長、志龍學長、小朱學長、小胖學長和麗蓉學姊,給予 實驗室設備和研究上的幫助與建議。也要感謝juju和秉威學弟的支持與相伴。當然,最 要感謝一直支持我的家人與昱伶,每當我隻身在外求學感到孤單時,你們是我最大的精 神支柱與避風港。 最後僅將我的論文獻給我最摯愛的家人與朋友。盧建君

國立交通大學

中華民國九十六年十二月

目錄

中文摘要 ii

英文摘要 iii

誌謝 iv

表目錄 vii

圖目錄 viii

第一章 緒論... 1

1.1 研究動機 ... 1 1.2 論文組織 ... 1第二章 光纖通訊接收端系統與設計考量 ... 3

2.1 系統概觀 ... 3 2.2 轉阻放大器基本設計考量 ... 4 2.2.1 增益 ... 4 2.2.2 頻寬 ... 5 2.2.3 雜訊 ... 6第三章 具高輸入電容容忍度之光接收轉阻放大器 ... 10

3.1 簡介 ... 10 3.2 架構 ... 10 3.2.1 自我補償架構 ... 10 3.2.2 負阻抗與電感補償技術 ... 13 3.2.3 系統架構 ... 13 3.3 電路設計 ... 15 3.3.1 電感與負電容補償設計 ... 15 3.3.2 轉阻放大器核心電路 ... 18 3.3.3 負阻抗補償之增益緩衝器 ... 21 3.4 模擬和佈局 ... 22 3.5 量測結果 ... 29 3.5.1 量測環境 ... 29 3.5.2 量測結果 ... 30第四章 90 奈米 CMOS 之 10Gb/s 光接收轉阻放大器 .... 36

4.1 簡介 ... 36 4.2 架構 ... 36 4.2.1 單端式與差動式架構 ... 36 4.2.2 系統架構 ... 39 4.3 電路設計 ... 41 4.3.1 偽差動式輸入架構 ... 41 4.3.2 雙級差動轉阻放大器 ... 43 4.3.3 主動式回授輸出緩衝器 ... 45 4.4 模擬和佈局 ... 46 4.5 量測結果 ... 49第五章 結論與未來工作 ... 53

參考文獻... 54

附錄... 56

簡歷... 64

表目錄

表 1. 1 各種通訊方式比較表 ...2 表 3. 1 預定規格與模擬效能比較 ...28 表 3. 2 量測效能總結與比較 ...35 表 3. 3 晶片效能比較 ...35 表 4. 1 預定規格與模擬效能比較 ...48 表 4. 2 量測效能總結與比較 ...52 表 4. 3 晶片效能比較 ...52圖目錄

圖 2. 1 光通訊接收端電路區塊圖 ...3 圖 2. 2 轉阻放大器 ...5 圖 2. 3 共閘極轉阻放大器 ...6 圖 2. 4 多級串連轉阻放大器 ...6 圖 2. 5 不同光功率的輸入錯誤率碼曲線例子 ...7 圖 2. 6 加入雜訊源之轉阻放大器 ...7 圖 2. 7 使用電感衰減技術之共閘極轉阻放大器 ...8 圖 2. 8 電感衰減技術之設計概念 ...9 圖 2. 9 電感衰減技術之模擬 ...9 圖 3. 1 自我補償電路 ... 11 圖 3. 2 自我補償電路小信號模型 ... 11 圖 3. 3 (a)v2端波德圖 (b)v3端波德圖 (c)雙端波德圖...12 圖 3. 4 負阻抗補償之轉阻放大器 ...13 圖 3. 5 系統架構 ...14 圖 3. 6 電感補償之放大器 ...15 圖 3. 7 電感補償之頻率響應 ...16 圖 3. 8 負電容補償之放大器 ...16 圖 3. 9 不同傳導係數之頻率響應 ...17 圖 3. 10 不同補償電容之頻率響應 ...17 圖 3. 11 轉阻放大器核心電路 ...18 圖 3. 12 負電阻之電流源電路 ...20 圖 3. 13 負電容之電流源電路 ...20 圖 3. 14 比較器電路 ...21 圖 3. 15 增益級緩衝器電路 ...21 圖 3. 16 輸出級電路 ...22 圖 3. 17 bond-wire 模擬考量...22 圖 3. 18 轉阻放大器頻率響應模擬 ...23 圖 3. 19 (a)無補償的眼圖模擬 (b)有負阻抗的眼圖模擬(b)有負阻抗與電感的眼圖模擬 ... 23 圖 3. 20 轉阻放大器 LC 串聯的交流耦合之頻率響應模擬...23 圖 3. 21 (a)電容交流偶合的眼圖模擬 (b) 電感電容串聯之交流偶合的眼圖模擬 ...23 圖 3. 22 增益級電路之頻率響應模擬 ...24 圖 3. 23 (a)無主動式補償的眼圖模擬 (b)有主動式補償的眼圖模擬...24 圖 3. 24 SS 和溫度 80°C 的頻率響應模擬 ...25 圖 3. 25 (a)無電流追蹤技術的眼圖模擬 (b)有電流追蹤技術的眼圖模擬...25圖 3. 26 FF 和溫度 0°C 的頻率響應模擬...25

圖 3. 27 (a)無電流追蹤技術的眼圖模擬 (b)有電流追蹤技術的眼圖模擬...26

圖 3. 28 (a)Rf=2k 和沒有 ESD 電路的眼圖模擬(b)Rf=2k 和有 ESD 電路的眼圖模擬 ..26

圖 3. 29 (a)Rf=450 和沒有 ESD 電路的眼圖模擬(b) Rf=450 和有 ESD 電路的眼圖模擬 ... 26 圖 3. 30 佈局平面圖 ...27 圖 3. 31 四層堆疊式電感立體圖 ...27 圖 3. 32 (a)晶片顯微圖(b)晶片與檢光二極體整合顯微圖...28 圖 3. 33 晶片頻率響應量測安裝環境 ...29 圖 3. 34 晶片眼圖和錯誤碼率量測安裝環境 ...30 圖 3. 35 頻率響應量測結果 ...30 圖 3. 36 輸入訊號功率-16dBm、5GHz 和有靜電防護電路的眼圖...31 圖 3. 37 輸入訊號功率-16dBm、5GHz 和無靜電防護電路的眼圖...31 圖 3. 38 輸入訊號功率+0dBm、5GHz 和有靜電防護電路的眼圖...32 圖 3. 39 輸入訊號功率+0dBm、5GHz 和無靜電防護電路的眼圖...32 圖 3. 40 位元錯誤率曲線圖 ...33 圖 3. 41 輸出雜訊功率分佈圖 ...34 圖 3. 42 單端輸出之 Gaussian-shaped Histogram...34 圖 4. 1 (a)單級放大器(b)雙級串聯放大器(c)三級串聯放大器 ...38 圖 4. 2 最大電壓增益曲線圖 ...38 圖 4. 3 雙級串聯差動式轉阻放大器 ...38 圖 4. 4 系統架構 ...39 圖 4. 5 偽差動式轉阻放大器 ...41 圖 4. 6 極、零點分佈曲線圖 ...42 圖 4. 7 頻率響應模擬(當 C/Cp = 0.1,1,100) ...43 圖 4. 8 頻率響應模擬(當 C/Cp = 0.8,1,1.2) ...43 圖 4. 9 雙級差動轉阻放大器電路 ...44 圖 4. 10 比較器電路 ...44 圖 4. 11 輸出緩衝器電路 ...45 圖 4. 12 bond-wire 效應模擬...46 圖 4. 13 轉阻放大器頻率響應模擬 ...46 圖 4. 14 (a) LBW=1nH 的眼圖 (b) LBW=2nH 的眼圖 (c) LBW=3nH 的眼圖 ... 47

圖 4. 15 (a) 10.0Gb/s 和 10uApp 的眼圖模擬(b) 10.0Gb/s 和 1.5mApp 的眼圖模擬 ...47

圖 4. 16 (a) 13.3Gb/s 和 10uApp 的眼圖模擬(b) 13.3Gb/s 和 1.5mApp 的眼圖模擬 ...47

圖 4. 17 佈局平面圖 ...48

圖 4. 18 (a) 晶片顯微圖(b)晶片與檢光二極體整合之顯微圖...48

圖 4. 20 輸入訊號功率-15dBm 和 10.0GHz 的眼圖...49 圖 4. 21 輸入訊號功率-14dBm 和 13.5GHz 的眼圖...50 圖 4. 22 輸入訊號功率+0dBm 和 10.0GHz 的眼圖...50 圖 4. 23 輸入訊號功率+0dBm 和 13.5GHz 的眼圖...50 圖 4. 24 位元錯誤率曲線圖 ...51 圖 4. 25 單端輸出之 Gaussian-shaped Histogram...51

第一章

緒論

1.1 研究動機

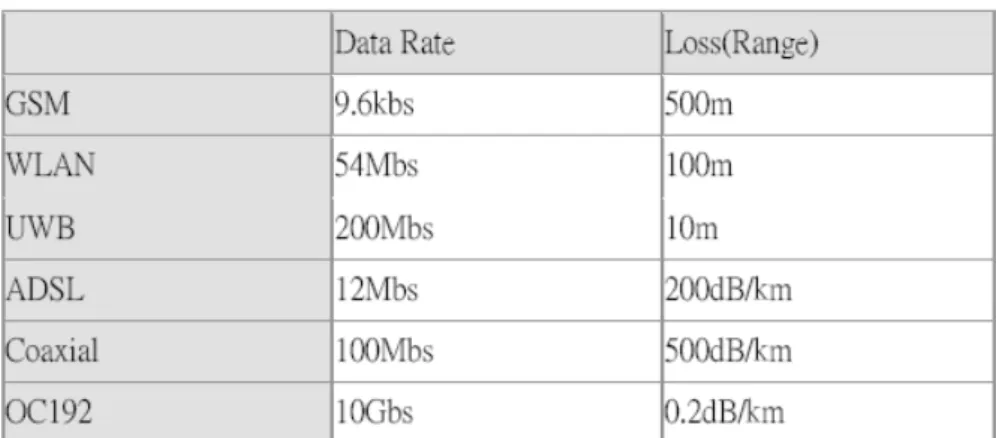

隨著網際網路的出現,人們不斷發現新的應用方法,例如資料傳輸、視訊會議等。這些 應用都需要更快的傳輸速度,因此光纖通訊以其超快的頻寬與極低的傳輸損耗,一直是 滿足這些需求的終極解決方案。光通訊的原理是利用光纖(fiber)來傳遞光訊號,如 (表 1. 1)所示是光通訊和其他不同的通訊方法比較表。由表中可明顯看出,光通訊的頻 寬可達百億位元(10Gbs),遠大於其餘各種通訊方法,而且其損耗也很低,每公里只 有0.2dB。事實上,由於光纖本身的頻寬可達 500 億赫茲(50GHz)以上,因此光通訊 的頻寬是被電子零件的頻寬所限制住,但是隨著近年來製程進步與電晶體速度的提升, 光 通 訊 電 路 也 變 得 越 來 越 重 要 。 現 在 市 面 上 的 寬 頻 上 網 大 部 份 都 是 利 用 ADSL (Asymmetric Digital Subscriber Line),它的好處是只要用現有的電話線路即可,但是 由表 1. 1 可以明顯看出,它的損耗相當大,因此頻寬沒辦法作到很高,尤其是對於像視 訊會議這種須要雙向都很快的應用是沒有辦法的。是故,未來光纖到家(fiber to the home;FTTH)會成為必然的趨勢,台灣地小人稠,正好適合這種光纖到家的終極解決 方案,光通訊電路勢必會成為下一代網路通訊的骨幹。 在光纖通訊電路方面,必須要能夠處理高速的資料,因此在90 年代中期,砷化鎵 (GaAs)和磷化銦(InP)是高性能光電介面電路的唯一解決之道。但由於矽半導體製 程的進步,逐漸出現矽鍺(SiGe)製程或雙載子互補式金氧半(Bi-CMOS)製程等替代 方案[1] -[5] 。早期互補式金氧半(CMOS)製程受限於製程技術的限制,多半應用在一 般的數位邏輯電路上,但隨著製程技術快速的推進到深次微米技術,使得 CMOS 電晶 體操作頻率已可超過10GHz[6] [7] 。而 CMOS 製程在成本上佔有很大的優勢,且現今 相關熱門的系統晶片(system on chip, SoC)研究,其最可能實現之技術亦將採用 CMOS 製程。因此,光纖通訊不僅朝更高速的訊號傳輸量邁進,甚至可將傳送及接收端電路均 整合在一顆晶片上。1.2 論文組織

本論文共分為五章,本章即第一章,介紹論文的研究動機和組織。第二章是詳細說明並 探討光纖接收器的系統概觀和轉阻放大器電路之設計考量。第三章是一個具有高輸入電

容容忍度的光接收轉阻放大器設計和實驗結果。第四章是利用 90 奈米互補式金氧半製 程來設計一個高速光接收轉阻放大器設計和實驗結果。第五章,也就是最後一個章,則 是針對所設計的光接收轉阻放大器做成結論。

表 1. 1 各種通訊方式比較表

第二章

光纖通訊接收端系統與設計考量

2.1 系統概觀

光通訊電路接收端系統如圖 2. 1 所示,光信號經由光纖傳送,先到達光偵測器 (Photodetector;PD),將光信號轉換為光電流。接下來再由轉阻放大器(Transimpedance Amplifier;TIA)將光電流轉換為電壓信號,再經限制放大器(Limiting Amplifier;LA) 將電壓信號放大到可以當作數位信號的程度。接下來再將此信號送給數據時脈回復電路 (Clock and Data Recovery;CDR),判斷資料為 0 或 1,並順便以資料的速度產生一固 定時脈的方波信號,讓後級的數位電路可以使用這個轉換出來的信號。 圖 2. 1 光通訊接收端電路區塊圖 在這些電路區塊中,每個部份都有其特定的功能和要求,以下將一一說明。首先, 在光偵測器部份是將光信號轉換為光電流,故其主要規格在於光電轉換的光反應度 (Responsivity)和光偵測器本身的反應速度。一般說來,其光反應度必須在 0.7A/W 以 上,也就是說若有10µW 的光輸入,要有 7µA 的光電流輸出。如果光反應度太低,會 限制了光纖傳輸的距離。另外,反應速度必須達到系統的要求,例如在OC192 規格中, 就要求百億赫茲(10GHz)的速度。 轉阻放大器的功能在將光電流轉換為電壓信號,故其小訊號轉阻增益和頻寬是必然 的規格。另外,由於轉阻放大器位於光通訊電路接收端的最前級,類似RF 電路的低雜訊放大器(LNA),轉阻放大器也必須有低的雜訊比才能將整個系統的雜訊降低。有些 應用還要求轉阻放大器要有很大的動態範圍(dynamic range),通常是如果輸入光電流 信號太大的話,轉阻放大器必須有一機制讓過大的光電流宣洩,否則會使轉阻放大器沒 辦法操作在其應有的操作點。一般的作法是會在轉阻放大器中增加自動增益控制 (Automatic Gain Control;AGC)的功能。

另外,由於轉阻放大器尚須有低雜訊的功能,因此到這裡的輸出電壓信號還很小, 限制放大器的作用在把小電壓信號再放大,以達到數位電路所需求的大信號輸出。是故 限制放大器的主要規格有頻寬和靈敏度(sensitivity),靈敏度是指該限制放大器所能接 受的最小輸入,其值一般為5mV 左右,表示轉阻放大器的輸出電壓振幅要超過 5mV, 限制放大器才能正常動作。靈敏度越小,則表示在設計上,轉阻放大器的轉阻增益可以 小一些。 最後一級電路是 CDR,這個區塊已經完全是數位電路。因為傳輸過程中一定會有 一些小的雜訊混入信號中,所以通常輸入信號到這裡的雜訊會比較大,CDR 電路可以 將這些雜訊再縮小,並抓出資料的時脈。例如雖然是在 OC192 規格下傳送,但是資料 速度不一定剛好是準確的 10GHz,有可能是 9.9GHz 或 10.2GHz 等等。如果用不對的 時脈去取資料會得到錯誤的結果,因此CDR 電路利用鎖相迴路(Phase Lock Loop;PLL) 的技巧來鎖定資料的速度,並一起提供給後級電路使用。 在 CDR 之後就是大家所熟知的數位信號了,通常經由解調器(demultiplexer; demux)就可以將頻寬分配給各個使用者。

2.2 轉阻放大器基本設計考量

轉阻放大器(transimpedance amplifier)的功用是將電流放大成電壓訊號,除了輸入端的檢 光二極體元件所造成的寄生電容限制了光接收器的頻寬以及靈敏度之外,製程尺寸與供 應電壓(supply voltage)降低的趨勢也產生了更多的挑戰。在接下來的小節中,我們將介 紹轉阻放大器電路設計的基本考量,包含增益、頻寬和雜訊等,這些基本設計考量不只 有助於之後電路設計及製作,在系統的規劃上也有很大的幫助。2.2.1 增益

轉阻放大器增益則必須使輸出的訊號夠大到能克服下一級電路(功率放大器或限制放大 器)的等效輸入雜訊。例如,當一個限制放大器的雜訊電壓為5nV/√Hz 時,轉阻放大器 的增益必須超過5k 歐姆,使輸入參考雜訊電流降低至 1pV/√Hz 以下。所以在增益、頻 寬及voltage headroom 的考量下,通常轉阻放大器與次級電路是一起做設計及最佳化。 同時,若是應用在短距離的光纖接收端,常會有光電二極體接收功率過強產生電流振幅 過大而導致轉阻放大器產生非線性(nonlinearity)的問題,而這通常造成輸出與輸入不成 正比,產生失真的問題而提高了系統的位元錯誤率。所以通常會在轉阻放大器的輸出再接一個自動增益控制電路(automatic gain control)的回授電路,其功用便是在偵測轉阻放 大器的輸出振幅並與一個參考位準做比較並再調整轉阻放大器的阻抗增益(impedance gain)。使其輸出能在一個線性範圍並且是定值的。

2.2.2 頻寬

頻寬大小選擇

資料傳輸的速度及碼間幹擾(intersymbol interference)的考量,決定了轉阻放大器的頻 寬。頻寬越低,其碼間幹擾的情形就越嚴重,使eye closure 及 noise margin 變小,提高 了位元錯誤率(bit error rate)。而頻寬越大,又會使雜訊功率升高(因雜訊屬於寬頻訊號) 而降低了系統輸出訊號雜訊比(output signal to noise ratio)。所以,在這裡頻寬的選擇需 要做一個系統訊號雜訊比的考量,通常頻寬選擇為0.7×(1/Tb),其中 Tb 為訊號位元週期 [8] 。若考慮傳送訊號速度達 10Gb/s,那轉阻放大器頻寬需要 7GHz。頻寬設計挑戰

對於轉阻放大器電路而言(圖 2. 2),輸入端的寄生電容大大的影響整個光接收器的頻 寬。當我們將檢光二極體(PD)與光接收器整合在一起時,轉阻放大器的寄生電容包含檢 光二極體的接面電容(CD)、靜電防護負載電容(CESD)、焊墊負載電容(CPAD)以及轉阻放大 器輸入負載電容(CTIA),對於設計一個高速度的光接收轉阻放大器而言,輸入端的寄生 電容往往是整體系統設計上最大的瓶頸。 圖 2. 2 轉阻放大器 傳統上,為瞭解決輸入端負載電容的問題,通常採用低輸入阻抗的設計,如圖 2. 3 的共 閘極轉阻放大器和圖 2. 4 的多級串連轉阻放大器[9] 都是低輸入阻抗的設計方案,前者 的輸入阻抗Rin =1/(gm1+gm1b),透過提升 gm的方式可以擁有較低的輸入阻抗,然而其 主要缺點為雜訊性能惡化。後者可以透過三級放大器的串聯以提升電路的開迴路增益,進而降低輸入阻抗與電路頻寬,但是較大相位的降低使得系統的穩定度嚴重不足。 圖 2. 3 共閘極轉阻放大器 圖 2. 4 多級串連轉阻放大器

2.2.3 雜訊

低雜訊的考量是因為相同的傳輸訊號強度對較低的雜訊電流強度的電路可有較遠的傳 輸距離(考慮相同的衰減係數下)。 接收靈敏度(sensitivity)是系統動態範圍的一部分,系統靈敏度的定義是接收器至少 需要多大輸入功率,才能在輸出端達到所指定的訊號雜波比或位元錯誤率(BER),靈敏 度取決系統雜訊的大小,越小的雜訊則是越好的靈敏度。如圖 2. 5 所示,達到所指定 的位元錯誤率10-10時,靈敏度為接收器至少需要Psensitivity輸入功率。如果輸入光功率太 大的話,導致轉阻放大器產生非線性的問題,而這通常造成輸出與輸入不成正比,產生 失真的問題而提高了系統的位元錯誤率,錯誤率提升到系統可接受的最大錯誤率時,輸 入的光功率最大值就定義為電路的超載(overload)。所以動態範圍(Dynamic Range)就取 決於系統靈敏度和超載之間的範圍。圖 2. 5 不同光功率的輸入錯誤率碼曲線例子 為了提升頻寬而使用共閘極之轉阻放大器電路設計,此架構雖然擁有低輸入阻抗但 是卻也是高雜訊的電路架構,雜訊的惡化對於靈敏度的影響就變成非常嚴重了。圖 2. 6 是加入雜訊源的共閘極之轉阻放大器,為了簡化分析我們先忽略通道長度調變和基板效 應的影響,然後再利用重疊原理(superposition)來計算出每一個雜訊源的貢獻[8] 。 (1)所有的 2 2 M , n I 流過電阻RD 產生 2 2 M , n 2 DI R 的輸出雜訊。 (2)因為 ro2=∞導致沒有 2 1 M , n I 流過電阻RD, (3)因為從電晶體 M1 的汲極端看進去的阻抗無限大,所以所有的 2 RD , n I 流過電阻RD 產生 2 RD , n 2 DI R 的輸出雜訊。 圖 2. 6 加入雜訊源之轉阻放大器

下列的方程式是共閘極轉阻放大器的輸出雜訊 2 D 2 RD , n 2 2 M , n 2 out , n (I I )R V = + (2. 1) 2 D D 2 m R )R 1 kT(γT 4 = + (2. 2) 方 程 式(2. 2)除以轉阻放大器增益平方得到輸入參考雜訊電流(input-referred noise current): ) R 1 kT(γT 4 I D 2 m 2 n,in = + (2. 3) =I2n,M2+I2n,RD (2. 4) 從方程式(2. 4)可以知道輸入參考雜訊電流大小直接由電晶體 M2 和電阻 RD 的雜訊 大小所決定,所以輸入阻抗和輸入參考雜訊電流是互相權衡(trade-off),也就是說,擁有 低輸入阻抗的轉阻放大器就會造成較大的輸入雜訊電流。 為了降改善電流源M2 所貢獻的雜訊,我們提出使用 inductor degeneration 技術,如 圖 2. 7 所示,將電感 L1 串接在電晶體 M2 與地之間。設計概念如圖 2. 8 所示,透過電 感元件的直流短路和高頻開路特性,以及Ia=Ib的關係式,讓M2 的雜訊電流在高頻時流 到 輸 出 端 的 大 小 趨 近 於 零 , 使 得 積 分 起 來 的 全 部 雜 訊 功 率 下 降 , 所 以 inductor degeneration 技術的補償可以降低共閘極轉阻放大器的雜訊。 利用 Hspice 軟體模擬,如圖 2. 9 所示,當頻寬和資料速度(Rb)相等時,利用 inductor degeneration 技術補償的效果是最好的,M2 雜訊功率大小可以降低至五分之一。 圖 2. 7 使用電感衰減技術之共閘極轉阻放大器

圖 2. 8 電感衰減技術之設計概念

第三章

具高輸入電容容忍度之

光接收轉阻放大器

3.1 簡介

對於一般的光纖網路系統而言,將檢光二極體與光接收器整合在一起時,在訊號輸入端 由檢光二極體元件與靜電放電防護電路所造成的電容負載效應是光接收轉阻放大器設 計上所面臨的最主要問題,其對頻寬與雜訊等重要接收性能有著關鍵性的影響。所以本 章節目標是以1.8伏特供應電壓和0.18微米標準CMOS製程,以及大約0.8pF負載電容的檢 光二極體與0.5pF負載電容的輸入端靜電防護電路,來完成一個操作在5Gb/s並且具有高 輸入電容容忍度的光接收轉阻放大器,其預定效能為-20dBm的靈敏度、3.5GHz的頻寬 和85dBΩ的增益。為達到上述的設計目標,我們利用自我補償的電路架構來降低輸入端 之電容負載效應[11] ;此外,再結合主動式補償之轉阻放大器[12] 與電感補償技術 [14] ,除了可以讓設計的電路系統擁有高頻寬和高增益的特色之外,又改善製程變異和 晶片操作溫度變異所造成的補償不匹配,其中電感是利用堆疊式電感[15] [16] ,以達到 晶片面積節省。3.2 架構

3.2.1 自我補償架構

自我補償電路架構如圖 3. 1 所示,其中包括一個檢光二極體﹙PD﹚、兩個負載電容約 0.5pF 的靜電防護電路、一個正回授電路﹙M1﹚和一個差動轉阻放大器。將檢光二極體 負載電容透過正回授的抵銷機制[10] 與差動式電流偵測設計合而為一,透過此一巧妙結 合,可抵銷於差動輸入端上由靜電放電防護電路所造成的電容負載效應,徹底解決了輸 入端負載電容的難題;此外,運用此種設計架構還可獲得兩倍的增益和增加3dB 的靈敏 度。圖 3. 1 自我補償電路 圖 3. 2 是自我補償電路的小信號模型,R1和 R2為後級差動轉阻放大器的等效輸入阻 抗,Cp為檢光二極體的寄生電容,C1和C2為靜電防護電路對地的負載電容。經過一連 串的公式推導,此小信號模型的單端輸出轉移函數分別是方程式(3. 1)與方程式(3. 2), 以及方程式(3. 3)的雙端輸出轉移函數。 圖 3. 2 自我補償電路小信號模型 1 s ) C R g C C ( s g R ) C C C C C C ( ] 1 ) g C ( s [ R i v 2 2 m p 1 2 m 2 2 1 p 2 p 1 m 1 2 2 + + + + + + + − = (3. 1) 1 s ) C R g C C ( s g R ) C C C C C C ( ] 1 ) C C ( sR [ R i v 2 2 m p 1 2 m 2 2 1 p 2 p 1 2 1 2 3 3 + + + + + + + + = (3. 2) 1 s ) C R g C C ( s g R ) C C C C C C ( ] 1 ) g C ( s [ R ] 1 ) C C ( sR [ R i v v 2 2 m p 1 2 m 2 2 1 p 2 p 1 m 1 2 2 1 2 3 2 3 + + + + + + + + + + = − (3. 3) 為了簡化電路的分析,我們假設C1=C2=C、R1=R2=R 和 gm>>(2/R)代入方程式(3. 1)、方 程式(3. 2)和方程式(3. 3),得到方程式(3. 4)、方程式(3. 5)和方程式(3. 6)。方程式(3. 4) 具有兩個極點,ωp1、ωp2,和一個零點,ωz1,的轉移函數,其波德圖如圖 3. 3(a)所示, 此輸出端的頻率響為頻寬不足;方程式(3. 5) 具有兩個極點,ωp1、ωp2,和一個零點, ωz2,的轉移函數,其波德圖如圖 3. 3(b)所示,此輸出端的頻率響應卻擁有過大的頻寬;

但是雙端輸出的方程式(3. 6)卻具有極零點相等,ωp1、ωz3,的轉移函數,其波德圖如 圖 3. 3(c)所示。所以透過此小信號模型的推導可以證明自我補償電路架構可以透過差動 輸出互相抵消的特性,來解決輸入端的對地負載電容的影響,使轉阻放大器具有高輸入 電容容忍度。 1) 1)(s/ω (s/ω 1) R(s/ω -1 RC)s g C C ( s g R ) C (2CC 1) g C R(s i v p2 p1 z1 m p 2 m 2 p m 2 + + + = + + + + + + − = (3. 4) 1) 1)(s/ω (s/ω 1) R(s/ω 1 RC)s g C C ( s g R ) C (2CC 1] R[s2RC i v p2 p1 z2 m p 2 m 2 p 3 + + + = + + + + + + = (3. 5) 1) 1)(s/ω (s/ω 1) R(s/ω 1 RC)s g C C ( s g R ) C (2CC ] g C 2 R[s2RC i v v p2 p1 z3 m p 2 m 2 p m 2 3 + + + = + + + + + + + = − (3. 6) 圖 3. 3 (a)

v

2端波德圖 (b)v

3端波德圖 (c)雙端波德圖 ⎪ ⎪ ⎪ ⎪ ⎩ ⎪⎪ ⎪ ⎪ ⎨ ⎧ = = + + + + = = ≈ − − 1 z2 m z1 p p p m p2 z3 1 p1 (2RC) ω C g ω C) RC(2C C C C 2C g ω ω (RC) ω3.2.2 負阻抗與電感補償技術

如圖 3. 4 所示,將差動式負阻抗與 shunt peaking 加入差動轉阻放大器的輸出端,負阻 抗補償技術具有同時提升電路的增益和頻寬的優點,shunt peaking 也具有提升頻寬的好 處。由方程式(3. 7)推導出補償後的增益 Av(Zc)比未補償的增益 Av(Zc-1=0)可以提升 γ 倍, 也就是說,此補償等效提昇轉阻放大器的增益且降低輸入阻抗,因而使其整體頻寬獲得 改善。 圖 3. 4 負阻抗補償之轉阻放大器 C f L f L 1 C V i O C V Z 1 R 1 R 1 R 1 R 1 γ where 0) (Z A γ V V ) (Z A − + + = = ⋅ = = − (3. 7)3.2.3 系統架構

整個系統架構如圖 3. 5 所示,其中包括了一個檢光二極體﹙PD﹚、兩個靜電防護電路 ﹙ESD Protection Circuit,負載電容約0.5pF﹚、一個正回授電路﹙M1﹚來降低跨於檢光二極體兩側的暫態電壓、一個差動轉阻放大器、雙回授直流偏壓控制電路、以及兩級的 增益緩衝器和一個輸出級(Output stage)。

自我補償電路

如圖 3. 5所示,檢光二極體的陰極經過電感(L)和電容(C)的串聯到電晶體M1的閘極端 再到源極端為自我補償電路的正回授路徑。M1的傳導係數(gm)大小決定正回授的增益 與輸入端的頻寬,相對也決定雜訊貢獻的大小,所以電路頻寬與雜訊大小是相互trade off,除此之外,電感與電容的串聯共振可以增強正回授的電壓訊號,所使用的C為3pF 的MIM電容,L為5nH的堆疊式電感。為了提供檢光二極體於高速工作所需要的1.2V逆向偏壓,所設計差動轉阻放大器輸入偏壓1.5V與電晶體M1的源極端偏壓為0.3V。 圖 3. 5 系統架構

雙回授直流偏壓控制電路

為解決檢光二極體所造成的輸出端直流位準漂移問題,系統架構包含兩個比較器和兩個 可控制電流源的雙回授直流偏壓控制電路,主要是透過比較器偵測流過負回授電阻的直 流電流,然後控制輸入端電流源的直流電流大小,此負回授特性使檢光二極體的直流電 流無法流入回授電阻,所以解決了直流位準漂移的問題,可有效改善大訊號波型失真的 現象。除此之外,這兩個比較器設計具有0.3V的直流偏移(Vos),造成差動轉阻放大器輸 出端比輸入端低0.3V的直流位準,也就是說,輸出端增加0.3V的headroom可以等效提昇 差動轉阻放大器的開迴路增益與輸入端頻寬。差動轉阻放大器核心電路

差動轉阻放大器核心電路為圖 3. 5 的 T1。設計一個好的轉阻放大器必須考量雜訊、速 度、和增益之間的互相影響,傳統的轉阻放大器為使轉阻放大器電路擁有比較低的雜 訊,設計大的回授電阻可以擁有較低的雜訊,但是轉阻放大器的頻寬卻會受到回授電阻 的限制。為了克服這個問題,我們在輸出端使用包含負電阻與負電容的主動式補償以及 shunt peaking 補償的技術;負電阻是補償輸出的負載電阻,可以等效提昇其轉阻放大器 的增益,因而使其輸入阻抗下降與頻寬的增加;負電容與shunt peaking 是補償輸出的寄 生電容,shunt peaking 是不消耗 headroom 而能增加頻寬的補償技術,負電容可以隨消 耗headroom 大小而增加頻寬補償能力的技術。結合 shunt peaking 和負阻抗補償技術, 除了可以增加電路頻寬與增益之外,也改善電容補償的不匹配。所以為了轉阻放大器能 擁有高頻寬以及低雜訊的效能,我們對轉阻放大器的輸出端使用主動式補償和 shuntpeaking 補償。

雙級增益緩衝器

介於轉阻放大器與輸出級之間的電路必需是一個高頻寬的緩衝器,所以主動式補償之技 術亦可運用在緩衝器上,讓緩衝器可以同時擁有高增益和高頻寬的效能,雙級增益緩衝 器的設計使得整體系統效能可以達到80dBΩ以上的高增益。加入前面所列出的補償技術 所新設計的系統,可以使新設計的系統頻寬比未補償系統頻寬和增益都獲得改善,在接 下來小節的模擬將獲得驗證。3.3 電路設計

3.3.1 電感與負電容補償設計

在設計高速電路時,電感與負電容都是十分有用的頻寬補償技術,前者的優點是不消耗 headroom 下可以提升頻寬,但是它卻需要考量晶片佈局、面積、寄生電容與電感值估計 的準確性,後者的優點是具有彈性的補償與節省晶片面積的技術,但是它卻需要消耗 headroom 才能提升補償的能力。在這一小節中我們將探討使用電感與負電容補償技術的 設計方式與準則。電感補償設計準則

因為inductive peaking 技術[14] 不需消耗電路的 headroom,所以可以應用在低電壓設計 上。圖 3. 6 是一個共源極放大器,藉由輸出電阻 R 與電感 L 的串聯可以產生一個新的 零點來抵消極點,然後產生一個更高頻的極點以達到頻寬提昇的目的。 圖 3. 6 電感補償之放大器 使用負電容補償之輸出的阻抗為下列方程式: 1 sRC LC s sL R Zo 2 + + + = (3. 8)

1 s m s ) m s 1 ( R 2 2τ + τ+ τ + = (3. 9) 中τ=RC 和 m=L/R2C。圖 3. 7 是針對不同 m 值的頻率響應,沒有使用電感補償的曲線 (m=0)作為頻寬改善的參考點,所以將其增益和 3dB 頻率設為 1(RL=1 和 CL=1),當 m=0.4 時,擁有最平坦的頻率響應,此時的頻寬增加70%。當 m=0.7 時,擁有增加 85%的最大 頻寬改善,但是卻增加 1.5dB 的 peaking。所以當輸出負載電容增加時,提升電感大小 才能增加頻寬的改善,但是需要考量晶片佈局困難以及面積與寄生電容的增加。 圖 3. 7 電感補償之頻率響應

負電容補償設計準則

為了增加電路頻寬,我們可以將放大器的輸出端加入負電容補償,如圖 3. 8 所示,一個 差動放大器的輸出端加入電晶體Mc1 Mc2 與電容 kCL 來產生負電容效應,此電路的輸出 端會產生一個新的零點來抵消原本的極點,並且產生一個更高頻的極點讓輸出端的頻寬 增加。使用負電容補償之輸出的阻抗如方程式(3. 10)所示,其中的 gmc代表電晶體 Mc1 和Mc2 的傳導係數(transconductance) 圖 3. 8 負電容補償之放大器 k g s ) g C R ) 2 k 1 ( C 2 ( s C R 2 ) s C 2 k g ( R Z mc mc L L L 2 2 L L L mc L o + − + + + = (3. 10)為了分析方程式(3. 10)的阻抗特性,我們分成兩方向來討論: (1)以固定的電容(k=0.2)來改變電晶體 Mc1和Mc2 的傳導係數(gmc) 如圖 3. 9 所示,針對不同的傳導係數下的輸出阻抗之頻率響應,沒有使用負電容補償的 曲線(gmc=0)作為頻寬改善的參考點,所以將其增益和 3dB 頻率設為 1 (將 RL=1 和 CL=1 代入Zo);當 gmc=0.1 時,頻寬增加 10% ;當 gmc=1 時,頻寬增加 70%。也就是說,在 不增加輸出負載電容大小的條件下,增加負電容偏壓電流可以提昇頻寬的補償能力,所 以負電容對頻寬的補償是受限於輸出的headroom。 (2)以固定的傳導係數(gmc=0.1)來改變補償電容(k)的大小 如圖 3. 10 所示,針對不同的補償電容(k)下的輸出阻抗(Zo)之頻率響應,沒有使用負電 容補償的曲線(gmc=0)作為頻寬改善的參考點,所以將其增益和 3dB 頻率設為 1 (將 RL=1 和CL=1 代入 Zo);當 k=0.1 時,頻寬增加 10% ;當 k=0.25 時,頻寬也 10%,但是卻增 加0.4dB 的 peaking。也就是說,越大補償電容(k)並不能增加頻寬反而增加 peaking,造 成系統的不穩定。 圖 3. 9 不同傳導係數之頻率響應 圖 3. 10 不同補償電容之頻率響應

3.3.2 轉阻放大器核心電路

圖 3. 11為整體系統架構的完整轉阻放大器核心電路,T1,輸出端加入包含負電阻與負 電容的主動式補償電路,其中的電晶體Mr1 Mr2產生電阻效應,負電容則利用電晶體Mc1 Mc2 與電容CC 來控制。對於電阻回授之單級差動對轉阻放大器而言,可以使系統具有 較佳的雜訊效能與系統的穩定,但是它的低開迴路增益卻是造成寬頻設計上的困難,一 般上,增加開迴路增益可以使用主動式負載來取代被動式負載,然而較差的線性特性使 系統無法擁有較大的動態範圍。透過在輸出端加入的負阻抗可以調節其阻抗特性,等效 提昇其轉阻放大器的增益,因而使其整體頻寬獲得改善,相較於單端式轉阻放大器而 言,差動轉阻放大器更容易實現負阻抗補償。 圖 3. 11 轉阻放大器核心電路 使用負電阻補償之開迴路增益為下列方程式: L mR L m1 mR f L m1 o R g 1 R g ) g 1 // //R (R g A − ≈ − × = (3. 11) 由於方程式圖 3. 11的分母不得為負,以及需要考量負電阻補償的變異,所以設計分母 的值為1/2,可以推導出方程式(3. 12)和方程式(3. 13)L mR 2R 1 g = (3. 12) L o m1 2R A g = (3. 13) 再利用電流相等來推導出差動對電晶體與負電阻電晶體的尺寸大小關係,如方程式(3. 14),這裡先忽略負電容的部份,因為負電容主要是針對改善輸出阻抗不匹配的補償。 r r ox n 2 mR 1 1 ox n 2 m1 R 1 C R 1 L W L ) C 2µ g ( W L ) C 2µ g ( I I I I I I = + + ≈ + = × + × (3. 14) 此外,在不消耗headroom下使用shunt peaking補償技術更能提升轉阻放大器的頻寬。在 回授電阻上並聯一個手動電壓控制的可變電阻(使用電晶體Mg1和Mg2來完成)可以提升 overload的大小。為了控制輸出的共模電壓準位,加入一個包含比較器和控制電流源的 負回授電路。

改善輸出補償的不匹配

隨著製程上corner 的變異或是晶片內操作溫度的變異,負電阻的變異導致輸出端補償的 不匹配,所以我們設計一個隨corner 變異和晶片操作溫度變異的負電阻和負電容,其設 計概念為透過負電阻與負電容偏壓電流的調變來改善輸出補償的變異。 所設計的負電阻電路,如圖 3. 12 所示,Ir提供了負電阻所需要的偏壓電流,在電流鏡的閘極端加入了一個w/i Silicide 的電阻 Ry,此電阻具有正溫度係數的特性。當corner

變為FF 或溫度下降時,藉由方程式(3. 15)的推倒,可以知道遷移率(µn)的上升會使得負 電阻變大,造成負電阻對系統補償過頭,除此之外,透過方程式(3. 16)負電阻偏壓電流, Ir,與電阻 Ry的關係,以及電阻 Ry正溫度係數的特性,使得負電阻的偏壓電流下降, 達到反向開迴路的補償機制。同理,當 corner 變為 SS 或溫度上升時,因為遷移率(µn) 的下降使得負電阻變小,造成負電阻對系統補償不足,所以透過 Ry 變大的特性使得負 電阻的偏壓電流上升,也達到反向開迴路的補償機制。 L W C µ 2 1 I 2 2 gm 2 --R ox n r× × × − = = (3. 15) ) R Vt (I W W I W W I y m x r x x r r = × = × − (3. 16) 當corner 變為 SS 或溫度上升時,電感串聯的電阻變大,造成使用電感來補償頻寬的能 力降低,所以在此利用負電容來彌補此時電感的不足,主要的設計概念是透過w/i Silicide 的電阻在SS 或溫度上升能變大的特性,使負電容的偏壓電流( Ic )也能隨著 SS 或溫度上 升能變大(如圖 3. 13),由前一小節的分析可以知道負電容的頻寬補償能力隨偏壓電流的 上升而變大,所以負電容補償頻寬能力的變大可以彌補電感補償的不足。同理,當corner 變FF 或溫度下降時,負電容的偏壓電流隨著 FF 或溫度下降而變小,使得負電容補償頻 寬能力的變小可以降低對系統補償過頭。

圖 3. 12 負電阻之電流源電路 圖 3. 13 負電容之電流源電路

比較器電路

圖 3. 14 為雙回授直流偏壓控制電路和差動核心轉阻放大器﹙T1﹚控制輸出共模電壓所 需的比較器電路,此比較器電路為雙端輸入和單端輸出,且頻寬必須小於50kHz 以確保 電路只控制直流偏壓,所以在輸出端加入10pF 大小的負載電容(如圖中的 C1 和 C2), 因為此比較器的主極點發生在輸出上。由於雙回授直流偏壓控制電路需要透過比較器提 供0.3V 的直流偏移(Vos),所以我們設計電晶體M11通道寬度為電晶體 M12的γ倍,由 方程式(3. 17)與方程式(3. 18)的電流相等推導出直流偏移電壓(Vos)方程式(3. 19),然後 再將方程式(3. 20)與方程式(3. 21)代入方程式(3. 19),可以獲得所需要設計的γ值為 1.9。(

)

2 tn i ox n 1 D V V L W C 2 1 I ⎟ − ⎠ ⎞ ⎜ ⎝ ⎛ γ µ = − (3. 17)(

)

(

)

2 tn OS i ox n 2 tn i ox n 2 D V V V L W C 2 1 V V L W C 2 1 I ⎟ + − ⎠ ⎞ ⎜ ⎝ ⎛ µ = − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ µ = + − (3. 18)(

)

(

i tn)

OS 1 V V V = γ − −− (3. 19)( )

VOS StableVOS Max ⇔ (3. 20) 9 . 1 V 3 . 0 V V 4 . 0 V V 2 . 1 V V : quirements Re OS tn R i = γ ⇒ ⎪ ⎩ ⎪ ⎨ ⎧ = = = = − (3. 21)圖 3. 14 比較器電路

3.3.3 負阻抗補償之增益緩衝器

圖 3. 15 為所設計的單級增益緩衝器完整電路,此電路是加上負阻抗補償的 Cherry Hooper 電路架構[19] ,其中的電晶體 Mr3 Mr4 產生負電阻效應,負電容則利用電晶體 Mc3 Mc4 與電容CC2 來控制,由於Cherry Hooper 電路架構是轉導放大級和轉阻放大級的 結合,加入負阻抗補償技術[12] 可以調節其轉阻放大級的輸出阻抗特性,以等效提昇其 轉阻放大器的增益,而且擁有高寬頻的單級增益電路。圖 3. 16 為輸出級的電路圖,為 了驅動示波器上的50 歐姆阻抗,所以輸出級必須有高電流驅動能力。在最近的研究上, 共源極放大器常常被作為最好的輸出級選擇,因為他輸出的直流偏壓準位可以獨立於輸 入閘極電壓準位,再加上輸出阻抗的匹配可以用簡單的50 歐姆電阻或者 2 個 100 歐姆 電阻並聯來完成。 圖 3. 15 增益級緩衝器電路圖 3. 16 輸出級電路

3.4 模擬和佈局

模擬使用主動式補償之轉阻放大器

由於轉阻放大器與檢光二極體是利用 bond-wire 方式整合在同一電路印刷板上,所以在 模擬轉阻放大器頻率響應和眼圖時,必須考量bond-wire 的電感效應,如圖 3. 17 為所 示,1nH 的 LBW作為bond-wire 的電感模擬,輸入端的檢光二極體負載電容 CPD為0.8pF、 串聯電阻Rs 為 15 歐姆,以及靜電防護電路的負載電容為 0.5pF。圖 3. 18 為模擬轉阻 放大器使用負阻抗補償與電感補償的頻率響應,由圖中可以得到沒有使用補償的頻寬為 320MHz,加入負阻抗補償轉阻放大器的頻寬從 320MHz 提升到 1.9GHz,增益也提升了 3.5dB 歐姆,再加入電感補償轉阻放大器的頻寬從 1.9GHz 提升到 3.0GHz。圖 3. 19(a) 為模擬沒有補償之轉阻放大器的眼圖,圖 3. 19(b)為模擬有負阻抗補償之轉阻放大器的 眼圖,圖 3. 19(c)為模擬有負阻抗與電感補償之轉阻放大器的眼圖。所以不論從頻率域 或時間域都可以證明使用主動式補償的轉阻放大器可以同時改善增益與頻寬的效能 圖 3. 17 bond-wire 模擬考量模擬使用電感和電容串聯的效應

圖 3. 20 為模擬轉阻放大器使用電感和電容串聯的交流耦合的頻率響應,由圖中可以得 到只有使用電容的交流偶合的頻寬為 2.4GHz,使用電感和電容串聯的交流耦合的頻寬 從2.4GHz 提升到 3.8GHz, 圖 3. 21 (a)為模擬只有使用電容的交流偶合的眼圖,圖 3. 21 (b)為模擬使用電感和電容串聯的交流耦合的眼圖由此可以證明電感和電容串聯的交流 耦合可以提昇正回授的電壓訊號,以達到提昇轉阻放大器的頻寬。圖 3. 18 轉阻放大器頻率響應模擬 (a) (b) (c) 圖 3. 19 (a)無補償的眼圖模擬 (b)有負阻抗的眼圖模擬(b)有負阻抗與電感的眼圖模擬 圖 3. 20 轉阻放大器 LC 串聯的交流耦合之頻率響應模擬 (a) (b) 圖 3. 21 (a)電容交流偶合的眼圖模擬 (b) 電感電容串聯之交流偶合的眼圖模擬

模擬使用主動式補償之增益緩衝器

圖 3. 22 為模擬增益緩衝器使用負阻抗補償的頻率響應,加入負阻抗的頻寬從 4.5GHz 提升到6GHz,增益提升了 5.5dB 歐姆。圖 3. 23(a)為模擬沒有加負阻抗補償之增益緩衝 器的眼圖,圖 3. 23(b)為模擬有負阻抗補償之增益緩衝器的眼圖。所以不論從頻率域或 時間域都可以證明使用主動式補償可以同時改善增益與頻寬的效能。 圖 3. 22 增益級電路之頻率響應模擬 (a) (b) 圖 3. 23 (a)無主動式補償的眼圖模擬 (b)有主動式補償的眼圖模擬模擬改善輸出補償變異

隨著製程上corner 的變異或是晶片內操作溫度的變異,導致轉阻放大器核心電路輸出端 使用負阻抗與電感補償能力的改變,所以使用偏壓電流追蹤技術來改變負電阻與負電容 的補償能力,以降低系統效能的變異。 當corner 為 SS 和溫度為 80°C 時,圖 3. 24 為模擬轉阻放大器使用偏壓電流追蹤技 術的頻率響應,使用追蹤技術的頻寬從1.24GHz 提升到 2.48GHz;圖 3. 25(a)為模擬當 溫度80°C 和 corner 為 SS 時沒有使用偏壓電流追蹤技術的眼圖,圖 3. 25(b)為模擬當溫 度+80°C 和 corner 為 SS 時有使用偏壓電流追蹤技術的眼圖。 當corner 為 FF 和溫度為 0°C 時,圖 3. 26 為模擬轉阻放大器使用偏壓電流追蹤技術的頻率響應,使用追蹤技術的peaking 從 10dB 降低到 1.8dB;圖 3. 27(a)為模擬當溫 度0°C 和 corner 為 FF 時沒有使用偏壓電流追蹤技術的眼圖,圖 3. 27(b)為模擬當溫度 0°C 和 corner 為 FF 時有使用偏壓電流追蹤技術的眼圖。 圖 3. 24 SS 和溫度 80°C 的頻率響應模擬 (a) (b) 圖 3. 25 (a)無電流追蹤技術的眼圖模擬 (b)有電流追蹤技術的眼圖模擬 圖 3. 26 FF 和溫度 0°C 的頻率響應模擬

(a) (b) 圖 3. 27 (a)無電流追蹤技術的眼圖模擬 (b)有電流追蹤技術的眼圖模擬

模擬輸入端電容容忍度

圖 3. 28(a)為輸入訊號 10uApp、5GHz 的 K28.5k 訊號和輸入端沒有靜電防護電路的模擬 眼圖,圖 3. 28(b)為輸入訊號 10uApp、5GHz 的 K28.5k 訊號和輸入端有靜電防護電路的 模擬眼圖,圖 3. 29(a)為輸入訊號 800uApp、5GHz 的 K28.5k 訊號和輸入端沒有靜電防 護電路的模擬眼圖,圖 3. 29 (b)為輸入訊號 800uApp、5GHz 的 K28.5k 訊號和輸入端有 靜電防護電路的模擬眼圖。 (a) (b)圖 3. 28 (a)Rf=2k 和沒有 ESD 電路的眼圖模擬(b)Rf=2k 和有 ESD 電路的眼圖模擬

(a) (b)

佈局平面圖

圖 3. 30 為晶片佈局平面圖。為了節省晶片的面積,轉阻放大器的電感是使用堆疊式, 立體圖如圖 3. 31 所示,在我們設計的立體電感中用了四層的金屬,從最上層的金屬 (metal 6)開始順時針往內繞兩圈,再連接下一層金屬(metal 5)往外繞兩圈,再連接下一層 金屬(metal 4)往內繞兩圈,最後再連接下一層金屬(metal 3)往外繞兩圈即可完成我們所需 要的電感。對於電感特性的模擬,主要是利用安捷倫公司所開發出來的ADS Momentum 作電磁模擬,需注意的參數有線寬,線距,內徑等,模擬電感的感值和串聯的阻值,以 便將所設計的堆疊式電感和轉阻放大器共同整合模擬。圖 3. 32 (a)為晶片顯微圖,晶片 下方為輸入端,晶片上方為輸出端,圖 3. 32 (b)為晶片與檢光二極體(圖中下方的晶片) 整合在同一電路印刷板上的顯微圖,其中檢光二極體的感光直徑為60µm。 圖 3. 30 佈局平面圖 圖 3. 31 四層堆疊式電感立體圖(a) (b) 圖 3. 32 (a)晶片顯微圖(b)晶片與檢光二極體整合顯微圖

模擬效能總結

表 3. 1 為此轉阻放大器模擬效能結果與預定規格的比較,其中模擬的靈敏度估算是由方 程式(3. 22)[25] 來求得大約為-19.2dBm (ρ=0.9W/A,re=9.5dB)。 ] 1000 ) 1 r ( 2 ) 1 r ( I 1 . 14 log[ 10 y sensitivit e e N × − ρ + × × = (3. 22) 表 3. 1 預定規格與模擬效能比較 預定規格 模擬結果Technology 0.18µm CMOS 0.18µm CMOS

Supply voltage 1.8V 1.8V

PD capacitance 0.8pF 0.72pF

ESD capacitance 0.5pF 0.5pF

Data rate 5Gb/s 5Gb/s

Receiver bandwidth 3.5GHz 3.86GHz(w/o ESD)

3.10GHz(w/ ESD) Input equivalent noise current - 1.19uA(w/o ESD) 1.23uA(w/ ESD) Sensitivity -20dBm -19.2dBm

Transimpedance gain 85dBΩ 88dBΩ (differential)

Output swing 360mVpp 360mVpp (differential)

Power consumption - 62.5mW

3.5 量測結果

3.5.1 量測環境

頻率響應量測環境

圖 3. 33(a)為理想光接收器的頻率響應量測環境,由網路分析儀的 Port 1 將電訊號送入 光發射器把電訊號轉成光訊號,然後將產生光訊號送入寬頻光接收器,輸出電壓訊號再 送回到網路分析儀的Port 2,量測出 S21_Wideband。圖 3. 33(b)為晶片頻率響應量測環 境,由網路分析儀的Port 1 將電訊號送入光發射器把電訊號轉成光訊號,然後利用光對 準器(Optical probe)將光訊號和檢光二極體互相耦合,此 InGaAs PIN 的檢光二極體與轉 阻放大器整合在同一電路印刷板(PCB)上,操作在 1.2 伏特逆向偏壓的檢光二極體的寄 生電容為0.72pF 與打入 1310nm 光波長的光反應度為 0.9A/W,所產生光電流訊號送入 轉阻放大器,輸出電壓訊號再送回到網路分析儀的Port 2,量測出 S21_DUT。最後把兩 個S21 相除,如下列方程式,即可以得到頻率響應量測結果。 Wideband _ 21 S DUT _ 21 S 21 S = (3. 23) (a) (b) 圖 3. 33 晶片頻率響應量測安裝環境眼圖與靈敏度量測環境

圖 3. 34 為晶片眼圖與靈敏度量測環境,利用安捷倫 N4901B 送出 5Gb/s 的 231-1 的偽隨機二進制數據流(PRBS)給 Externally Modulated DFB Source,此發射器會將電訊號轉成 光訊號並且送出具有9.5dB Extinction ratio 和 1310nm 光波長的光訊號,再利用光對準器 (Optical probe)將光訊號和檢光二極體互相耦合,此 InGaAs PIN 的檢光二極體與轉阻放 大器整合在同一電路印刷板(PCB)上,操作在 1.2 伏特逆偏壓的檢光二極體的寄生電容 為0.72pF 和打入 1310nm 光波長的光反應度為 0.9A/W;透過檢光二極體的接收將光轉 換成電流訊號,再由所設計的轉阻放大器放大成電壓訊號到安捷倫86100B 視波器上,

量測出不同光功率下的眼圖;以及透過一個40dB Ω的寬頻放大器送回 N4901B 來估算 位元錯誤率,最後形成位元錯誤率曲線,即得到系統靈敏度。 圖 3. 34 晶片眼圖和錯誤碼率量測安裝環境

3.5.2 量測結果

頻率響應量測結果

量測結果如圖 3. 35 所示,轉阻放大器沒有加入靜電防護電路(w/o ESD)的頻寬為 3.0GHz,加入靜電防護電路(w/ ESD)的頻寬為 2.7GHz,也就是說,靜電防護電路對於 轉阻放大器輸入端所增加的負載電容只有降低 0.3GHz 的頻寬,所以此轉阻放大器對輸 入端的負載電容有較大的容忍度。 圖 3. 35 頻率響應量測結果眼圖量測結果

圖 3. 36 為輸入訊號功率-16dBm、5GHz 的 231-1 的偽隨機二進制數據流(PRBS)和輸入 端有靜電防護電路的量測眼圖,圖 3. 37 為輸入訊號功率-16dBm、5GHz 的 231-1 的偽隨 機二進制數據流(PRBS)和輸入端沒有靜電防護電路的量測眼圖。圖 3. 38 為輸入訊號功 率+0dBm、5GHz 的 231-1 的偽隨機二進制數據流(PRBS)和輸入端有靜電防護電路的量 測眼圖,圖 3. 39 為輸入訊號功率+0dBm、5GHz 的 231-1 的偽隨機二進制數據流(PRBS) 和輸入端沒有靜電防護電路的量測眼圖。 圖 3. 36 輸入訊號功率-16dBm、5GHz 和有靜電防護電路的眼圖 圖 3. 37 輸入訊號功率-16dBm、5GHz 和無靜電防護電路的眼圖圖 3. 38 輸入訊號功率+0dBm、5GHz 和有靜電防護電路的眼圖 圖 3. 39 輸入訊號功率+0dBm、5GHz 和無靜電防護電路的眼圖

靈敏度量測 I

圖 3. 40 是使用安捷倫 N4901B Serial BERT 儀器,量測的位元錯誤率曲線圖,在符合位 元錯誤率在 10-12 條件下,沒有靜電防護電路之轉阻放大器的靈敏度為-17.6dBm,當加 入靜電防護電路時靈敏度下降至-17.2dBm,驗證了此電路架構可達到高輸入電容的容忍 度。靈敏度量測 II

圖 3. 41 是關閉輸入訊號時,使用安捷倫 E4400A 頻譜分析儀,量測晶片單端輸出雜訊 功率分佈圖[17] ,將雜訊功率積分至 5GHz 的單端輸出總雜訊功率 Pn,out = -33.1dBm, 再代入方程式(3. 24)算出輸入參考雜訊電流 IN (方程式(3. 24)中的 47 為 dBm 與 dBmV 單 位轉換因素),最後由方程式(3. 25)[25] 來算出靈敏度(sensitivity)為-17.5dBm (方程式(3. 25)中的 ρ=0.9W/A,ρ 為檢光二極體的光反應度(responsivity);re=9.5dB,re為發射器的 extinction ratio) ,與安捷倫 N4901B 所量測的靈敏度只相差 0.1dB。 gain mV 10 I ) 20 47 P ( N out , n ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ = + (3. 24) ] 1000 ) 1 r ( 2 ) 1 r ( I 1 . 14 log[ 10 y sensitivit e e N × − ρ + × × = (3. 25)靈敏度量測 III

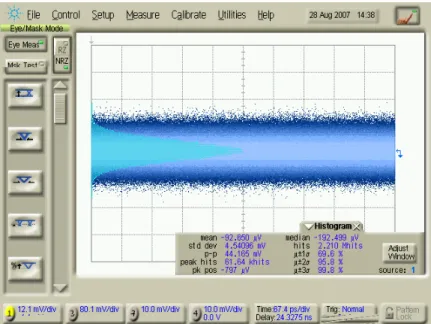

圖 3. 42 是 關 閉 輸 入 訊 號 時 , 使 用 安 捷 倫 86100B 視 波 器 , 量 測 晶 片 單 端 輸 出 的 Gaussian-shaped Histogram[18] ,輸出雜訊為4.54mV,除以增益2.75k得到輸入參考雜訊 電流 IN ,最後由方程式(3. 25)[25] 來算出靈敏度(sensitivity)為-17.9dBm (方程式(3. 25) 中的ρ=0.9W/A,ρ為檢光二極體的光反應度(responsivity);re=9.5dB,re為發射器的 extinction ratio) ,與安捷倫N4901B所量測的靈敏度只相差0.3dB。 圖 3. 40 位元錯誤率曲線圖圖 3. 41 輸出雜訊功率分佈圖

圖 3. 42 單端輸出之 Gaussian-shaped Histogram

晶片效能比較

表 3. 2 為量測效能總結與模擬的比較,表 3. 3 為晶片效能與其他晶片的比較,在相同 的製程與供應電壓下,此設計具有較高的頻寬和較大的增益。

表 3. 2 量測效能總結與比較 預定規格 模擬結果 量測結果 Technology 0.18µm CMOS 0.18µm CMOS 0.18µm CMOS Supply voltage 1.8V 1.8V 1.8V PD capacitance 0.8pF 0.8pF 0.72pF ESD capacitance 0.5pF 0.5pF 0.5pF Data rate 5Gb/s 5Gb/s 5Gb/s Receiver bandwidth 3.5GHz 3.86GHz (w/o ESD) 3.10GHz (w/ ESD) 3.0GHz (w/o ESD) 2.7GHz (w/ ESD) Input equivalent noise current - 1.19uA (w/o ESD) 1.23uA (w/ ESD) 1.77uA (w/o ESD) 1.92uA (w/ ESD) Sensitivity -20dBm -19.2dBm -17.6dBm

gain 85dBΩ 88dBΩ (differential) 81dBΩ (differential)

Output swing 360mVpp 360mVpp (differential) 360mVpp (differential) Power consumption - 62.5mW 62.5mW Die size - 600x520 µm2 600x520 µm2 表 3. 3 晶片效能比較

This Work ISSCC 2007[13]

Technology 0.18µm CMOS 0.18µm CMOS

Supply voltage 1.8V 1.8V

PD capacitance 0.72pF 0.8pF

ESD capacitance 0.5pF 0.5pF

Power consumption 63mW 40mW

Data rate 5Gb/s 5Gb/s

Transimpedance gain 11kΩ (differential) 3.5kΩ (differential)

Bandwidth 3.00GHz 1.82GHz

Dynamic range(BER = 10-12) -17.6dBm to +0dBm -20.3dBm to +0dBm

Output swing 360mVpp (differential) 570mVpp (differential)

第四章

90 奈米 CMOS 之 10Gb/s

光接收轉阻放大器

4.1 簡介

隨著多媒體網路應用的快速發展,以及標準互補式金氧半(CMOS)製程上的演進和低功 率消耗的需求,使用低成本的CMOS製程與低供應電壓來設計更快傳輸速度的光接收器 是整個光纖網路的未來趨勢,像這近六年來使用CMOS設計高速光通訊前端類比電路的 期刊論文[22] -[26] 或會議論文[27] [28] 都已經成為主流。由於光接收器電路必須把檢 光二極體與轉阻放大器整合在一起,所以設計一個光接收轉阻放大器時,除了考慮輸入 端寄生電容對接收器的效能造成瓶頸之外,提供給檢光二極體高速工作所需要的偏壓也 是設計上所需要考量的。所以本章節目標是以90奈米標準CMOS製程與大約0.15pF負載 電容的檢光二極體,搭配偽差動式輸入架構、雙級差動轉阻放大器與shunt peaking補償 技術,來完成一個1.2伏特供應電壓和操作在10Gb/s的光接收轉阻放大器,其預定效能為 -18dBm的靈敏度、7GHz的頻寬和60dBΩ的增益。4.2 架構

4.2.1 單端式與差動式架構

圖 4. 1(a)是一個單級放大器,它的增益頻寬積為下列方程式: T m s 1 s 1 f C g BW A × = ≈ (4. 1) 為了確保回授的穩定度,此放大器的頻寬(BW1s)必需比轉阻放大器頻寬(BWTIA)大α倍 TIA s 1 BW BW =α× (4. 2) 將方程式(4. 2)代入方程式(4. 1)中,推導出單級放大器的最大電壓增益方程式(4. 3)TIA T s 1 BW f A × α = (4. 3) 圖 4. 1(b)是一個雙級串聯放大器,包含兩級相同的放大器,每一級的增益頻寬積為下列 方程式: T m i, s 2 i, s 2 f C g BW A × = ≈ (4. 4) 當它使用在轉阻放大器時,為了達到足夠的相位邊際,每級放大器的頻寬(BW2s,i)必需比 單級放大器(BW1s)大β倍,使得它們具有相同的相位邊際,由下列方程式推導出β值 ) 1 ( tan 2 ) 1 ( tan-1 -1 β × α × = α (4. 5) 對於雙級串聯放大器而言,每一級放大器所需的頻寬(BW2s,i)為下列方程式所示: TIA i, s 2 BW BW =α×β× (4. 6) 將方程式(4. 6)代入方程式(4. 4)中,推導出雙級串聯放大器的最大電壓增益方程式: 2 TIA T 2 i, s 2 s 2 ) BW f ( A A × β × α = = (4. 7) 圖 4. 1(c)是一個三級串聯放大器,包含三級相同的放大器,每一級的增益頻寬積為下列 方程式: T m i, s 3 i, s 3 f C g BW A × = ≈ (4. 8) 當它使用在轉阻放大器時,為了達到足夠的相位邊際,每級放大器的頻寬(BW3s,i)必需比 單級放大器(BW1s)大γ倍,使得它們具有相同的相位邊際,由下列方程式推導出γ值 ) 1 ( tan 3 ) 1 ( tan-1 -1 γ × α × = α (4. 9) 對於三級串聯放大器而言,每一級放大器所需的頻寬(BW3s,i)為下列方程式所示: TIA i, s 3 BW BW =α×γ× (4. 10) 將方程式(4. 10)代入方程式(4. 8)中,推導出三級串聯放大器的最大電壓增益方程式: 3 TIA T 3 i, s 3 s 3 ) BW f ( A A × γ × α = = (4. 11) 將α=2,β=2.11,γ=3.2代入方程式(4. 3)、方程式(4. 7)和方程式(4. 11)中,針對不同的 fT/BWTIA作圖,如圖 4. 2所示,發現轉阻放大器的頻寬越大時,雙級串聯的架構比三級 串聯的架構可以提供較大的電壓增益,例如,當fT/BWTIA=10時,雙級電壓增益約為三 級電壓增益的1.5倍。所以在設計高速的轉阻放大器時,雙級的架構具有較高的電壓增益 來提昇轉阻放大器頻寬的優點,然而單端式的架構卻無法實現雙級串聯的轉阻放大器, 所以我們提出使用雙級串聯差動式轉阻放大器的架構,如圖 4. 3所示,不僅可以達到提 升開迴路電壓增益的功能之外,差動式架構具有較佳的供應電源與基板雜訊的抵抗能 力,所以我們採用雙級差動式架構來設計10Gb/s之光接收轉阻放大器。

圖 4. 1 (a)單級放大器(b)雙級串聯放大器(c)三級串聯放大器

圖 4. 2 最大電壓增益曲線圖

4.2.2 系統架構

10Gb/s之光接收轉阻放大器的整體系統架構如圖 4. 4所示,包括了一個檢光二極體 ﹙PD﹚、一個雙級的差動轉阻放大器﹙T2﹚、雙負回授直流偏壓控制電路、和一個輸 出緩衝器(BUF)。偽差動式輸入

如圖 4. 4 所示,只有單輸入端有輸入訊號的架構為偽差動式輸入。僞差動式架構可以透 過無訊號輸入端的負載電容與檢光二極體(PD)寄生電容的互相匹配,使得轉阻放大器具 有較高的頻寬。相較於單端式轉阻放大器,運用雙級串聯放大器來設計高速轉阻放大器 時,唯有差動轉阻放大器才可以使用雙級來同時達到開迴路增益提升與隔離第一級放大 器輸出負載與回授電阻負載的功能,除此之外,差動放大器還擁有較佳的Power Supply Rejection (PSR) 特性。 圖 4. 4 系統架構雙級差動轉阻放大器

使用先進CMOS 製程時,低供應電壓(supply voltage)對於電路效能的影響是越來越嚴重 了。光纖類比前端接收器電路必須把檢光二極體與轉阻放大器整合在一起,一般的檢光 二極體在高速工作時,需要提供給它適當的偏壓,此偏壓通常是透過供應電壓和轉阻放 大器電路之間所供給的,由於輸出端的偏壓會透過回授電阻連接至輸入端,導致輸出端 的headroom 遭受檢光二極體所需偏壓的壓縮,同時放大器會因為低 headroom 而有較低 的開迴路增益與較高的輸入阻抗,頻寬因此無法提升。對於開迴路增益不足的問題,我

們使用雙級串連放大器的設計可以獲得解決,透過雙級電壓增益的相乘,再加上回授電 阻沒有限制第一級輸出的 voltage headroom,使得雙級放大器可以在不增加輸出端負載 電容而能提升系統的開迴路增益與頻寬。除此之外,使用不消耗輸出 headroom 而能增 加頻寬的shunt peaking 補償技術[14] 。 方程式(4. 12)為雙級放大器串聯的轉移函數,為了提供足夠開迴路電壓增益來降低 輸入阻抗,所以我們設計每級的開迴路增益大約為3,雙級放大器相乘後的開迴路增益 為9,由方程式(4. 13)與方程式(4. 14),推算出我們設計每一級放大器所需要的頻寬,將 串聯後的頻寬 12GHz(BWtot)和 n=2 代入方程式中,得到每一級放大器的頻寬需要設計 18.6GHz(BWstage)。

(

A 9)

) 1 ω s ( A ) 1 ω s ( A (s) 2 A (s) 1 A (s) A 2 2 1 v = + × + = × = (4. 12) 串聯級數 = − =BW 2 1 n BW 1n stage tot (4. 13) cell pd f 2 tot BW C π R 2 A 2 BW = ⇒ (4. 14)雙回授直流偏壓控制電路

為解決檢光二極體所造成的輸出端直流位準漂移問題,系統架構包含兩個比較器和兩個 可控制電流源的雙回授直流偏壓控制電路,主要是透過比較器偵測流過負回授電阻的直 流電流,然後控制輸入端電流源的直流電流大小,此負回授特性造成檢光二極體的直流 電流無法流入回授電阻,所以解決了直流位準漂移的問題,可有效改善大訊號波型失真 的現象以及動態範圍的提升。除此之外,這兩個比較器設計具有0.1V的直流偏移(Vos), 造成差動轉阻放大器輸出端比輸入端低0.1V的直流位準,也就是說,輸出端增加0.1V的 headroom可以等效提昇差動轉阻放大器的開迴路增益與輸入端頻寬,對於直流偏移大小 的選擇,必須考量輸入端可控制電流源對系統所增加的雜訊,因為直流偏移的大小決定 輸入端可控制電流源的大小。緩衝器

介於轉阻放大器與輸出級之間的電路必需是一個具有高頻寬的緩衝器,所以主動式負回 授之技術[20] 和shunt peaking可運用在緩衝器上,使緩衝器可以擁有高頻寬的效能。4.3 電路設計

4.3.1 偽差動式輸入架構

圖 4. 5 偽差動式轉阻放大器 圖 4. 5 是一個偽差動式轉阻放大器等效小信號模型,此電路是一個單端信號源輸入的架 構,電容Cp 為檢光二極體的負載電容,電容 C 為沒有信號輸入的負載電容,以及回授 電阻Rf和輸出負載電阻 RL。對於轉阻放大器輸入端的負載電容 Cp 和 C 的比例會影響 電路的頻寬和特性,為了找到設計上的最佳點,我們利用此小信號模型進行轉移函數推 倒,方程式(4. 15)是偽差動式轉阻放大器等效小信號模型的轉移函數,此函式為二階系 統的特徵方程式。 ) R g 2 1 ( )] R R ( R g R R )[ C C ( s ) R R ( CC s ] R g R g 1 ) R g 1 )( R R ( sC [ R V L m L f L m L f p L f p 2 L m f m f m L f L 1 o + + + + + + + + + − + − + = i (4. 15) 經由求根公式,可以解出兩個極點,分別為方程式(4. 16)和方程式(4. 17),其中 R=(Rf+RL) : p 2 p L m 2 p 2 L 2 m p L m p 1 p RC 2 ) 1 C C )( R g 2 1 ( ) 1 C C ( R g ) C C ( ) R g 1 )( C C 1 ( ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ − + + + − + + = ω (4. 16) p 2 p L m 2 p 2 L 2 m p L m p 2 p RC 2 ) 1 C C )( R g 2 1 ( ) 1 C C ( R g ) C C ( ) R g 1 )( C C 1 ( ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ − + + + + + + = ω (4. 17) 方程式(4. 15)的分子可求出一個零點為方程式(4. 18) :p p L f f m L m f m 1 z RC 1 ) C C ( RC 1 C ) R R ( 1 R g 1 R g R g 1 × = ≈ + × ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ − + − = ω (4. 18) 由以上推倒的方程式可以發現極點和零點的大小關係取決於gmRL大小以及C/Cp 的比例 關係。為了簡化分析,假設在固定的gmRL之下,以不同電容C 和電容 Cp 的比例代入, 可以得到不同極零點的關係,也就是說電容C 設計的大小影響到電路系統的頻寬。 圖 4. 6 是先將 gmRL=5 代入方程式(4. 16)、方程式(4. 17)和方程式(4. 18)中,再以不 同C/Cp 比例值代入所對應的極點(pole)和零點(zero)的分佈關係圖。 圖 4. 6 極、零點分佈曲線圖 由圖 4. 6 中可以歸納出三個設計方向 :

(1) 當電容 C 越小於電容 Cp 時,pole 2 會越來越大,但是 zero 1 比 pole 1 大,導致極零 點無法互相抵消,使得電路的3dB 頻寬由 pole 1 決定。

(2) 當電容 C 等於電容 Cp 時,pole 1 可以和 zero 1 互相抵消,使系統的 3dB 頻寬由 pole 2 大小決定。

(3) 當電容 C 越大於電容 Cp 時,pole 2 逐漸下降,而且 zero 1 比 pole 1 小,此時電路形 成一個帶通放大器,使系統的高頻3dB 頻寬仍由 pole 2 決定。

為了驗證公式推導的正確性,圖 4. 7 是 3 種不同設計方向的頻率響應模擬。當 C=0.1Cp 時,如歸納的方向(1),雖然 pole 2 =13GHz,但是因為 zero 1 比 pole 1 大,所以 3dB 頻 寬由pole 1 決定;當 C=Cp 時,如同歸納的方向(2),因為 pole 1 與 zero 1 的互相抵消, 所以3dB 頻寬由 pole 2 決定;當 C=100Cp 時,如同歸納的方向(3),pole 2 = 1.2GHz, 而且zero 1 比 pole 1 小,形成一個帶通的頻率響應,所以高頻 3dB 頻寬由 pole 2 所決定。 當電容 C 等於電容 Cp 時,此放大器是一個對稱差動式轉阻放大器。當電容 C 比電 容Cp 大 100 倍時,轉阻放大器的無輸入訊號端等效上接地,此負回授路徑無效,此放 大器是一個非對稱差動式轉阻放大器。因為偽差動式轉阻放大器(C=Cp)的 pole 2 比非對 稱偽差動轉阻放大器(C=100Cp)的 pole 2 大 2 倍,所以對稱偽差動式轉阻放大器比非對 稱偽差動轉阻放大器具有提升2 倍頻寬的優點。也就是說,設計一個對稱偽差動式轉阻

![圖 3. 14 比較器電路 3.3.3 負阻抗補償之增益緩衝器 圖 3. 15 為所設計的單級增益緩衝器完整電路,此電路是加上負阻抗補償的 Cherry Hooper 電路架構[19] ,其中的電晶體 M r3 M r4 產生負電阻效應,負電容則利用電晶體 M c3 M c4 與電容 C C2 來控制,由於 Cherry Hooper 電路架構是轉導放大級和轉阻放大級的 結合,加入負阻抗補償技術[12] 可以調節其轉阻放大級的輸出阻抗特性,以等效提昇其 轉阻放大器的增益,而且擁有高寬頻的](https://thumb-ap.123doks.com/thumbv2/9libinfo/8212534.170108/33.892.215.727.99.361/與電容來控制由電路架構是轉導放大級和轉阻放大級加入可以調頻的.webp)