國 立 交 通 大 學

資訊科學與工程所

碩

士

論

文

多輸入多輸出的正交分頻多工之

射頻系統整合平台設計

The Design of Integrated Platform for

MIMO-OFDM Systems

研 究 生 : 王淳泰

指導教授 : 許騰尹 博士

多輸入多輸出正交分頻多工之射頻系統整合平台設計

The Design of Integrated Platform for MIMO-OFDM Systems

研 究 生:王淳泰 Student:Chuen-Tai Wang

指導教授:許騰尹 Advisor:Terng-Yin Hsu

國 立 交 通 大 學

資 訊 科 學 與 工 程 研 究 所

碩 士 論 文

A ThesisSubmitted to Institute of Computer Science and Engineering College of Computer Science

National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of Master

in

Computer Science

June 2006

Hsinchu, Taiwan, Republic of China

多輸入多輸出的正交分頻多工

之射頻系統整合平台設計

學生:

王淳泰

指導教授:許騰尹 博士

國立交通大學資訊科學與工程學系 研究所碩士班

摘要

近年來,多輸入多輸出(MIMO)的技術,被廣泛運用於各通訊系統。主要的原因在於 其可提供資料傳輸時的效率和品質。此外,通訊領域中,正交分頻多工(OFDM)的技術, 也由於可提供高速資料傳輸,以及根據頻率之通道選擇的特性,而在通訊領域中,亦佔 有舉足輕重的地位。若能結合兩者的技術來實做一套通訊領域系統,可使得通訊系統的 效能大大提升。 本論文將搭配平台上的各種消除非理想效應之演算法,包含同步封包偵測(packet detection),封包取得(packet acquisition),載波頻率偏移(CFO),等化器(equalizer) 設計的演算法。 本篇論文的重點在於,整合FPGA系統模組和RF系統,並藉由HDL硬體語言,來協助 底層硬體設計的訊號系統整合,將此套2x2的OFDM傳輸系統做實現。FPGA可高速傳輸並 將訊號由類比和數位的格式之間做轉換,並執行高效能傳輸。RF系統可將基頻訊號 (baseband signal)由天線現送出,遭遇多種通道效應(channel effect)後,正確將資料接收。

為了解實作的成效,我們將利用 matlab 軟體來觀察此系統所接收的訊號,並進一

步分析其接收的效能及相關的疑點,來協助此系統更近一步的改善。使得此硬體架構 更趨完善。

The Design of Integrated Platform for

MIMO-OFDM Systems

Student: Chuen-Tai Wang

Advisor: Dr. Terng-Yin Hsu

Department of Computer Science and Information Engineering,

National Chiao Tung University

Abstract

Recently years, MIMO technique is widely used in much communication system. What the main reasons are it accomplish the objects which include performance and quality in transmission data. Besides, OFDM technique is also provides data transmission with high speed and the character that select the channel according to frequency. It still has the important status in communication area.

The thesis will cancel the non-ideal effect by the algorithm on platform, includes packet detection, packet acquisition, CFO compensation and equalizer algorithm.

What the important issue in the thesis is integration FPGA and RF module. Besides, it will integrate the signal and system in bottom level by HDL language and implement the communication system by 2x2 RF module. In the system FPGA can transform the signal between analog and digital type and transmit in high performance. RF module can transmit the baseband signal by the antenna. The signal will meet all kinds of non-ideal channel effect then the receiver antenna will receive the signal and decode them.

In order to test the performance of the system, we will use matlab software to observe the received signal. Besides, further analyze the performance of the received signal and related problem to improve the system. In order to improve the performance more perfect in the system.

Acknowledgment

I would like to express sincerely my gratitude to those people for their invaluable help during the past two years, stayed in Hsin-Chu. Especially, I want to express my deepest gratitude to my advisor Prof. Terng-Yin Hsu for his enthusiastic guidance and encouragement to overcome many difficulties throughout the research, and I give him and his family my best wish faithfully.

Also, I want to thank my ISIP group mates, Ming-Fu Sun, You-Hsien Lin, Wei-Chi Lai, Ta-Yang Juan for their suggestions and great helps during my research. I would like to thank all members in ISIP laboratory for their plenty of fruitful assistance.

Finally, I give the greatest respect and love to my family and all my friend. I express my highest appreciation and dedicate the thesis to them for their assistance and attention during the most important stage in my life.

Chuen-Tai Wang July 2007

Contents

page

中文摘要 ……….…..….i 英文摘要 ………...ii 誌謝 ………..…..…iii 目錄 ………..…...iv 圖目錄 ………....vi Abbreviations……….……….….viii CHAPTER 1 introduction…….. ……….….1CHAPTER 2 MIMO-OFDM SYSTEM MODELS.………...…3

2.1 Matlab Transmitter platform architecture..………...3

2.2 Matlab receiver platform architecture ………...5

CHAPTER 3 PLATFORM DESIGN...…...………...………...6

3.1 Hardware Device...6

3.2 Software System Design…..………..10

3.3 Hardware System Design………..13

3.4 The Implementation of the MIMO-OFDM System...,………15

CHAPTER 4 IMPLEMENTATION RESULT.……….…22

CHAPTER 5 CONCLUSIONS AND FUTURE WORKS ………...34

List of Figures

page

Figure 2-1 MIMO-OFDM 基本傳送端結構……… ………..4

Figure 2-2 MIMO-OFDM 基本接收端結構………...5

Figure 3-1 FPGA 模組系統介面 ……...7

Figure 3-2 Barker Code的Cross Correlation架構………... ….…….10

Figure 3-3 MATLAB支援FUSE toolbox的執行程序流程圖………...…….……..11

Figure 3-4 MIMO-OFDM硬體設計流程圖………...……….……...15

Figure 3-5 MIMO-OFDM系統實現架構……….………..…….…….16

Figure 3-6 MIMO-OFDM實現的傳送端硬體架構圖……….……....18

Figure 3-7 MIMO-OFDM實現的接收端硬體架構圖...…….……….…19

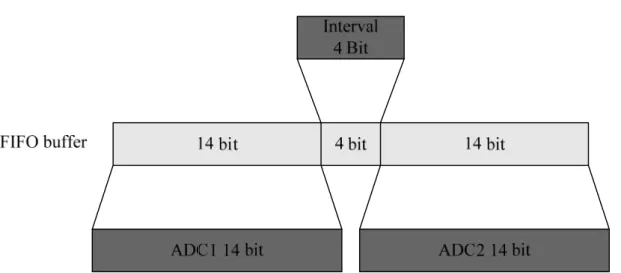

Figure 3-8 FIFO buffer的位元組合示意圖……….………....20

Figure 4-1 FPGA 之間以 MCX 線相連結的系統架構圖……….…..23

Figure 4-2 FPGA 間以 MCX 接線相連的 BPSK 和 QPSK 的 constellation …….…..23

Figure 4-3 FPGA 間以 MCX 接線相連的 16-QAM 和 64-QAM 的 constellation…...24

Figure 4-4 FPGA 藉由 RF 模組經由 SMA 接頭傳輸系統架構圖……….…24

Figure 4-5 FPGA 藉由 RF 模組經由 SMA 接頭相連的 BQSK 和 QPSK………25

Figure 4-6 FPGA藉由RF模組經由SMA接頭相連的16-QAM和64-QAM...25

Figure 4-7 FPGA 藉由 RF 模組經由天線無線傳輸的系統架構圖………....27

Figure 4-8 RF 模組經由天線無線傳輸的 BPSK 的 constellation 和 CFR ………27

Figure 4-9 RF 模組經由天線無線傳輸的 QPSK 的 constellation 和 CFR…..……..…28

Figure 4-10 RF模組經由天線無線傳輸的16-QAM的constellation和CFR…..……...28

Figure 4-11 RF 模組經由天線無線傳輸的 64-QAM 的 constellation 和 CFR……..…28

Figure 4-12 FPGA 藉由 RF 模組經由天線 2x2 無線傳輸系統架構圖………..….29

Figure 4-15 2x2天線無線傳輸的16-QAM的constellation和CFR………..31

Figure 4-16 2x2MIMO-OFDM系統的CFO補償示意圖………...31

Figure 4-17 傳送端與接收端的影像圖比較………..……….…………...33

Figure 4-18 MIMO-OFDM傳輸系統實現圖………...33

Abbreviations

AWGN additive white Gaussian noise

BPSK binary phase shift keying

CFO carrier frequency offset

DFT discrete Fourier transform

DVB-T digital video broadcasting terrestrial TV

FFT fast Fourier transform

IFFT inverse fast Fourier transform

I/Q in phase/quadrature phase

I/Q-M I/Q mismatch

FDI frequency dependent imbalance

LO local oscillator

MIMO multi-input multi-output

OFDM orthogonal division frequency modulation

PER packet error rate

PPDU PLCP protocol data unit

PSDU PHY service data unit

RF radio frequency

SNR signal-to-noise ration

第一章

導論

隨著通訊科技的發展,無線網路在現今的社會,逐漸佔有舉足輕重的地位。802.11a 的 OFDM 在通訊系統中,佔有舉足輕重的地位,由於其包含高頻寬利用率以及抗雜訊 (noise)的優點,更具有更高的資料傳輸速率,使 OFDM 的技術能迅速為市場所接受。 OFDM藉由多重子載波(sub-carries)來傳送調變訊號,亦藉由延長其符元週期(symbol duration),更增加系統穩定性和載波頻寬的利用度。所有的子載波在傳送時,皆已正交 的方式來傳輸,避免子載波的訊號之間互相干擾,而在OFDM的同步和頻道估計則依 靠PLCP的preamble來實做。這些特性已經廣泛用於各種OFDM傳輸系統,例如: 802.11a/g 的無線區域網路系統,數位影音傳輸系統(DAB, DVB-T)。 然而,不幸的,OFDM系統對於非理想的同步效應可能造成系統效能嚴重驟降。因 此,傳送端和接收端之間極易受到載波頻率偏移(CFO, carrier frequency offset)的影響,期間亦包含區域振盪器的所產生的相位以及頻率的誤差,所產生的內部復載干擾(ICI, inter-carrier interference),在OFDM系統的接收端中,為了解決此類的困擾而造成系統

效能驟降,本身則需要做精確的通道估計和相位追蹤來決定其正確的符元週期。

另外,MIMO (multiple-input multiple-output)是一種現階段嶄新的傳輸技術,可在不 提高頻寬的情況下,藉由多根傳送和接收端天線,傳送個別獨立的資料串列,以提昇

系統的多樣性和頻譜利用率。此外,藉由兩根天線傳輸資料,更能大幅增加系統的穩 定性以及安全性,當其中有天線在傳輸時損壞無法正常運作時,亦可藉由另根天線來

傳送資料,保證系統不會因此無法運作。

而本論文將對於 MIMO_OFDM 的 2x2 無線傳輸系統進行實做,而其中應用到的模 組有 FFT、AFC、和時脈同步…等。設計的系統模組,則包含了 FPGA、DAC、ADC、

USB、RF 傳送接收模組,以及 DMA…等。此藉由 FPGA 來實做的平台,將會搭配硬 體描述語言設計和 MATLAB 軟體語言的分析,並進一步改善此系統的效能。 在本論文的第一章將做簡單的概論介紹。第二章便回對於MIMO-OFDM系統模型架 構,包含傳送端,接收端的編碼解碼過程,做整體架構上詳細的描述。第三章將會對 於整體系統的設計,分為軟體層面設計和硬體層面設計來說明。第四章陳述此系統架 構所執行的效能,以及各種參數造成接收到的訊號相關層面的影響。第五章將會對此 論文做最後的總結,以及未來可進一步發展的方向。第六章,則會補充說明本系統的 實現,參考到的相關書籍以及論文。此即本論文的架構。

第二章

系統平台

在本章節將會介紹802.11n的傳送和接收端的系統區塊,以及通道產生的效應。傳

送端將訊號經過多種編碼方式後,即可將基頻訊號由射頻裝置送出。而通到效應的影

響,將使得訊號受到各種相關效應的干擾,其中包含附加性白色高斯雜訊(AWGN,

additive white Gaussian noise),載波頻率偏移(CFO, carrier frequency offset), 多通道效

應(Multi-path),相位雜訊(Phase Noise),取樣時脈偏移振盪器(SCO),IQ不平衡效應 (IQ-mismatch)…等等。最後,將由接收端將經由通道效應所影響的訊號接收後,逐步進 行解碼。 MIMO-OFDM支援四種調變方式,包含BPSK,QPSK,16-QAM,64-QAM。而其 編碼速率亦有1/2、2/3、3/4、5/6等,共四種編碼速率,和2x2或4x4兩種方式來傳送和 接收訊號。

2.1 傳送端架構

欲傳送資料會經由FEC編碼器進行編碼,如convolution encoder。而在下一個階 段,puncture區塊會由 1/2、2/3、3/4、5/6 選定特定的編碼速率,便將此選定的資料部 份,傳送至spatial parse以便將訊號分布成多個空間資料串流。對於每個串流中,每個區塊的位元資料,交錯(Interleaved)處理後,便會對應到單一的OFDM的符號,此步驟 即稱為“frequency interleaving”。此步驟很類似 802.11a中的交錯(Interleaver)。再來,將

訊號經過QAM-mapping,將資料經過處理後,會執行調變的工作,如同: BPSK、QPSK、 16-QAM、64-QAM以及 256-QAM。而在本套系統中,將會選定 16-QAM和 64-QAM

兩種調變模式分別進行傳送。資料會被送至,Alamouti STBC進行編碼。在STBC中, 調變的訊號會根據k根傳送端天線數量分隔成k個資料串流,即NSTS = k NSS,若是單天 線的情況,則不需要STBC區塊,亦即k=1。而其方程式表示如下: NSTS = ⎪⎩ ⎪ ⎨ ⎧ used is STBC kN used not is STBC N SS SS

{

}

而在MIMO系統中,期中的關係必須遵守NSS ≤ min N NTx, Rx ,NTX和NRX分別代表傳 送端和接收端的天線數量。 經過 STBC 處理的資料會被送至 IFFT 的區塊,此時,訊號將由頻域 (FrequencyDomain)轉為時域 (Time Domain)。每個 OFDM 的符元都會有 64 個子載波,其中有 52

個資料載波和4 個引領載波(pilot carrier),其餘則為空載波。再來,訊號便會由 DAC

將資料送出,其示意圖如圖2-1: FE C e nc oder pun ct u re sp a tia l p a rse frequency interleaver frequency interleaver

spatial streams Space-time streams antenna streams QAM mapping QAM mapping STBC IFFT IFFT Insert GI Insert GI analog & RF analog & RF … … … … … Figure 2-1 MIMO-OFDM 基本傳送端結構

2.2 接收端架構

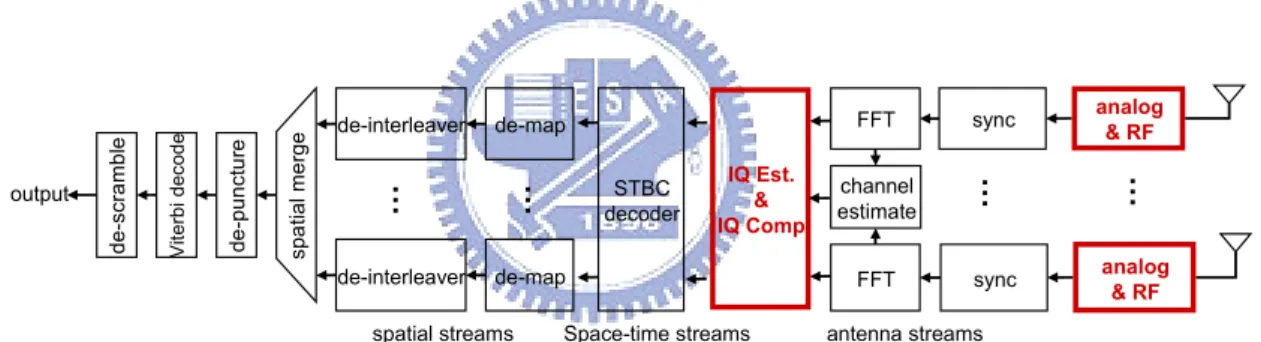

訊號經由ADC模組順利收下後,會先經由演算法的同步機制,判斷此訊號是否包 含資料的成分,以便正確將訊號接收下來。在一般的同步處理機制下,將會週期性的對 訊號進行取樣,並取在提升取樣(Up-Sample)過後的訊號的尖峰值,以正確判別此訊號 的大小。再來,相異於傳送端,接收端會藉由FFT將訊號由時域轉換至頻域處理。另一 方面,等化器(equalizer)會補償訊號通過通道所產生的失真,並由Alamouti Decoder將多 個資料串流合併成單獨一份資料後,在經由設計的演算法分析解碼,其接收端架構表示 如圖2-2。 sync sync channel estimate FFT FFT STBC decoder de-map de-map de-interleaver de-interleaver spa tial me rge de -pun ctu re Vi ter bi dec ode de-scra m bl e output … … … analog & RF analog & RF IQ Est. & IQ Comp. …spatial streams Space-time streams antenna streams

第三章

平台設計

本章節將介紹此平台的設計方式,其中又可概分為硬體和軟體兩種層面來探討。首 先,硬體方面將選用FPGA來實做,其相較於ASIC的實做,具有更大的彈性修改空間, 更能在短期內偵測出演算法的效能是否符合預期。然而,利用FPGA設計的缺點在於, 其消耗更多電力,對於較複雜的電路亦不容易處理。在本論文選用Xilinx公司所設計之 XC2VP30的FPGA版來實作此系統。近年來,由於其高速運算效能的特性,FPGA已經 被用來實做許多較複雜的電路,如: FFT,Convolution編碼器,效能皆較傳統微處理器 為佳。再來將會介紹此系統的設計應用的模組,包含FPGA(Filed Programmable Gate

Array)、直接記憶體存取裝置(DMA, Directly memory access)、數位轉類比轉換器(DAC, Digital to analog converter)、類比轉數位轉換器(ADC, Analog to digital converter)、

USB(Universal Serial Bus)以及傳送端接收端射頻模組(RF, radio frequency)…等。第一節 將會詳細敘述使用到的FPGA內部模組和設計架構。第二節將會敘述硬體層次和軟體層

次的設計。第三節將詳細描述除錯時的相關設備以及裝置。

此FPGA 內分別有獨立雙通道的數位轉類比轉換器(DAC)和類比轉數位轉換器 (ADC),普遍可常見於用來傳輸 HDTV、影像傳輸以及 3G 網路…等。而在本系統中

將利用此DAC 和 ADC 模組來傳送和接收訊號。而將以 DMA 處理器作為主要傳輸和

處理資料的媒介。此外,亦會藉由軟體的寫入和讀取觸發,與FPGA 的系統開發硬體

版做溝通。然後,皆下來的章節,將會對於整體的系統每個應用模組做詳細的敘述。

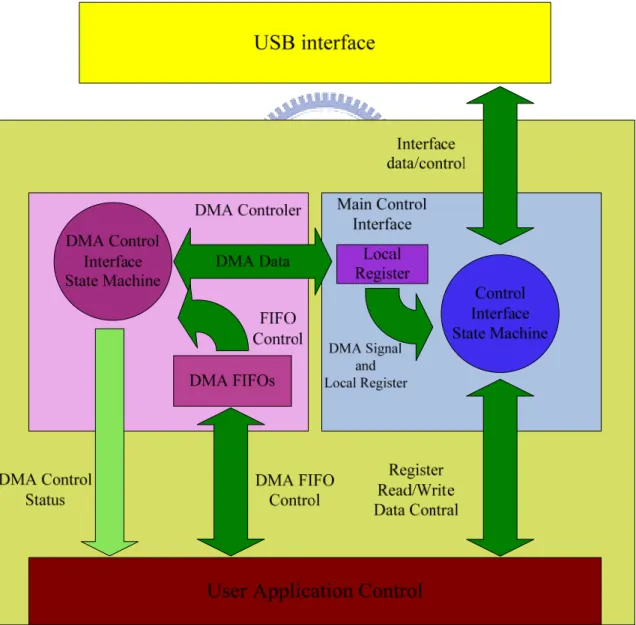

3.1.1 FPGA傳輸介面架構

上圖是此FPGA系統傳輸資料的流程圖。由此圖可知,欲藉由軟體應用程式中,遞

送欲傳輸的資料,可藉由USB傳送至FPGA後,並經過兩種傳輸介面,分別為圖右的讀 取寫入暫存器控制(Register Read/Write Data Control)和圖左的DMA傳輸控制介面(DMA

Control Status)。本設計則挑選DMA處理器為主要傳輸控制介面。其主要原因如下: 1. 資料量大 相異於暫存器存取,可由圖中架構得知DMA控制器可將資料儲存於FIFO buffer中, DMA處理器能準確控制資料的起始和傳輸過程,並藉由握手(Handshake)協定來進行資 料傳輸。若設定傳輸和接受時脈皆為30Mhz,亦即時脈為33(ns),若需傳送214筆資料, 只需要33x214(ns)。若藉由暫存器傳輸資料,則需要宣告某特定暫存器,並利用軟體執 行 for 迴圈呼叫214次,此行為須藉由軟體交錯執行,極度浪費時間。 2. 記憶體數量 若藉由DMA處理器來存取資料,則好處在於,如前述,可將預存取資料儲存於FIFO 匯流排中,而無須在硬體設計中而外手動設計匯流排。反之,若藉由暫存起來傳輸資料, 則需要在硬體中設計相對應數量的匯流排來存資料,極度消耗硬體SRAM的容量。在本 FPGA系統模組中,其支援32MB的記憶體空間,以供軟體做寫入讀取。 3. 可測試性 在FPGA測試期間,嘗試及除錯是不可避免的。然而,若以暫存器存起設計為主要存 取介面,硬體設計龐大,修改設計後,執行合成以及驗證以及生成位元檔(Bitfile)時, 往往極度消耗時間。而相對於DMA,已內建硬體匯流排,在合成以及驗證時,不需花 費額外的時間來生成匯流排,時間相對快速許多,大大節省除錯所花費的時間。 4. 搭配射頻模組

圈,並執行暫存器寫入指令。而此過程需要軟體語言來協助for迴圈的運作,因此會成 為其傳輸速率的瓶頸。而無法順利通過RF模組。然而,若以DMA處理器來處理輸入的 資料,則可一次便將資料寫入FPGA系統中,軟體便不會造成送出資料速率的瓶頸,便 可順利由射頻模組送出。

3.1.2 數位轉類比轉換器(DAC)和類比轉數位轉換器(ADC)

FPGA 系統模組其內建雙獨立通道的數位類比轉換器(DAC)和類比轉數位轉換器 (ADC),其規格如下:1. DAC 的晶片為 DA9772A,DAC 的晶片為 AD6645

2. 其支援的時脈為 20MHz 到 120MHz 3. DAC 和 ADC 皆提供 14 bit 的資料準確度

在本系統將會藉由軟體層次將訊號分解為I 和 Q 兩 Channel 來傳送,分別將訊號送

至DAC Channel 1(簡稱 DAC1)和 DAC Channel 2(簡稱 DAC2),分別由接收端的 ADC

channel 1(簡稱 ADC1)和 ADC channel 2(簡稱 ADC2)收下後進行處理。

DAC 的部份,主要負責控制傳送端的訊號處理,亦須同時確保兩頻道的輸出時間 相等。因此,傳送端可依靠暫存器訊號觸發,藉由使用者達到同步的功效。

ADC 的部份,主要負責控制接收端的訊號控制,為確保訊號能準確達到同步的功

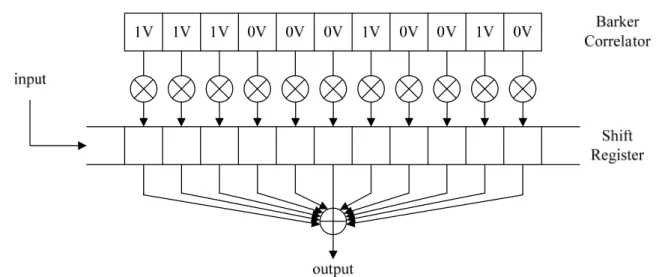

效,並同時接收。接收的條件由Barker Correlation 的原理來實做。根據向上取樣

(Up-Sample Rate)速率為 4,且 ADC 和 硬體將設計一套 11 x 4 x 14 = 616 位元的移

位暫存器,每次由ADC 輸入 14 位元的資料,並位移暫存器的值全部左移 14 位元,

並做Cross Correlation,直到其輸出的乘積大於初始的瓶頸值(Threshold Value),即代

其示意如下:

Figure 3-2 Barker Code 的 Cross Correlation 架構

3.1.3 射頻(RF)模組

射頻模組分為傳送端與接收端,傳送端射頻模組支援輸入-1~1V的訊號,接收端則 輸出-1~1V的振幅。此外,射頻模組由於其內建電桿元件,電桿屬於低通濾波器(Low Pass Filter),會過濾低頻訊號,使低頻訊號無法順利通過射頻模組。根據測量結果,若訊號 頻率低於300Khz,則訊號無法通過。射頻模組裝置如下圖:3.2 軟

體系統設計

為協助傳送端和接收端訊號的編碼和解碼過程,MATLAB軟體可提供快速的 平台系統整合。然而,Xilinx廠商有提供MATLAB相關的FUSE Toolbox,使得使用者可以藉由MATLAB軟體,並存取FPGA系統,引入硬體的設計後,即可執行硬體設計的運 算。

下圖為系統平台與FPGA系統溝通的資料傳輸流程圖:

Figure 3-3 MATLAB支援FUSE toolbox的執行程序流程圖

軟體架構會執行以下動作來控制並與FPGA系統連結: 1. Config Device: 系統會抓取與PC相連結的FPGA系統數目,並分別給予每個FPGA系統特定專 有的ID,提供PC辨認和呼叫。 探討本系統而言,應該會有三片FPGA提供傳送端系統辨認,以及兩片FPGA 提供接收端系統辨認。

2. Download Bitfile: 如同在前述章節說明,可藉由硬體語言設計電路,並產生位元檔(Bitfile)。此 步驟即可引入已產生的位元檔(Bitfile),根據每個FPGA的ID,載入指定的FPGA系 統,即可對FPGA系統引入特定的設計,而驅動FPGA硬體執行。 在傳送端的三片FPGA系統中,傳送資料的兩FPGA,可引入相同的傳送端硬 體架構,並經由第3片FPGA,引入同時驅動DAC模組的硬體裝置,驅動傳送端兩 片FPGA。 在接收端的兩片FPGA系統,將負責正確的將完整的資料封包接收,因此可將 兩FPGA引入相同的硬體架構,並分別根據RF對訊號敏感度,設定相異的Threshold 值即可。

3. Set clock rate:

此步驟會設定整個FPGA系統的工作時脈(Clock rate), DAC, ADC的傳送和接收 時脈,以及系統存取時脈。 本系統為簡化硬體的複雜度,工作時脈,DAC的傳送時脈和ADC的接收時脈 皆控制在30Mhz。 4. Reset Device: 執行此步驟,系統將會初始化FPGA內部循序(Sequential)邏輯裝置。此步驟藉 由matlab軟體部分執行的好處在於,在執行時,無須考慮系統內部時脈的相互運作 影響。換句話說,若系統接收完整一份packet封包以後,可立即執行Reset指令,等 待接收下一個封包。此外,值得一提的是,每次重新傳送一次資料時,執行Reset 指令的時間較為快速,儘可能減少軟體拖延系統和硬體之間的互相等待的情形發 生。

此步驟運作於,硬體系統全部初始化之後。包含的行為主要有: 寫入資料、讀 取資料、讀取暫存器以及確認系統的行為等等。而此階段執行的行為,完全取決於 Verilog HDL所撰寫的內容,經由第2個步驟中的Bitfile,來執行FPGA的資料傳輸呼 叫的動作。 6. Close Device: 待系統執行結束後,需對於FPGA執行Close Device。否則,直接將USB接面拔 除,可能會造成系統非預期的錯誤。若執行Close Device指令後,又須要執行傳輸 系統,再次抓取系統連結的FPGA裝置即可。

3.3

硬體系統設計

本節將由設計層面探討設計的架構,硬體語言方面,常見的硬體語言包含Verilog 和VHDL兩種最為常見。本設計將以Verilog語言為主,主要用途用來控制FPGA系統以 及內部的相關的模組,包含數位轉類比轉換器(DAC)、類比轉數位轉換器(ADC)、直接 記憶體存取模組(DMA)以及暫存器(Register)…等。 為控制FPGA系統的行為,系統將藉由ISE 6.2版電路模擬軟體,搭配Verilog以及電 路設計圖,設計出符合預期功能的電路架構。 設計電路過程中,可概分為三個步驟: 1. Verilog Design: (1) Design Entry: 設計者會將欲設計之電路圖,以Verilog HDL的語言,用RTL code的方式,描述 電路架構行為。 (2) Schematic:

配邏輯元件,實現邏輯線路。

(3) Synthesis:

合成此電路架構,此過程可合成的元件包含: IOB, IO buffer, MUX, flip-flop, latch, Timing Constraint, Area, gate conunts。

2. Implemente Design: (1) Translate:

此過程將Verilog Code中,呼叫其內建的Function,轉換成邏輯電路,ex: FIFO

buffer, Memory, ROM.

(2) Mapping:

此過程可將設計之電路input和output接腳對應至FPGA系統的IO port。

(3) Place & route

此將會對最佳化FPGA系統電路板接線的線路。

3. FPGA module: (1) Bit File Generated

經由電子設計自動化工具(Electronic Design Automatic Design Tool)軟體合成所 設計之電路,在此階段可產生相對於此硬體設計的位元檔(Bit file)。吾亦可利用 此位元檔在matlab中,控制FPGA系統版的行為。 (2) Config Device 此過程可將設計之線路行為,載入FPGA的系統。 (3) Action 此過程可執行硬體設計之動作,包含傳送訊號的時程,接收訊號的條件,以及 資料數量。 MIMO-OFDM硬體設計流程圖及驗證過程如下:

Figure 3-4 MIMO-OFDM硬體設計流程圖

3.4

MIMO-OFDM系統之硬體實現

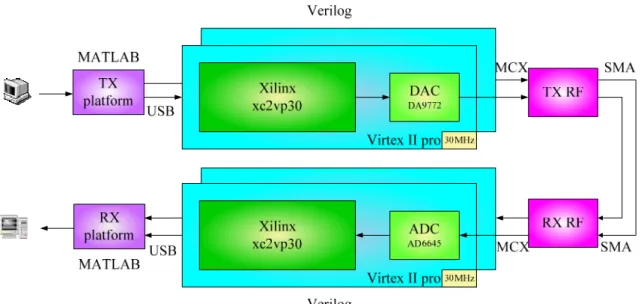

吾將搭配FPGA和RF來實現MIMO-OFDM之系統。其架構大致上可分為傳送端 (TX),接收端(RX),兩大部分。其概略圖描繪如下:

Figure 3-5 MIMO-OFDM系統實現架構 如圖所示,架構可概述如下: 1. 傳送端會藉由電腦執行MATLAB軟體,會根據產生欲傳送之訊號格式,來設定 相關的參數,例如: PSDU,資料長度,編碼類型,調變格式以及資料內容…。 2. 由MATLAB產生資料後,會執行與呼叫FPGA,並經由USB將資料寫入FPGA中。 3. 利用模組化的特性,經由Verilog HDL的設計,期間亦可調整電路的架構和擴充 硬體的設計,若合成時對於設計有需要改良,即可重新更改RTL code,並合成, 省去大量的測試時間。確定設計符合需求後,再將寫入FPGA的資料,由DAC 送出,轉為類比訊號。 本MIMO_OFDM系統著重於2x2的架構,實現電路的架構上,傳送端的2根天線 具有相同的FPGA硬體傳送端架構,由MATLAB分別判斷兩FPGA系統,並確認 寫入特定FPGA的資料。對於展望未來4x4, 8x8的硬體架構上,亦可在傳送端四 根天線引入相同的硬體架構至FPGA中,使實現的效益上更有彈性。 4. 經由傳送端RF可將基頻訊號送出,並由接收端的RF天線收下訊號,根據簡易的

號,則收下受到通道雜訊(Channel noise)影響的訊號,並儲存至FPGA內部的儲 存裝置。 5. 如同傳送端的FPGA硬體設計,接收端亦架構於模組化的特性之上,由硬體 Verilog HDL語言設計一套屬於接收端架構的硬體模組,其中包含各項硬體模 組,為增加可擴充性,硬體架構均設計為可參數化,若設計上有需要,隨時可 更改其硬體模組的大小和寬度,儲存更多資料點數。 6. FPGA中儲存的資料,會由MATLAB執行指令後,由DMA取出,並根據接收端 平台的參數設定,傳入MATLAB系統平台,解除其受到通道雜訊(Channel noise)

造成的非理想效應,EX: 時間同步,載波頻率偏移(CFO),碼間干擾(Inter Symbol

Interference, ISI),載波間干擾(Inter Carrier Interference, ICI)…等,還原資料的型

態,解碼並分析此資料型態和數值。

之後的章節,吾將對於系統各模組的硬體系統的實現過程和成果詳細介紹。

3.4.1 傳送端硬體架構

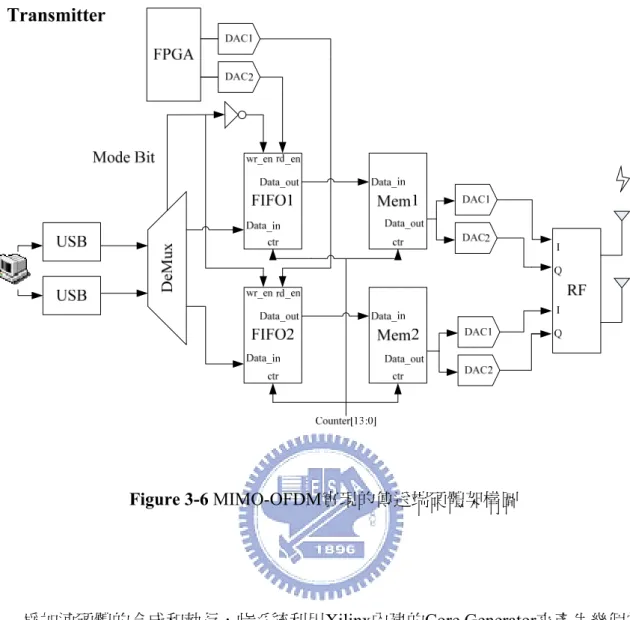

Figure 3-6 MIMO-OFDM實現的傳送端硬體架構圖

為加速硬體的合成和執行,此系統利用Xilinx內建的Core Generator來產生幾個常用

的模組,其中包含FIFO buffer和Memory。其中,實現FIFO的目的在於,可儲存經由USB 介面傳輸的寫入資料,兩FIFO buffer皆保留14 bit寬的Buffer,長度為16384筆資料。在

MATLAB平台的部份,可分別根據Mode Bit的判別位元,分辨先後順序,將欲送出一個 Packet的資料寫入FIFO1和FIFO2儲存。 為了保證兩訊號由DAC送出的時間相同,FIFO1和FIFO2的允許讀出(rd_en)訊號不 可由MATLAB直接控制,由於MATLAB語言為循序執行,須避免此先後關係。因此, 本系統在控制MIMO_OFDM的傳送端,採用第三片FPGA模組,控制兩獨立DAC通道。 欲傳送端送出資料時,即控制第三片FPGA模組,同時傳送Barker Code,以便驅動第一 片和第二片FPGA模組,的四條DAC通道,將其順利傳送至TX_RF。

封包訊號以前,可將封包訊號存放至Memory中,無須在送出資料後即刻清空,可協助 設計者將封包遞迴傳送,協助除錯。 FPGA模組的工作頻率設定在30Mhz,其最高可支援至120Mhz,DAC的工作傳送頻 率亦為30MHz。DAC和FPGA的工作頻率需要適度搭配,否則傳送時可能產生非預期的 錯誤。

3.4.2 接收端硬體架構

下圖為接收端硬體架構圖:Receiver

FIFO1 rd_en wr_en 0.2V ADC1 ADC2 Read_trigger Data_in USB Data_out FIFO2 rd_en wr_en 0.2V ADC1 ADC2 Read_trigger Data_in Data_out RF I Q I Q USB Figure 3-7 MIMO-OFDM實現的接收端硬體架構圖建立MIMO-OFDM系統接收端架構設計上,為確定14 bit的ADC能順利轉換,避免 訊號在線路傳送過程中,造成大量失真,分析的過程如下: 1. 以訊號線直接連結DAC,並以示波器紀錄其輸出的電壓值。 2. 確認DAC送出的訊號,並通過訊號線路,由ADC的接收端收下後,由FPGA確 認信號強度。 3. 比較傳送端的DAC和ADC兩值或訊號形式,紀錄其衰減情形,以協助在ADC端 補償適度的電壓值還原至原來的信號。 為加速接收端硬體的執行以及合成的過程,接收端實現亦使用Xilinx內建的Core Generator來產生部分的硬體模組,包含FIFO1和FIFO2的FIFO buffer。此FIFO buffer的容

量,亦同傳送端的FIFO buffer,均設計為16384的長度,以及寬度實現為32 bit,RF的兩 根天線皆為獨立通道,將第一根天線訊號收入FPGA的ADC。其中,兩ADC通道ADC1

和ADC2皆有14 bit,收下之後,為節省硬體的花費,一塊FPGA中,僅僅宣告一個32 bit 的FIFO buffer,前14 bit存放ADC1的資料,後14 bit存放ADC2的資料,中間保留4 bit的

區間位元,可避免資料傳輸過程受雜訊干擾而讓兩ADC通道彼此影響,其接收示意圖 描繪如下:

此外,關於同步接收機制的實現,此系統採用Adaptive Cross Correlation的技巧,在 接收端系統初始化(Reset)後,每個時脈觸發(trigger)時,取一個參考點(Reference Point), 待接收5000個點,即可計算平均的訊號強度,此即目前環境的參考雜訊(Reference Noise) 係數。此外,可根據硬體設計一段Barker Code,和收下的訊號執行CrossCorrelation,計 算出其Correlation後的平均乘積(Product Sum),此值即可令為δ。而系統設定的瓶頸 (Threshold)值,即為δ與參考雜訊(Reference Noise)的和,其訊號強度瓶頸值如圖,等式 可參照如下:

Threshold = δ+ reference noise

此設計的好處在於,訊號會受到環境的各種變化而遭受影響,瓶頸值(Threshold

Value)亦可根據隨之更改其參考雜訊(Reference Noise)的係數,具有更大的彈性空間,而 不致於因為環境造成系統同步接收機制崩潰(Breakdown)。

待同步接收條件成立,系統會開始儲存FIFO大小的資料量,在此架構即為16384個 點,即可將FIFO buffer填滿,並將buf_full信號設定為1。

MATLAB初始化後,以忙碌等待(Busy Waiting)的模式,不斷的讀取FIFO buffer容 量大小,若回傳的buf_full信號為1,表示FIFO已存滿資料,通知MATLAB將資料取出

第四章

實現結果分析與討論

為了觀察此MIMO-OFDM的系統,其搭配演算法,FPGA和RF模組後,平台實現的 效能,與最佳和預期的效能是否相符。 實測的演算法將根據以下的參數設計: 1. 系統傳輸頻率: 30MHz 2. CFO補償演算法: 開啟 3. 相位補償(Phase Recovery): 開啟 4. 向上取樣(Up-Sample)頻率: 2倍 向下取樣(Down-Sample)頻率: 2倍 5. PSDU長度: 15006. 同步: Adaptive Cross Correlation 7. 調變(modulation): (1) MCS = 8, BPSK (2) MCS = 10, QPSK (3) MCS = 12, 16QAM (4) MCS = 14, 64QAM 其分析比較此平台效能的主要依據,分別可歸類為以下三種: (一) FPGA之間以MCX線相連結 (不含RF模組)

此設計,主要特色在於,基頻訊號經由PC藉由USB傳輸至FPGA後,將訊號由DAC 送出。經由MCX接線,直接傳送至ADC後,送至PC解碼,其簡易架構描繪如下: Figure 4-1 FPGA之間以MCX線相連結的系統架構圖 此設計最需考慮的狀況在於電壓與平台邏輯值之間的轉換,若調整得當,解碼後的 正確率可達100%。 其constellation圖如下: Figure 4-2 FPGA間以MCX接線相連的BPSK(左)和QPSK(右)的Constellation

Figure 4-3 FPGA間以MCX接線相連的16-QAM(左)和64-QAM(右)的Constellation 觀察圖4-2和圖4-3可發現,其解調變的constellation非常的完整,若直接以MCX接頭 的訊號線,直接連結DAC和ADC的訊號,類比和數位訊號之間的轉換,其間誤差幾 乎不影響解碼的數值,此現象可用來驗證系統正確性。 (二) FPGA藉由RF模組經由SMA接頭傳輸訊號 此設計,相似於(一)的架構。不同在於,訊號經由DAC送出後,需藉由MCX和SMA 的介面,傳送至RF模組。再經由SMA的接線,將2.4Ghz的訊號送至接收端的RF, 並傳送至ADC後,經由PC解碼。

Figure 4-4 FPGA藉由RF模組經由SMA接頭傳輸系統架構圖

此設計有CFO效應,需要開啟CFO補償演算法,無多重路徑(Multipath)效應,訊號 品質較為穩定。整體錯誤率較無線傳輸低,較FPGA直接連結為高。

其constellation圖如下:

Figure 4-6 FPGA藉由RF模組經由SMA接頭相連的16-QAM(左)和64-QAM(右) 經由圖4-5和圖4-6的Constellation可發現,相較於(一)的設計,明顯造成Constellation 較為模糊。主要原因在於,接上RF模組後,訊號再RF傳送端送出後,訊號的頻率 提升為2.4GHz,在接收端在降頻為30MHz,而此執行過程,即會造成訊號CFO效應 的增益。開啟CFO演算法,可適度補償接收端收到的訊號Constellation旋轉的現象, 避免資料解碼錯誤。多路徑效應(Multipath)方面,由於訊號的Channel僅侷限於訊號 線中,因此無多路徑效應現象產生。 (三) FPGA藉由RF模組經由天線無線傳輸訊號 此設計相異於(二)的架構在於,RF的傳送端和接收端模組,訊號不在經由SMA接線 轉換,而改以天線的方式,無線傳輸。受到的非理想效應極為明顯。其描繪如下:

Figure 4-7 FPGA藉由RF模組經由天線無線傳輸的系統架構圖

此設計有CFO效應,需要開啟CFO補償演算法,亦有多重路徑(Multipath)效應,由以下

分析圖可得知。

其constellation和CFR分析如下:

Figure 4-9 RF模組經由天線無線傳輸的QPSK的Constellation(左)和CFR(右)

藉由圖 4-8 到圖 4-11,可發現若藉由天線取代 SMA 接頭的傳輸線,其每張圖的 Constellation 具有明顯的旋轉情形,此可得知,受到 CFO 的效應較(三)的設計為嚴重, 若不開啟CFO 補償的效應,會造成系統無法順利解資料。 (四) FPGA藉由RF模組經由天線2x2無線傳輸訊號 此設計,即為本系統最完善的架構,相異於(三)的地方在於,RF的傳送端將同時傳 送兩根天線的資料到接收端模組,CFO和多路徑效應(Multipath)將更為顯著。受到 的非理想效應極為明顯。其系統架構描繪如下: Figure 4-12 FPGA 藉由 RF 模組經由天線 2x2 無線傳輸系統架構圖 此設計有CFO效應,需要開啟CFO和FEC補償,亦有多重路徑(Multipath)效應,天線和 天線之間的訊號亦會互相干擾。

Figure 4-14 2x2 天線無線傳輸的 QPSK 的 Constellation(上)和 CFR(下) 此設計相較於(三),兩根天線均發送訊號,圖 4-13 的 BPSK Constellation 和 4-14 的 QPSK 的Constellation,明顯較(三)為模糊,此可證明,兩根天線均發送資料時,其所受到的 多路徑效應(Multipath)較為嚴重。在 CFO 效應方面,亦可明顯察覺,旋轉情形更為嚴 重,不易補償,例如圖4-14 相較於圖 4-9 旋轉更為嚴重,亦會造成資料的錯誤率提升, 造成此部分問題的主要原因如下。 實現此2x2 MIMO-OFDM系統中,有一關鍵性的問題在於。首先,可觀察下圖為 16_QAM的Constellation和CFR: Figure 4-15 2x2天線無線傳輸的16-QAM的Constellation(左)和CFR(右)

若傳輸的調變(Modulation)為16_QAM或更為複雜的訊號,可觀察其Constellation發現 其解碼資料非常不易辨認其正確位置,其BER錯誤率約為40%。觀察在此調變的方式中, 受到CFO效應,其Constellation的圖形旋轉非常嚴重。 經由傳輸過程的得知,一般系統中,兩傳送端天線具有獨立的時脈。接收端部分, 亦有兩根天線同步等待接收,其示意圖如下: Figure 4-16 2x2MIMO-OFDM系統的CFO補償示意圖 不失一般性探討接收端第一根天線,根據演算法的設計,會將接收到的訊號,並經 由頻道估計(Channel-estimation)計算CFR值,分析訊號來源的天線為何,如CFR圖所示。 再來,會執行CFO估計(CFO-estimation),對此訊號做CFO補償後,送至STBC解碼。然而, 在此架構中,訊號經由第一根天線收下後,若獨立測試情況下,需要對傳送端第一根天 線補償 6 ppm,第二根天線補償 10 ppm,在此演算法執行CFO估計後,則會對此混合訊 號(傳送端第一根天線 + 傳送端第二根天線)補償其平均值,約為 8 ppm。則對於傳送端 第一根天線則產生補償過多,而第二根卻產生補償不足的情形,導致在較高複雜度的調 變時,受到CFO影響極其嚴重。其解法有以下兩種: 1. 在RF模組方面,利用同一個時脈控制,但仍須考慮可能會有些微的誤差。 2. 不在收下混合訊號後作補償,而等到訊號由STBC分解為兩獨立訊號後,在分別對兩 獨立訊號作CFO估計,獨立作補償。

Figure 4-17 傳送端與接收端的影像圖比較 圖4-17 為,實現此系統後,傳送端的影像與接收端解碼後的影像相互比較,在此,利 用JPG 的圖像格式傳送檔案。觀察此圖形可發現,影像可正確的還原不會受到劇烈失 真影響而無法辨認,吾即可利用此影像的解析圖形,來設計連續的 MIMO-OFDM 影 像傳輸系統。 下圖即為此傳輸系統: Figure 4-18 MIMO-OFDM 傳輸系統實現圖

第五章

結論與未來展望

本研究的主要貢獻描述如下:

1. 實現此MIMO-OFDM無線傳輸系統,以及應用許多通訊理論實現於硬體架構

中,例如: Adaptive Cross Cross-Correlation的同步接收機制。

2. 對於歷屆學長姐的演算法,藉由FPGA和RF模組,更進一步的實現證明,驗證其 效能與最佳值,理論值和實際測量值相比較,包含: 同步演算法、CFO補償、 Phase Recovery、FEC解碼、頻道估計…等。更加提升演算法的價值與說服力。 此外,在未來MIMO-OFDM系統,可能包含4x4、8x8…等,皆可以繼續利用此系統 的傳送端和接收端相同的硬體架構即可,更改軟體演算法部分即可,具有更大的可擴充 性,使得此系統更加穩定及完善。 實現此 2x2 MIMO-OFDM 系統,傳送接收訊號的過程中,最耗效能的部份分別位 於: 1. 藉由 MATLAB 產生欲傳送的訊號部份送至 DAC。 2. 藉由 MATLAB 取出 ADC 的資料並解碼。 簡單來說,此系統藉由軟體與硬體之間的搭配建構而成。若能利用 FPGA 實現前述 2 步驟的動作,而經由硬體直接執行,完全不需要通過 MATLAB 的呼叫或初始化,由

FPGA 系統控制全部的時脈。在傳送端部份,由硬體語言產生訊號格式,引導送出訊

號的觸發時間。在接收端部分,則將 MATLAB 接收端演算法部分,以硬體完全實現, 完全省略 MATLAB 的部份,其中包含: 同步演算法、CFO 補償、Phase Recovery、FEC

解碼、頻道估計…。

期間,需要考慮硬體實現的複雜度,自然不在話下。FPGA 的邏輯閘個數亦須妥善

利用,否則硬體設計將無法完全放置於 FPGA 系統內。然而,藉由完全的硬體實現, 對於效能的提升,絕對有突破性的發展,估計可達到完全即時的效果。

參考

[1] “Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY)”,

specifications, IEEE 802.11b standard 1999

[2] “Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY)”,

specifications, IEEE 802.11a standard 1999

[3] “Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY)”,

specifications, IEEE 802.11g standard 2003

[4] Bernard Sklar, Digital Communications - Fundamentals and Applications Second

Edition, Prentice-Hall Inc., Communication Engineering Services, Tarzana, California and University of California, Los Angeles, 2001

[5] Kan-Si Lin, “The Study of Adaptive Equalization in MIMO-OFDM Systems”, NCTU thesis, 2007

[6] I-Yin Liu, “The Study of Carrier Synchronization for MIMO-OFDM Baseband Designs”, NCTU thesis, 2007

[7] Hsin-Nan Chen, “The Study of Front-end Signaling and Timing Synchronization in MIMO-OFDM systems”, NCTU thesis, 2007

[8] Terng-Yin Hsu, “The Study of All Digital Phase-Locked Loop (ADPLL) and its Applications”, NCTU, master thesis, June 1999

[9] Chih-Sheng Wu, “Joint Design of MIMO-OFDM and MIMO-CDMA Transceivers”, NCTU thesis, 2003

[10] JR-Wei Huang, “FPGA Realization of MIMO-OFDM Transceiver”, NCTU thesis 2003 [11] Yen-Yu Chen, “FPGA Realization of MIMO-OFDM System with Optimized Hardware