逢 甲 大 學

資 訊 工 程 學 系 專 題 報 告

使用8051製作俄羅斯方塊

薛 友 倫 (四乙)

學

生: 徐 得 祥 (四乙)

林 坤 宏 (四乙)

指

導

教

授 : 陳 德 生

中華民國九十一年十二月

目錄

圖表目錄•

•••••••••••••••••••••• III摘要•

••••••••••••••••••••••••• V第一章 導論••••••••••••••••••• 1

1.1 動機•••••••••••••••••••••••• 1 1.2 目的•••••••••••••••••••••••• 1第二章 8051 的架構 •••••••••••••• 2

2.1 MCS-51/52 單晶片簡介•••••••••••••••• 2 2.2 MCS-51/52 晶片介面接腳說明••••••••••••• 2 2.3 MCS-51/52 記憶體結構•••••••••••••••• 9 2.3.1 程式記憶體•••••••••••••••••• 9 2.3.2 資料記憶體•••••••••••••••••• 10 2.4 MCS-51/52時脈輸入•••••••••••••••••• 17 2.5 MCS-51/52的重置••••••••••••••••••• 17第三章 開發環境簡介••••••••••••••• 19

3.1 整體工作流程•••••••••••••••••••• 19 3.2 TS controls 8051 Emulator 軟體模擬器簡介•••••• 21 3.3 PICE 80C52 單晶片線上模擬器簡介••••••••••• 23第四章 繪圖型LCD顯示器模組•••••••••••• 24

4.1 繪圖型LCD顯示器LCG-128064功能介紹•••••••••• 24 4.2 LCG-128064 內部暫存器•••••••••••••••• 25 4.3 LCG-128064 讀寫時序••••••••••••••••• 29 4.4 LCG-128064 控制指令集•••••••••••••••• 30第五章 程式介紹及原理•••••••••••••• 34

5.1 遊戲介紹•••••••••••••••••••••• 34 5.2 程式流程•••••••••••••••••••••• 355.3 按鍵原理•••••••••••••••••••••• 38 5.4 中斷原理•••••••••••••••••••••• 40 5.4.1 MCS-51計時/計數器••••••••••••••• 40 5.4.2 中斷••••••••••••••••••••• 48 5.5 顯示原理•••••••••••••••••••••• 55

第六章 總結••••••••••••••••••• 58

6.1 問題與討論••••••••••••••••••••• 58 6.2 檢討與改進••••••••••••••••••••• 58附錄•••••••••••••••••••••• 59

A 參考資料••••••••••••••••••••••• 59 B 成品照片••••••••••••••••••••••• 59圖表目錄

第一章

第二章

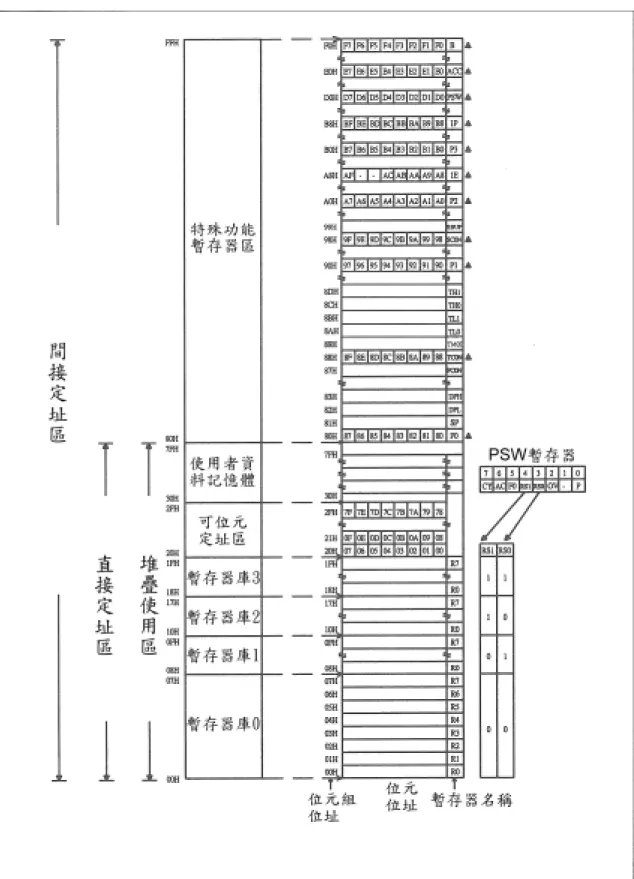

圖2-1 MCS-51 接腳圖••••••••••••••••••• 2 圖2-2 MCS-51 功能方塊圖••••••••••••••••• 3 表2-1a MCS-51 PIN腳詳細說明a•••••••••••••• 6 表2-1b MCS-51 PIN腳詳細說明b•••••••••••••• 7 表2-1c MCS-51 PIN腳詳細說明c•••••••••••••• 8 圖2-3 MCS-51 記憶體結構圖•••••••••••••••• 9 圖2-4 MCS-51內部資料記憶體結構圖•••••••••••• 12 表2-2 特殊功能暫存器•••••••••••••••••• 14 表2-3 程式狀態字暫存器位元功能表•••••••••••• 16 圖2-5 使用內部震盪器接線圖••••••••••••••• 18第三章

圖3-1 程式開發流程圖•••••••••••••••••• 20 圖3-2 選擇燒錄檔畫面•••••••••••••••••• 21 圖3-3 執行TSCE 軟體模擬功能•••••••••••••• 22 圖3-4 PICE連接圖•••••••••••••••••••• 23第四章

圖4-1 LCG-128064 外觀圖••••••••••••••••• 24 表4-1 LCG-128064接腳名稱與功能說明••••••••••• 25 表4-2 暫存器選擇及動作說明••••••••••••••• 26 圖4-2 LCG-128064功能方塊圖••••••••••••••• 26 圖4-3 讀取顯示資料RAM時序圖••••••••••••••• 27 圖4-4 啟動重置時間圖•••••••••••••••••• 29 表4-3 時序圖參數規格•••••••••••••••••• 29 圖4-5 LCG-128064讀寫時序圖••••••••••••••• 30 圖4-6 Start Line和Display之關係圖•••••••••••• 31 圖4-7 顯示資料RAM位址排列方式•••••••••••••• 32第五章

圖5-1 參考遊戲畫面••••••••••••••••••• 35 圖5-2 方塊設定圖•••••••••••••••••••• 36 圖5-3 主程式流程圖••••••••••••••••••• 37 圖5-4 2x2矩陣式按鍵••••••••••••••••••• 38 表5-1 TMOD暫存器位元功能表••••••••••••••• 42 表5-2 TCON暫存器位元功能表••••••••••••••• 43 圖5-5 計時/計數器控制邏輯電路圖••••••••••••• 43 圖5-6 計時/計數器1模式0結構圖•••••••••••••• 46 圖5-7 計時/計數器1模式1結構圖•••••••••••••• 47 圖5-8 計時/計數器1模式2結構圖•••••••••••••• 47 圖5-9 計時/計數器0模式3結構圖•••••••••••••• 48 表5-3 IE暫存器位元功能表•••••••••••••••• 49 表5-4 IP暫存器位元功能表•••••••••••••••• 50 表5-5 中斷優先順序表•••••••••••••••••• 51 圖5-10 MCS-51/52 中斷控制架構•••••••••••••• 51 圖5-11 中斷程式流程圖•••••••••••••••••• 54 表5-6 DPTR驅動繪圖型LCD對照表•••••••••••••• 55 圖5-12 專題實驗電路圖•••••••••••••••••• 57第六章

附錄

圖B-1 LH-056模組照片•••••••••••••••••• 60 圖B-2 遊戲功能介紹••••••••••••••••••• 61 圖B-3 遊戲中畫面•••••••••••••••••••• 62 圖B-4 遊戲結束畫面••••••••••••••••••• 63摘要

這篇報告主要內容包括,單晶片微控制器系統8051(以下簡稱8051) 應用系統的開發環境,8051的架構,繪圖型LCD 模組的架構和鍵盤、中斷 的控制。市面上一般書籍中,有關繪圖型LCD 模組的資料極少,因此使 用者必須花費許多時間來尋找相關資料,十分浪費時間,在本次專題的 研究中我們也因為資料的不足,吃足了苦頭。這份報告中對於繪圖型LCD 模組會就所發現的問題以及解決的方法加以討論,除了詳細的說明外, 並附有完整的原始程式。另外對於8051應用系統的開發環境也有簡要的 介紹, 並且寫下使用上的經驗。相信能夠讓想要開發8051 應用系統的 人減少許多不必要時間。第一章 導論

1.1 動機

自從大二時修習過組合語言,便為這種直接控制CPU動作的程式語 言深深著迷,也開始為CPU的架構產生興趣。大三時,修習了MCS-51的 課程便也對這種將輸出/輸入介面晶片、記憶體晶片等功能整合在一起 (之所以稱之為單晶片的原因)而能獨立作業的單晶片微電腦系統產生 興趣。單晶片微電腦具有電路精簡不佔空間的優點,主要應用在工業控 制及民生消費性產品,如鍵盤、電子秤、防盜器、遙控器等應用相當廣 泛,尤其如今凡事講求自動化降低人力成本,因此我認為單晶片微電腦 有其施展的空間,值得我們好好的研究。1.2 目的

我的專題主要是以坊間常見的益智遊戲—俄羅斯方塊為題,研究學 習以模組上的2x2矩陣式按鍵為輸入,以使用LCG-128064的繪圖型LCD模 組作為輸出顯示,並以計時器中斷讓遊戲進行•除此之外,熟悉開發工 具的使用,如硬體線上模擬器(ICE,In-Circuit Emulator)和軟體模 擬器(如TS controls Emulator 8051),以及熟悉開發的過程,也是 此次專題研究的目的。第二章 8051架構介紹

2.1 MCS-51/52 單晶片簡介

MCS-51/52 為 八 位 元 微 電 腦 , 內 部 有 4/8Kbyte 唯 讀 記 憶 體 (ROM/EPROM)及128/256Byte隨機存取記憶體(RAM),外部RAM和ROM則 可個別擴充到64KB。提供5/6個中斷源並可執行雙層中斷優先規劃功 能,四組並列式平行I/O埠(共32位元),一個全雙工串列埠,並能位元 定址及執行布林運算。下頁圖2-2為MCS51系列晶片功能方塊圖。2.2 MCS-51/52 晶片介面接腳說明

圖2-1為MCS-51系列晶片40支接腳DIP包裝的接腳圖,圖中並列式 I/O埠P0、P1、P2、P3接腳為多功能,依執行模式及需求而友不同的用 途。40支接腳可概分為四大類,在底下說明中接腳信號名稱後面括號中 的數字代表接腳號碼。圖2-1 MCS-51 接腳圖

一、電源部份 1.Vcc (40) : +5 電源輸腳。 2.Vss (20) : 接地 (GND) 電源輸入腳。 二、時脈部份 1.XTAL 1(19) : 振盪時脈信號輸入腳 1 。 2.XTAL 2(18) : 振盪時脈信號輸入腳 2 。 三、控制部份 1.RST (9) 硬體重置 (Reset) 信號輸入腳。此接腳信號在正常狀態時保持低電 信,若信號為高電位時,CPU 會被重置。重置後內部特殊暫存器 (SFR) 會變成預設值,內部 RAM 的值則不影響。 2.EA____ (31)

外部讀取致能 (External Access Enable) 輸入接腳。此腳決定唯 讀記憶體 (ROM) (儲存程式的記憶體) 最前面 4K/8K (Byte)位址從 0000H ~ 0FFFH / 0000H ~ 1FFFH 儲存在單晶片內部或在外部擴充的 ROM

中。若 EA____ = 1 表示在晶片內部,EA____ = 0 表示在外部擴充的 ROM 中。

8031(8032)之EA____ 腳必須接地 (即接低電位信號)。

3.ALE (30)

位址鎖住致能源 (Address Latch Enable) 信號輸出腳和並列埠 P0 配合使用 。P0 為多功能型態,在擴充模式下,P0 既提供位址信號也提 供資料信號,經由 ALE 線及閂鎖晶片如 74LS373 可將位址信號和資料 信號分開。ALE 的信號頻率為振盪頻率 ( fosc ) 的 1/6,也可以當作 脈波信號源。

4. PSEN________ (29)

程式儲存致能 ( Program Store Enable ) 信號輸出腳。在提取儲

存在外部 ROM 的指命時,PSEN________ 此接腳會送出控制信號,以便讀外部 ROM

的指令資料。

四、並列輸入 / 輸出埠部份 1. P0.0 ~ P0.7 (39~32)

電路低八位元位址 (A0~A7) 及資料 (D0~D7) 。若當作 I/O 埠 時,為開極體 (Open Drain) 的 I/O 埠。

2. P1.0 ~ P1.7 (1~8) 埠 1,為雙向 I/O 埠,內部電路有提升電阻。在 MCS-52 系列的 晶片,P1.0、P1.1 有另外的功能如下: P1.0 (T2):計時 / 計數器 2 外部信號輸入端。 P1.1 (T2 EX):計時 / 計數器 2 在捕捉摸式 (Capture) 下緣 觸發 / 重新載入信號輸入腳。 3. P2.0 ~ P2.7 (21~28) 埠 2,有兩種功能。當外接擴充記憶體或介面電路時,提供擴充 電路高八位元位址(A8~A15)。若當作 I/O 埠時,為雙向 I/O 埠, 內部電路有提升電阻。 4. P3.0~P3.7 (10~17) 埠 3,為雙向 I/O 埠、內部電路有提升電阻。各接腳依需求具有 另外的功能用途如下: P3.0(RXD):串列埠信號輸入腳。 P3.1(TXD):串列埠信號輸出腳。 P3.2(INT0_______):外部中斷 0 信號輸入腳。 P3.3(INT1_______):外部中斷 1 信號輸入腳。 P3.4(T0):計時 / 計數器 0 外部信號輸入腳。 P3.5(T1):計時 / 計數器 1 外部信號輸入腳。 P3.6(WR____):將資料存入外部記憶體或介面晶片之控制信號輸出 腳。 P3.7(RD ____ ):從外部記憶體或介面晶片讀取資料之控制信號輸出 腳。 下頁表格為所有PIN腳詳細說明:

2.3 MCS-51/52 記憶體結構

MCS-51/52 其位址線為十六位元,因此記憶體空間可達 64K Byte。 由於 MCS-51/52 讀取程式記憶體 (Program Memory)有專用的控制線 PSEN ________ ,所以程式記憶體和資料記憶體(Data Memory)二者選址時完全獨 立不相干。MCS-51/52 記憶體結構圖如圖 2-3 所示。圖2-3 MCS-51 記憶體結構圖

2.3.1 程式記憶體

程式記憶體主要是存放程式碼,CPU 會自動到程式記憶體提取程式 碼,並依照程式內容執行工作,所以 CPU 無法存入或更新程式記憶體資 料。 MCS-51/52 以其內部 ROM 的觀點可以分成兩類: 一、內部不含 ROM(ROMless) 如 8031(8032)。由於晶片內部沒有 ROM,所以程式碼均存放在外部 記憶體晶片(EPROM、EEPROM)。二、內部含有 ROM 如 8051(8052),8751(8752)。由於晶片內部含有 ROM 8051(8751) 內部有 4K Byte (8052、8752 則有 8K Byte)。程式記憶體前 4K(0000H~0FFFH)(8052、8752 為前 8K(0000H~1FFFH))存於晶片內部, 其餘程式則存放在外部記憶體晶片(EPROM、EEPROM)。 MCS-51/52 依據EA____腳(P31)接腳電位的狀態判斷晶片內部是否存放 程式碼。若EA____腳(P31)接地(低電位,邏輯 0),則判斷程式碼均存放在外 部記憶體晶片中,即晶片內部有程式碼,也視為無效。若EA____腳(P31)接 +5V(高電位,邏輯 1),則判斷程式碼前 4K Byte(8051、8751)或 8K Byte(8052、8752)存放在晶片內部,其餘的程式碼存放在外部記憶體晶 片中,8031、8032 因內部沒有 ROM,所以EA____腳務必要接地。

2.3.2 資料記憶體

MCS-51 資料記憶可分成內部資料記憶體和外部資料記憶,內部資料 記憶體位址和外部資料記憶體位址彼此互相獨立且存取的指令也各有 不同。內部資料記憶體的存取以助憶符號 ”MOV” 為首的指令群。外 部資料記憶體的存助憶符號 ”MOVX” 指令為首的指令群。當 CPU 存取 外部資料記憶體也就是執行 “MOVX” 指令時,CPU 會令WR____(P16)腳或RD____ (P17)腳送出相對應的控制信號。但是 CPU 在存、取內部資料記憶體也 就是執行 “MOV” 指令時WR____、RD____並不會送控制信號。底下說明存、取 內部資料記憶體的方法。 (1)讀取內部資料記憶體位址 50H 的資料到累積器 ACC 中。 直接定址:MOV A,50H 間接定址:MOV R0,#50H (R0、R1 為間接定址暫存器) MOV A,@R0 (2)將累積暫存器 ACC 的值存在內部資料記憶體位址 50H 中。 直接定址:MOV 50H,A 間接定址:MOV R0,#50H MOV @R0,A 底下說明存、取外部資料記憶體的方法。 (1)讀取外部資料記憶體位址 50H 的資料到累積器 ACC 中。 間接定址:MOV DPTR,#0050H(DPTR 為指標暫存器 16 位元)間接定址:MOV R0,#50H(R0(R1)為間接定址暫存器)

MOVX A,@R0(此時RD____ (P17)腳送出 LOW 控制信號)

(2)將累積暫存器 ACC 的值存在外部資料記憶體位址 50H 中。 間接定址:MOV DPTR,#0050H MOVX A,@DPTR(此時WR ____ (P16)腳送出 LOW 控制信號) 間接定址:MOV R0,#50H

MOVX A,@R0(此時WR____ (P15)腳送出 LOW 控制信號)

MCS-51/52 內部資料記憶體的空間為 128/256 Byte 位址從

00H~FFH,其功能規劃參考圖 2-4。由圖中可以看出內部資料記憶體分成 下列五個部份:

一、暫存器庫(Register Bank)

暫存器庫位址從 00H~1FH 續共 32 個 Byte,分成 4 組暫存器庫 Bank 0(00H~07H),Bank 1(08H~0FH),Bank 2(10H~17H),Bank 3(18H~1FH), 每組暫存器為 8 個 Byte,均以 R0~R7 表示。既然 4 組暫存器庫均以 R0、 R1…R7 表示,CPU 如何辨認此時 R0、R1…R7 是來自哪一組的暫存器庫 呢?CPU 會以特殊功能暫存器(SFR)中程式狀態字暫存器(PSW)的 RS1、 RS0 兩位元決定組別。例如:(RS1,RS0) = (0,0)時指 Bank 0,R0 指 位址 00H,R1 指位址 01H。(RS1,RS0) = (1,1)時指 Bank3,R0 指位址 18H,R7 指 1FH。RS1、RS0 在開機時或重置時其值為 0,R0、R1…R7 指 向 Bank 0。 暫存器庫主要是用在提高程式撰寫的效率,不同功能的程式段、副 程式使用不同組別的暫存器 R0~R7。例如:規主程式使用 Bank 0,外部 中斷副程式使用 Bank 1,計時 / 計數中斷副程式使用 Bank 2 ……等, 彼此使用不同組的暫存器 R0~R7,資料不會混淆。 二、可位元定址區 可位元定址區的資料記憶體位址 20H~2FH 共 16Byte,除了具備資料 記憶體的功能外尚提供單獨位元定址的功能,能直接使用布林運算指令 更改位元值。如圖 2-4 中位址 20H 的第 0 位元其位元位址為 00H 也可以 用 20H.0 表示,位址 2FH 的第 7 位元其位元位址為 7FH,也可以用 2FH.7 表示。例如:將 23H 的位元 0 設為 1,(23H 的位元 0 其位址為 18H)指令 為 SETB 18H,將位元位址 18H 直接設定為 1,為了減少查表的困擾,也

可以用 23H.0 表示,指令為 SETB 23H.0。 三、使用者資料記憶區(User RAM) 位址 30H~7FH 共 80 Byte 提供一般資料儲存用由於系統開機或重置 時,堆疊指標 SP 之初始值指向 07H,CPU 執行呼叫(CALL)指令或中斷時 會將程式計數(PC)值從 08H 往上堆疊,因為 Bank 1(08H)以後的內部資 料記憶不能使用,否則可能造成系統當機。撰寫程式時通常使用 MOV 指 令將堆疊指標 SP 搬移到使用者資料記憶區(30H~7FH)較方便。 四、內部資料記憶體(80H~FFH) 80H~FFH 共 128 Byte 只有 MCS-52 系統有擁有此堆資料記憶體而 MCS-51 係統則沒有。這塊區域的記憶體限定使用間接定址的方式存、取 資料,假如使用直接定址的方式存、取到特殊記憶體(SFR)的資料。例 如要讀取內部資料記憶體位址 80H 的資料,使用指令如下: MOV R0,80H ;(R0,R1 為間接暫存器) MOV A,@R0 ;使用間接定址方式讀取位址 80H 的資料到累積器中 MOV A,80H 若使用直接定址方式則讀取到特殊暫存器 P0 的值。 五、特殊功能暫存器(Special Function Register SFR)

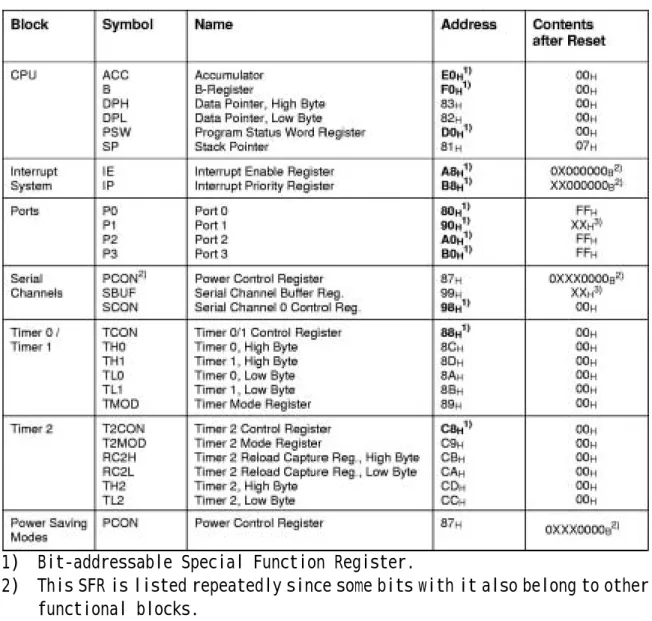

位址 80~FFH 共 128 Byte 為特殊功能暫存器區,特殊功能暫存器名 稱及位址配置如表 2-2 所示,SFR 中可位元定址及位元名稱如表 1-3 所 示。在表中空出的位址(如 84H~86H),不能當作資料記憶體使用,請注 意。 系統在開機時或被重置後(RESET),特殊功能暫存器的值會被重新 設定成固的初始值,特殊功能暫器的初始值如表 2-2 所示。 特殊功能暫存器的功能及用途,簡述如下: ACC (Accumulator)累積暫存器(E0H) MCS-51/52 執行算術 / 邏輯運算時,都以 ACC 為主要遲算對象,指 令中出閱頻率很高。資料長度為 8 位元,可位元定址。 B 暫存器(F0H) 在執行乘法及除法運算指令時,必然使用到此暫存器。資料長度 8 位元,可位元定址。

表 2-2 特殊功能暫存器

1) Bit-addressable Special Function Register.

2) This SFR is listed repeatedly since some bits with it also belong to other functional blocks.

3) X means that the value is indeterminate and the location is reserved.

DPTR (Data Pointer)資料指標暫存器 DPTR 主要用在存、取外部資料記憶體時指定外部資料記憶體的位址 或讀取程式記憶的程式碼時指定要讀取的位址。DPTR 為 16 位元, 由兩個獨立的 8 位元暫存器 DPH(83H),DPL(82H)所組成,DPH 指 DPTR 的高位元組,DPL 為 DPTR 的低 8 位元組,若 DPTR 不使用,DPH,DPL 可當作一般暫存器用。 IE (Interrupt Enable)中斷致能暫存器(A8H) MCS-51/52 的中斷為可遮罩式;由中斷致能暫存器選擇致能 / 禁止

中斷的發生。可位元定址。 IP (Interrupt Priority)中斷優先暫存器(B8H) 中斷優先暫存器以位元控制中斷的優先層次,每一位元代表一個中 斷源,若位元值為 0 則其相對應的中斷優先權較低,若位元值為 1 則相對應的中斷有較高的中斷優先權。 P0,P1,P2,P3 暫存器(80H,90H,A0H,B0H)

P0,P1,P2,P3 為 MCS-51/52 四個 I/O 埠的閂鎖器(Latch),存放 I/O 的狀態資料,四個埠暫存器均可位元定址。

PCON 功率控制暫存器(Power Control)(87H)

電源控制暫存器主要用在 CHMOS 版本的 CPU 如 80C51、80C52、87C51、 87C52,控制 CPU 進入功率下降模式及閒置模。另外一個用途為控制 串列傳輸時鮑率值。

PSW (Program Status Word)程式狀態字暫存器(D0H)

程式狀態字暫存器主要記錄 CPU 執行算術 / 邏輯運算後進位、溢 位、輔助進位的狀態值、暫存器庫的選擇及同位位元,可位元定址。 程式狀態字暫器的位元格式及功能如表 2-3 所示。 RCHAP2H,RCAP2L 捕捉(Capture)暫存器(CCH,CBH) 捕捉暫存器只有 MCS-52 系統才有,配合 MCS-52 系統計時 / 計數器 2 使用。當計時 / 計數器 2 捕捉模式時,若 T2EX(P1.1)腳輸入信號 由 1 下降為 0(負緣),計時 / 計數器暫存器之值會移 RCHAP2H、 RCAP2L 暫存器中。

SBUF (Serial Data Buffer)串列資料緩衝器(99H)

MCS-51/52 之串列傳輸為全雙工,在同一時間執行資料的傳送及接 收,故 SBUF 有兩個暫存器,一個專職傳送資料用的緩衝器,另一個 接收資料的緩衝器。

SCON (Serial Control)串列傳送控制暫存器(98H)

串列傳送控制暫存器為控制串列傳輸的工作模式及反應串列埠傳送 及接收狀態旗號。

表2-3 程式狀態字暫存器位元功能表

PSW:程式狀態字(Program Status Word) 位址:D0H(可位元定址) B7 B6 B5 B4 B3 B2 B1 B0 CY AC F0 RS1 RS0 OV - P CY 進位旗號 AC 輔助進位旗號 F0 一般用途 RS1 暫存器庫選擇位元1 RS0 暫存器庫選擇位元0 RS1 RS0 暫存器庫 R0-R7的位址 0 0 0 00H-07H 0 1 1 08H-0FH 1 0 2 10H-17H 1 1 3 18H-1FH OV 溢位旗號 - 保留將來使用 P 同位元旗號,在每個指令週期,由硬體設定或清除,以指出 累加器(ACC)”1”的個數為奇數個(p=1)或偶數個(p=0) SP (Stack Pointer)堆疊指標潛存器(81H) 堆疊指標暫存器在系統開機時或重置時其初始值為 07H。主要功能 為管理堆疊區,當執行 CALL、PUSH、POP 或中斷時會改變堆疊指標 暫存器的內容。

TCON (Timer/Counter Control)(88H)

計時 / 計數控制暫存器主要控制計時 / 計數器 0(1)啟動 / 停止 及反應計時 / 計數狀態信號,另外尚控制外部中斷信號的觸發型態

及反應外部中斷的狀態旗號。

T2CON (Timer/Counter 2 Control)(C8H)

計時 / 計數 2 控制暫存器主要控制計時 / 計數 2 的工作模式及啟 動 / 停止。

TMOD (Timer/Counter Mode) (89H)

計時 / 計數器模式控制暫存器主要是設定計時 / 計數器 0(1)的工 作模式。 (TH0,TL0) (TH1,TL1) (TH2,TL2) (8CH,8AH)(8DH,8BH)(CEH,CDH) 計時 / 計數器主要用來儲存計時 / 計數的值,THX(X:0,1,2)表示 高位元組,記錄計時 / 計數值的高 8 位元,TLX(X:0,1,2)表示低 位元組,記錄計時 / 計數值的低 8 位元。

2.4 MCS-51/52 時脈輸入

MCS-51/52 晶片內部有一個振盪器,可以當作 CPU 的時脈源。在設 計時脈源時,若使用晶片內部的振盪器,只要在 XTAL1(P19),XTAL2(P18) 兩腳間接振盪頻率範圍 3.5MHz~12MHz 的石英震盪晶體或陶質共振器, 並各自接 20PH~50H 的電容,如圖 2-5 所示。2.5 MCS-51/52 的重置

任何微電腦系統均有硬體重置的功能,硬體重置主要用來確保 CPU 在開機時從程式的預定啟始位址開執行及當系統當時使系統能重新開 始。 MCS-51/52 的重置信親輸入腳為 RST(P9)腳,此輸入腳為高電位動 作,且高電位信號至少要維持 2 個機械週期也就是 24 個振盪週期,若 振盪頻率 fosc=12MHz 則重置信號高電位要持續 2 微秒(μS)。開機時 RST 接腳電位為高電位促使系統重置,利用電容充電效應使 RST 接腳電位降 成低電位。MCS-51/52 完成重置動作,固定到程式記憶體位址 000H 開始 執行。第三章 開發環境簡介

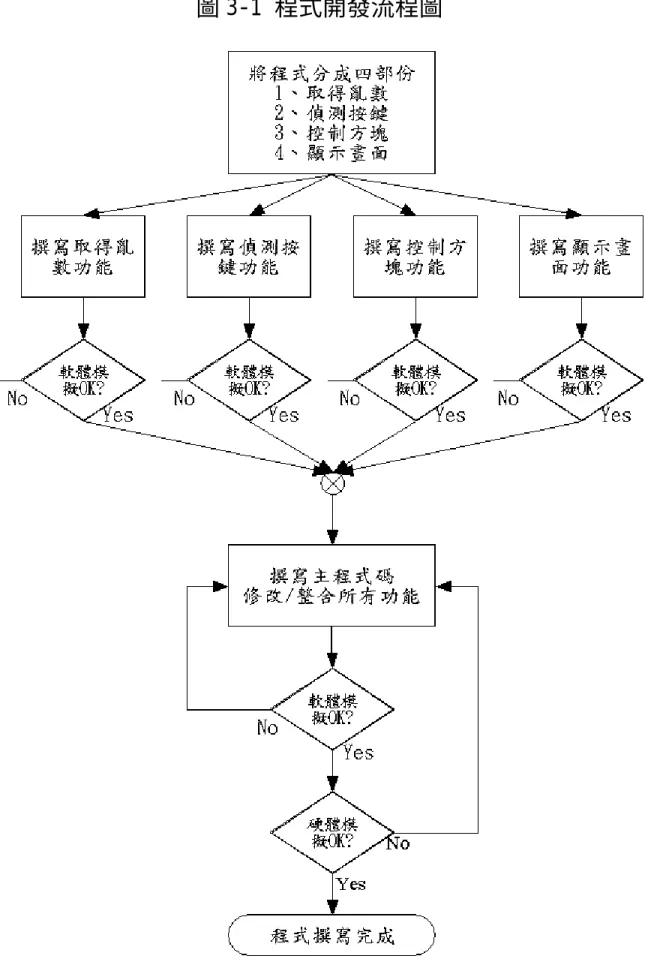

3.1 整體工作流程

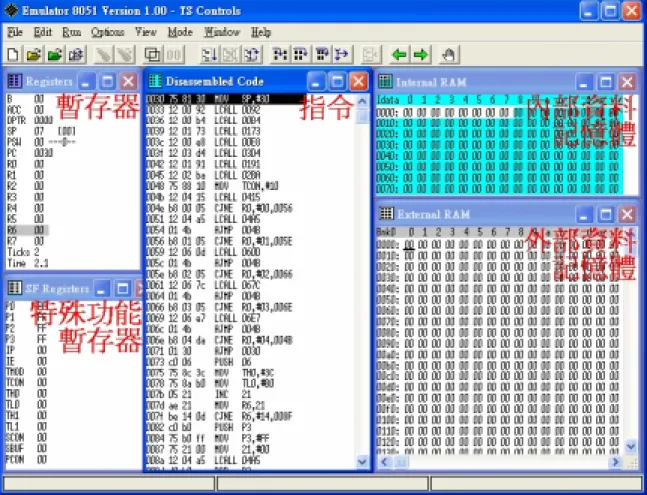

每一個應用系統可分成硬體電路及軟體程式兩大部分,依據系統規 格之需求規劃設計電路,再根據硬體電路規劃軟體程式,直到軟、硬體 測試互相配合符合系統的需求才算完成。在進行軟、硬體測試時,若不 能符合系統所要求的規格需求,表示軟、硬體必存在一些問題,尋找問 題的根源(Debug)除了需要耐心、細心之外、適當的發展工具也是不 可或缺的。本次專題完全是以 8051 組合語言開發,因此 Debug 可以說 是相當重要的一環。 我們使用軟體模擬器來測試程式的邏輯功能是否正確無誤,最後再 以線上硬體模擬器來檢查結果是否達到要求。軟體模擬部份主要以 TS controls 公司發展的 Emulator 8051 來完成對於整個應用系統作除錯與 追蹤的工作。但也僅限於做到邏輯層面的模擬與除錯,並不能表現出硬 體實際的特性。例如週邊 I/O 裝置的狀態和介面的時序等。 硬體模擬的原理是利用一個仿真的 8051 電路再外加一些具有除錯 功能的電路,並由此模擬真正的 8051 和支援額外的除錯功能。利用 PICE-52 可以完整的模擬出 8051 的硬體特性。一般而言,程式組譯完成 時都會先用 TS controls Emulator 8051(以下簡稱 TSCE)的模擬功能 作除錯的工作,先將程式中邏輯性的錯誤除去,再載入 PICE-52 內進行 整個系統的模擬和除錯,以修正和硬體有關的錯誤。程式開發流程如下 頁圖 3-1。3.2 TS controls 8051 Emulator 軟體模擬器簡介

TSCE 主要功能純綷是軟體模擬除錯,下面介紹使用方法。當程式碼 撰寫完成後,需先將原始碼組譯成目的檔,並連結成燒錄檔(.HEX)檔, 此後就可載入此燒錄檔,並開始模擬。如下圖。圖 3-2 選擇燒錄檔畫面

I/O Port 的內容並不是真正經由外部裝置傳送到 8051 的資料,使 用者必須以手動方式設定 I/O Port 的值來觀察程式是否能正確的處 理。Timer 則會自動由模擬器計算每個指令所需的機械週期來設定。如 果是開發中斷服務程式(Interrupt Serves Routine, ISR)的話,TIMER 0 和 TIMER 1 都是會自動觸發中斷的,此外也可以按 Ctrl+F9 產生中斷 訊號。的瀏覽視窗,以及 Step/Step Over Call 的執行方法,因此可以非常方 便的檢查程式是否有邏輯上的錯誤。進行模擬除錯時的畫面如圖 3-3。

3.3 PICE 80C52 單晶片線上模擬器簡介

PICE-52 是一套 8051 的線上硬體模擬器(In-Circuit Emulator,簡 稱 ICE),在使用上可以完全的視做真正的 8051 單晶片。PICE-52 與 PC 的連接利用 RS232,此外 PICE 尚需使用 40-Pin Cable 與實驗板連接以 測試特定的功能,本次專題便是連接 LCD 顯示模組。下圖為 PICE-52 跟 電腦連接的方法,由左到右分別為 PC、PICE-52 和實驗板。

圖 3-4 PICE 連接圖

PICE-52 內部具有 64K 的外部資料記憶體和 64K 的外部程式記憶 體,所以在使用時不可以再外接任何的記憶體模組。另外 Port0 和 Port2 因同時作為外部記憶體的資料/位置匯流排。所以在使用這兩個 Port 時 必須考慮 PICE 會隱含性的使用這兩個 Port,不然會使外部記憶體無法 正常運作。第四章 繪圖型 LCD 顯示器模組

4.1 繪圖型LCD顯示器LCG-128064功能介紹

繪圖型 LCD 顯示器是以點矩陣均勻分布,顯示幕上每一點均能顯 示,而文字型 LCD 顯示幕上字元與字元之間預留空間則不能顯示。繪圖 型 LCD 之解析度以行點數(C)×列點數(R)表示,如 128×64 表示顯示幕有 128 行 64 列。 繪圖型 LCD 因使用控制晶片之不同,其顯示的功能及控制方法略有 差異,而有混合型(以指令規劃為繪圖模式或文字模式顯示)和繪圖型的 區別。我們在此使用編號 LCG-128064 之繪圖型 LCD,其解析度為 128× 64,外觀如圖 9-1 所示,接腳功能及說明如表 9-1 所示請參考。圖 4-1 LCG-128064 外觀圖

LCG-128064 結構方塊如圖 4-2,列驅動由晶片 HD61203 控制,當致 能線 CS1 作動時左半部 64 行可以顯示資料,同理 CS2 作動時,則右半 部 64 行可以顯示資料,以下針對 HD61202 內部功能說明。表 4-1 LCG-128064 接腳名稱與功能說明

接腳編 號 信號名 稱 動作準 位 功 能 說 明 1 Vss 電源接地:0V 2 Vdd 電源正端:+5V 3 Vo LCD 亮度調整電壓輸入端,可直接與第 18 腳 VEE 相連 4 D/I__ H/L 資料暫存器/指令暫存器(Data/Instruction) 0: 指令暫存器 1: 資料暫存器 5 R/W___ H/L 讀寫線 0:資料寫入,將資料寫入繪圖型 LCD 1: 資料讀取,讀取繪圖型 LCD 資料6 E H,H→L 資料致能腳(Enable):E 腳由 high 變 low,資料

才能有效轉移 7-14 DB0~ DB7 H/L 資料匯流排(Data Bus) 15 CS1 H 晶 片 選 擇 腳 1: 高 電 位 時 , 將 致 能 第 一 顆 HD61202,即可顯示左邊 64×64 點 16 CS2 H 晶 片 選 擇 腳 2: 高 電 位 時 , 將 致 能 第 二 顆 HD61202,即可顯示右邊 64×64 點 17 RST______ L 重置接腳(Reset):低電位時重置 HD61202 18 VEE LCD 驅動電壓,約-10 伏。本實驗器所用模組以 附有負電壓產生電路,不必由外部在供應電壓 到此接腳。 19,20 N.C. 此兩腳未用(No Connected)

4.2 LCG-128064 內部暫存器

一、暫存器 經由控制信號線 D/I__及 R/ W___,作暫存器的選擇,其功能如表 4-2 所 示。 1.輸入暫存器(Input Register)用來暫時儲存要寫入至顯示資料 RAM(Display Data RAM)的資料, 當我們欲將資料寫入顯示資料 RAM 時,其內部會透過輸入暫存器將資料

寫入顯示資料 RAM 中。當 CS=1,D/I__=1 且 R/ W___=0,資料是在信號 E 轉變 成負緣時被鎖入(Latch)輸入暫存器中。

表 4-2 暫存器選擇及動作說明

D/I__ R/ W___ 動 作 功 能 0 0 寫入指令暫存器 0 1 讀取忙碌旗標及狀態資料 1 0 將資料寫入顯示 RAM 中,內部運作會先將輸入之資料存入 輸入暫存器,然後再寫入顯示資料 RAM 內。 1 1 讀取顯示 RAM 資料,內部運作會先將顯示資料 RAM 之資料 存放至輸出暫存器,然後再由輸出暫存器送出資料。圖 4-2 LCG-128064 功能方塊圖

2.輸出暫存器(Output Register) 讀取顯示資料 RAM 時如圖 4-3 所示。無法直接讀取顯示資料 RAM 的 資料,顯示資料 RAM 的資料會先儲存在輸出暫存器中,再由輸出暫存器 輸出。當下達讀取顯示資料命令時,信號線 CS=D/I__=R/ W___=1(如圖 9-3 E時序編號 6),信號線 E 在高電位時,輸出暫存器所儲存位址 N 的資料輸 出給 MPU;信號線 E 在負緣(1→0)時,位址指標(Address 標示 N+1)所示 的顯示資料被送到輸出暫存器中,而位址指標自動加 1(Address 標示 N+2)。 執行讀取顯示資料 RAM 指令時,輸出暫存器的內容會變動,而執行 位址設定指令時,輸出暫存器內容則維持不變,因此下達位址指令設定 指令後必須連續兩次下達讀取顯示資料 RAM 指令,才能讀取到正確的資 料。如時序圖 9-3 中下達位址設定指令後(E 時序編號 2,Address N), 下達第一次讀取指令(E 時序編號 4)讓位址 N 的資料存入輸出暫存器 中,下達第二次讀取指令(E 時序編號 6)才能正確讀取到位址 N 的資料。

圖 4-3 讀取顯示資料 RAM 時序圖

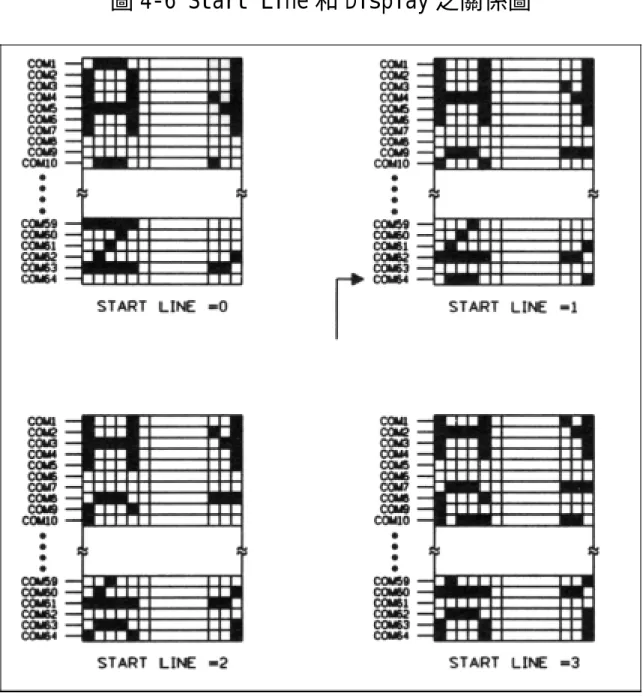

二、顯示器開始列暫存器(Display Start Line Register)

顯示器開始列暫存器主要用在螢幕捲動,此暫存器的內容指定螢幕 第一列的顯示資料,藉由改變暫存器的內容,達到螢幕捲動的效果。顯 示器開始列暫存器的內容,由顯示器開始列指令設定,請參考控制指令 集的指令(2)。

X,Y 位址計數器標示內部顯示資料 RAM 的位址,總共 9 位元,X 位 址計數器顯示內部資料 RAM 位址的高 3 位元,Y 位址計數器則顯示內部 顯示資料 RAM 的低 6 位元。X,Y 位址計數器特性說明如下: 1.X 位址計數器: 不具有計數功能的普通暫存器,其值不會自動增加,必須由指令設 定。 2.Y 位址計數器: 由指令設定 Y 位址計數器值,並且執行讀寫顯示資料指令時,此計 數器會自動加 1。Y 位址計數器隻值由 0 到 63 循環計數,及計數至 63 時,若在加 1 則回復為 0。

四、顯示資料 RAM(Display Data RAM)

顯示資料 RAM 儲存顯示器各點資料(dot data)。RAM 中 1 位元(bit) 資料對顯示器面板(display panel)上的 1dot,若該位元值為 1 則對應 的 dot 會亮,位元值為 0 則 dot 暗。 五、忙碌旗標(Busy Flag) 我們藉由讀取狀態字碼的位元 7 值(DB7)可得忙碌旗標的狀態,當 忙碌旗標為”1”時,表示 HD61202 內部正在運作,此時除了狀態讀取 指令外,其他的指令都不將被接受,因此,在下達指令前,應先確定忙 碌旗標是否為 0。 六、重置(Reset) 當啟動電源或系統送低電位(Low)給RST______腳時 HD61202 會被初始化 (initialized): 1.顯示器 OFF。 2.顯示開始列數暫存器之值設定為 0(第 0 列) 當RST______腳為 Low 時(標示清除重置)及 DB7(BUSY)=0(表示已經備妥) 後,才能下達其他指令,執行重置時 HD61202 暫存器內容令被破壞,顯 示 ON/OFF 正反器及 RAM 的資料則保存。啟動電源時重置時間如圖 4-4 所示。

圖 4-4 啟動重置時間圖

4.3 LCG-128064 讀寫時序

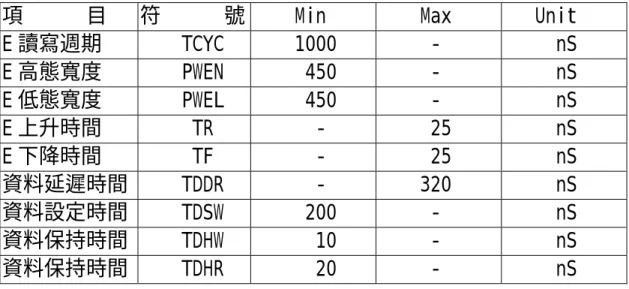

LCG-128064 讀寫時序圖如圖 5-5 所示,表 4-3 為時序圖參數規格資 料,時序圖參數規格的單位為奈秒(nS)。

表 4-3 時序圖參數規格

項 目 符 號 Min Max Unit

E 讀寫週期 TCYC 1000 - nS E 高態寬度 PWEN 450 - nS E 低態寬度 PWEL 450 - nS E 上升時間 TR - 25 nS E 下降時間 TF - 25 nS 資料延遲時間 TDDR - 320 nS 資料設定時間 TDSW 200 - nS 資料保持時間 TDHW 10 - nS 資料保持時間 TDHR 20 - nS

圖 4-5 LCG-128064 讀寫時序圖

4.4 繪圖型 LCD LCG-128064 控制指令集

1.顯示器 ON/OFF R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 0 0 1 1 1 1 1 D D=1:顯示 RAM 資料呈現在顯示器上。 D=0:畫面上將無顯示,但資料仍存在顯示 RAM 中;因此,可再將 D=0 改變成 D=1,使資料呈現於畫面上。2.顯示器開始列(Start line)

R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Code 0 0 1 1 A A A A A A

用來設定顯示器開始列數暫存器值,使顯示 RAM 中某一列資料顯示 於 LCD 面板的第一列,圖 9-6 為 Start line=0~3 之顯示情形。

3.設頁數(Set page),page 指的是 X 位址 R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 1 0 1 1 1 A A A 圖型 LCD 模組其顯示資料 RAM 位址排列方式如圖 4-7 所示,縱向、 橫向各右 64 點(dot),縱向由 X 位址計數器控制,橫向由 Y 位址計數器 控制。縱向 64 點分成 8 頁(page),藉由 3 個二進位 AAA 設定 X 位址計 數器,若 AAA=000,則 X 位址計數器為 0 表示第 0 頁,隨後執行讀寫顯 示資料 RAM 指令均指向第 0 頁,至於正確位址則由 Y 位址計數器決定。 當要讀寫其他頁的資料時,則必須要先更改 X 位址計數器的值 4.設 Y 位址 R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 0 1 A A A A A A 顯示資料 RAM 位址排列方式如圖 4-7 所示橫向 64 點(dot)由 Y 位址 計數器控制,藉由 6 個二進位 AAAAAA 設定 Y 位址計數器值,若 AAAAAA=000000,則表示第 X(由 X 位址計數器決定)的第 0 個位元組 (Byte)。當執行讀寫顯示資料 RAM,則 Y 位址計數器自動增加 1。

圖 4-7 顯示資料 RAM 位址排列方式

5.狀態讀取

R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Code 1 0 Busy 0 ON/OFF RESET 0 0 0 0

•BUSY: Busy=1 表示 HD61202 無法接受控制指令 Busy=0 表示 HD61202 可以接受控制指令 •ON/OFF: ON/OFF=1 表示顯示器為 OFF 狀態,螢幕不顯示資料。 ON/OFF=0 表示顯示器為 ON 狀態,螢幕正顯示資料。 •RESET RESET=1 表示系統正執行初始化工作。 RESET=0 表示系統已初始化完畢,處在正常運作狀態。 6.寫入顯示資料(Write Display Data)

R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

Code 0 1 D D D D D D D D

將 8 位元資料 DB7~DB0 寫入到顯示資料 RAM 中;然後,Y 位址計數 器將自動加 1。

7.讀取顯示資料(Read Display Data)

R/ W___ D/I__ DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 1 1 D D D D D D D D 將顯示資料 RAM 中讀取 8 位元資料後,Y 位址計數器將自動加 1。 若重新設定位址則要執行假讀(dummy read)一次,如此才能夠讀取到正 確的資料。有關讀取顯示資料詳細說明,請參考輸出暫存器部分。 第五章將會有使用 LCG-128064 所做的繪圖型 LCD 顯示器實驗模組 的詳細方法。

第五章 系統介紹及原理

5.1 遊戲簡介

俄羅斯方塊是一款風靡全球的電視遊戲機和掌上遊戲機遊戲,它曾 經造成的轟動與造成的經濟價值可以說是遊戲史上的一件大事。這款遊 戲最初是由蘇聯的遊戲製作人Alex Pajitnov製作的,它看似簡單但卻 變化無窮,令人上癮。相信大多數的人都還記得為它痴迷得茶不思飯不 想的那個俄羅斯方塊時代。 究其歷史,俄羅斯方塊最早還是出現在PC上。對一般人來說,它的 規則簡單,容易上手,且遊戲過程變化無窮,使人們能輕易感受到遊戲 中的樂趣。 遊戲中有七種由四個格子構成的不同形狀方塊,遊戲區域是在一個 10x16(通常由設計者決定,本次專題使用10x16大小以便讓位置座標存 在一個8位元的暫存器內。)個格子的範圍內。遊戲開始後會將一個隨 機的方塊放在遊戲區域的最上面,此時這個方塊會開始由上往下慢慢掉 落,如果下頭還有空間,這些方塊就會自動往下掉落一格填補空間,當 方塊掉落到最底或碰觸到其他方塊之後,方塊停止移動並佔住此四格空 間,並且放入新的方塊。而當某一列被填滿時,就消掉這一行,而原先 堆在上頭的方塊也會往下掉落,若是沒有空將讓方塊放入遊戲區域中遊 戲就結束。當然方塊在掉落到停止的途中,可以由使用者自由控制將方 塊左移、右移、下移或是旋轉,盡量讓方塊填滿每一列。遊戲畫面如5-1 圖所示(非本次專題畫面,僅供參考。)。圖5-1 參考遊戲畫面

5.2 程式流程

程式執行的詳細流程如下說明: 1.程式開始時,先設定好一些8051系統或是遊戲本身會用到的變數 的初始值,稱為初始化。再來將繪圖型LCD顯示器初始化,如執行顯示 器ON指令,設定顯示器開始列,此部分可參考第四章的LCG-128064控制 指令集。清除LCD螢幕畫面,也就是清除顯示RAM。畫出遊戲標 題”TETRIS”以及”Press Start”字樣還有遊戲區域邊框。 2.計時並等待按鍵輸入,使用者按鍵之後,停止計時,此時便以TL1 暫存器的低7位元(範圍為0~127)當作亂數表偏移值。亂數表為一系列 不規則數值資料,本系統以64個位元組儲存此表格,每次取4個位元(範 圍為0~15)備用。之所以需要亂數表偏移值,是因為若沒有偏移值則每 次重新開始遊戲將皆由第一個位元組取得數值,造成亂數的可預料性,而將亂數表偏移值當作亂數表取得的起始位置則可有效避免此情況。遊 戲開始後,以取得的亂數(範圍為0~6)決定放入的方塊種類(編號為 0~6)。再以方塊種類決定方塊所佔的初始位置,分別將位置座標值放 入R2、R3、R4和R5,高4位元放X(列)座標,低4位元放Y(行)座標, 七種方塊編號、形狀和其所佔初始位置如下所示,其中R2為旋轉方塊時 不動的部份。

圖5-2 方塊設定圖

編號 0: R2 (5,0) R3 (6,0) R4 (4,0) R5 (3,0) ┌┬┬┬┐ └┴┴┴┘ 編號 1: R2 (4,1) R3 (5,0) R4 (5,1) R5 (4,0) ┌┬┐ ├┼┤ └┴┘ 編號 2: R2 (4,1) R3 (5,0) R4 (3,1) R5 (4,0) ┌┬┐ ┌┼┼┘ └┴┘ 編號 3: R2 (4,1) R3 (3,0) R4 (5,1) R5 (4,0) ┌┬┐ └┼┼┐ └┴┘ 編號 4: R2 (4,1) R3 (3,1) R4 (5,1) R5 (5,0) ┌┐ ┌┬┼┤ └┴┴┘ 編號 5: R2 (4,1) R3 (3,1) R4 (5,1) R5 (3,0) ┌┐ ├┼┬┐ └┴┴┘ 編號 6: R2 (4,1) R3 (3,1) R4 (5,1) R5 (4,0) ┌┐ ┌┼┼┐ └┴┴┘ 3.進入等待使用者按鍵的無限回圈,等使用者按下按鍵便執行相對應的動作。此系統需要四顆按鍵分別對應左移方塊、右移方塊、下移方 塊和旋轉方塊等功能。左移、右移以及旋轉等動作均須先檢查移動後的 位置是否已經由其他的方塊佔走,不是就移動方塊,若是則得取消動 作。下移時若是檢查出已有其他方塊擋住,就必須檢查是否已經填滿一 列,若是就將此列消除,將其上的所有方塊下移,因為每個方塊是由四 格組成,因此最多得檢查四行。最後放入亂數產生的新方塊並重複步驟 3。 4.最後是中斷的部份,因為方塊會隨著時間慢慢往下掉,而在此同 時又需要在無限回圈裡等待按鍵,因此我們規劃利用計時器中斷讓方塊 每經過一定的時間(約一秒)就往下移一格。同樣地,下移時若是檢查 出已有其他方塊擋住,就必須檢查是否已經填滿一列,若是就將此列消 除,將其上的所有方塊下移。 程式流程圖如下所示,中斷程式部分可參考5.4節中斷原理。

圖5-3 主程式流程圖

5.3 按鍵原理

本次專題所使用的繪圖型LCD顯示器實驗板為LH-056,此板設計有 2x2矩陣式按鍵,如圖5-4所示。圖5-4 2x2矩陣式按鍵

此種按鍵偵測方法為先將P3.5設為0,P3.2、P3.3和P3.4都設為1, 此時若檢查到P3.2的值為0則可知SW6被按下,若檢查到P3.3的值為0則 可知SW7被按下;再將P3.4設為0,P3.2、P3.3和P3.5都設為1,此時若 檢查到P3.2的值為0則可知SW4被按下,若檢查到P3.3的值為0則可知SW5 被按下。若是沒有偵測到P3.2或P3.3的值變為0,表示使用者並無按下 任何按鍵,於是便重複這些步驟。以下為偵測按鍵程式片段: $1: MOV P3,#00011100b ;將P3.5設為0,P3.2、P3.3和P3.4都設為1 MOV B,P3 ;第一次檢查按鍵值 CALL DELAY_20MS ;延時20ms,軟體去彈跳用 MOV A,P3 ;第二次檢查按鍵值XRL A,B JNZ $1 ;則兩次檢查案鍵值不一樣,表示非穩定按鍵,重新檢查 MOV A,B CJNE A,#00011000B,$2 ;檢查是否按下SW6不是就跳到$2 …… ;這裡放偵測到SW6被按下時所做的後續處理 …… RET $2: CJNE A,#00010100B,$3 ;檢查是否按下SW7不是就跳到$3 …… ;這裡放偵測到SW7被按下時所做的後續處理 …… RET $3: MOV P3,#00101100B ; 將P3.4設為0,P3.2、P3.3和P3.5都設為1 MOV B,P3 ;第一次檢查按鍵值 CALL DELAY_20MS 延時20ms,軟體去彈跳用 MOV A,P3 ;第二次檢查按鍵值 XRL A,B ;若A和B一樣則A為0,若A不是0 JNZ $3 ;則兩次檢查案鍵值不一樣,表示非穩定按鍵,重新檢查 MOV A,B CJNE a,#00101000b,$4 ;檢查是否按下SW4不是就跳到$4 …… ;這裡放偵測到SW4被按下時所做的後續處理 …… RET $4: CJNE A,#00100100B,$1 ;檢查是否按下SW5不是就跳到$1 …… ;這裡放偵測到SW5被按下時所做的後續處理 …… RET JMP $1 ;重複步驟

5.4 中斷原理

5.4.1 MCS-51 計時

計數器

MCS-51 內部有兩組十六位元計時/計數器、計時/計數器 0

(TIMER/COUNTER0)及計時/計數器 1(TIMER/COUNTER1),以後說明簡稱 Timer 0,Timer 1,MCS-52 內部計時/計數器除了 Timer 0,Timer 1 外尚增加一組計時/計數器 2(TIMER/COUNTER2)以後說明簡稱 Timer 2。 以上三組計時/計數器均可經由軟體規劃成計數器或者是計時器。 計時器的時間單位 若規劃成計時器,以機械週期(Machine Cycle)為計時基準,每經 過一個機械週期,其計時/計數器暫存器會自動增加 1。由於一個機械週 期為 12 個振盪週期,因此計時器的最小時間單位為 12 個振盪週期。例 如,若振盪頻率(fosc)為 12MHz,一個振盪週期為 1/fosc 等於 1/12 微 秒(μS),則計時器的最小時間單位為 1 微秒(μS)。 計數器的頻率限制 若規劃成計數器時,則量測經由相對應輸入接腳 Tx(x:0,1,2) (Timer 0 則量測 T0(P3.4)接腳)信號,信號由 Hi 降到 Low 時(“↘”), 其計時/計數器會自動增加 1。MCS-51/52 量測外部信號時,外部信號頻 率最高不能超過 fosc/24 並且輸入信號 Hi、Low 準位最少要維持 12 個 振盪週期。例如,若振盪頻率(fosc)為 12MHz,則輸入信號其頻率最高 不能超過 fosc/24 為 500KHz 且輸入信號在 Hi、Low 準位最少要維持 1 微秒(μS)以上。 計時/計數器工作模式 Timer 0,Timer 1 不管是執行計時器或者是計數器,均可各別規劃 成下列四種工作模式: (1)模式 0(MODE 0):13 位元計時/計數模式。 (2)模式 1(MODE 1):16 位元計時/計數模式。 (3)模式 2(MODE 2):8 位元自動載入計時/計數模式。 (4)模式 3(MODE 3): Timer0 分成兩組獨立的 8 位元計時/計數模 式。

Timer1 停止計時/計數工作。 Timer0,Timer1 在模式 0,模式 1 及模式 2 中使用方法均相同,在 模式 3 中 Timer0 為兩組獨立可同時工作 8 位元計時/計數器而 Timer 1 進入模式 3 便停止 Timer 1 計時/計數的工作。 Timer 0 與 Timer 1 規劃步驟 在規劃 Timer 0、Timer 1 時,必須使用到特殊功能暫存器(SFR)中 計時/計數器模式控制暫存器(TMOD),計時/計數器控制暫存器(TCON)及 計時/計數器(TH0,TL0)、(TH1,TL1)。在以後說明中,若 Timer 0、Timer 均有的暫存器或位元,由於其特性均一樣,我們將以 x(x:0 或 1)表示 TR0 及 TR1。 規劃步驟及使用方法說明如下: 步驟一:由 TMOD 之 C/T__位元規劃執行計時功能或計數功能。 步驟二:由 TMOD 之 M1、M0 位元選擇工作模式。 步驟三:由 TMOD 之 GATE 位元決定計時/計數器啟動之方式。 步驟四:由 TLX,THX 設定計時時間或計數數目。 步驟五:由 TCON 中 TRX 位元控制計時/計數器的啟動/停止。當 TMOD 之 GATE=1 時,則由INTX_______ (P3.2 或 P3.3)接腳信號啟動。 步驟六:由 TCON 中 TFX 偵測計時/計數器工作是否完成。

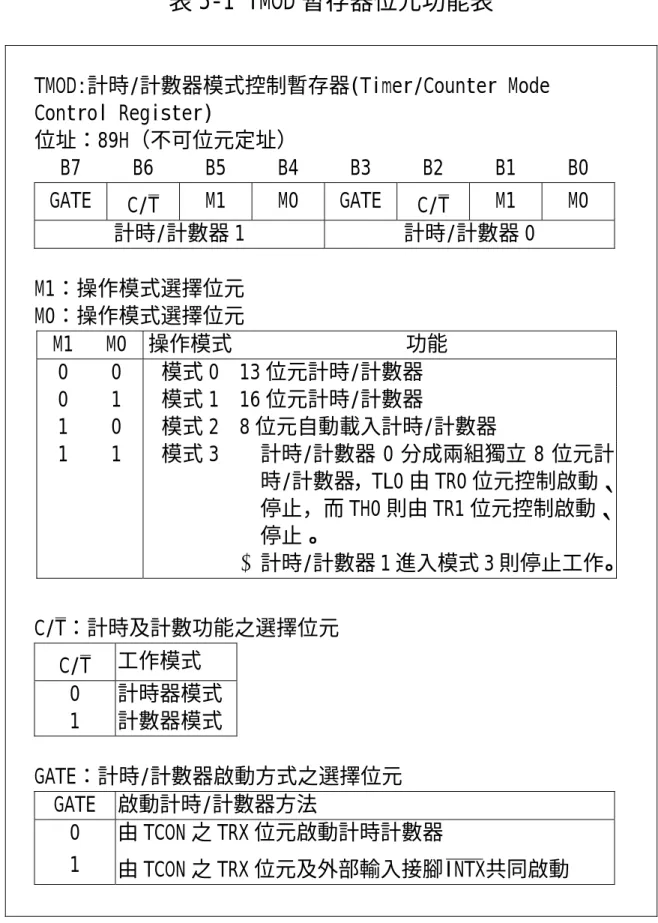

由以上六個步驟,可以看出 TMOD 及 TCON 的重要性,TMOD 格式及位 元功能請參考表 5-1,TCON 格式及位元功能請參考表 5-2,由 TMOD 及 TCON 兩個暫存器組合而成的控制邏輯電路圖如圖 5-5 所示,其真值表如 表 5-3 所示。 在表 5-3 第一行,當 TRX 為 0 時,其餘三個輸入腳為隨意項,則控 制開關 OFF 不執行計時/計數功能,也就是將 TRX 清除為 0 可以停止計 時/計數的功能。 表 5-3 第二、第三行,若 TRX 設定為 1 且 GATE 清除為 0,則控制開 關 ON,由 C/T__決定執行計時或計數功能。若 C/T__為 1 執行計數功能經由 TX 接腳輸入脈波數目,C/T__為 0 則執行計時功能。第二、三行的控制方 式為較常用的模式,通常先設 GATE 位元為 0,再由軟體設定 TRX 為 1 以啟動計時/計數的功能,此種方式,適用於延遲時間方式。

表 5-1 TMOD 暫存器位元功能表

TMOD:計時/計數器模式控制暫存器(Timer/Counter Mode Control Register) 位址:89H(不可位元定址) B7 B6 B5 B4 B3 B2 B1 B0 GATE C/T__ M1 M0 GATE C/T__ M1 M0 計時/計數器 1 計時/計數器 0 M1:操作模式選擇位元 M0:操作模式選擇位元 M1 M0 操作模式 功能 0 0 模式 0 13 位元計時/計數器 0 1 模式 1 16 位元計時/計數器 1 0 模式 2 8 位元自動載入計時/計數器 1 1 模式 3 計時/計數器 0 分成兩組獨立 8 位元計 時/計數器,TL0 由 TR0 位元控制啟動、 停止,而 TH0 則由 TR1 位元控制啟動、 停止。 計時/計數器 1 進入模式 3 則停止工作。 C/T__:計時及計數功能之選擇位元 C/T__ 工作模式 0 計時器模式 1 計數器模式 GATE:計時/計數器啟動方式之選擇位元 GATE 啟動計時/計數器方法 0 由 TCON 之 TRX 位元啟動計時計數器 1 由 TCON 之 TRX 位元及外部輸入接腳INTX_______共同啟動表 5-2 TCON 暫存器位元功能表

TCON:計時/計數器控制暫存器(Timer/Counter Control Register)

位址:88H(可位元定址)

B7 B6 B5 B4 B3 B2 B1 B0 TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 TFX(X:0、1):計時/計數器 X 之溢位旗標,溢位時硬體自動設定 為 1。當執行計時/計數器 X 之中斷程式時,硬體 會自動將溢位旗標清除,否則需由軟體清除。 TRX(X:0、1):計時/計數器 X 之啟動位元,由軟體設定為 1 時自 動啟動,清除為 0 時關閉。 IEX(X:0、1):外部中斷 X 之中斷旗號,當外部中斷信號(由 P3.2 或 P3.3 接腳輸入)被偵測時,硬體會自動設定為 1, 當執行外部中斷服務程式時,硬體自動清除為 0。 ITX(X:0、1):規劃外部中斷信號觸發型態 ITX=0 低準位觸發。 ITX=1 負緣(1→0)觸發。

圖 5-5 計時/計數器控制邏輯電路圖

表 5-3 第四行,若 TRX 設定為 1,GATE 設定為 1,當INTX_______為 0 時則 控制開關為 OFF,不執行計時/計數功能。 第五、六行若 TRX 設定為 1,GATE 設定為 1,當INTX_______為 1 時,則控 制開關 ON,由 C/T__決定執行計時/計數功能。此種控制方式通常先設定 TRX 及 GATE 為 1,由外部INTX _______ 接腳訊號啟動計時/計數的功能,此種方 式適用於量測外部信號之週期或頻率。 由以上的分析、整理出兩項結論: 計時/計數器啟動方式:

一、軟體啟動:先將 TMOD 之 GATE 位元清除為 0,再由軟體設定 TCON 之 TRX 為 1 以啟動計時/計數器。

a.GATE=0(TMOD) b.TRX=1(TCON)

二、外部輸入信號啟動:先將 TMOD 之 GATE 位元及 TCON 之 TRX 位元設

定為 1,則當外界輸入信號INTX_______為 1 時啟動計時/計數器。 a.GATE=1(TMOD) b.TRX=1(TCON) c.INTX_______=1(外部輸入信號) 計時/計數脈波源的選擇: 一、C/T__=0(TMOD):選擇計時脈波,計時脈波頻率為 fosc/12。 二、C/T__=1(TMOD):選擇計數脈波,計數 T0(T1)的脈波頻率。 計時時間/計數數目的設定及計算 MCS-51/52 計時/計數器採用上數計數方式,由兩個八位元計時/計 數器暫存器(THX,TLX)負責計數。每送入一個脈波,(THX,TLX)值會自 動加 1,因此(THX,TLX)之初使值設定為討論的重點。 例題:十六位元計時/計數器 0,若要設定計時/計數數目為 5000,則 (TH0,TL0)之初始值為何?程式如何設計?

解:十六位元計數器,最高計數值為 2^16=(65536)D(D 表十進制)預定 計數 5000,而計數器為上數方式。所以(TH0,TH1)之初始值為 2^16-5000=65536-5000=(60536)D (60536)D=(EC78)H(H 表十六進制) TH0=(EC)H,TL0=(78)H 程式寫法可由下列幾種方式: MOV TL0,#78H MOV TH0,#ECH 或 MOV TH0,#>(2**16-5000) MOV TL0,#<(2**16-5000) #<(2^16-5000)表示將(2^16-5000)運算後取十六進制的 Low Byte 值 (78)H #>(2^16-5000)表示將(2^16-5000)運算後取十六進制的 High Byte 值 (EC)H 或 MOV TL0,#(2**16-5000)˙MOD˙256 MOV TH0,#(2**16-5000)/256 2^16-5000=60536=236×256+120 #(2^16-5000)/256 表示取運算完後的商數(236)D=(EC)H #(2^16-5000)˙MOD˙256 表示取運算完後的餘數(120)D=(78)H 計時/計數器四種工作模式說明如下: 模式 0 模式 0 為 13 位元計時/計數器,電路結構圖如圖 5-6 所示。圖中控 制邏輯電路與圖 5-5 所示一樣,因此啟動方式及脈波源的選擇,請參考 表 4-3。由於 TLX 為低 5 位元(B4~B0),只能計數 2^5=32 個脈波,因此

計時時間/計數目的計算略有不同。 例如:要設計計數 5000 個脈波,則(TLX,THX)的初始值為 TLX=(2^13-5000)˙MOD˙32 THX=(2^13-5000)/32 若使用 Timer0 則程式 MOV TL0,#(2**13-5000)˙MOD˙32 MOV TH0,#(2**13-5000)/32 若使用 Timer1 則程式 MOV TL1,#(2**13-5000)˙MOD˙32 MOV TH1,#(2**13-5000)/32

圖 5-6 計時/計數器 1 模式 0 結構圖

模式 1 模式 1 為 16 位元計時/計數器,電路結構圖如圖 5-7 所示。模式 1 和模式 0 除了計數暫存器位元長度不同外,(模式 0 為 13 位元),其餘 動作方式均相同,請參考模式 0。圖 5-7 計時/計數器 1 模式 1 結構圖

模式 2 模式 2 為 8 位元自動載入計時/計數器,電路結構圖如圖 5-8 所示。 圖中控制邏輯電路與圖 5-5 所示一樣,啟動方法及脈波源的選擇,請參 考表 5-3。TLX 為執行計數脈波的計數器,而 THX 則存放計數暫存器之 初始值,當 TLX 計數器溢位時,硬體除了設定溢位溢味旗號外(TFX=1) 會自動將 THX 的值載入到 TLX 中。圖 5-8 計時/計數器 1 模式 2 結構圖

模式 3 模式 3 工作情形較特殊,計時/計數器 0 分成兩個獨立的 8 位元計時/計數器,電路結構圖如圖 5-9 所示。TLO 使用計時/計數器 0 的控制 位元INT0_______,GATE,TR0,C/T__及 TF0,可規劃成計時器或計數器。TH0 則 由 TR1 控制啟動/停止只能當作計時器,TH0 溢位時 TF1 設定為 1 要求中 斷。 雖然當計時/計數器 0 在模式 3 時使用 TR1 及 TF1 控制位元,但計 時/計數器 1 仍可執行只是溢位時無法產生中斷請求,計時/計數器 1 採 用進入/離開模式 3 方式來停止/啟動計時/計數器 1 的工作。

圖 5-9 計時/計數器 0 模式 3 結構圖

5.4.2 中斷

MCS-51 有五種中斷源,MCS-52 則有 6 種中斷源,各中斷源由中斷 致能暫存器(IE; Interrupt Enable Register)及中斷優先權暫存器(IP; Interrupt Priority Register)控制、各暫存器功能依序說明如下: 中斷致能暫存器(IE; Interrupt Enable Register)中斷致能暫存器的位元格式及功能如表 5-3 所示。EA 元控制所有的 中斷致能/禁能,當 EA=0,則禁止所有中斷 MCS-51/52 不接受中斷處理。 當 EA=1,MCS-51/52 可以接受中斷處理。各中斷源由相對中斷控制元決 定中斷能力,例如當 ET0=0 時,雖然計時/計數器 0 溢位 TF0=1,也無法 執行計時/計數器 0 中斷處理,若 ET0=1,當 TF0=1 會執行計時/計數器 0 中斷處理,各位元被清除為 0,因此要執行中斷功能時必須由軟體加 以設定。

表 5-3 IE 暫存器位元功能表

IE:中斷致能暫存器(Interrupt Enable Register) 位址:A8H(可位元定址)

B7 B6 B5 B4 B3 B2 B1 B0

EA - ET2 ES ET1 EX1 ET0 EX0

EA:整體中斷致能 禁能位元。 EA=1 中斷致能,EA=0 中斷禁能。 -:保留未使用。 ET2:計時 計數器 2 中斷致能 禁能位元(MCS-52 才有) ET2=1 中斷致能,ET2=0 中斷禁能。 ES:串列埠中斷致能 禁能位元。 ET1:計時 計數器 1 中斷致能 禁能位元。 ET1=1 中斷致能,ET1=0 中斷禁能。 EX1:外部中斷 1(INT1 接腳信號)中斷致能 禁能位元。 EX1=1 中斷致能,EX1=0 中斷禁能。 ET0:計時 計數器 0 中斷致能 禁能位元。 ET0=0 中斷致能,ET0=0 中斷禁能。 EX1:外部中斷 0(INT0 接腳信號)中斷致能 禁能位元。 EX0=1 中斷致能,EX0=0 中斷禁能。

中斷優先權暫存器的位元格式及功能表如表 5-4 所示,預設的中斷 優先順序如表 5-5 所示。中斷優先權暫存器規劃各中斷源的中斷權位, 即高優先中斷權和低優先中斷權,如 PT0=1,表示計時/計數器 0 的中斷 屬於高優先中斷,若 PT0=0,表示為低優先中斷。中斷優先權暫存器(IP) 再系統開機或重置時,各位源被清除為 0,各中斷源均為低優先中斷權, 若數種中斷源同時中斷時其優先權順序如表 5-5 所示。

表 5-4 IP 暫存器位元功能表

IP:中斷優先權暫存器(Interrupt Enable Register) 位址:B8H(可位元定址) B7 B6 B5 B4 B3 B2 B1 B0 - - PT2 PS PT1 PX1 PT0 PX0 -:保留未使用。 PT2:計時 計數器 2 中斷優先權(MCS-52 才有) PT2=1 高優先權,PT2=0 低優先權。 PS:串列埠中斷優先權。 PT1:計時 計數器 1 中斷優先權。 PT1=1 高優先權,PT1=0 低優先權。 PX1:外部中斷 1(INT1 接腳信號)中斷優先權。 PX1=1 高優先權,PX1=0 低優先權。 PT0:計時 計數器 1 中斷優先權。 PT0=0 高優先權,PT0=0 低優先權。 PX1:外部中斷 0(INT0 接腳信號)中斷優先權。 PX0=1 高優先權,PX0=0 低優先權。

表 5-5 中斷優先順序表

中斷源 優先順序 IE0 1(最高優先) TF0 2 IE1 3 TF1 4 RI 或 TI 5 TF2 或 EXF2 6(最低優先) MCS-51/52 中斷控制系統如下圖所示。圖 5-10 MCS-51/52 中斷控制架構

各中斷源使用說明如下: 1.外部中斷週邊介面 IC(如 8279、8255)的中斷請求信號,由INT0_______(P3.2)或INT1_______

(P3.3)進入 MCS51/52,外部中斷INT0_______、INT1_______的中斷觸發型態由 TCON 的

若 IT0(IT1)=1 為負緣觸發,當INT0_______ (INT1_______)接腳信號由 Hi 降成 Low(負緣)時,硬體自動將 TCON 的 IE0(IE1)位元設定為 1(具閂鎖作 用),一直等到 CPU 跳到中斷向量位址 0003H(0013H)執行中斷副程式後 硬體自動將 IE0(IE1)清除為 0。由於硬體架構原故,外部中斷請求信號 在負緣之前的高電位信號要維持一個機械週期,負緣之後的低電位信號 最少要維持一個機械週期(震盪頻率為 12MHz 時,一個機械週期為 1μS)

若 IT0(IT1)=0 時,為低電位觸發,INT0_______ (INT1_______)接腳的電位信號必

須維持低電位直到 CPU 執行中斷為止,若 CPU 執行中斷之前,接腳信號 準位變成高電位,則無法執行中斷。另外,低電位觸發時,在中斷服務 程式結束前,若接腳信號保持低電位,則會一直產生中斷。 2.計時/計數器中斷 計時/計數器 0(1)溢位時,硬體自動將溢位旗標 TF0(TF1)設定為 1 (計時/計數器 1 模式 3 例外),直到 CPU 跳到中斷向量位址 000BH (001BH) 執行中斷副程式後硬體自動將 TF0(TF1)清除為 0。 3.串列埠中斷 傳送中斷旗號(T1)或接受中斷旗號(R0)為 1 時,均會產生中斷請求 信號,在執行串列埠中斷副程式時,必須先檢查 T1 和 R1 旗號以確定該 執行傳送或接受中斷服務程式。執行中斷程式時,硬體不會自動清除 T1 和 R1 旗號,必須由軟體清除。 4.計時/計數器 2 中斷 計時/計數器 2 只有 MCS-52 才有、當計時/計數器 2 的溢位旗號(TF2) 或外部旗號(EXF2)為 1 時,均會產生中斷請求信號,再執行計時/計數 器 2 中斷副程式時,必須先檢查 TF2 和 EXF2 旗號以確定中斷原因。執 行中斷程式時,硬體不會自動清除 TF2 和 EXF2 旗號,必須由軟體清除。 程式實作: 本系統規劃以計時器0產生中斷,因此必需先設定TMOD的值為#01H 使用計時 計數器0的16位元計時器模式,把IE設定為#82H也就是將EA 和ET0設為1,以致能計時器0中斷。並在位址001BH放置JMP指令跳到中 斷服務程式所在位址,最後將TCON的值設定為#10H也就是把TR0設為1, 啟動計時器0。程式碼片段如下所示:

ORG 0BH ;假指令,表示以下指令從000BH放起 JMP Address Of ISR ;跳到中斷服務程式位址 …… MOV TMOD,#00000001b ;將計時器0設定為16位元計時模式 MOV IE,#10000010b ;致能計時器0中斷 MOV TH0,#>(2**16-50000) ;這兩行設定計時50ms MOV TL0,#<(2**16-50000) ;在50ms之後溢位,TF0變為1 …… MOV TCON,#00010000b ;啟動計時器0 ;啟動計時器0也可用以下指令 SETB TR0 計時器中斷最長的中斷間隔為65536μs,也就是約65ms,因此我們 將每次中斷的間隔時間設為50ms,並設一計數器COUNTER,每次的中斷 發生時都在中斷服務程式中將COUNTER值加一。等到COUNTER的值為20 時,便將方塊下移,並將COUNTER設為0。 下頁圖5-11為本次專題中斷程式的流程圖。

5.5 顯示原理

繪圖型LCD以擴充記憶體方式驅動,其解碼電路以基本邏輯閘組合 而成,如圖5-12電路圖所示。當(P2.7、A6、A5、A4)=(1、1、0、0)時 CS1=1致能繪圖型LCD左半部,當(P2.7、A6、A5、A4)=(1、1、0、1)時 CS2=1致能繪圖型LCD右半部。以位址信號線A0連接D/I __ 接腳,當A0=0表 示選擇指令暫存器,A0=1時選擇資料暫存器。 在第二章的並列輸入/輸出埠部份曾經介紹:埠 0,當外接擴充記憶 體或介面晶片時,提供擴充電路低八位元位址 (A0~A7) 及資料 (D0~D7);埠 2,當外接擴充記憶體或介面電路時,提供擴充電路高八位 元位址(A8~A15)。因此我們知道當執行 MOVX @DPTR,A 指令時,MCS-51 會以 P0 和 P2 當作存取外部記憶體的位址線。其對應方式如表 5-6 所示。表 5-6 DPTR 驅動繪圖型 LCD 對照表 DPH 為 DPTR 暫存器高 8 位元

DPL 為 DPTR 暫存器低 8 位元

DPH

A15 A14 A13 A12 A11 A10 A9 A8

P2.7=1 - - -

DPL

A7 A6 A5 A4 A3 A2 A1 A0

- A6=1 A5=0 CS1______/CS2 - - - D/I__

程式實作: 依據上述分析,我們以 8040H 表示左半部指令暫存器位址、8041H 為左半部資料暫存器位址,8050H 表示右半部指令暫存器位址、8051H 為右半部資料暫存器位址。並撰寫 WRITE_IR 和 WRITE_DR 兩個副程式分 別控制 LCD 模組的指令暫存器和資料暫存器,繪圖型 LCD 顯示模組 LCG-128064 的詳細控制指令請參考第四章說明。 以控制左邊 LCD 顯示器為例,程式片斷如下:

LEFT_IR EQU 8040H LEFT_DR EQU 8041H RIGHT_IR EQU 8050H RIGHT_DR EQU 8051H WRITE_IR: MOV DPTR,#LEFT_IR ;預備存取左邊 LCD 的指令暫存器

MOVX A,@DPTR ;將指令暫存器資料放入 A,檢查狀態

$1 JB ACC.7,$1 ;檢查 BUSY 旗標,為 1 表示忙碌中 MOV A,#00111111B ;將 LCD 螢幕開啟指令,可參考第四章 MOVX @DPTR,A ;將指令放入左邊 LCD 的指令暫存器 RET WRITE_DR: MOV DPTR,#LEFT_IR ;預備存取左邊 LCD 的指令暫存器

MOVX A,@DPTR ;將指令暫存器資料放入 A,檢查狀態

$1 JB ACC.7,$1 ;檢查 BUSY 旗標,為 1 表示忙碌中 MOV DPTR,#LEFT_DR MOV A,#00111111B ;預備將資料放入資料暫存器 MOVX @DPTR,A ;將資料放入左邊 LCD 的資料暫存器 RET 成品實際照片請參考附錄 B 部份。

第六章 總結

6.1 問題與討論

這節我們將整個系統開發過程中所遭遇的一些問題和一些改進的 想法提出來討論。開發硬體時最麻煩的就是除錯的問題,因為不容易分 辨是硬體的錯誤還是程式邏輯上的錯誤方面的錯誤。 尤其是LCG-128064常常會有同一段程式碼卻有不同結果產生的情 況發生,一開始實作時,常常因為搞不清楚是程式邏輯錯誤或硬體錯 誤,找不出問題而耗費許多時間。常常在軟體模擬確定沒有問題後,再 使用PICE-52模擬卻出現畫面閃爍不定,或是出現非預期動作的情況, 因此除錯的過程非常的沒有效率。 即便如此,這次的專題卻是令我獲益良多,得到了許多在開發系統 的時候的經驗,學會了如何面對問題,也懂得了遇到問題時如何去蒐集 資料解決問題的方法,。這些,都是沒辦法在課堂上學到的。6.2 檢討與改進

整個專題當然還有許多可改進的地方,最主要因為俄羅斯方塊說好 聽點是一個家喻戶曉的遊戲,說難聽點就是了無新意。本次專題之所以 選擇製作俄羅斯方塊也是因為它的普及性,且規則簡單。 如果能夠利用MCS-51/52系統提供的多處理機通訊功能,將程式改 進成為可對戰式的遊戲,除了可大大提高可玩性之外,更可藉機學會多 處理機的通訊架構方式,或許這可以是以後改進的方向。附錄

A 參考資料

參考書籍:[1] 鍾明政,單晶片 8051 原理與實作,長高電腦圖書,Aug.1999 三 版

[2] Han-Way Huang,”Using the MCS-51 Microcontroller”, Oxford University Press,1999

參考文件:

[1] http://www.atmel.com/atmel/acrobat/doc0265.pdf

[2] http://www.keil.com/dd/docs/datashts/intel/ism51.pdf [3] http://www.icbase.com/pdf/HYD/HYD00050106.pdf

圖 B-1 LH-056 模組照片

A:繪圖型 LCD 顯示器──LCG128064 B:2x2 矩陣式按鍵