Integrated Single-Inductor Buck-Boost or Boost- Boost DC-DC Converter with Power-Distributive

Control

Hung-Wei Chang* ,Wei-Hsun Chang **

Dept. of Electrical Engineering National Cheng Kung University

Tainan, Taiwan

E-mail: v2696203@ee.ncku.edu.tw*

n28981280@mail.ncku.edu.tw**

Chien-Hung Tsai Dept. of Electrical Engineering National Cheng Kung University

Tainan, Taiwan E-mail: chtsai@ee.ncku.edu.tw

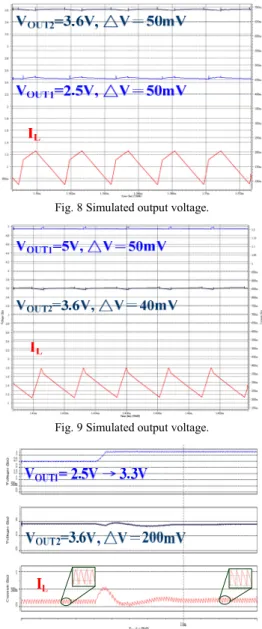

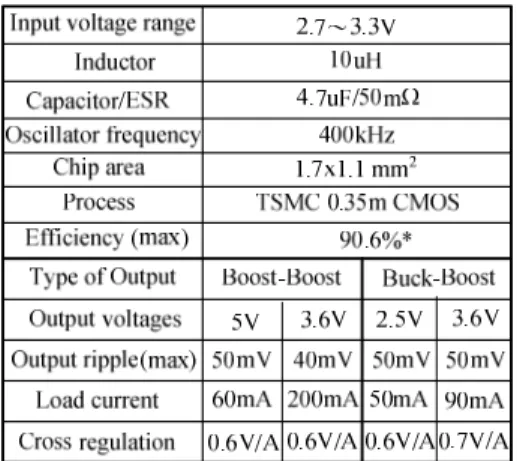

Abstract—This paper presents a fully integrated single-inductor dual-output (SIDO) buck-boost or boost-boost DC-DC converter with power-distributive control. This converter works under voltage mode control to have better noise immunity, uses fewer power switches/external compensation components to reduce cost, and is thus suitable for system on chip (SoC) applications. The proposed SIDO converter was fabricated in TSMC 0.35 μ m 2P4M CMOS technology with input supply voltage 2.7-3.3 V. The first output V O1 can operates either at buck mode or boost mode (output voltage in between 2.5V to 5V), while the second output V O2 can only operates at boost mode (output voltage 3.6V).

Keywords-component; buck/boost-boost converter; single inductor; power distributive convtrol

I. I NTRODUCTION

Today’s modern battery-operated portable products demands for advanced power management integration in SoC chips [1]. To minimize power consumption, multiple supply voltages and dynamic voltage scaling schemes are widely adopted [2]. Recently, several single-inductor multiple-output (SIMO) DC-DC converters [3-10] have been proposed as the most promising solution to minimize component (inductor and power switch) counts/footprints and production cost. However, there exists many design challenges for the SIMO converters, such as cross-regulation, efficiency, system stability, and flexibility, for achieving better step-down and step-up conversion.

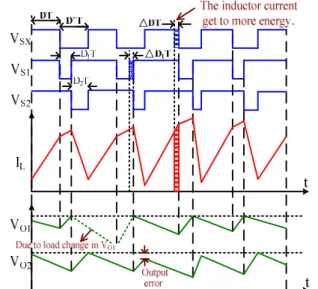

The operational principles of SIMO DC-DC converters are based on time-multiplexing approaches [11], which deliver energy stored in the inductor to each output in every switching cycle by means of different feedback control mechanisms.

They can be classified as voltage control [3-5], peak current control [6-7] [10], and charge control [8-9]. In terms of inductor current waves, converters are divided into discontinuous conduction mode (DCM) [3] [7], pseudo- continuous conduction mode (PCCM) [4] [8-9], continuous conduction mode (CCM) [5], and DCM/CCM [6]. They also can be sorted into boost/boost converters [3-4] [6-7], buck/buck converters [5], and hybrid buck/boost converters [8-10] by using output voltage types. For the embedded SIMO

DC-DC converter in SoC application, although voltage control is slower than current mode control, it has no external current sensors and good noise immunity. Hence, voltage control is more suitable than current control in embedded SoC environments. Converters operated in DCM or PCCM of the conventional time-multiplexing approaches [3-4] will avoid cross-regulation, but DCM suffers large current ripples and has current driving problems. Although PCCM overcomes limitations of DCM, it dissipates unnecessary power due to non-zero current in resistance of inductor and the freewheel- switch. Converters operating in CCM suffer serious cross- regulation problems and are difficult to consider stability analysis [4]. In general, SIMO converters have to combine several compensators which have the same number of output voltage. Recently, there is a reference [6] proposes ordered power-distributive control (OPDC), which can operate in DCM/CCM, and using only one compensator. Besides, compared with familiar SIMO converters [3-4], this time- multiplexing power-distributive approach of [5-9] has less switching number in one cycle, therefore it increase efficiency.

(a) (b) (c) Fig. 1. Architecture of the buck-boost dc-dc converter.

In many applications, there are need for a single-inductor dual-output DC-DC converter with one output voltage set to be lower (buck) and another higher (boost) than the supply voltage. In traditional SIDO buck/boost converters shown in Fig.1 (a), there are five power switches [10]. Fig.1 (b) is another implementation of four power switches [8-9]. This paper adopts the Fig.1 (c) (reduce freewheel-switch S 4 of Fig.1 (b)) topology which has three power switches, and it uses power-distributive control from [6] and applies them to voltage control. Thus, there needs only one output compensation loop, which reduce the amount of external

PEDS2009

1184

compensated components used, such as [6]. Moreover, this paper also extends the availability of Fig.1(c) topology to implement Buck-Boost or Boost-Boost converter according to different demands.

In this paper, operation and control of the proposed SIDO converter and the effect of cross regulation are discussed in Section II. Section III presents circuit design and implementation issues. Post-layout simulation and results are shown in Section IV. The conclusions are given in Section IV.

II. O PERATION OF SIDO B UCK -B OOST C ONVERTER

Fig. 2. Architecture of the proposed buck-boost or boost-boost dc-dc converter.

A. Architecture and Control Strategy

The architecture of the SIDO buck-boost or boost-boost DC-DC converter in power-distributive control with one compensator is shown Fig. 2. The output V O1 is controlled by the comparator loop, which determines the switching from V O1 to V O2 . The output V O2 is controlled by compensation loop that is responsible for compensating the total control loop.

The logic control generator is used to control the timing of the converter. The zero current detectors prevent the reversed inductor current.

DT

I L

V S2

V S1 V SX

t

I L

t V O1 <V IN

V O1 >V IN

V O2

V O1 V O2

V O2 V O1 V O2

V O1

V O1

D1T

D2T