多媒體無線接收機系統單晶片設計技術之研究(1/3)

子計畫三:數位基頻帶處理器之研製

Design and Implementation of A Digital Baseband Pr ocessor 計劃編號:NSC89-2215-E-002-027 執行時間:1999/8/1-2000/7/31 計劃主持人:龐台銘教授 摘要 本計畫的目標是發展一個數位基頻信 號處理器,它將大部份數位無線系統 所 需 元件 整 合 成 一 個 可 定 製 的 單 晶 片。在這個年度中我們研究了許多現 有的信號處理器架構,並採用了一個 RISC-like 的架構實現第一版 DSP。 關鍵詞

Digital Signal Processor, Modulus ad-dressing , MAC.

Abstr act

We aims at developing a digital base-band processor that integrates all the digital components needed for most digital wireless systems in a single-chip customizable solution. In this year, we studied many architectures of existing DSPs, and adopt one RISC-like archi-tecture to implement the first DSP. 一、計劃緣由與目的 最近幾年隨著行動電話及網際網 路的迅速發展,使得行動電話手機和 高速數據機的需求大增。以往這兩項 產品用來進行資料編碼、解碼、壓縮、 解壓縮及信號處理的核心運算單元, 皆以特定用途積體電路(ASIC)或特定 用途信號處理器(ASSP)實現。但隨著 積體電路製程的進步,邏輯閘的速度 增加,使可程式信號處理器也可以滿 足原來要特定用途信號處理器才能實 現的功能。而且可程式信號處理器允 許下載新軟體就可升級的優勢,和可 縮短產品研發時間的特點,使得越來 越多的行動電話手機和數據機使用可 程式信號處理器。而未來的趨勢,在 無線通訊中除了原有的語音服務,也 將整合數據傳輸及影像傳輸。延續在 行動電話手機和數據機上的優勢,可 程式信號處理器在新一代的無線通訊 產品中預計也將被廣泛的使用。但因 為提供的服務增加了,硬體效能的需 求也提昇了,研製一個更高效能的可 程式信號處理器是必須的。 二、研究方法及成果 一個可程式化信號處理器為了滿足 應用上速度的需求,必須要有以下幾 個特點:

1. Modified Harvard Architecture, 以 避免記憶體匯流排造成的瓶頸。 2. 快速的乘法累加器,以加速乘法累 加運算。 3. 特殊的迴圈控制硬體,以加速信號 處理中常見的迴圈運算。 4. 兩個資料位址產生器,使得一個時 脈週期可讀取兩筆資料。

5. Circular Addressing Capability,以 加速濾波器之運算。

6. Bit Reversal Addressing Capabil-ity,以加速 FFT 之運算。 7. 支援 round, saturate 之硬體。 8. 計算指數之硬體,以加速正規化 (normalize)的運算。 我 們 所採 用 的 架 構 皆 滿 足 以 上 的 特 點,並說明如下。 (1)架構簡介 整個架構的方塊圖如圖一。共有三 個 算 數 運 算 單 元 : ALU, MAC, SHIFT,兩個位址產生器,一個程式控 制 器 (program sequencer)。七個匯流 排 : PAB(program address bus), PB(program bus), DAB(data address bus), DB(data bus), CAB(coefficient address bus), CB(coefficient bus),

R(internal bus)。每個算數運算單元的 輸 入 及輸 出 都 有 暫 存 器 , 以 暫 存 資 料。而每個暫存器都可經由 DMD bus 存取。另外每個算數運算單元的輸出 暫存器都接在 R bus 上,並連接到每個 算數運算單元的輸入埠,因此任一個 算數運算單元的結果可直接成為另一 個算數運算單元的輸入,避免多餘的 資料搬動。以下分別介紹每個方塊的 細部架構。 [1]ALU 架構如圖二所示。運算電路即為圖中 的 16-bit ALU,在 ALU 的兩個輸入埠 前各有兩個 16-bit 暫存器組 AX, AY, 而輸出埠後也有一個 16-bit 暫存器 AR,另外還有一個 16-bit 回授暫存器 AF,可使 ALU 的輸出直接當作往後運 算的輸入。如前所述除了 AF 之外的暫 存器皆可由 DMD bus 存取,另外 AY 也可由 PMD bus 輸入資料。 [2]MAC 架構如圖三所示。包括了一個 17x17 bits 的乘法器,一個 40-bit 的加法器, 兩個 16-bit 輸入暫存器組 MX, MY,一 個 40-bit 的輸出暫存器 MR0, MR1, MR2,一個 16-bit 回授暫存器 MF。如 同 ALU 中的輸入暫存器組一樣,除了 MF 之外的暫存器皆可由 DMD bus 存 取,MY 也可由 PMD bus 輸入,因此 在一個週期內可同時經 DMD bus 輸入 input data 至 MX 經 PMD bus 輸入 coefficient 至 MY,並執行乘法累加運 算,以加速濾波器的運算。 [3]SHIFTER 如圖四所述,這個單元不只包括 shifter array , 還 包 括 一 個 指 數 產 生 器 (Exponent detector) , 一 個 比 較 器 (compare)及一些輸出輸入暫存器。這 個單元可支援三類運算: (1) 位移運算(shift):可將 16-bit 的輸 入向左或向右位移 16-bit,得到一個 32-bit 的輸出。欲位移的資料由 SI 暫 存器或 R-bus 輸入至 shifter array 的 I 埠,並由 C 埠指定位移量,結果由 O 埠輸出經 or/pass 電路存入 SR 暫存

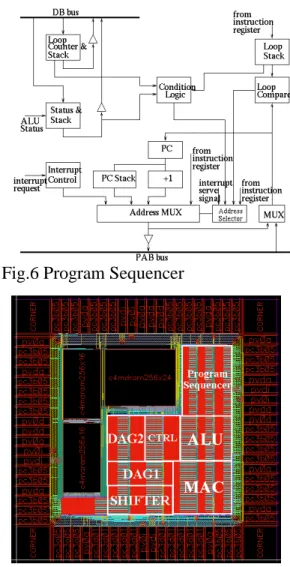

器。其中 or/pass 的電路用來支援多位 元組資料(multi-words data)的位移。 (2) 指 數 判 斷 (exponent detector, SE register):用來判斷一筆資料的 sign bit 位元數,如(1111_10xx_xxxx_xxxx)2有 5 個 sign bit,x 為 don’t care。得到的 結果存入 SE 暫存器。此項功能可加速 正規化(normalize)的運算。 (3) 區塊指數產生(compare, SB):用來 支援對一個區塊內的資料進行整體的 正 規 化 。 如 一 個 區 塊 內 的 資 料 為 (0000_1xxx_xxxx_xxxx, 110x_xxxx_xxxx_xxxx, 1111_11xx_xxxx_xxxx)2,其中 sign bit 個數最少的為第二筆資料的 2 個,因 此為了提高 16-bit 能表示的精確度,並 顧及記憶體空間的考量下,將區塊內 的每個數都向右位移 1bit。這個電路的 功能就是找出最少的 sign bit 數。 [4] 位址產生器 架構如圖五所示。共有三個暫存器組 I, M, L。I 儲存欲存取的記憶體位址, M 儲存在存取記憶體後 I 要加上的位 移量(offset),L 存宣告的環狀記憶體 (circular buffer)大小。Modulus address circuit 可支援線性及環狀位址產生,其 功能依選定的 L register 而定,若 L 的 值為零即為線性定址,非零即為環狀 定址。另外在位址產生器 1 的輸出埠 有一個位元反向器,可使原輸出值的 MSB 變為 LSB,以達成 bit-reversal 功 能。 [5]Program sequencer 這個單元的主要功能是控制程式的流 向,及處理中斷要求。其架構如圖六。 其中 Loop Counter & Stack, Loop Stack and Loop compare 是用來加速迴圈執 行的硬體,它們可以判斷迴圈執行的 次數、終止條件,使得只要兩個指令 即可執行迴圈(一個指令指定迴圈執行 次數,一個指定迴圈範圍和終止條件)。 (2)管線設計(pipeline design) 在這個 DSP 中我們使用了五階的管 線。 [1] prefetch:在這個週期的開始,將

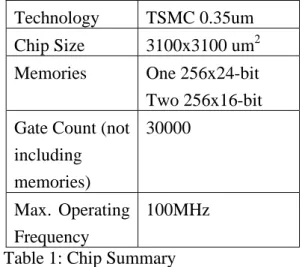

欲 讀 取 的 程 式 記 憶 體 位 址 (program address)放到 PAB,在週期結束時,把 PAB 上的位址寫回 Program Counter, 同時程式記憶體也把 PAB 上的位址寫 入位址暫存器。 [2] fetch:在這個週期的開始,程式 記憶體依據位址暫存器內的值,讀取 資料並放在 PB 上,在週期結束時,把 PB 上 的 程 式 碼 寫 入 程 式 暫 存 器 (instruction register)。 [3] decode:在這個週期的開始,依據 程式暫存器內的程式碼,解出程式的 型態,及接下來的兩階管線該執行的 動作,在週期結束時,把解碼後的結 果寫入暫存器。 [4] access:在這個週期的開始,將欲 存取的資料記憶體位址(data memory address)放到 DAB,在週期結束時,把 資料位址產生器算出的下一個位址寫 回 I 暫存器,同時資料記憶體也把 DAB 上的位址寫入位址暫存器。 [5] execute:這個階段可能有兩種動 作被執行: (1) 資 料 的 存 取 : 在 這 個 週 期 的 開 始,資料記憶體依據位址暫存器內的 值,讀取資料並放在 DB 上,在週期結 束時,把 DB 上的資料寫入指定的暫存 器。或在週期的開始,被指定的暫存 器將資料放在 DB 上,而資料記憶體依 據 位 址暫 存 器 內 的 值 , 在 週 期 結 束 時,把 DB 上的資料寫入指定的記憶體 位址。 (2) 算數運算:在這個週期的開始, 依據解碼的結果執行運算,在週期結 束時,把運算結果寫回指定的暫存器。 我們已經完成合成後的模擬及晶片佈 局,其佈局結果及與現有 DSP 效能比 較列於表一及表二。 Technology TSMC 0.35um Chip Size 3100x3100 um2 Memories One 256x24-bit Two 256x16-bit Gate Count (not

including memories) 30000 Max. Operating Frequency 100MHz Table 1: Chip Summary 三、結論與討論

在這個年度中我們研究了許多現 有的信號處理器架構,並採用了一個 RISC-like 的架構實現第一版 DSP。 四、參考文獻

[1] Analog Device Inc., “2100 family user's manual”,.

[2] Analog Device Inc., “Digital Signal Processing Applications Using The ADSP-2100 Family”.

[3] Wai Lee et al.,”A 1V Programmable DSP for Wireless Communication”,

IEEE JSSC, vol. 32, pp.1766-1776, Nov. 1997.

[4] Texas Instruments Inc.,

TMS320C54x User’s Guide, 1995.

[5] B.W. Kim et al,”MDSP-II: A 16-Bit DSP with Mobile Communication Ac-celerator.”, IEEE JSSC, vol. 34,

pp.397-404, Mar. 1999.

[6] Dirk Weinsziehr et al,”KISS-16V2: A One-Chip ASIC DSP Solution for

GSM”, IEEE JSSC, vol. 27,

pp.1057-1066, July 1992.

Operation/Cycles TI C54x LODE MDSP-II Proposed

FIR N+4 N/2+A N/2+B N+11

IIR 2N+11 N+C N+D 2N+16

Adaptive FIR(LMS) 2N+14 X X 4N+22

Fig 1 Overview of the DSP

Fig 2 ALU architecture

Fig. 3 MAC architecture

Fig. 4 Shifter architecture

Fig.5 Data address generator archi-tecture

Fig.6 Program Sequencer