行政院國家科學委員會補助專題研究計畫

□ 成 果 報 告

;

期中進度報告

智慧型車輛之即時影像系統與影像追蹤技術研發(2/3)

Development of a Real-Time Image System and Image Tracking

Scheme of Intelligent Vehicles (2/3)

計畫類別:□ 個別型計畫

;

整合型計畫

計畫編號:NSC 91-2213-E -009-033

執行期間:

91 年 08 月 01 日起至 92 年 07 月 31 日

計畫主持人:

宋開泰 教授

共同主持人:

計畫參與人員: 王忠富、黃信益、邱黃正憲、沈柏翰

成果報告類型(依經費核定清單規定繳交):

;

精簡報告 □完整報告

本成果報告包括以下應繳交之附件:

□赴國外出差或研習心得報告一份

□赴大陸地區出差或研習心得報告一份

□出席國際學術會議心得報告及發表之計畫各一份

□國際合作研究計畫國外研究報告書一份

處理方式:除產學合作研究計畫、提升產業技術及人才培育研究計畫、列

管計畫及下列情形者外,得立即公開查詢

□涉及專利或其他智慧財產權,

;

一年□二年後可公開查詢

執行單位:

國立交通大學電機與控制工程學系

摘 要

本計畫主要目的在設計、製作及測試可用於智慧型車輛之即時影像系統,整合電腦視覺 硬體與軟體以展示實用功能。本計畫主要發展方向有三項:1.移動中車輛之影像追蹤與位置 估測技術開發、2.智慧型車用即時影像處理架構設計與製作及 3.即時影像處理感測晶片設計 與製作。本計劃在第二年執行期間已經完成影像處理硬體電路製作及整合測試,主要利用 Philips SAA7111AHZ 視 訊 晶 片 擷 取 影 像 , 將 CCD 類 比 訊 號 (NTSC 類 比 訊 號 ) 轉 換 成YUV(4:2:2),並以 Altera Flex10K 200s(Field Programmable Gate Array, FPGA)做為系統之數位

影像處理器,進行影像擷取控制、背景影像移除與即時影像邊緣處理。在影像處理部分,完 成以 SUSAN 法則來執行影像邊緣處理,並於 FPGA 電路上實現即時化處理。本電路之邊緣 影像處理,採用序列處理方式設計,每秒最快可處理 60 張圖場,所得邊緣資訊透過 PCI 介面 傳給主電腦,主電腦再利用這些邊緣資訊進行車輛監控處理。

Abstract

This project aims to design, implement and test a real-time image system for intelligent vehicles. The developed image processing platform can be used to integrate hardware and software to demonstrate vehicle monitoring and safety applications. The real time image system not only can provide the driver video information of the vehicle surroundings, but also give processed data to indicate dangerous situations and assist the driver with more prompt response. In the second year of the project, a real-time image processing system has been designed and realized. In this system a Philips SAA7111AHZ video chip is used for NTSC CCD image acquisition. An Altera Flex10K200s FPGA is employed to realize image-acquisition control, background removing and edge detection. We developed an efficient circuitry for hardware realization of SUSAN algorithm for real-time edge detection. The host computer obtains the processed image data through PCI bus interface. The edge information can be used for monitoring and control purpose.

一 、計劃緣由與目的

智慧型車輛發展之目的主要希望透過特殊軟硬體之建立與結合,提供車外交通路況之即 時資訊,減少車輛事故之發生,並提高道路上行駛之汽車之安全性。軟硬體技術包括了微電 子 技 術 (Microelectronics) 、 人 工 智 慧 機 器 人 (AI robotics) 、 感 測 器 (sensing) 、 通 訊 系 統 (communication) 及 控 制 (control) [1] , 提 供 車 外 資 訊 一 個 重 要 媒 介 為 電 腦 視 覺 (Computer

vision),利用影像處理技術來獲取即時資訊,必須以硬體實現才可達成即時化目標。

智慧型車輛的一個重要項目為電腦視覺(Computer vision),利用此技術可求得車外路況的 交通資訊。一般即時電腦視覺技術可分為下列三項:影像擷取設備、即時影像處理器與演算 法。影像擷取設備為一個影像識別系統的基本元件,一般 TV cameras 的亮度對比(Intensity contrast) 500:1,但 ITS 的應用須求為對每一圖場而言需要 10,000:1 動態範圍( dynamic range)。

即時影像處理器關心著系統執行的效率,一般 ITS 的應用多採用係處理器的架構,將不同的 演算法利用不同的處理器執行,最後再將其資訊整合,求得所需的交通參數。1995 年, Ninomiya.et.al.利用多重處理器的架構應用於智慧型汽車系統 [2],其將處理器分四大部份:

樣板比對模組(Template matching module)、立體視覺模組(Stereo vision module)、光流模組 (Optical flow module)及邊緣資料擷取模組(Edge segment extraction module),四個模組分別利

用 TMS320C40 實現,最後再由電腦端將四大部份所求得資訊匯整處理。 多處理器的架構之下,每一個模組的都有符合其特性之處理器,可採用一般處理器 CPU、 DSP、FPGA 或其於特殊演算法晶片。各類處理器必須配合演算法來做選擇,即時系統的考量 都會以單一晶片處理特殊演算法的問題。1998 年,Martin et.al. 以可程式化的混合信號陣列 理器[3],操作速度為 0.8MIPS,在 5V 是的消耗功率為 1.8mW,處理器為一個陣列執行邊緣 偵測和子像素解析度的演算法。 在發展即時影像處理系統,考慮使用上述中以晶片實現的方式完成,但發展為求可程式 化的便利,但又有晶片實現的需求時,可考量利用 FPGA 實現的方。2001 年,Jamro. and Wiatr 以 FPGA 的架構實現 Convolution Operation[4],應用於即時影像處理系統。1994 年,Box 以 FPGA 的架構實現可配置的前置處理器[5]。

都以 FPGA 實現。2000 年,Torres-Huitzil. and Arias-Estrada.以 FPGA 執行邊緣偵測(SUSAN 演算法)[6]。各類邊緣偵測的演算法其效能也有所差別,但常用邊緣偵測的演算法為 Sobel, 但其效能並不如上述作者所使用的 SUSAN 演算法,其以 512x512 影像效能比較如表 1 所示, 表 1 中時間為代表邊緣偵測運算時間,並不包含影像擷取時間,本計畫將提出一套可以即時 實現 SUSAN 演算法的架構,整合影像擷取與邊緣偵測於單一電路中,利用硬體加快其運算 速度。 本計畫本年度主要目的在設計、製作與測試適用於智慧型車輛之即時影像邊緣處理裝置, 本影像邊緣處理裝置可以擷取道路影像,並即時進行背景移除與邊緣處理處理,再透過 PCI 介面將邊緣資訊提供給主電腦,讓主電腦依據這些邊緣資訊進行車輛追蹤。

二、研究方法與成果

2.1 系統架構設計

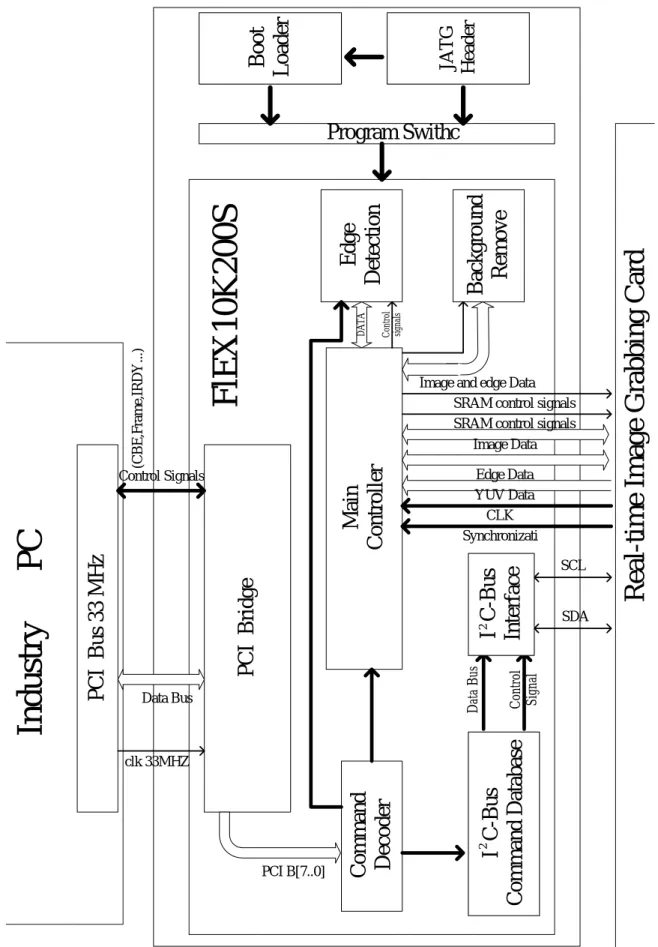

本計畫所發展之獨立式影像處理系統之系統架構如圖 1 所示。其中即時影像處理單元包 含後兩部份即時影像擷取單元及影像前置處理單元。即時影像處理單元依其功能可分為下列 6 項:1.影像擷取模組、2.Altera Flex10K 200s(Field Programmable Gate Array, FPGA)、3. 邊緣

影像處理,4.背景影像處理、5. I2C 介面控制電路、6. PCI Target Interface Controller 。圖 2 為 影像擷取單元系統方塊圖,圖 3 為即時影像前置處理單元系統方塊圖。本架構分為兩大單元, 其功能如下: 1. 影像擷取單元: 採用 Philips SAA7111AHZ 視訊晶片作為擷取影像,將 CCD 類比訊號(NTSC 類比訊 號)轉換成 YUV(4:2:2)訊號。 2. 即時影像前置處理單元:

(1) Altera Flex10K 200s FPGA:

利用 FPGA 做為系統輔助處理器,主要目在於影像資料存取控制、影像前置處理、 I2C 介面設計、PCI 介面設計。

(2) 邊緣影像處理:

主要利用 SUSAN Algorithm 做為邊緣影處理法則,邊緣影像處理法則主要利用 Altera Flex10K 200s FPGA 完成硬體實現的方式。

(3) 背景影像處理:

主要功能在於規劃儲存原始背景影像及移除背影之功能,主要利用 Altera Flex10K 200s FPGA 完成硬體實現的方式。

(4) I2C 介面控制電路:

主要功能在於設定規劃 I2

C 訊號時序(SDA,SCL),主要利用 Altera Flex10K 200s FPGA

完成硬體實現的方式。 (5) PCI Target 介面控制:

表 1 Sobel 及 SUSAN 演算法效能比較[6]

Machine Architecture Timing Algorithm SPARC-20(model 40) VonNeumann 3.60 sec

i-860 Pipelined 51.9 ms

Splash-2 FPGA based 13.89 ms CM*-5 MIMD(512 PEs) 40 ms MasPar-2 SIMD(4K Pes) 84 ms DateCube Pipelined 13.8 ms Pentium III 450 MHz 128M RAM Software implementation 53 ms Sobel .3x3 mask

SUSAN Arch. FPGA -Pipeline 8.35 ms SUSAN .7x7 mask PCI Interface I N D U S T R I A L P C Intergrated Software PCI Interface Video Grabber Card N T S C I C-Bus Interface YUV-to-RGB and Output Formater S A A 7 1 1 1 A V i d e o Ouput PCI Interface Controller I C-Bus Interface Main Controller FLEX EPF10K200S Boot load Program Switch Image Data Background Data Edge Data Integrated Information Flex10K PCI Development Board

J T A G Header 2 S D A S C L Image Memmory S R A M 512Kx8bit S R A M 512Kx8bit 2 圖 1 影像擷取及即時前置影像處理單元系統架構

Memory(512K*8bit) Background Image Data

Memory(512K*8bit) Edge Data Interface Bus C I2 − SCL SDA Luminance Circuit Synchronization Circuit Clock Circuit Image Data (NTSC) Environment YUV(4:2:2)

Digital Image Data LCC LCC2

HREF VREF RTS0

Cotrol signal (OE,WE,CE)

Data Bus

Data Bus

Cotrol signal (OE,WE,CE)

Real-time Image Processing Card

圖 2 影像擷取卡系統架圖

2.2 影像擷取模組

本計畫採用 Philips 公司之 SAA7111AHZ 影像視訊晶片進行影像擷取[7],其主要特點如 下: (1) 兩個類比視訊訊號輸入(NTSC or PAL)。 (2) 對於類比視訊訊輸入可設定為自動調整其增益。 (3) 兩個內建類比 anti-aliasing 濾波器。 (4) 自動偵測 50/60 Hz 圖場頻率且能 PAL 與 NTSC 標準之間自動切換。 (5) 可控制影像之亮度、對比與飽和度。PCI Bridge

Industry PC

PCI Bus 33 MHz

Command

Decoder

Main

Controller

Real-time Image Grabbing Card

Background

Remove

Edge

Detection

FlEX10K200S

Program Swithc

clk 33MHZ Data Bus Control Signals(CBE,Frame,IRDY...)PCI B[7..0]

Data Bus Control Signal

SCL SDA Synchronizati CLK YUV Data Edge Data Image Data SRAM control signals SRAM control signals Image and edge Data

DAT A Cont rol si gna ls

I C-Bus

Interface

I C-Bus

Command Database

22Boot

Loader

JATG Header(6) 影像輸出格式有:

i. 565 RGB (16-bit)

ii. 888 RGB (24-bit)

iii. 411 YUV (12-bit)

iv. 422 YUV (16-bit)

v. 422 YVU (CCIR-656 12-bit)

(7) 可利用 I2C Bus 來規劃上述之設定。

本計畫所規劃的訊號規格為 60Hz 圖場頻率 NTSC 訊號輸入,影像輸出格式為 422 YUV (16-bit)如圖 4 所示,而目前系統影像需求為灰階影像,因此可直接採用 422 YUV (16-bit)中

Y(8-bit),Y 資料也就相對於灰階影像之像素灰階值。

2.3 I

2C-Bus 介面設計

I2C (Inter-Integrated Circuit) Bus 為所發展的雙向 2 線式串匯流排標準[8 ],其主要優點為

只需 2 條線傳輸線(SDA 與 SCL)便可以對 IC 內部之存暫器進行設定,而且此介面可串接多個 元件,不需經過解碼電路,而由於 I2C Bus 介面本身為 Open Drain 或 Open Collector,因此 在使用上必需外將 2 條線傳輸線 SDA 與 SCL Pull High。,SDA 主要負責傳輸真正的資料, SCL 則是負責同步用的。其傳送方式說明如下,起始傳送狀態當 SCL 為 Logic High 時,若

停止傳送狀態當 SCL 為 Logic High 時,若 SDA 有一 Logic Low 轉 Logic High 的情形發生 時,則 Device 會認知到一個傳輸已經結束。位元傳送方式為 SCL 為 Logic High 時,SDA 的值才是正確的,因此 Host 若要傳輸下一個 Bit ,資料的改變必須在 SCL 為 Logic Low 時 更改。而 I2C-bus 每傳送 8Bit 就必需去確定 Acknowledge,外 Acknowledge 這個 Bit 對於 Host 來說,必須在 SDA 這個腳位上放 Logic High ,這時 Device 若有正確回應的話,會在 SDA 上 放 Logic Low 表示確認。在本系統中主要利用 I2 C 介面規劃 SAA7111AHZ 影像視訊晶片,因 此在 Altera FLEX10K 中規劃一 I2 C 介面如下圖 5 所示,其 I2C 介面參數及腳位功能如表 2 所 示,圖 6 為 I2 C Bus 起始傳送時序圖,圖 7 為 I2C Bus 連續傳送時序圖。 圖 5 I2 C 介面 圖 6 I2 C Bus 起始傳送時序圖

表 2 I2

C 介面參數及輸入腳位功能表

PARAMETERS

DIVISOR The DIVISOR value should be set to.You should then set the divisor value to 10MHz / 400kHz = 25.

INPUT PORTS

SysClk System clock input. Clk_en Clock Enable input.

/reset Asynchronous reset of all registers within the I2C Controller. Din[7..0] Parallel data input.

Ack_Tx Acknowledge to send, when in receiver mode. Cmd_Stop Generate STOP condition on I2C port.

Cmd_Start Generate START condition and send slave address on I2C port. Cmd_Send Send a byte to I2C port.

Cmd_Receive Receive a byte from I2C port.

Execute After Execute goes to logic high then on the next positive edge of SysClk, Din[], Ack_Tx, Cmd_Stop, Cmd_Start, Cmd_Send, Cmd_Receive will be sampled, and execution will start.

OUTPUT PORTS

Dout[7..0 Parallel data output.

Ack_Rx Last received acknowledge.

Busy While Busy is high, no new commands are accepted. SDA I2C data

SCL I2C clock

圖 7 I2

2.4 影像擷取控制電路

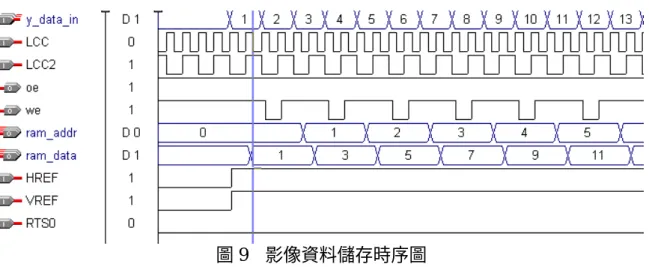

影像擷取控制電路主要目的在擷取 SAA7111AHZ 視訊處理晶片由類比 NTSC 訊號轉換至 422 YUV (16-bit) 數位訊號,將擷取之數位訊號輸出至記憶體,要達成上述部份之時序控制, 必須提供適當的訊號來做時序之動作,以下將分別對於擷取 SAA7111AHZ 視訊處理晶片訊號 及存儲時序做說明。 目前由視訊處理晶片訊號輸出 422 YUV (16-bit) 數位訊號,而目前系統只取灰階影像, 因此在 YUV 16-bit 輸出只取 Y channel 訊號輸出為 8-bit,而 YUV 視訊輸出方式為奇偶圖場 分離,其完場圖場大小最大為 720x480,但本系統只取偶圖場,因此必需對於每一條掃描線 做 down sample(如圖 8 所示),如此一偶圖場最大為 360x240,而本系統應用上只取 320x240 之影像資料。圖 8 中 LCC 及 LCC2 為 SAA7111AHZ 輸出之振盪同步訊號,HREF 及 VREF 分別為垂直同步訊號及水平同步訊號,RTS0 為奇偶圖場分離訊號,當 RTS0 為 Low 表示目 SAA7111AHZ 目前輸出偶圖場影資料,亦即所要之影像數位資料。而因為目前影像資料只需320x240 之影像資料,因此由圖 8 可看出 Y channel 只取 1,3,5,7….等訊號。利用 Load Data 致

能後,可得如圖 9 之資料儲存波形,

圖 9 影像資料儲存時序圖

2.5 背景影像移除控制電路

本裝置增加背景影像移除功能,將可應用於一般道路交通監視,可以取得移動車輛或機 車的資訊,對於長期不變的資訊(車道線、班馬線或標誌…等),對於影像追蹤並無實質的意 義,因此我們將這些無用的資訊移除,可增加影像的單純化及處理的穩定性。取得背景資訊 的方式,主要利用判斷目前車道是否存在車輛,做為背景更新的依據,因背景的資訊可能會 依其時間而改變甚大(時間不同光線改變),因此必須在固定時間內去改變所需的背景資訊, 其更新的方式如圖 10 所示,由圖可知其更新的依據為車輛是否存在車道,如車道內 10 秒內 都無車輛進入,將進行背景影像更新,其方式為讀取現刻之影像做為背景影像資訊。2.6 影像邊緣偵測法則與控制電路設計

為了達成即時的邊緣處理,必須採用較為快速之影像邊緣偵測方法。本研究採用 Susan Algorithm[6],求得影像邊緣的資訊,在即時性的考量之下,利用 FPGA 來實現 SusanAlgorithm,而實現的方式本論提出一序列資料處理的方式,即時處理序列影像。在此即時的

定義為處理每張影像時間為 1/60 秒,換而言之也就是必需即時的處理,每一序列資料,即可 達成所需的即時性。Susan Edge Detector 可使用 3x3 的 mask,或使用 37pixels 的 circular mask, 目前所採用的為較簡易的 3x3 mask 以提升所需的速度,而將 3x3mask 所得資料放入一暫存 區域,在此定義為區域為 USAN(Univalue segment assimilating nucleus),其演算的過程如下:

Image Grabber

Background Image Memmory Subtract Image from

Background Image

Read Data

Update Background Image If (Timer>10s &&

No Car in the Image) Timer Reset False True New Image 圖 10 背景影像更新流程圖 Step1:將 mask 所包圍的點,全部都和中心點做比較,其方式如下所示: > − ≤ − = t r I r I if t r I r I if r r c ) ( ) ( 0 ) ( ) ( 1 ) , ( 0 0 0 (1) 其中 t: threshold r0:mask 中心點 r:mask 中心點以外其他點 I(r0):中心點的影像強度 I(r):mask 中心點以外其他影像強度

Step2:由將step1 所比較的結果,以 mask 為中心的方式相加,其方式如 2.3 節所示:

∑

= r r r c r n( 0) ( , 0) (2) n(r0): 定義為 USAN 中 r0的值Step3:將USAN 所求的值與 Threshold g 做比較,如果所求為邊的資訊 g=3nmax/4,而所求所

角的資訊,g=nmax/2,其方程式表示如下: < = otherwise g r n if r R 0 ) ( 1 ) ( 0 0 (3) 以下將偵對上述演算法依其步驟說明如何設計實現一即時邊緣處理架構: 由(1)式中了解,假設一影像資訊如圖 11 所示,以 image(3,3)為中心點時,其必需和其他 8 個點做比較,相同的以 image(2,2)為中心點時在比較時必需同時取得其他 8 點的數值,但

image(3,3)為中心點時,己經和 image(2,2)做過比較,所以如果在以 image(2,2)為中心時再做一

減少不必要的運算及資料讀取的時間,進而提升演算速度,以下將對上述問題說明解決的方 式。 實際的影像資訊為串流輸入,其資訊源源不斷,因此必需即時的完成資訊處理。如果要 利用資訊時再由記憶體讀取出資料,其速度將被限制於記憶體的讀取速度。在以上描述中, 了解每一影像點最少必需做 8 次運算,其中包括水平運算 2 次,垂直運算 2 次,右斜運算 2 次,左斜運算 2 次。因資料串列輸入原故,因此同一時間內只能有 4 個運算,在同一資料的 下一個列時再做 4 個運算。本計畫利用上述關念設計一即時處理法則,可達成每秒 60 個圖場 (frame)之 320×240 像素 CCD 影像邊緣抽取,設計其影像邊緣處理架構如圖 12 所示。由影像 邊緣處理架構圖中,設計四個運算單元,水平運算、垂直運算、右斜運算及左斜運算,以將 分別說明其運算方式。 1) 水平運算處理單元 其主要運算相鄰像素比較如圖 15 所示,image(1,1)與 image(1,2)比較,image(1,2)與 image(1,3)比較,由圖 14 所示本系統設計一 Delay1 clock 於影像輸入端,將可得到現在時

刻輸入影像資料與上 1 Clock 所輸入影像,如此將可完成水平運算。 (1,1) (1,2) (1,3) (1,4) (1,5) (1,6) (1,7) (1,8) (1,9) (2,1) (2,2) (2,3) (2,4) (2,5) (2,6) (2,7) (2,8) (2,9) (3,1) (3,2) (3,3) (3,4) (3,5) (3,6) (3,7) (3,8) (3,9) (4,1) (4,2) (4,3) (4,4) (4,5) (4,6) (4,7) (4,8) (4,9) (5,1) (5,2) (5,3) (5,4) (5,5) (5,6) (5,7) (5,8) (5,9) (6,1) (6,2) (6,3) (6,4) (6,5) (6,6) (6,7) (6,8) (6,9) 圖 11 3x3mask 示意圖

Image Data Horizontal Operation Unit Threshold T Delay 1 clock FIFO x 319 Delay 1 clock Delay 1 clock Assemble Data Compare Unit Threshold G Slant Right Operation Unit Vertical Operation Unit Slant Left Operation Unit Edge Image 圖 12 邊緣影像運算處理架構圖 (1,1) Horizontal (1,2) (1,3) (1,4) (1,5) (1,6) (1,7) (1,8) (1,9) (2,1) (2,2) (2,3) (2,4) (2,5) (2,6) (2,7) (2,8) (2,9) (3,1) (3,2) (3,3) (3,4) (3,5) (3,6) (3,7) (3,8) (3,9) (4,1) (4,2) (4,3) (4,4) (4,5) (4,6) (4,7) (4,8) (4,9) (5,1) (5,2) (5,3) (5,4) (5,5) (5,6) (5,7) (5,8) (5,9) (6,1) (6,2) (6,3) (6,4) (6,5) (6,6) (6,7) (6,8) (6,9) Slant Right Vertical Slant Left 圖 13 影像示意圖 2) 左斜運算處理單元 其設計關念如同水平運算處理單元,水平運算其為影像中左右資料則 Delay 1 clock, 而左斜運算為現刻影像資料與下列影像資料運算,如圖 13 所示,為 image(1,2)與 image(2,1) 運算,其 image(1,2)如需要與 image(2,1)運算時則必需 Delay 319 clock,因此設計一 FIFO 做為資料暫存,如圖 12 所示。

3) 垂直運算處理單元

如圖 13 所示,為 image(1,2)與 image(2,2)運算,其 image(1,2)如需要與 image(2,2)運算 時則必需 Delay 320 clock,因此在 FIFO 之後再加入 Delay 1 clock,如圖 12 所示。

4) 右斜運算處理單元

圖 13 所示,為 image(1,2)與 image(2,3)運算,其 image(1,2)如需要與 image(2,3)運算時 則必需 Delay 321 clock,因此在 FIFO 之後再加入 Delay 2 clock,如圖 12 所示。

Image Data:主要是由 SAA7111AHZ 所提供,序列資料輸入一奇偶圖場所需的時間大約為

1/60 秒

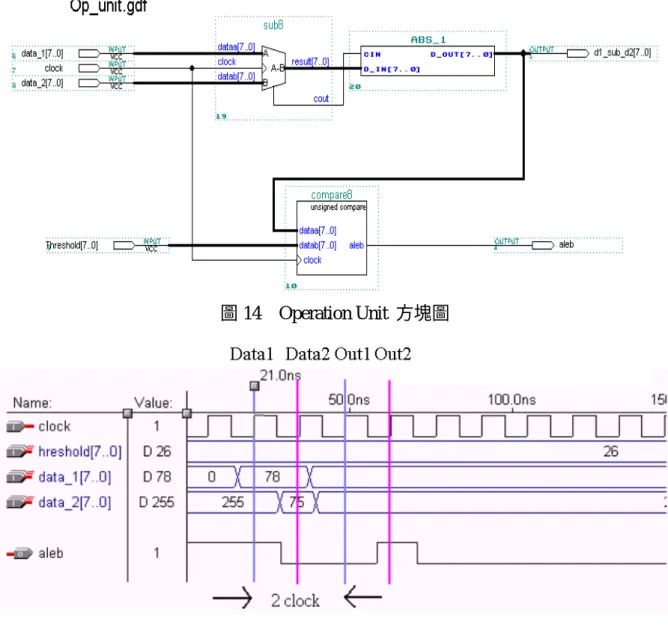

2.6.1 邊緣影像運算處理單元

運算單元主要組成如圖 14 所示,其功能主要將兩筆資料相減(sub8),再取絕對值運算 (ABS_1),最後再將其結果與 Threshold 做比較(compare8),大於時輸出’0’,小於時輸出’1’, 其波形如圖 14 所示。

由圖 15 運算單元輸出波形可看出,其運算結果輸入至輸出需要 2 clock 的時間,但不影 響資料的輸入,資料依然可 1clock 輸入一筆資料,並不造成資料量累積的問題。在整個 SUSAN 演算法,只需使用 4 個 Operation Unit ,也就是 8 個 8 位元減法器及 8 個 8 位元比較器。

FIFO:First In First Out 記憶元件,在電路常用來做為資料的緩衝器(Data Buffer)及事件的排

隊等用途。在此當做資料的緩衝器,其共有 2 個資料埠,一端資料寫入,另一端為資 料讀出。其指向暫存器的指標亦有 2 個,一個資料寫入指標,另一為資料讀出指標。 其運作方式如下圖 16 所示。所設計之 FIFO 512 8╳ ,其代表有 8 位元寬,FIFO 的深度 為 512。如果所使用的影像為 320 240╳ ,則其所需深度至少 319。

圖 14 Operation Unit 方塊圖 圖 15 Operation Unit 輸出波形 Read Pointer Write Pointer Write Data Write Data Write Pointer Read Data Write Pointer Read Data Read Pointer 圖 16 FIFO 電路操作示意圖

2.6.2 運算資料匯集單元 主要目的在匯集由運算單元所輸出的結果將其整理,其每一影像點共有,八個結果由運 算單元所輸出的結果如圖 17 所示,如此序列資料輸入,第一筆邊緣影像資訊將第二列第三行 資訊輸出之後獲得,其匯集資料流程圖如圖 18 所示。 以下將再分別說明(1)~(8)資料匯集的方式,圖 19 為匯集(1)∼(5)的資料,匯集的方式如 下所示,因(6)~(8)必須再下一個 row 時才可得到資料,因此利用 FIFO 的方式將資料暫存,等 (6)~(8)輸出結果再行輸出。其資料匯集波形如下圖 20 所示。 (6)~(8)必須輸出資料,再結合 FIFO 所輸出的資料,其資料匯集波形如下圖 10 所示。 (1,1) (1,2) (1,3) (1,4) (1,5) (2,1) (2,2) (2,3) (2,4) (2,5) (3,1) (3,2) (3,3) (3,4) (3,5) (4,1) (4,2) (4,3) (4,4) (4,5) (5,1) (5,2) (5,3) (5,4) (5,5) (1) (2) (3) (4) (5) (6) (7) (8) 圖 17 Operation Unit 所輸出的 8 個結果 Assemble Data Data (1)~(4) Delay 1 clock Assemble Data Data (1)~(5) FIFO x319 Assemble Data Data (1)~(6) Delay 1 clock Assemble Data Data (1)~(7) Delay 1 clock Assemble Data Data (1)~(8) Horizontal Slant Left Vertical Slant Right Data (1)~(4) Data (1)~(4) Data (5) Data (6) Data (7) Data

(1)~(5) (1)~(6)Data (1)~(6)Data (1)~(7)Data Data

(1)~(7)

Data (1)~(8) Data (8)

2.6.3 邊緣影像輸出單元 將 2.6.1~2.6.2 節中,所取得之結果匯整成完整的資料,並取一臨界值運算,求出影像邊 緣資料,圖 21 為所求得之邊緣影像資料,數值為 0 或 1。

2.7 PCI-Bus 介面設計

PCI-Bus 主要工作在於當作即時影像前處前處理卡與工業電腦端資訊的傳遞的介面,其 傳遞資訊包含了影像資訊、邊緣影像資訊、命令傳遞…等。因此在即時影像前處前處理卡必 圖 19 匯集(1)∼(5)資料波形圖 圖 20 匯集(6)∼(8)資料波形圖 圖 21 影像邊緣資料輸出波形圖需有一 PCI Target 介面控制做為與工業電腦端之 PCI Master 介面做傳輸溝通,主要將 PCI Target 分為二部份,一為 PCI Interface 與 PCI Host Interface。PCI Interface 主要工作在於與 PCI

Master 介面做傳輸溝通與資料解碼,透過 PCI 介面送入命令進行讀取影像控制、邊緣影像處 理控制、背景影像讀取控制、邊緣影像 Threshold 控制。

2.8 測試結果

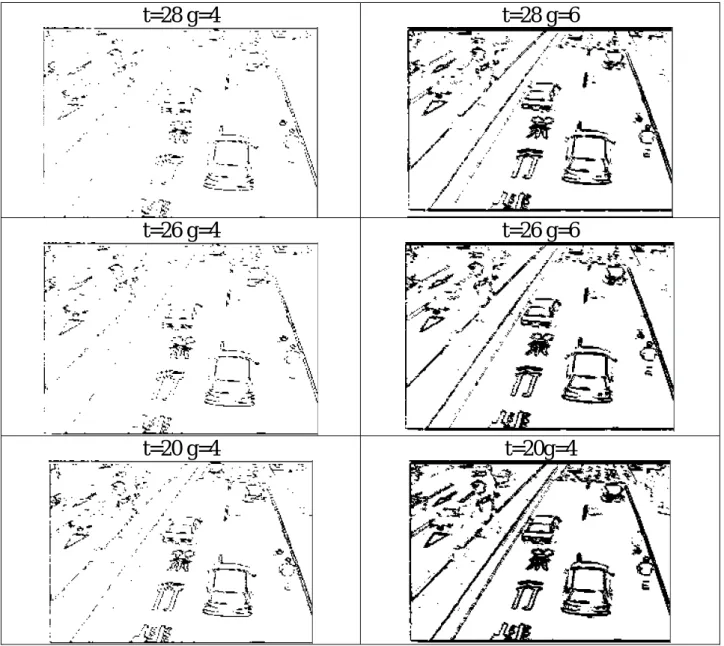

圖 22 與圖 23 分別為本計畫所研製之影像擷取卡實體圖與即時影像前置處理卡實體圖, 本裝置之邊緣影像處理,採用序列處理方式設計,可達成每秒處理 60 張圖場的目標,正確處 理時間計算如下所示: ms s 277 . 15 015277 . 0 324 13.5MHz 1 240 13.5MHz 1 ) 138 720 ( 324 13.5MHz 1 ) 240 ( 324 13.5MHz 1 = = × + × × + = × + × = × + = 水平同步時間 影像輸入時間 影像邊緣擷取時間 我們對所研發之影像擷取卡及 SUSAN Algorithm 邊緣處理性能進行測試分析。本影像處理卡內含 SAA7111AHZ 影像擷取晶片與 Altera Flex10K 200s CPLD,利用 VHDL 語言於 Altera Flex10K 200s 上實現 SUSAN Algorithm。我們透過 PCI 介面設定 SUSAN Algorithm 的

Intensity threshold 與 geometrical threshold,對不同之 Threshold 所取得之 SUSAN Algorithm 邊

緣處理結果如圖 24 所示。由圖 24 可知於相同之 Intensity threshold 設定值下,geometrical threshold 會影響到邊緣特徵點的數量,因此依據使用狀況,geometrical threshold 的設定值可

圖 23 影像前置處理卡

t=28 g=4

t=28 g=6

t=26 g=4

t=26 g=6

t=20 g=4

t=20g=4

三、 結論與未來工作

在本計劃第二年的執行期間已完成即時影像處理系統之設計、製作與測試。未來主要工 作方向將發展一套可自動調整 Intensity threshold 設定值之方法與整理 SUSAN 即時化處理所 需用到之資料匯流排與控制訊號匯流排,未來將進行較有系統之訊號流程規劃,以期完成 IP 化。使用者將依據不同的輸入影像品質,調整 threshold 以取得所需的邊或角的特徵點資訊。 並繼續發展以 CMOS 影像感測器整合訊號處理電路於單一晶片,偵測車輛四周物體之相對速 度,進而產生輔助駕駛的功效。 計畫成果自評: 目前計畫之執行已達到原設定之目標,完成一即時影像處理系統之設計 與製作,以 FPGA 執行 320x240 之影像,可達成每秒 60 個圖場邊緣萃取之速度,適合在影像 追蹤的應用。部分結果已投稿至國際研討會 IEEE ICRA2003,並被接受發表,較完整之影像 追蹤系統,將投稿於學術期刊發表。

參考文獻

[1] Masaki, I., “Machine-vision systems for intelligent transportation systems,” IEEE Intelligent Systems, pp.24-31,Vol.13, 1998.

[2] Ninomiya, Y.; Matsuda, S.; Ohta, M.; Harata, Y.; Suzuki, T.,“ A real-time vision for intelligent vehicles,” Proceedings of the Intelligent Vehicles '95 Symposium, pp .315-320, 1995.

[3] Martin, D.A.; Lee, H.S.; Masaki, I.A, “ Mixed –Signal Array Processor with Early Vision Application,” IEEE Journal of Solid-State Circuits, pp. 497-502, Vol.33, March 1998.

[4] Jamro,E.; Wiatr, K., “Convolution operation implemented in FPGA structures for real-time image processing,” Proceedings of the 2nd International Symposium on Image and Signal Processing and Analysis, pp.417-422, 2001.

[5] Box, B., “Field programmable gate array based reconfigurable preprocessor,” Proceedings of the IEEE National Aerospace and Electronics Conference, pp.427-434 Vol.1, 1994.

[6] Torres-Huitzil, C.; Arias-Estrada, M., “An FPGA architecture for high speed edge and corner detection,” Proceedings of Fifth IEEE International Workshop on Computer Architectures for Machine Perception, pp.112-116, 2000.

[7] “SAA7111A Enhanced Video Input Processor,” Philips Semiconductor, 1998. [8] “The CI2 -Bus Specification Version2.1,” Philips Semiconductor, January 2000.

![表 1 Sobel 及 SUSAN 演算法效能比較[6]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8521896.186573/6.892.83.758.156.1088/表1Sobel及SUSAN演算法效能比較6.webp)

![圖 2 影像擷取卡系統架圖 2.2 影像擷取模組 本計畫採用 Philips 公司之 SAA7111AHZ 影像視訊晶片進行影像擷取[7],其主要特點如 下: (1) 兩個類比視訊訊號輸入(NTSC or PAL)。 (2) 對於類比視訊訊輸入可設定為自動調整其增益。 (3) 兩個內建類比 anti-aliasing 濾波器。 (4) 自動偵測 50/60 Hz 圖場頻率且能 PAL 與 NTSC 標準之間自動切換。 (5) 可控制影像之亮度、對比與飽和度。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8521896.186573/7.892.187.707.108.594/本計畫公司之兩個類比視訊訊號輸入NTSC對於視訊濾波器頻率且能與.webp)