The Design of Outsourcing Planning for

Semiconductor Backend Turnkey Service

S. H. Chung

1*, I. P. Chung

1, Y. T. Tai

2, Y. M. Chu

1 1Department of Industrial Engineering and Management National Chiao Tung University, Hsinchu, Taiwan, ROC

2Department of Industrial Engineering and Management, Ta Hwa Institute of Technology, Hsinchu, Taiwan, ROC

E-mail: shchung@mail.nctu.edu.tw, ipchung.iem94g@nctu.edu.tw, ytdai@thit.edu.tw, pig.iem95g@nctu.edu.tw

*Corresponding author. Tel: 886-3-5731638; Fax. 886-3-5722392; e-mail: shchung@mail.nctu.edu.tw.

Abstract

Wafer fabrications provide the semiconductor backend turnkey service (SBTS) that help their customers to handle the outsourcing business of the three backend processing stages including circuit probing testing, integrated circuit assembly, and final testing. When the process of wafer fabrication is completed, the SBTS provider needs to select appropriate outsourcing firms and to allocate the semi-finished orders to them. In the process of selecting suitable outsourcing firms, the SBTS providers consider the constraints of limited capacity, production cost, due dates, and the processing capabilities of each outsourcing firm. The planning problem for SBTS is very complicated because of requirement variations of orders and capability variations of outsourcing firms. In this paper, a mixed integer programming model for SBTS with the total cost minimization criterion is presented. A case is also provided to demonstrate its applicability of the IP model in real practice.

Keywords—Semiconductor backend turnkey service (SBTS), outsourcing, wafer fabrication.

1. Introduction

With the increasing progress of technology, the product lifetime becomes shorter and shorter. This make product profits be reduced and customer due dates be tightened, particularly, in the semiconductor supply chain. To achieve the requirements of quick responses to customers and to shorten production cycle time, the integrated planning of the supply chain for semiconductor manufacturing is essential and critical.

The semiconductor backend turnkey service (SBTS) provided by wafer fabrications is a new production model which is used to achieve the integrated planning

of the supply chain. In SBTS, wafer fabrications coordinate production planning of the entire semiconductor supply chain, which involves wafer fabricating, circuit probing testing (C/P testing), integrated circuit (IC) assembly, and final testing, for IC design companies. The production planning of SBTS is to allocate customer orders to appropriate sites and to meet due dates under the environment of multi-stages processes and multi-outsourcing factories. With SBTS, IC customers can avoid much unnecessary following-up activities. Also, the SBTS planning can shorten the entire production cycle time and enhance the competitive edges for whole semiconductor supply chain.

In recent years, new research studies have appeared about the issue of SBTS. Chung et al. [1] developed an integer-programming model with considerations of a collaborative production-distribution planning under the environment with multi-products, multi-stages, and multi-capabilities outsourcing factories. They also provided a heuristic algorithm which modified the generalized saving algorithm proposed by Christofides et al. [2] so that the proposed algorithm can solve large-scale problems efficiently. Chiang et al. [3] adjusts the level of work in process (WIP) to enhance the performance of order fulfillment for the entire back-end semiconductor manufacturing. The model of WIP management provided by Chiang et al. includes three main sections: (1) using the method of analytic hierarchy process (AHP) to determine the weights of the following performance indices: average on-time delivery percentage, cycle time, throughput rate, and bottleneck utilization; (2) using the simulation approach and the experimental design to develop the model of acceptable WIP deviation level (AWDL) which sets upper acceptable WIP deviation level (UAWDL) and lower acceptable WIP deviation level (LAWDL); (3) providing a dispatch rule to ensure the achievement of AWDL. The main idea is to ensure that

the WIP level is between the UAWDL and LAWDL for each workstation. Such that can the bottleneck workstation can avoid starvation. The computational results showed that the AWDL model could improve the customer satisfaction effectively. Furthermore, Guo et al. [4] considered a multi-objectives exception management model for turkey service with considerations of hot lots and normal lots for semiconductor back-end environment. They improves the dispatching rule provided by Chiang et al. [3]. Guo et al. [4] demonstrated their model can help the WIP management and can enhance the performance of order fulfillment for the supply chain of semiconductor manufacturing.

Hsu and Su [5] presented the development of a collaborative production planning system with activity-based costing. As orders are released to production line at the earlier stage, the system can estimate and control profits of semiconductor backend turnkey operational services. Moreover, Chiu [6] presented a supply chain model based on theory of constraints (TOC) and critical chain project management (CCPM) for the semiconductor manufacturing. He used a real case and conducted an experimental design to demonstrate whether or not the proposed model performs better than adopting the rule of critical ratio (CR) with criteria of on time delivery and throughput. Li [7] proposed an exception management system for foundry fabricators with turnkey services so as to manage the production planning of outsourcing factories. She conducted a simulation model and showed that the proposed system is applicable to help the foundry fab to manage the outsourcing factories for backend semiconductor manufacturing.

However, in the SBTS, there are various types of service requested by IC design companies due to practical considerations. Orders placed by IC design companies are not always need to pass through all of the stages of the backend semiconductor manufacturing. To solve the order allocation problem in SBTS, we propose a mixed integer programming model for the SBTS considering capacity limitation and due date achievement. The paper is organized as follows. In Section 2, the description of SBTS problem is presented. The IP model is constructed in Section 3. For clarity, a case study is provided in Section 4 to illustrate how the IP model can be applied in the real world case. We also provide the solutions for the SBTS in Section 5. Finally, the conclusion and future research are included in Section 6.

2. SPTS problem

To avoid the business confidentiality giving away, some IC design companies want to assign some of backend processing stages by themselves to specific

partners. To confront such practical situations, the SBTS should provide more flexible service selections in order to satisfy specific requirements regarding outsourcing stages, process type, and quantities for each customer. These constraints make the planning of SBTS become more complicated than the classical production problems which ignore the considerations of these practical requests.

In this paper, there are four major limitations should be considered for allocating orders to backend outsourcing factories. First, the limitations of capacity should be considered for each product type in each factory. Second, process capabilities of each backend factory should are considered. The orders can be only allocated to the outsourcing factories with specific capability. Third, the outsourcing prices may be different for each backend factory because of the capability difference and the concerns of long-term contracts. Fourth, the ability for accepting multi-stage or single-stage outsourcing orders should be considered for each outsourced factory. Some outsourcing firms can handle multiple-stage orders due to their advanced technologies or large invested capital; the others may be only capable to handle single-stage orders. Notably, production cycle time can be reduced when one multiple-stage order is assigned to one outsourcing factory for processing two or more consecutive stages of operations. However, as the quality control, scheduling, and the transportation of WIP are taken by the outsourced factory, the total outsourcing cost is higher than those of two single-outsourced activities.

The semiconductor backend turnkey service (SBTS) problem faces the constraints related to limited capacity, process capabilities, and order due dates, and especially, various service requirements about the three backend processing stages. In this paper, there are two main costs regarding the production planning for SBTS problem. First, the outsourcing costs paid to the backend factories. Second, the backlog cost incurred when orders cannot be satisfied in time.

3. Mixed Integer Programming Model for

SPTS

A mixed integer programming (MIP) model is proposed to solve the SBTS problem. The objective of this MIP model is to minimize the total cost on the premise of satisfying the various requirements of orders under the constraints of backend foundry factories. To clearly present the SBTS problem, we first explain the following notations.

Superscripts:

0

j= represents the dummy product.

1,...,

j= e represents the product index for wafer

probing.

1,...,

j e= + e+ f represents the product index for

IC assembly. 1,...,

j e f= + + e f+ +g represents the product index for final testing.

k: route indicator, k∈

{

pr spa mpa ssft smft mmf, , , , ,}

, wherepr represents that the route reaches C/P testing

only..

spa represents that the route reaches IC assembly,

and the previous stage is processed by single-stage outsourcing.

mpa represents that the route reaches IC assembly,

and the previous stage is processed by multiple-stage outsourcing.

ssft represents that the route reaches final testing

stage, and the first and second stages are processed by single-stage outsourcing respectively.

smft represents that the route reaches final testing

stage, and the first stage is processed by single-stage outsourcing and the second single-stage is processed by multiple-stage outsourcing.

mmft represents that the current stage is final testing

stage, and the first and second stage are processed by multiple-stage outsourcing.

Subscripts:

i

: order index, i=1, ...,I .m : index of foundry factory, m=0,1,...,M ;

0

m= represents dummy factory that process

dummy product only.

t

: planning period, t=1,...,T. Decision variables: k j, t m iX,,: single-stage outsourcing quantity for product

j

of orderi

by adopting route k and releasedat period

t

to factory m, k j, t m iY, ,: multiple-stage outsourcing quantity for product

j

of orderi

by adopting routek

and releasedat period

t

to factorym

, k j, t m iOX,,: single-stage throughput for product

j

of orderi

by adopting route k and completed duringperiod

t

in factorym

, k j, t m iOY,,: multiple-stage throughput for product

j

oforder

i

by adopting route k and completedduring period

t

in factorym

,i

Z : an indicator show the requirement of order

i

isprocessed or not.

Because of the usage of dummy product and dummy factories, every order can be expressed as demanding three main process stages. Note that the dummy product is filled in when the corresponding process stage is not requested by an order. The decision variable and the route indicator show how

order

i

completes its process requirement throughfinal test stage, which are (1) processed in different factories for the each of the process stages

( , ', ",

, , , ', , ",

Xj pr,Xj spa,Xj ssft

i m t i m t i m t); (2) processed in one factory for

the C/P testing stage and processed in another factory for the IC assembly and final testing stages

( , ', ",

, , , ', , ",

Xj pr,Yj spa,Yj smft

i m t i m t i m t ); (3) processed in one factory for

the C/P testing and IC assembly stages and processed in another factory for the final testing

stage ( , ', ",

, , , , , ',

Yj pr,Yj spa,Yj mmft

i m t i m t i m t ); and (4) processed in the

same factory for the different process stages

( , ', ", , , , , , , Yj pr,Yj mpa,Yj mmft i m t i m t i m t ). Parameters: , j m t

a : Reserved capacity for for product

j

duringperiod

t

in factory m due to previousscheduling,

j m

x

c : cost of single-stage order for product

j

infactory m,

j m y

c : cost of multiple-stage order for product

j

infactory m ,

j m

x

ct : required cycle time for product

j

adoptingsingle-stage production in factory m ,

j m

y

ct : required cycle time for product

j

adoptingmultiple-stage production in factory m,

t, i

d : quantity for order

i

arrived at periodt

,i

due: due date of order

i

.e

: total number of product types at C/P testingstage,

f

: total number of product types at IC assemblystage,

g

: total number of product types at final testingstage,

j m

q : supplied capacity for product

j

in factory m,pe : the penalty cost incurred by an unsatisfied

orders,

j

pt : processing time for product

j

in factory m,i

r

p : product type of order

i

at wafer probing stage,{

}

ri 1,...,

p ∈ e ,

i a

p : product type of order

i

at IC package stage,{

1,...,}

i

pa ∈ +e e f+ ,

i

ft : product type of order

i

at final testing stage,{

}

The mathematical formulation of the SBTS problem is shown as follows.

Minimize I M T J j,k j I M T J j,k j ,m, m ,m, m 1 m 1 t 1 j 1 k KXi t x 1 m 1 t 1 j 1 k KYi t y i= = = = ∈ ×c +i= = = = ∈ ×c ∑ ∑ ∑ ∑ ∑ ∑ ∑ ∑ ∑ ∑ (1) I ,t 1(1-Z )i i i= d pe +∑ × × (2) Subject to j; ; t m; , a -q pt * ) Y (X j t m, j m I i k K j k j, t m, i, k j, t m, i, + ≤ ∀ ∀ ∀

∑∑

∈ (3) M T pr ,pr M T pr ,pr i ii,t i,m,t 1 i,m,t 1

m 0 1 m 0 t t 1 d * i X Y , i; ; t t Z + + t = = + = = + =∑ ∑ +∑ ∑ ∀ ∀ (4) ; t i; Y X OX M 0 m T t t spa , pa 1 t m, i, M 0 m T t t spa , pa 1 t m, i, M 0 m pr , pr t m, i,i =

∑ ∑

i +∑ ∑

i ∀ ∀∑

= =+ + = =+ + = , 1 1 (5) ; t m; i; Y OY T 1 t t mpa , pa 1 t m, i, pr pr, t m, i, =∑

i ∀ ∀ ∀ + = + , (6) ; t i; X OX M 0 m T t t ssft , ft t m, i, M 0 m spa , pa t m, i, i =∑ ∑

i ∀ ∀∑

= =+ = , 1 (7) ; t m; i; Y OY T t t smft , ft t m, i, spa , pa t m, i, i =∑

i ∀ ∀ ∀ + = , 1 (8) M T T pa ,mpai ft ,mmfti ft ,mmftii,m,t i,m,t 1 i,m,t 1

m 0 t t 1 t t 1 OY X + Y + , i; ;t = = + = + =∑ ∑ +∑ ∀ ∀ (9) K; k j; ; t m; i; , OX X j,k ctx t m, i, k j, t m, i, j m ∀ ∀ ∀ ∀ ∈ = + −1 (10) K; k j; ; t m; i; , OY Y j,k cty t m, i, k j, t m, i, j m ∀ ∀ ∀ ∀ ∈ = + −1 (11) j,k j,k i,m,t i,m,t (X +Y )<=M* Z , i; m; ; j;ki ∀ ∀ ∀ ∀t =pr; (12) T j,k j,k i,m,t i,m,t t due 1i (OX OY ) 0, i; m; j;k pr; =∑+ + = ∀ ∀ ∀ = (13) 0 Xj,k t m i, , ≥ , Yi,j,mk,t≥0 , OX 0 k j, t m i, , ≥ , OY 0 k j, t m i, , ≥ , i ∀ ,∀m,∀t,∀j,∀k (14) Zi∈{0,1}

,

∀i (15)The objective function seeks to minimize the sum of total production cost and penalty cost of unsatisfied orders. The constraints in (3) guarantee that the total load of orders assigned to the outsourcing factory must be equal to or less than the

capacity offered in factory m. The constraints in (4)

to (9) are related to demand satisfaction. The

constraint (4) guarantees that the demand of order

i

assigned to the C/P testing stage must be equal to the amounts of single-stage and multiple-stages outsourcing. The constraints in (5) and (6) state that

the amount of order

i

completed at the C/P testingstage must transfer to IC assembly stage. The constraint in (5) guarantees that the output related to

order

i

from the single C/P testing stage must equalto the amounts transferred to assembly stage by single-stage or multiple-stages outsourcing. The

constraint (6) states that the orders

i

adoptingmultiple-stages outsourcing in C/P testing stage

must stay in the same factory for the IC assembly stage outsourcing. The constraints in (7) to (9) are related to amount transferred to final testing stage. The constraint (7) guarantees that the output

produced for order

i

through single-stageproduction in IC assembly stage must equal to the amount that adopting single-stage production in final testing stage. The constraint (8) states that

order

i

adopting multi-stage production from ICassembly stage must keep multi-stage outsourcing decision in final testing stage. The constraint (9)

states that the order

i

completed the multi-stageoutsourcing from C/P testing to IC assembly stages can have its final stage outsourcing assigned to another single-stage factory or keep the multi-stage production in factory m. The constraints (10) and (11) are time transition equations, which states that the output time an order equals to its release time plus the cycle time. The constraint (12) checks whether an order is released or not. The constraint (13) requests that an order released must be completed before its due date. The constraints in

(14) request the value of j,k

t m i X,,, k j, t m i Y, ,, OXij,,mk,t and k j, t m i OY, , be a non-negative integer. The constraint (15) limits

the decision variableZ to be either zero or one. i

Formulation complexity: the computational

complexity of the mixed integer programming model is described as follows. The integer programming model

contains 6

×

I×

M×

T×

J variables of j,k t m i X, , , j,k t m i Y, , , k j, t m iOX,, and OYi,j,mk,t, respectively. The constraints set in

(3) contain M

×

T×

J equations, the constraints set in(4), (5), (7) and (9) contain I

×

T equations, theconstraints set in (6) and (8) contain I

×

M×

Tequations, the constraints set in (10) and (11) contain

6

×

I×

M×

T×

J equations, , the constraints set in (12)contain I

×

M×

T×

J equations, , the constraints set in(13) contain I

×

M×

J equations. Thus, the total numberof variables is 24

×

I×

M×

T×

J, and the total numberof equations is T(M

×

J+4I+2I×

M+13×

I×

M×

J)+6I

×

M×

J.4. Case study

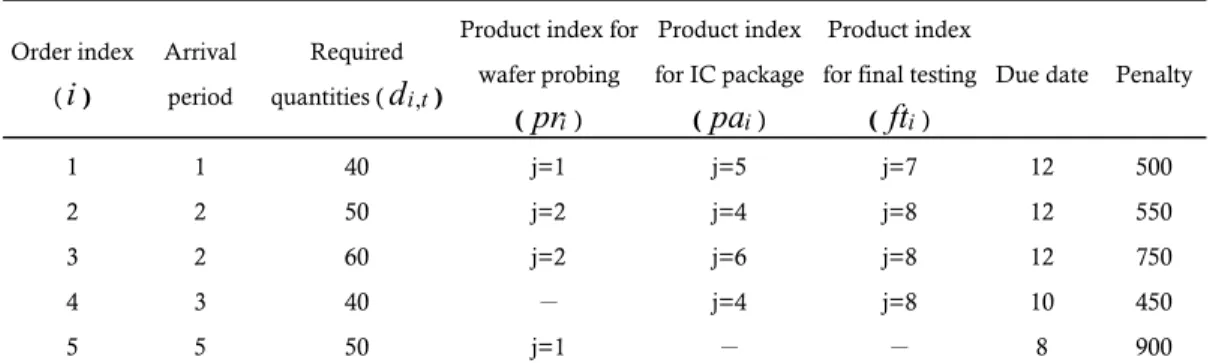

To demonstrate the applicability of the proposed mathematical model for the semiconductor backend turnkey service (SBTS) problem, a practical case from the semiconductor supply chain is taken. There are five backend outsourcing factories collaborated with the wafer fabrication to do SBTS. As the wafer fabrication is responsible to allocate to orders capacities for SBTS, the order information including arrival period, demanded quantities, requested process stages and product types are presented in Table 1. Furthermore,

the information regarding the production capability and

available capacity for backend factories are presented in Table 2. Table 3 and Table 4 show the unit outsourcing cost and production cycle time under single-stage or multiple-stage outsourcing contract.

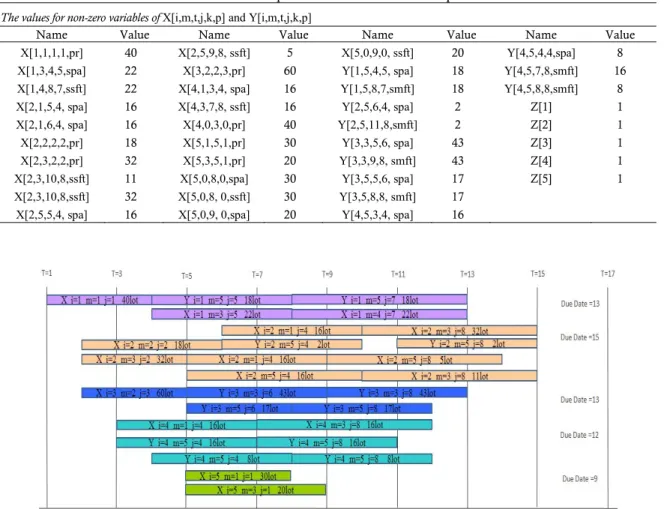

5. Solutions for the SPTS problem

To solve the mixed integer programming model, the software ILOG CPLEX is adopted to solve the problem. For the case with five backend factories described in Section 4, the MIP model contains 351,005 variables and 209,500 constraints. Table 5 states that computational time for the MIP model run on a Pentium 4.3 G Hz PC with 1.00 GB memory is 53.99 seconds. The production cost is 18,694 dollars. Table 6 presents the optimal solution obtained from the mathematical model. Figure 1 is depicted the optimal solution via a Gantt chart.

6. Conclusions

In this paper, the collaborative production planning problem for semiconductor backend turnkey service (SBTS) is studied. The SBTS can help customers to handle the outsourcing business of the three backend processing stages efficiently and to enhance the competitive edges of the semiconductor supply chain. A mixed linear programming model is provided to solve the planning problem of SBTS. The MIP model not only tries to minimize the total outsourcing cost in Table 1. The information of order demand

Order index (

i

) Arrival period Required quantities (d

i t, )Product index for wafer probing (

pr

i) Product index for IC package (pa

i) Product index for final testing(

ft

i)Due date Penalty

1 1 40 j=1 j=5 j=7 12 500

2 2 50 j=2 j=4 j=8 12 550

3 2 60 j=2 j=6 j=8 12 750

4 3 40 - j=4 j=8 10 450

5 5 50 j=1 - - 8 900

Table 2. Available capacity and processing time for processing each product type.

Product type 1 2 3 4 5 6 7 8 9 factory 1 1440 720 720 720 1440 0 - - - 2 0 1440 2880 - - - - - - 3 720 1440 0 0 720 1440 0 1440 1440 4 - - - - - - 720 1440 1440 5 - - - 720 1440 1440 1440 1440 0 Proc. time 35 33 38 45 30 30 32 33 36

Table 3. Unit outsourcing cost for single-stage (multi-stage) order in each factory.

Product type 1 2 3 4 5 6 7 8 9 factory 1 (40) 35 (35) 30 (45) 40 (31) 26 (37) 32 - - - - 2 - 28 30 - - - - - - 3 (39) 34 (35) 30 - - (30) 25 (36) 31 - (32) 27 (42) 37 4 - - - - - - 26 34 34 5 - - - (43) 38 (43) 38 (38) 33 (34) 29 (35) 30 -

Table 4. Cycle time for single-stage (multi-stage) order in each factory Product type 1 2 3 4 5 6 7 8 9 factory 1 3(2) 3(2) 4(3) 4(3) 5(4) - - - - 2 - 4 3 - - - - - - 3 4(3) 3(2) - - 4(3) 5(4) - 5(4) 6(5) 4 - - - - - - 5 6 5 5 - - - 5(4) 5(4) 4(3) 6(5) 5(4) -

Table 5. Integer programming optimal solution for the SBTS case.

The objective value and the solution time

objective value 18694 Solving Time 53.99 (second)

Constraints 209500 Variables 351005

order to achieve the maximal profit, but also considers the due date satisfaction in chain to ensure service levels. However, when meeting problem with large-scale size, the model may not able to solve them within an acceptable run time. To reduce the computational time and to save the computational memory, the development of a heuristic algorithm is an essential further concern.

References

[1] S. H. Chung, I. P. Chung, and A. H. I. Lee, “Collaborative Production-Distribution Planning for Semiconductor Production Turnkey Service,” Lecture

Notes in Computer Science, 4705, pp. 860- 870, 2007.

[2] N. Christofides, A. Mingozzi, P. Toth, and C. Sandi.

Combinatorial Optimization. John Wiley & Sons: New

York, 1979.

[3] D. M. Chiang, R. S. Guo, and F. Y. Pai, “Improved customer satisfaction with a hybrid dispatching rule in semiconductor back-end factories, " International

Journal of Production Research, pp. 1- 21, 2007.

[4] R. S. Guo, D. M. Chiang, and F. Y. Pai, “Multi-objectives exception management model for semiconductor back-end environment under turnkey service," Production

Planning & Control, 18(3), pp. 203- 216, 2007.

[5] H. P. Hsu and C. T. Su, “The implementation of an activity-based costing collaborative planning system for semiconductor backend production,” International

Journal of Production Research, 43(12), pp. 2473- 2492,

2005.

[6] S. K. Chiu, “A Study of Critical Chain Project Management (CCPM) on Semiconductor Turnkey Services,” thesis, Department of Industrial Engineering and Management in National Chiao Tung University, Taiwan, 2002.

[7] Y. C. Li, “The Construction of Exception Management System for Semiconductor Supply Chain Turn Key Services,” thesis, Department of Industrial Engineering and Management in National Chiao Tung University, Taiwan, 2002.

Figure 1. The optimal solution for the example case.

Table 6. The optimal solution for the example

The values for non-zero variables of X[i,m,t,j,k,p] and Y[i,m,t,j,k,p]

Name Value Name Value Name Value Name Value X[1,1,1,1,pr] 40 X[2,5,9,8, ssft] 5 X[5,0,9,0, ssft] 20 Y[4,5,4,4,spa] 8

X[1,3,4,5,spa] 22 X[3,2,2,3,pr] 60 Y[1,5,4,5, spa] 18 Y[4,5,7,8,smft] 16 X[1,4,8,7,ssft] 22 X[4,1,3,4, spa] 16 Y[1,5,8,7,smft] 18 Y[4,5,8,8,smft] 8

X[2,1,5,4, spa] 16 X[4,3,7,8, ssft] 16 Y[2,5,6,4, spa] 2 Z[1] 1 X[2,1,6,4, spa] 16 X[4,0,3,0,pr] 40 Y[2,5,11,8,smft] 2 Z[2] 1 X[2,2,2,2,pr] 18 X[5,1,5,1,pr] 30 Y[3,3,5,6, spa] 43 Z[3] 1 X[2,3,2,2,pr] 32 X[5,3,5,1,pr] 20 Y[3,3,9,8, smft] 43 Z[4] 1 X[2,3,10,8,ssft] 11 X[5,0,8,0,spa] 30 Y[3,5,5,6, spa] 17 Z[5] 1 X[2,3,10,8,ssft] 32 X[5,0,8, 0,ssft] 30 Y[3,5,8,8, smft] 17