具應變技術之90奈米SOI互補式金氧半場效電晶體特性分析與可靠度研究

全文

(2)

(3) 具應變技術之90奈米SOI互補式金氧半場效電晶體 特性分析與可靠度研究. 指導教授:葉文冠 博士 (教授) 國立高雄大學電機工程研究所. 學生:王振安 國立高雄大學電機工程研究所 摘要. 應 變 矽 已 常 被 用 來 提 升 N型 和 P型 金 氧 半 場 效 電 晶 體 驅 動 電 流 的 方 法 之 一 , 尤 其 是 在 90奈 米 技 術 以 下 的 製 程 。 本 篇 論 文 中 , 我 們 運 用 了 幾 項 新 穎 與 低 成 本 技 術 來 同 時 提 升 N、PMOSFET 的 特 性,包 含 SOI、FUSI、 CESL 等 方 法 。 我 們 探 討 了 接 觸 蝕 刻 截 止 層 對 金 氧 半 場 效 電 晶 體 電 性 的 影 響 , 發 現 不 同 CESL 製 程 對 元 件 特 性 有 明 顯 的 影 響 , 包 含 載 子 的 遷 移 率,驅 動 電 流 及 閘 極 漏 電 流 等 特 性。另 外,由 於 較 高 的 應 力 可 能 在 元 件 的 通 道 及 氧 化 層 界 面 造 成 缺 陷,因 此,我 們 進 一 步 的 探 討 具 應 變 元 件 的 可 靠 度 ( R e l i a bi l i t y) , 發 現 NMOSFE T 在 高 伸 張 應 力 CESL 具 有 較 差 的 熱 載 子 退 化 機 制 , 而 PMOSFE T在 高 壓 縮 應 力 CE SL有 較 好 的 負 偏 壓 不 穩 定 性,我們也提出相關的影響機制。. 關鍵字:應變矽、接觸蝕刻截止層、絕緣層上矽、全金屬矽化物. I.

(4) The Investigation of Characteristic and Reliability for 90nm SOI CMOSFETs with Strain Technology. Advisor : Dr. Wen-Kuan Yeh (Professor) Institute of Electrical Engineering National University of Kaohsiung. Student: Chen-An Wang Institute of Electrical Engineering National University of Kaohsiung. ABSTRACT. In this thesis, we investigate the impact of the strain technology on Characteristic and Reliability for 90nm SOI CMOSFET with Strain Technology. For nMOSFET, device driving capability can be improved by tensile CESL especially with thicker thickness. But higher interface and oxide defects were also induced by CESL, resulting in device degradation; thus, the thickness of the CESL must be optimized to enhance device performance without inducing defect. For reliability inspection, more serious hot-carrier-induced devices degradation happen on thicker CESL device due to higher impact ionization rate. However, we found that less serious PBI happened on nMOSFET with thicker CESL, which due presumably to suppression of oxide defect by CESL. For pMOSFET, in comparison with tensile CESL device, we found that compressive CESL device possess higher device driving capability. But higher CESL induced interface and oxide defects were found high compressive pMOSFET using low frequency analysis. In comparison with tensile CESL device, less serious NBI was found on pMOSFET, which due presumably to suppression of oxide defect by CESL.. Keywords: Strained-Si , CESL , SOI , FUSI. II.

(5) 誌謝. 感謝二年來一直帶領我的指導教授葉文冠博士,在他細心的教導 下,讓我學習到做研究的方法以及待人處世的道理,並提供給我一個 自己發揮的環境,在遇到瓶頸時,能適時的指點我方向,使得問題能 得以解決。 在此更要感謝中山大學李杰穎博士,謝謝老師近一年多來的指導 與愛護,在我研究過程之中,協助我面對問題、解決問題,並提供許 多良好的建議,更從老師身上學習到不同作研究的風格,以及謹慎的 態度和實事求是的精神,著實讓我受益良多。 其次感謝已經工作的賴建銘學長和徐韶華學姐以及剛考上成功大 學博士班的許家維學長,在我剛進實驗室時,因為有你們耐心的訓練 我使用實驗室的儀器,並教導我許多該注意的事項及基礎理論,讓我 能在實驗室更快速的上手。另外,還要感謝清華大學陳育廷學長,因 為有你的幫忙與教導,使得我在國家奈米實驗室的量測能如此順利, 並從你身上學到許多量測技巧。當然也感謝持續兩年互相加油打氣的 產碩班同年級學生炫銘及政宏,還有帶來歡笑聲不斷的學弟群啟彰、 玄德、育哲及大四的學弟俊宇的幫忙。使我在高大作實驗的日子都能 很開心。 最後感謝我的爸、媽,讓我能在無後顧之憂的情況下完成學業。 您們真的很偉大。也感謝我的姐姐,在我感到挫折時能給予我鼓勵。 感謝時常支持我給我打氣的朋友們宏俊、寶清、國明、元仔、及哲偉。 並感謝所有曾經幫過我的人。. III.

(6) 目錄 中文摘要-----------------------------------------------------------------------------------------------I 英文摘要-----------------------------------------------------------------------------------------------II 誌謝-----------------------------------------------------------------------------------------------------III 目錄-----------------------------------------------------------------------------------------------------IV 表目錄--------------------------------------------------------------------------------------------------VI 圖目錄--------------------------------------------------------------------------------------------------VI 第一章 緒論-----------------------------------------------------------------------------------------01 1.1 研究背景與動機-------------------------------------------------------------------------01 1.2. 有關應變技術之研究-------------------------------------------------------------------04. 1.3. 論文架構---------------------------------------------------------------------------------06. 第二章 基本電性量測結果分析------------------------------------------------------------------07 2.1. 先進元件製程---------------------------------------------------------------------------07 2.1.1 絕緣層上矽(SOI)------------------------------------------------------------------07 2.1.2 金屬閘極(Metal-Gate)--------------------------------------------------------08 2.1.3 接觸蝕刻停止層(CESL)--------------------------------------------------------09. 2.2. 基本元件電性量測設計------------------------------------------------------------10 2.2.1 電容-電壓特性分析(C-V)-----------------------------------------------------10 2.2.2 ID-VD 特性曲線------------------------------------------------------------------10 2.2.3. 2.3. ID-VG 特性曲線-------------------------------------------------------------------11. C-V 量測結果與分析-------------------------------------------------------------------11. 2.4 I-V 量測結果與分析-------------------------------------------------------------------13 第三章. 氧化層品質量測結果與分析-------------------------------------------------------15. 3.1 低頻雜訊(Low quency Noise)-------------------------------------------------------15 3.1.1 Thermal noise---------------------------------------------------------------------15 3.1.2 Shot noise--------------------------------------------------------------------------16. IV.

(7) 3.1.3 Avalanche noise--------------------------------------------------------------------16 3.1.4 G-R noise----------------------------------------------------------------------------16 3.1.5 Flicker noise-------------------------------------------------------------------------17 3.2. Flicker Noise量測結果分析-----------------------------------------------------------18 3.2.1 實驗量測方式----------------------------------------------------------------------18 3.2.2 實驗結果----------------------------------------------------------------------------19. 3.3. Charge Pumping-------------------------------------------------------------------------20 3.3.1 Charge Pumping 基本原理-------------------------------------------------------20 3.3.2 Charge Pumping 量測方式-------------------------------------------------------21 3.3.3 實驗結果-----------------------------------------------------------------------------22. 第四章. 元件可靠度量測結果與分析---------------------------------------------------------23. 4.1. 元件退化機制---------------------------------------------------------------------------23. 4.2. 可靠度實驗設計------------------------------------------------------------------------24. 4.3. 實驗結果分析---------------------------------------------------------------------------25. 第五章. 4.3.1. Hot-Carrier-Stressing實驗結果------------------------------------------------25. 4.3.2. PBI/NBI實驗結果---------------------------------------------------------------27. 結論與未來展望-----------------------------------------------------------------------30. 5.1 結論---------------------------------------------------------------------------------------30 5.2 未來展望-----------------------------------------------------------------------------------32 參考文獻----------------------------------------------------------------------------------------------81 附錄一. 投過的論文文章(IEDMS)--------------------------------------------------------------90. 附錄二. 投過的論文文章(EDSSC)--------------------------------------------------------------94. V.

(8) 表目錄 表2-1. 元件分類表-------------------------------------------------------------------------------------34. 表2-2. 單軸應變在增加伸張應力或減少壓縮應力下,載子遷移率的變化情形----------47. 表2-3 雙軸與單軸伸張與壓縮應變對N、PMOS之驅動電流影響-------------------------------47. 圖目錄 第二章. 基本電性量測結果. 圖2-1-1 SOI wafer smart-cut製程流程圖-------------------------------------------------------33 圖2-1-2 元件製程流程圖-----------------------------------------------------------------------------33 圖2-1-3 元件結構圖-----------------------------------------------------------------------------------34 圖2-2-1 Probe Station Configuration--------------------------------------------------------------35 圖2-2-2 HP-4156B 半導體參數分析儀------------------------------------------------------------35 圖2-2-3 HP-4284A LCR阻抗分析儀---------------------------------------------------------------36 圖2-2-4 HP-5250A 低漏電流交換器--------------------------------------------------------------36 圖2-2-5 Agilent ICS Software-----------------------------------------------------------------------37 圖2-2-6 ID-VD 特性曲線-----------------------------------------------------------------------37 圖2-2-7 ID-VG and GM-VG 特性曲線----------------------------------------------------38 圖2-3-1 W/L=10μm/10μm. NMOSFET固定SOI厚度在500A下改變不同CESL條件的電. 容對電壓特性比較圖 ---------------------------------------------------------------------39 圖2-3-2 W/L=10μm/10μm. NMOSFET固定SOI厚度在700A下改變不同CESL條件的電. 容對電壓特性比較圖 ---------------------------------------------------------------------39 圖2-3-3 W/L=10μm/10μm. NMOSFET固定SOI厚度在900A下改變不同CESL條件的電. 容對電壓特性比較圖 ---------------------------------------------------------------------40 圖2-3-4 W/L=10μm/10μm. NMOSFET固定CESL條件在Low Tensile 380A下改變不同. SOI厚度的電容對電壓特性比較圖 --------------------------------------------------------40. VI.

(9) 圖2-3-5 W/L=10μm/10μm. NMOSFET固定CESL條件在High Tensile 700A下改變不同. SOI厚度的電容對電壓特性比較圖 -------------------------------------------------------41 圖2-3-6 W/L=10μm/10μm NMOSFET固定CESL條件在High Compressive 700A下改變 不同SOI厚度的電容對電壓特性比較圖 ----------------------------------------------41 圖2-3-7 W/L=10μm/10μm. PMOSFET固定SOI厚度在500A下改變不同CESL條件的電. 容對電壓特性比較圖 ------------------------------------------------------------------------42 圖2-3-8 W/L=10μm/10μm. PMOSFET固定SOI厚度在700A下改變不同CESL條件的電. 容對電壓特性比較圖 ------------------------------------------------------------------------42 圖2-3-9 W/L=10μm/10μm. PMOSFET固定SOI厚度在900A下改變不同CESL條件的電. 容對電壓特性比較圖 ------------------------------------------------------------------------43 圖2-3-10 W/L=10μm/10μm PMOSFET固定CESL條件在Low Tensile 380A下改變不同 SOI厚度的電容對電壓特性比較圖 -----------------------------------------------------43 圖2-3-11 W/L=10μm/10μm PMOSFET固定CESL條件在High Tensile 700A下改變不同 SOI厚度的電容對電壓特性比較圖 -----------------------------------------------------44 圖2-3-12 W/L=10μm/10μm PMOSFET固定CESL條件在High Compressive 700A下改變 不同SOI厚度的電容對電壓特性比較圖 -----------------------------------------------44 圖2-3-13 NMOS在不同應變層元件之遷移率對有效電場特性比較圖-----------------45 圖2-3-14 PMOS在不同應變層元件之遷移率對有效電場特性比較圖-----------------4 5 圖2-3-15 NMOS在不同應變層元件之臨限電壓下滑特性比較圖---------------------46 圖2-3-16 PMOS在不同應變層元件之臨限電壓下滑特性比較圖-----------------------46 圖2-4-1 製程引起之strain應力方向示意圖-------------------------------------------------47 圖2-4-2. NMOS在不同應變層元件之ID-VD比較圖-------------------------------------48. 圖2-4-3. NMOS在不同應變層元件之Gm-VG比較圖------------------------------------48. 圖2-4-4. NMOS在不同應變層元件之ID-VG比較圖-------------------------------------49. 圖2-4-5. NMOS在不同應變層元件之IG-VG比較圖-------------------------------------49. 圖2-4-6. PMOS在不同應變層元件之ID-VD比較圖--------------------------------------50. 圖2-4-7. PMOS在不同應變層元件之Gm-VG比較圖-------------------------------------50. 圖2-4-8. PMOS在不同應變層元件之ID-VG比較圖--------------------------------------51. VII.

(10) 圖2-4-9. PMOS在不同應變層元件之IG-VG比較圖--------------------------------------51. 圖2-4-10 NMOS在不同應變層元件之ID-VD比較圖--------------------------------------52 圖2-4-11 NMOS在不同應變層元件之Gm-VG比較圖-------------------------------------52 圖2-4-12 PMOS在不同應變層元件之ID-VD比較圖--------------------------------------53 圖2-4-13 PMOS在不同應變層元件之Gm-VG比較圖-------------------------------------53 圖2-4-14 NMOS在不同應變層元件之ID-VD比較圖---------------------------------------54 圖2-4-15 NMOS在不同應變層元件之Gm-VG比較圖-------------------------------------54 圖2-4-16 PMOS在不同應變層元件之ID-VD比較圖---------------------------------------55 圖2-4-17 PMOS在不同應變層元件之Gm-VG比較圖-----------------------------------55 圖2-4-18 NMOS在不同應變層元件之Ion-Ioff比較圖-----------------------------------56 圖2-4-19 PMOS在不同應變層元件之Ion-Ioff比較圖-----------------------------------56 圖2-4-20 NMOS在不同應變層元件之Ion-Ioff比較圖-----------------------------------57 圖2-4-21 PMOS在不同應變層元件之Ion-Ioff比較圖-----------------------------------57. 第三章. 圖3-1-1. 氧化層品質量測結果與分析. Energy band-diagram of a MOSFET----------------------------------------------------58. 圖3-2-1 比較NMOSFET在線性區時高應力伸張CESL層與低應力伸張CESL層對元件缺 陷造成之影響-------------------------------------------------------------------------------------------59 圖3-2-2 比較PMOSFET在線性區時高應力壓縮CESL層與低應力伸張CESL層對元件缺 陷造成之影響-------------------------------------------------------------------------------------------59 圖3-2-3 比較NMOSFET在飽和區時高應力伸張CESL層與低應力伸張CESL層對元件缺 陷造成之影響-------------------------------------------------------------------------------------------60 圖3-2-4 比較PMOSFET在飽和區時高應力壓縮CESL層與低應力伸張CESL層對元件缺 陷造成之影響-------------------------------------------------------------------------------------------60 圖3-3-1 Charge Pumping 概念示意圖------------------------------------------------------------61 圖3-3-2 Charge Pumping 硬體架構圖-------------------------------------------------------------61 圖3-4-1 比較NMOS元件在不同應力下之ICP電流----------------------------------------------62 圖3-4-2 比較NMOS元件在不同應力下經由ICP電流換算之界面缺陷Nit------------------62 VIII.

(11) 第四章. 元件可靠度量測結果與分析. 圖4-2-1 電壓逼迫實驗設計流程圖----------------------------------------------------------------63 圖4-2-2 P-/NBI電壓逼迫實驗設計流程圖--------------------------------------------------------64 圖4-2-3 HC電壓逼迫實驗設計流程圖-------------------------------------------------------------64 圖4-3-1-1 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對汲極電壓關係圖----------------------------------------------------------------------------------65 圖4-3-1-2 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的互導對 閘極電壓關係圖----------------------------------------------------------------------------------------65 圖4-3-1-3 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對閘極電壓關係圖----------------------------------------------------------------------------------66 圖4-3-1-4 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的閘極電 流對閘極電壓關係圖----------------------------------------------------------------------------------66 圖4-3-1-5 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的基板電流對閘 極電壓關係圖-------------------------------------------------------------------------------------------67 圖4-3-1-6 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的汲極電流退化 量百分比對Stress Time的關係圖--------------------------------------------------------------------67 圖4-3-1-7 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的轉移電導退化 量百分比對Stress Time的關係圖--------------------------------------------------------------------68 圖4-3-1-8 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的臨限電壓變化 量百分比對Stress Time的關係圖--------------------------------------------------------------------68 圖4-3-1-9 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的閘極電流增加 量百分比對Stress Time的關係圖--------------------------------------------------------------------69 圖4-3-1-10 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對汲極電壓關係圖----------------------------------------------------------------------------------69 圖4-3-1-11 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的互導對 閘極電壓關係圖----------------------------------------------------------------------------------------70 圖4-3-1-12 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對閘極電壓關係圖----------------------------------------------------------------------------------70. IX.

(12) 圖4-3-1-13 室溫下90nm BC-SOI PMOSFET不同應力CESL加電壓前後的基板電流對閘 極電壓關係圖-------------------------------------------------------------------------------------------71 圖4-3-1-14 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的閘極電 流對閘極電壓關係圖----------------------------------------------------------------------------------71 圖4-3-2-1 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對閘極電壓關係圖----------------------------------------------------------------------------------72 圖4-3-2-2 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對汲極電壓關係圖----------------------------------------------------------------------------------72 圖4-3-2-3 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的轉移電 導對閘極電壓關係圖----------------------------------------------------------------------------------73 圖4-3-2-4 Schematic band diagram and subband splitting diagrams for direct carrier tunneling process in n-channel MOSFETs-------------------73 圖4-3-2-5 Schematic band diagram and subband splitting diagrams for direct carrier tunneling process in p-channel MOSFETs----------------------------------74 圖4-3-2-6 室溫下90nm BC-SOI NMOSFET不同應力CESL stress 100分鐘前後的閘極電 流對閘極電壓關係圖----------------------------------------------------------------------------------74 圖4-3-2-7 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的臨限電壓變化 量百分比對Stress Time的關係圖--------------------------------------------------------------------75 圖4-3-2-8室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的汲極電流退化量 百分比對Stress Time的關係圖-----------------------------------------------------------------------75 圖4-3-2-9 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的轉移電導退化 量百分比對Stress Time的關係圖--------------------------------------------------------------------76 圖4-3-2-10 室溫下90nm BC-SOI NMOSFET不同應力CESL加電壓前後的閘極電流增加 量百分比對Stress Time的關係圖--------------------------------------------------------------------76 圖4-3-2-11 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對閘極電壓關係圖----------------------------------------------------------------------------------77 圖4-3-2-12 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的汲極電 流對汲極電壓關係圖----------------------------------------------------------------------------------77. X.

(13) 圖4-3-2-13 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的轉移電 導對閘極電壓關係圖----------------------------------------------------------------------------------78 圖4-3-2-14 室溫下90nm BC-SOI PMOSFET不同應力CESL stress 100分鐘前後的閘極電 流對閘極電壓關係圖----------------------------------------------------------------------------------78 圖4-3-2-15 室溫下90nm BC-SOI PMOSFET不同應力CESL加電壓前後的臨限電壓變化 量百分比對Stress Time的關係圖--------------------------------------------------------------------79 圖4-3-2-16 室溫下90nm BC-SOI PMOSFET不同應力CESL加電壓前後的汲極電流退化 量百分比對Stress Time的關係圖--------------------------------------------------------------------79 圖4-3-2-17 室溫下90nm BC-SOI PMOSFET不同應力CESL加電壓前後的閘極電流增加 量百分比對Stress Time的關係圖--------------------------------------------------------------------80 圖4-3-2-18 室溫下90nm BC-SOI PMOSFET不同應力CESL加電壓前後的轉移電導退化 量百分比對Stress Time的關係圖--------------------------------------------------------------------80. XI.

(14) 第一章 緒論. 1.1 研究背景與動機. 世界上的第一顆電晶體發明至今已經長達了數十年之久,而發展電 晶體的主要目的乃是在於取代體積龐大的真空管,由於積體電路的想法 被提出及實現,使得積體電路產業開始蓬勃發展。目前每個世代的半導 體 元 件 都 是 根 據 有 名 的 摩 爾 定 律 (Moore’ s Law) 進 行 微 縮 (scaling) 。 在 1 9 6 5 年 時 , Gordon Moore 預 測 晶 片 (chip) 上 的 電 晶 體 數 目 將 隨 著 時 間 以 指 數 的 方 式 增 加 , 而 電 晶 體 的 尺 寸 (size) 亦 將 隨 著 時 間 以 指 數 的 方 式 縮 減 。 M o o r e 並 指 出 , 隨 著 電 晶 體 密 度 (density) 以 指 數 的 方 式 增 加 , 將 使 得製造成本得以降低。在過去的幾十年來,摩爾定律也一直被視為半導 體 工 業 製 程 技 術 的 藍 圖 (roadmap) 【 1 】 。 現 今 的 半 導 體 製 程 仍 是 以 發 展 時 間 較 久 而 且 技 術 也 較 為 成 熟 的 矽 基 (Silicon-base) 為 主 , 工 業 界 為 求 減少製造成本,除了不斷的增大晶圓的面積以外,並且微縮電晶體單位 尺 寸 , 以 求 能 在 相 同 晶 圓 面 積 下 有 較 高 的 積 體 電 路 密 度 (IC) 。 目 前 晶 圓 尺 寸 從 早 先 的 2 吋 發 展 至 今 日 的 1 2 吋 , 而 元 件 尺 寸 亦 從 1965 年 的 100 微 米 ( μ m )逐 漸 微 縮 至 今 日 ( 2 0 0 7 ) 的 4 5 奈 米 ( n m )。 現 今 元 件 從 微 米 世 代 進 入 到 了奈米的世代了,元件微縮除了降低製造成本與增加電晶體積集密度之 外,最主要還能提升元件的操作速度;因此,元件閘極的通道長度與閘 極 氧 化 層 厚 度 的 微 縮 已 是 必 然 的 趨 勢 【 2~3】 。 然 而 , 現 今 半 導 體 產 業 存 在 著 二 大 瓶 頸,一 是 當 元 件 不 斷 的 微 縮,將 會 有 不 好 的 短 通 道 效 應 (Shor t C h a n n e l E ffect, SCE) 出 現 , 其 二 是 傳 統 介 電 質 (dielectric)二 氧 化 矽 氧化層厚度已將接近極限,難以藉此來提升驅動電流。. 1.

(15) 一般而言,尺寸微縮之基本規範有兩種,即整體尺寸縮小或稱定電 場 尺 寸 縮 小 (full scaling or constant-filed scaling) 及 定 電 壓 尺 寸 縮 小 ( c o n stant-voltage scal ing)【 4】 , 其 中 最 被 廣 泛 應 用 的 規 範 為 定 電場微縮,但當元件尺寸不斷微縮時,其操作電壓並無法完全依照微縮 規範成比例下降,在元件進入深次微米時代後,將會出現各種短通道效 應,和增加閘極氧化層間的漏電流。例如汲極與源極之間因通道縮減, 使 得 空 乏 區 越 靠 越 近 , 造 成 基 板 穿 隧 電 流 增 加 , 崩 潰 電 壓 (Breakdown Voltage)下 降 , 嚴 重 時 更 會 引 起 貫 穿 效 應 (Punch Through Effect), 使 得 元 件 特 性 大 幅 衰 減 ; 此 外 , 還 會 伴 隨 著 次 臨 界 擺 幅 (Subthreshold S l o p e , SS) 的 增 加 與 汲 極 引 致 的 能 障 下 降 ( D r a i n - I n d u c e d B a r r i e r L o w e r i n g, DIBL)以 及 臨 界 電 壓 下 滑 (Threshold Voltage Roll-off)等 現 象 【 5~6】。 現 今 , 較 有 效 抑 制 短 通 道 效 應 的 方 法 有 使 用 較 薄 的 閘 極 氧 化 層 與 較 淺 的 源 、 汲 極 層 (Source/Drain Layer) ; 另 外 , 還 有 利 用 銦 環 型 佈 植 結 構 ( I n - H a l o 或 稱 為 口 袋 佈 植 Pocket Implantation) 來 抑 制 短 通 道 效 應 【 6~7】 。 其 次 , 當 元 件 進 入 奈 米 級 時 , 閘 極 氧 化 層 的 厚 度 約 微 縮 至 3nm 以 下 , 由 於 氧 化 層 厚 度 過 薄 , 閘 極 將 受 到 直 接 穿 隧 ( D i r e c t - Tunneling) 的 影 響 使 得 漏 電 流 遽 增 , 因 此 , 元 件 的 效 能 已 難 藉 由 縮 減 閘 氧 化 層 來 提 升 。 根 據 2006 年 國 際 半 導 體 技 術 藍 圖 (International Technology Roadmap for Semiconductors, ITRS)的 預 測 , 在 2 008 年 時 , 元 件 的 閘 極 尺 寸 可 能 微 縮 到 22nm , 而 氧 化 層 厚 度 則 為 0 . 9 n m ( 9 A) 。 為 了 解 決 傳 統 二 氧 化 矽 超 薄 氧 化 層 (Ultra Thinner Oxid e L a y e r ) 微 縮 的 問 題 , 故 ITRS 預 言 高 介 電 常 數 (High. Dielectri c. C o n s t a n t, High-K)材 料 將 被 用 來 取 代 傳 統 的 二 氧 化 矽 , 成 為 MOSFET用 來 抑 制 閘 極 直 接 穿 隧 漏 電 流 增 加 與 繼 續 元 件 微 縮 的 介 電 材 料 【 8~14 】 。 利 用高介電常數介電層可以抑制閘極漏電流的原因乃是在相同的等效氧化 層 厚 度 ( E quivalent Oxide Thickness , EOT) 下 , 其 物 理 厚 度 (P h y s i c a l 2.

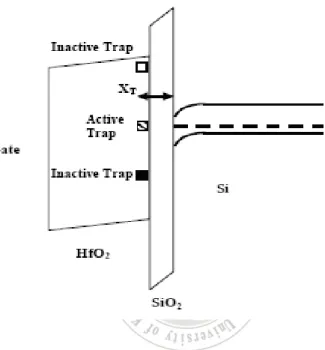

(16) T h i c k n e s s)為 傳 統 二 氧 化 矽 的 數 倍 , 故 可 抑 制 閘 極 漏 電 流 。 雖然高介電常數可有效的抑制閘極漏電流,但經過許多學者多年來 的 研 究 , 將 其 運 用 在 傳 統 的 CM OS 製 程 技 術 上 , 仍 舊 有 許 多 關 鍵 性 的 問 題 存 在 需 要 被 解 決 。 像 是 (1) 電 荷 補 捉 與 散 逸 ( C h a r g e T r a p p i n g a n d D e t r a p p ing): 在 元 件 受 到 偏 壓 及 溫 度 等 參 數 影 響 , 使 得 電 荷 被 補 捉 於 高 介電常數材料本體內與界面處,致使元件在電性上產生所謂的磁滯效應 ( H y s t e r e s i s E f f e c t ) 【 1 5 】。 ( 2 )較 高 的 界 面 陷 阱 密 度 (Interface Tra p D e n s i t y ):絕 大 部 份 的 高 介 電 常 數 材 料 屬 於 過 渡 金 屬 (Transition Metal ) 氧化物,及其材料的熱穩定性不佳,使得高介電常數與矽基板之間的界 面 特 性 不 佳 , 容 易 形 成 較 多 的 界 面 陷 阱 【 16 】 。 (3) 較 低 的 載 子 遷 移 率 ( M o b i l i ty , μ ) : 高 介 電 常 數 薄 膜 比 傳 統 的 二 氧 化 矽 有 更 嚴 重 的 庫 倫 散 射 ( C o u l omb Scattering)、 界 面 不 平 整 (Surface Roughness)及 聲 子 散 射 ( P h o n o n Scattering) 等 影 響 。 (4) 介 電 層 可 靠 度 的 問 題 : 研 究 指 出 , 當 介 電 層 厚 度 小 於 3.5nm 時 , 對 於 P 型 MOSFET 而 言 , 元 件 特 性 退 化 以 及 生 命 週 期 的 限 制 將 受 到 負 偏 壓 溫 度 不 穩 定 性 (Negative Bias Temperature I n s t a b i lity, NBTI)的 影 響 【 17~18】 。 因 此 , 有 許 多 的 學 者 正 研 究 著 如 何解決這二者之間存在的問題,然而在保有元件結構與不增加半導體製 作流程的情況下,選擇改善閘極通道工程是較不容易引發其他問題的方 法 。 例 如 (1) 採 用 超 薄 的 SOI(Ultra Thinner SOI , UTSOI) 能 有 效 的 提 升 轉 移 電 導 ( g m,Trans-Conducta nce)及 允 許 元 件 操 作 在 更 低 的 電 壓 下。(2 ) 運 用 應 變 矽 技 術 (Strain Silicon Technology), 由 於 應 變 矽 僅 需 改 變 矽 基 材 , 製 程 上 與 C MO S 均 相 容 , 是 一 種 不 需 要 改 變 製 程 就 能 大 幅 提 升 元 件 特 性 的 方 法 。 ( 3 ) 非 平 面 式 元 件 (3D Device), 如 鰭 式 電 晶 體 (Fin-FET), 此 種 設 計 大 大 的 增 加 了 MOS的 寬 度,增 加 了 元 件 的 驅 動 電 流 並 減 少 其 漏 電 流,同 時 也 縮 短 了 閘 極 的 通 道 長 度。除 了 極 短 的 閘 極 通 道 長 度 外,Fin-FE T 亦 可 依 製 程 的 技 術 在 通 道 形 成 Double gate 、 Tri-Gate 及 Nano-wire 等 來 3.

(17) 增 加 元 件 寬 度 【 19】 。 為了解決上述所提到的問題,我們利用應變矽的技術來改善。本論 文 所 研 究 探 討 的 應 變 方 式 為 利 用 閘 極 上 方 的 接 觸 蝕 刻 停 止 層 (Contact E t c h S t o p Layer , CESL) 來 造 成 通 道 產 生 應 力 , 藉 此 提 升 載 子 遷 移 率 的 技術;這樣的技術是近年來新發展出來的應變技術,用以產生應變矽通 道 , 其 優 點 為 能 與 現 有 的 MOSF ET 半 導 體 製 程 相 容 , 不 須 多 增 加 昂 貴 的 硬 體費用與製程步驟,因此可行性較高。實驗結果發現,雖由接觸蝕刻停 止層對通道產生應力能夠有效的提升載子的遷移率,但這樣的應力同時 也 會 對 元 件 造 成 一 定 程 度 的 傷 害 (Damage) , 因 此 我 們 也 對 這 種 具 應 變 技 術的金氧半場效應電晶體做可靠度的測試。. 1.2 有關應變技術之研究. 隨著半導體元件尺寸不斷的微縮,半導體工業面臨到了許多關鍵性 的挑戰。像是由於非常薄的介電層所引起的高閘極漏電流、較困難持續 維 持 高 比 率 的 導 通 與 截 止 電 流 (I on /I off )、 短 通 道 效 應 (SCE)、 高 功 率 散 逸等都是在小尺寸元件中所面臨到的挑戰。一些創新的技術像是應變工 程 ( S t r ain. Engineering) 、 淺 接 面 工 程 ( S h a l l o w. Junction. E n g i n e e r ing) 、 較 低 的 接 觸 電 阻 以 及 多 層 內 連 線 技 術 (Multilayer i n t e r c o n nects) 等 都 已 經 被 用 來 解 決 這 些 問 題 。 應 變 工 程 也 由 於 能 夠 提 升較大的通道載子遷移率,因此也被廣泛的相信它將是下一技術節點 ( T e c h n o l ogy Node)的 關 鍵 。 一 般 來 說 , 應 變 矽 的 分 類 可 由 作 用 的 面 積 大 小 來 區 別 為 全 面 性 應 變 矽 (Global. Strain) 又 稱 為 雙 軸 應 變. ( B i a x i a l -Strain) 與 局 部 性 應 變 矽 (Local Strain) 又 稱 為 單 軸 應 變 ( U n i a x i a l-Strain) , 其 中 施 加 的 應 力 種 類 又 可 包 括 伸 張 應 變 (Te n s i l e. 4.

(18) s t r a i n ) 及 壓 縮 應 變 (Compressive Strain)。 如 果 只 考 慮 到 前 段 製 程 , 則 應 變 的 方 式 可 分 為 基 板 應 變 (Substrate-Strain) 和 製 程 應 變 ( P r o c e s s -Induced Strain)二 種 。 應變矽發展的初期主要是以雙軸應變,利用材料的自然晶格常數 ( N a t u r a l Lattice)之 不 同 來 產 生 應 變 。 像 是 在 矽 表 面 以 磊 晶 方 式 成 長 不 同 比 例 的 Si 1 - x Ge x 晶 格 , 並 在 磊 晶 後 期 再 長 成 矽 原 子 , 由 於 晶 格 匹 配 的 關 係 , 使 得 磊 晶 後 的 矽 原 子 受 到 底 部 自 然 晶 格 常 數 較 大 的 鍺 (Ge) 原 子 拉 伸,因而形成伸張應變於矽層內;經由實驗證明,電子電洞遷移率均能 有效的提升。而全面應變矽具有提升載子遷移率的優點之外,其後續製 程 亦 與 M O S 製 程 相 同 。 如 應 變 矽 於 矽 鍺 基 板 (Relaxed SiGe)、 絕 緣 層 上 矽 鍺. ( S i G e-On-Insulator ,. SGOI) 、. 與. 絕. 緣. 層. 上. 應. 變. 矽. ( S t r a i n e d-Si-On-Insulator , SSOI) 等 都 屬 常 見 的 全 面 應 變 矽 。 另 外 單 軸 應 變 的 原 理 則 是 採 用 某 些 製 程 步 驟 , 像 是 淺 溝 槽 絕 緣 (Shallow Trenc h I s o l a t i o n, STI)、 矽 化 反 應 ( Silicidation)、 接 觸 蝕 刻 停 止 層 ( C o n t a c t E t c h S t o p Layer, CESL)、 或 矽 鍺 源 汲 極 (SiGe S/D)等 製 程 相 關 的 結 構 , 運用其存在之應力施加於元件上,以形成應變通道。單軸應變屬於局部 應 變 , 即 通 道 上 不 同 的 位 置 其 應 變 大 小 亦 不 同 , 可 在 X、 Y、 Z 方 向 分 別 得 到不同載子遷移率的變化,同時單軸應變與元件結構如通道長度與寬度 有 相 關 性 【 19~49】 。. 5.

(19) 1.3 論文架構. 為 了 瞭 解 元 件 尺 寸 在 微 縮 的 條 件 下 , 我 們 進 行 了 幾 種 不 同 SOI厚 度 的 條件做元件特性的探討;另外,我們採用幾種不同應力大小的接觸蝕刻 停止層,深入的研究接觸蝕刻停止層對金氧半場效應電晶體的影響。對 於不同條件的比較及實驗結果,可分為下面幾個章節來探討。 在 本 論 文 的 第 二 章 我 們 主 要 利 用 基 本 電 性 量 測 的 方 式 探 討 : (1)在 不 同 S OI厚 度 以 及 不 同 應 力 的 接 觸 蝕 刻 停 止 層 的 製 程 條 件 下 , 對 元 件 所 造 成 的 影 響 是 否 有 所 差 異 ; (2)在 不 同 應 力 的 接 觸 蝕 刻 停 止 層 , 其 對 金 氧 半 場 效應電晶體電性的影響程度。 第 三 章 中 , 我 們 知 道 雖 然 利 用 閘 極 上 方 的 接 觸 蝕 刻 停 止 層 (Contact E t c h S t o p Layer , CESL) 能 在 通 道 中 產 生 應 力 , 藉 此 提 升 載 子 遷 移 率 , 但是,這層接觸蝕刻停止層相對的也會對元件造成一定程度迫害,可能 在 氧 化 層 內 ( o xide defect ) , 或 是 在 矽 層 (T S i ) 與 前 端 氧 化 層 ( F r o n t - O xide)之 界 面 造 成 界 面 缺 陷 (interface defect); 因 此 我 們 利 用 二 種 量 測 方 式 : ( 1 ) 電 荷 幫 浦 (Charge Pumping), (2)低 頻 1/ f 雜 訊 (Lo w F r e q u e n c y Flicker Noise)的 方 式 探 討 。 第四章則是探討這層接觸蝕刻停止層對元件所造成的可靠度問題之 比 較 , 我 們 分 別 對 N、 PMOSFET做 了 二 種 實 驗 來 討 論 。 (1)熱 載 子 注 入 效 應 ( H o t - C a r rier Injection Effect, HCIE), (2)正 偏 壓 不 穩 定 性 (Positiv e Bias. Instability , PBI) 以 及 負 偏 壓 不 穩 定 性 (Negative. Bias. I n s t a b i l ity, NBI)。 在第五章的部份,我們對上述所提到的主題做總結,藉此瞭解應變 矽對元件所造成的影響,並提出對應變元件未來之展望。. 6.

(20) 第二章 基本電性量測結果分析. 2-1 先進元件製程. 半 導 體 元 件 在 近 30 年 來 不 斷 的 改 善 製 程 技 術 與 元 件 的 微 縮 , 其 目 的 在於降低成本、功能的增加以及效能的提升。本論文使用具多項先進製 程 技 術 的 CMOSFET 元 件 做 量 測 , 其 中 包 括 絕 緣 層 上 矽 (SOI) 、 淺 溝 槽 絕 緣 ( S h a l l o w Trench Isolation, STI)、 金 屬 閘 極 (Metal Gate)、 接 觸 蝕 刻 停 止 層 ( Contact Etch Stop Layer, CESL)等 技 術 。. 2 - 1 - 1 絕 緣 層 上 矽 (Silicon O n Insulator, SOI). S O I 與 傳 統 的 塊 材 矽 (Bulk-Si) 相 比 較 , 因 為 多 了 一 層 氧 化 層 , 元 件 之 間 彼 此 間 距 因 為 少 了 N 或 P 井 (Well) 而 縮 短 、 在 晶 圓 上 所 佔 的 面 積 可 以 大 幅 縮 小 、 具 有 低 電 壓 與 低 消 耗 功 率 、 較 佳 的 絕 緣 度 、 電 導 ( T r a n s - Conductor , Gm) 更 好 、 較 高 的 可 靠 度 (Reliability) 、 抑 制 短 通 道 效 應 ( for FD-SOI) 、 更 陡 斜 的 次 臨 限 斜 率 與 減 少 接 面 寄 生 電 容 等 特 性 【 50~51】 。 SOI晶 圓 製 作 方 面 , 目 前 較 常 見 的 有 SIMOX(separation by implante d o x y g e n ) 、 BESOI(bonding & etchback) 與 Unibond 法 , 亦 稱 為 smart-cu t 法 三 種 。 我 們 採 用 的 SOI晶 片 ( Wafer)是 使 用 smart-cut方 法 製 出 , 它 是 由 BESOI所 衍 生 出 來 的 方 法 , 一 樣 需 要 使 用 到 二 片 晶 片 , 先 在 一 片 頂 端 長 好 二氧化矽晶片利用離子佈植方法植入氫離子,再與另一片晶片做結合 (Bonding), 然 後 進 行 400~600度 的 熱 退 火 製 程 , 先 前 植 入 的 氫 離 子 因 熱 產 生 氣 泡 使 晶 片 自 然 斷 裂,最 後 再 用 化 學 機 械 研 磨 (Chemical Mechanica l 7.

(21) P o l i s h i n g, CMP)的 方 式 進 行 表 面 平 整 的 工 作 使 表 面 平 整 即 可 完 成 。 而 斷 開後的矽晶片仍然可以繼續使用,是相當經濟且品質佳的方式。. 2 - 1 - 2 金 屬 閘 極 (Metal-Gate). CMOS製 程 的 一 項 重 要 發 展 為 導 入 了 金 屬 閘 極 的 製 程 。 多 晶 矽 導 電 性 不如金屬,限制了訊號傳遞的速度。雖然可以利用摻雜的方式改善其導 電 性 , 但 成 效 仍 然 有 限 。 以 及 多 晶 矽 (Poly-Silicon) 在 偏 壓 下 , 會 因 為 掺雜物空乏使得閘極的電容值降低,或過多的掺雜物因擴散而穿透過閘 極 氧 化 層 (Gate Oxide) , 造 成 臨 限 電 壓 不 穩 的 情 形 , 而 使 用 金 屬 矽 化 閘 極可以避免此問題。此外,金屬矽化閘極還具有理想的遷移率、較低的 閘 極 漏 電 流 、 高 電 導 值 (Tr ans-Conductor , Gm) 及 可 調 整 臨 限 電 壓 ( T h r e s h old Voltage , Vt) 而 且 又 能 夠 耐 受 高 溫 製 程 。 因 為 金 屬 矽 化 物 的 位 置 是 在 閘 極 表 面 , 離 通 道 區 較 遠 , 所 以 也 不 會 對 MOSFET 的 臨 界 電 壓 造 成 太 大 影 響 等 【 52~57】 。 由於互補式金氧半場效應電晶體元件在執行最佳化時,需要分別對 N M O S 與 P M OS 調 整 適 合 的 功 函 數 , 所 以 必 須 要 用 到 二 種 不 同 功 函 數 的 金 屬 材 料 , 一 種 使 用 在 NMOS 上 , 而 另 一 種 則 使 用 在 PMOS 上 。 然 而 這 樣 的 需 求 將會造成製程步驟增加,同時也將會提高元件製造的複雜度及成本;在 此 , 我 們 採 用 了 鎳 (Nickel)金 屬 來 匹 配 N、 PMOS所 需 要 的 功 函 數 , 並 對 閘 極 進 行 金 屬 化 的 製 程,使 得 閘 極 變 成 Ni-FUSI Gate,同 時 運 用 在 N、PMOSFE T 元 件 上 。 這 種 將 多 晶 矽 完 全 的 合 金 化 的 方 法 稱 之 為 FUSI ( Fully-Silicide polysilicon gate)製程。. 8.

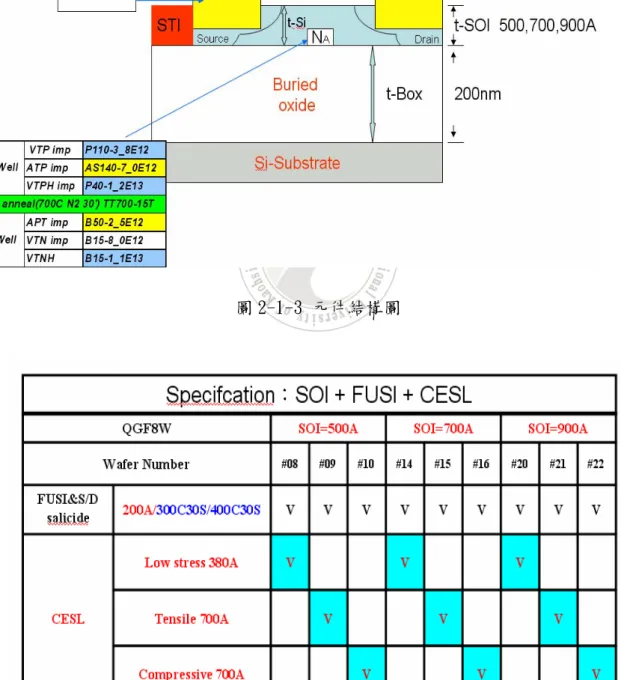

(22) 2 - 1 - 3 接 觸 蝕 刻 停 止 層 (Contact Etch Stop Layer, CESL). 應 變 技 術 的 種 類 大 致 上 可 分 為 二 種 ; 一 種 為 全 面 應 變 矽 (Global S t r a i n ), 這 是 運 用 材 料 上 晶 格 常 數 的 差 異 來 產 生 應 變 , 此 種 應 變 技 術 因 元件製作在同一基板上,不同的通道位置應力大小均相同,故也稱為雙 軸 應 變 ( Biaxial-Strain) , 因 為 應 變 力 存 在 於 基 板 表 面 平 行 及 垂 直 元 件 通 道 的 二 個 方 向【 1 9、2 1 】。此 外,另 一 種 為 局 部 應 變 矽 ( L o c a l S t r a i n ) 。 近 年 來 許 多 的 研 究 都 是 運 用 氮 化 矽 層 (SiN) 所 引 起 的 應 變 矽 通 道 會 影 響 元件的特性。一般來說,沉積氮化矽的方式有二種方式,若要使氮化矽 層 具 有 擴 張 應 變 的 效 果 , 則 使 用 高 溫 熱 成 長 化 學 氣 相 沉 積 (Chemica l Vapor Deposition, C V D ) 氮 化 矽 層 ; 欲 使 氮 化 矽 層 具 有 壓 縮 應 變 的 效 果 , 則 採 用 電 漿 增 強 式 化 學 氣 相 沉 積 (Plasma Enhanced Chemical Vapo r D e p o s i t i on , PECVD)氮 化 矽 層 來 完 成 。 本 論 文 所 使 用 的 元 件 結 合 了 上 述 幾 種 針 對 CMOS 元 件 做 效 能 提 升 的 新 技 術 , 首 先 使 用 s m art-cut SOI 製 程 , 如 圖 2 - 1 - 1 , 再 對 閘 極 進 行 全 金 屬 矽 化 , 最 後 沉 積 一 層 氮 化 矽 應 力 層 , 元 件 製 作 流 程 如 圖 2-1-2, 元 件 結 構 圖 , 如 圖 2-1-3 ; 在 此 我 們 擁 有 九 種 不 同 條 件 的 試 片 , 三 種 不 同 SOI 厚 度 的 條 件 , 分 別 為 500A、 700A、 及 900A, 另 外 , 我 們 針 對 同 一 SOI厚 度 的 條 件 分 別 再 做 三 種 不 同 應 力 條 件 的 試 片 , 分 別 為 傳 統 的 SiN 380A 、 高 伸 張 應 力 條 件 (High Tensile 700A) 及 高 壓 縮 應 力 條 件 ( H i g h C o m p r e s s i v e 7 0 0 A ) ; 如 表 2-1。. 9.

(23) 2-2 基 本 元 件 電 性 量 測 設 計. 我 們 的 實 驗 使 用 到 的 硬 體 是 八 吋 的 探 針 座 (DC Probe Station) , 如 圖 2 - 2 - 1 、 半 導 體 參 數 分 析 儀 ( HP-4156B) , 如 圖 2-2-2 、 電 感 電 容 電 阻 阻 抗 分 析 儀 (LCR-Analyzer, HP- 4284A), 如 圖 2-2-3、 低 漏 電 流 矩 陣 式 交 換 器 (HP-E5250A), 如 圖 2-2-4, 及 個 人 電 腦 一 部 ; 而 軟 體 的 部 份 則 使 用 由 安 捷 倫 公 司 (Agilent) 所 提 供 的 I C S ( I n t e r a c t i v e C h a r a c t e r i z a t i o n S o f t w a r e )軟 體 , 如 圖 2-2-5。 為 了 分 析 基 本 的 MOSFET 元 件 特 性 , 我 們 採 用 了 以 下 幾 種 量 測 方 式 , 用以萃取基本特性及物理上的分析,並探討閘極氧化層;以下分別針對 這些量測方法做一簡單的說明。. 2 - 2 - 1 電 容 - 電 壓 特 性 分 析 (C-V). 在 全 金 屬 矽 化 物 閘 極 CMOSFET 的 氧 化 層 特 性 是 利 用 HP-4284A 阻 抗 分 析 儀 在 頻 率 為 100KHz條 件 下 所 量 測 獲 得 的 。 所 有 的 C-V Curve均 是 將 元 件 操 作 在 累 增 區 再 到 反 轉 區 , 量 測 元 件 的 尺 寸 為 W/L=10μ m/10μ m, 其 目 的 在 於 量 測 氧 化 層 等 效 厚 度 (Tox )等 參 數 。. 2 - 2 - 2 I D-VD 特 性 曲 線. I D - V D 量 測 是 使 用 Agilent HP-4156B 半 導 體 參 數 分 析 儀 。 將 元 件 源 極 端 與 基 極 端 同 時 接 地 ( V S =V B = 0V), 由 汲 極 電 流 I D 和 汲 極 電 壓 V D 構 成 所 謂 的 輸 出 特 性 (Output Charact eristics) 曲 線 。 閘 極 電 壓 設 定 為 St ep( 從 0 V ~ 1 . 2 V , 每 0.6V 一 個 Step) , 汲 極 電 壓 設 定 為 Sweep( 從 0V~1.2V) ; 此 輸. 10.

(24) 出 特 性 曲 線 可 以 分 為 截 止 區 (Cut-Off Region)、 線 性 區 (Linear Region ) 及 飽 和 區 (Saturation Region)等 三 個 區 域 , 如 圖 2-2-6。. 2 - 2 - 3 I D -VG 特 性 曲 線. I D - VG 量 測 亦 使 用 Agilen t HP-4156B 半 導 體 參 數 分 析 儀 。 同 樣 將 元 件 源 極 端 與 基 極 端 同 時 接 地 (V S =V B =0V) , 並 將 元 件 操 作 在 線 性 區 ( V D S =0.05V) , 量 測 其 閘 極 (V G ) 電 壓 與 汲 極 電 流 ( I D ) 的 關 係 , 進 而 萃 取 出 臨 限 電 壓 ( V T ) 與 轉 移 電 導 (Gm) , 如 圖 2-2-7。. 2-3 C-V 量 測 結 果 與 分 析. 首 先 我 們 選 擇 固 定 SOI厚 度 (SOI=500A、 700A、 及 900A)的 條 件 下 , 改 變 不 同 C ESL 層 條 件 ( L o w T e n s i l e 3 8 0 A 、 H i g h T e n s i l e 7 0 0 A 、 以 及 H i g h C o m p r e s s ive 700A) 做 了 三 種 對 照 組 , 之 後 再 選 擇 固 定 C E S L 條 件 ( L o w T e n s i l e 380A、 High Tensile 700A以 及 High Compressive 700A), 而 改 變 不 同 S O I厚 度 (SOI=500A、 700A以 及 900A)條 件 下 做 了 三 種 對 照 組 ; 用 以 觀 察 在 相 同 S O I 厚 度 而 具 有 不 同 CESL層 條 件 下 , 以 及 在 相 同 CESL層 條 件 而 具 有 不 同 SOI厚 度 的 情 況 下,是 否 會 因 製 程 的 影 響 而 導 致 元 件 特 性 有 所 變 化。 我 們 採 用 的 元 件 尺 寸 固 定 在 W/L=10μ m/10μ m, 利 用 上 述 提 到 量 測 電 容 - 電 壓 特 性 分 析 (C-V) 的 方 式 , 觀 察 其 電 容 對 電 壓 的 特 性 是 否 有 所 變 化 。 圖 2 - 3-1~3 是 N MOS 元 件 分 別 在 固 定 SOI 厚 度 為 500 、 700 及 9 00A 時 , 改 變 不 同 C ES L 應 力 層 條 件 (Low Tensile 380A 、 High Tensile 700A 、 Hig h C o m p r e s sive 700A)所 量 測 得 到 的 電 容 對 電 壓 特 性 圖 形 。 由 此 三 張 圖 形 我. 11.

(25) 們 可 以 見 到 元 件 在 W/L=10 μ m/10 μ m 及 SOI 厚 度 相 同 的 條 件 下 , 不 同 的 C E S L 應 力 層 並 不 會 對 元 件 造 成 明 顯 的 影 響;如 臨 限 電 壓 的 漂 移 (V T Shift ) 以 及 經 由 全 金 屬 矽 化 閘 極 的 製 程 後 亦 不 會 造 成 閘 極 空 乏 ( P o l y - D e pletion)導 致 電 容 值 下 降 的 現 象 發 生 。 圖 2-3-4~6是 NMOS元 件 分 別 在 固 定 CESL 應 力 層 條 件 下 (Low Tensile 380A 、 High Tensile 700A 、 H i g h C o m pressive 700A), 分 別 改 變 不 同 SOI厚 度 條 件 ( SOI=500、 700、 9 0 0 A ) 所 量 測 得 到 的 電 容 對 電 壓 特 性 圖 形 。 我 們 亦 可 見 到 其 CV 圖 形 並 不 會 因 SOI 厚 度 不 同 而 造 成 明 顯 的 影 響 。 圖 2-3-7~9 是 PMOS 元 件 分 別 在 固 定 S O I 厚 度 為 500 、 700 及 900A 時 , 改 變 不 同 CESL 應 力 層 條 件 ( L o w T e n s i l e 3 8 0 A 、 H i gh Tensile 700A、 High Compressive 700A)所 量 測 得 到 的 電 容 對 電 壓 特 性 圖 形。相 同 的,由 此 三 張 圖 形 我 們 可 得 知 不 同 的 C E S L 應 力 層 , 在 P M O S 的 情 況 下 影 響 也 不 明 顯 。 圖 2-3-10~12是 PMOS元 件 分 別 在 固 定 CES L 應 力 層 條 件 下 , 分 別 改 變 不 同 SOI厚 度 條 件 所 量 測 得 到 的 電 容 對 電 壓 特 性 圖 形 , 其 結 果 亦 相 同 。 由 上 述 圖 2-3-1~12, 我 們 可 以 得 知 , 在 SOI厚 度 及 C E S L 應 力 層 條 件 不 同 的 情 況 下 , NMOS 與 PMOS 的 CV 特 性 影 響 並 不 大 , 另 外 我 們 亦 經 由 式 (1)可 以 計 算 出 氧 化 層 的 厚 度 。 d = ε oε rA / C … … … … … … … … … … … … … … … … … … … … … … … … ( 1 ). 接 著 我 們 欲 探 討 W/L=10 μ m/10 μ m 的 元 件 尺 寸 在 不 同 應 力 的 條 件 下,應 變 機 制 是 否 對 元 件 效 能 有 所 提 升,因 此 我 們 採 用 了 常 見 的 Split-C V 方 式 有 效 的 量 測 載 子 的 遷 移 率 【 58~60 】 。 由 圖 2-3-13~14 結 果 顯 示 N 、 PMOSFET經 過 高 應 力 應 變 層 所 造 成 遷 移 率 略 微 高 於 傳 統 低 應 力 應 變 層,但 並不是相當的明顯,主要原因為元件尺寸較大,導致元件通道受到應變 層所產生的影響較不明顯,因此元件遷移率提升的效能相當有限。另外 在 圖 2 - 3 -15~16 中 我 們 可 以 發 現 到 不 論 是 在 NMOSFET 或 PMOSFET 的 情 況 下 , 臨 限 電 壓 都 將 隨 著 通 道 逐 漸 微 縮 而 下 滑 (V T roll-off), 且 不 論 是 在 高 應 力 或 低 應 力 應 變 層 下 , 都 將 出 現 所 謂 的 短 通 道 效 應 發 生 (Short 12.

(26) C h a n n e l Effect , SCE) ; 明 顯 的 , 經 過 高 應 力 的 應 變 機 制 元 件 其 臨 限 電 壓均會高過傳統的低應力應變層元件,之所以會這樣,其主要原因乃是 高 應 力 應 變 層 會 對 元 件 的 氧 化 層 與 矽 層 界 面 造 成 界 面 缺 陷 (interface d e f e c t ) , 導 致 載 子 被 補 捉 (tr ap), 因 而 需 要 更 高 的 臨 限 電 壓 (V T )。. 2-4 I-V 量 測 結 果 與 分 析. 由 於 在 W/ L = 1 0 μ m/ 1 0 μ m 的 元 件 尺 寸 受 到 應 力 影 響 的 程 度 並 不 明 顯 , 因 此 我 們 改 採 用 尺 寸 較 小 的 元 件 W/L=10μ m/0.09μ m的 元 件 尺 寸 來 探 討 其 基 本 電 性 。 從 先 前 的 文 獻 【 19、 21~27、 29、 32、 34、 35、 37、 39、 4 4、 46、 4 8, 4 9 】 中 可 知 道 , 若 將 單 軸 伸 張 應 變 技 術 應 用 在 NMOSFET元 件 上 及 導 入 單 軸 壓 縮 應 變 技 術 至 PMOSFET元 件 上,其 對 元 件 的 效 能 均 具 有 提 升 的 作 用 。 圖 2-4-1為 製 程 所 引 起 的 元 件 應 變 3D立 體 示 意 圖 【 26】 。 我 們 可 以 從 表 2 - 2 及 表 2- 3 【 2 1 、 2 6 】 得 知 元 件 在 單 軸 與 雙 軸 應 變 下 , 載 子 遷 移率的變化情形。 這些應變後的元件特性表現可歸因於汲極電流公式中載子的遷移率 受應變作用而有所變化。若從能帶結構相關參數來檢驗載子的遷移率變 化,則載子於能谷的分佈比例、散射率與有效質量等三種參數影響最直 接。由於矽通道因應變而改變能帶與價帶的結構,造成次能帶的分離, 載子容易聚集在次能帶,有效的載子質量降低,也降低了載子在能谷內 的 散 射 率 (intervalley scatt ering rate) , 進 而 提 升 了 載 子 的 遷 移 率 【 1 9、 2 1】。 圖 2-4-2為 NMOS在 不 同 應 變 層 元 件 之 ID-VD比 較 圖 , 由 圖 中 我 們可以很明顯的發現到,運用高伸張應變技術的確能有效提升元件的驅 動 電 流 ; 相 同 的 在 元 件 的 轉 移 電 導 能 力 也 能 有 所 提 升 , 如 圖 2-4-3。 而 在 圖 2 - 4 - 4 與 2-4-5 中 我 們 可 以 見 到 高 伸 張 應 變 的 元 件 有 較 高 的 閘 極 引 致 汲. 13.

(27) 極 漏 電 ( G ate Induced Drain L eakage, GIDL)的 效 應 與 閘 極 漏 電 流 較 高 , 其 主 要 的 原 因 是 因 為 高 伸 張 應 力 會 對 通 道 及 Si/SiO2界 面 造 成 缺 陷 , 導 致 元件的漏電流較高。 在 P M OS 元 件 方 面 也 跟 NMOS 元 件 有 著 類 似 的 情 形 , 高 壓 縮 應 變 元 件 對 提 升 元 件 的 驅 動 電 流 及 轉 移 電 導 都 能 有 所 幫 助 , 見 圖 2-4-6 及 2-4-7 ; 但 在 元 件 漏 電 流 的 部 份,我 們 可 以 看 到,GIDL及 閘 極 漏 電 流 差 異 並 不 明 顯 , 其 主 要 原 因 為 我 們 所 使 用 的 低 應 力 應 變 矽 元 件 乃 是 屬 於 傳 統 的 SiN 低 伸 張 ( L o w T e n s i l e ) 應 變 而 非 低 壓 縮 (L ow Compressive) 應 變 , 因 此 我 們 認 為雖然高壓縮應力機制會因為應力過大而對元件造成缺陷,但低伸張應 力 不 僅 對 PMOS 元 件 效 能 沒 有 幫 助 , 反 而 還 會 因 為 低 伸 張 應 力 的 影 響 造 成 元 件 的 退 化 , 如 圖 2-4-8與 2-4 -9。 相 同 的 , 我 們 也 去 探 討 在 不 同 SOI厚 度 的 條 件 下 (500A、 700A), N、 PMOS在 驅 動 電 流 與 轉 移 電 導 都 能 有 所 提 升 , 見 圖 2 - 4 -10~17。此 外,我 們 也 針 對 應 變 元 件 的 導 通 與 截 止 電 流 (Ion-Iof f ) 做 探 討 , 圖 2-4-18為 SOI=900A NMOS元 件 的 Ion-Ioff比 較 圖 , 我 們 清 楚 的 看到在相同截止電流下,高伸張應變元件具有較佳的導通電流,原因為 其 對 N M O S 元 件 能 有 效 提 升 驅 動 電 流 ; 同 樣 的 , PMOS 元 件 在 高 壓 縮 應 變 的 作 用 下 , 在 相 同 的 截 止 電 流 下 也 能 有 較 好 的 導 通 電 流 , 見 圖 2-4-19 。 圖 2-4-20 與 2-4-21 分 別 為 SOI=700A 時 N 、 PMOS 的 導 通 與 截 止 電 流 ( I o n - I o ff), 均 與 SOI=900A時 有 著 相 同 的 趨 勢 。. 14.

(28) 第三章 氧化層品質量測結果與分析. 由 上 述 基 本 電 性 (IG-VG 與 ID-VG) 中 得 知 , 在 高 應 力 應 變 機 制 作 用 下 , 雖 然 驅 動 電 流 (ID) 與 轉 移 電 導 (Gm) 均 能 有 效 的 提 升 , 但 也 由 於 高 應 力對元件閘氧化層及矽基板與氧化層界面的影響,造成元件產生缺陷 ( d e f e c t )。因 此,我 們 採 用 了 二 種 量 測 技 術 方 法 來 探 討 在 高 應 力 作 用 下 , 元件受應力所產生缺陷的情形。 用 來 檢 測 電 晶 體 (Transistor) 氧 化 層 陷 阱 電 荷 密 度 (Density of O x i d e T r apped Charge) 與 界 面 陷 阱 電 荷 密 度 (Density of Interfac e T r a p s ) 目 前 最 常 見 的 方 式 有 : 電 荷 幫 浦 (Charge Pumping) 與 1/ f 雜 訊 ( O n e - O v e r-f Noise 或 Flicker Noise)【 61~64】 。. 3-1 低 頻 雜 訊 (Low frequency noise). 舉凡所有不希望接受到的訊號都可以稱作“雜訊"。電雜訊通常是 存在於電子元件和電路本身;產生雜訊的物理機制統稱為雜訊源,一般 與元件的結構內載子流動、行徑路線及材料界面有關。通常,在半導體 元 件 內,主 要 的 雜 訊 分 別 有:(1) Thermal noise、(2) Shot noise、(3) Avalanche noise、(4) Generation-Recombination noise、(5) Low frequency noise【65~67】。. 3-1-1. Thermal noise (Johnson noise):. 熱雜訊廣泛的存在於電阻性元件中,本質上看來是不能完全被消除 的,同時它也代表著電阻性元件最小的雜訊。熱雜訊是由於半導體中的 載 子 (electorn or hole)在 非 絕 對 零 度 的 環 境 下 , 電 荷 載 子 因 有 隨 機 的 熱運動,這種無規則運動的載子在半導體內行進時會碰撞到晶格缺陷、 15.

(29) 殘留的離子或鍵結邊界,此時微量的能量交換造成了電流或電壓偏離平 均值的微擾動,這種機制即是熱雜訊的來源。熱雜訊的現象必須在熱平 衡的狀態下才成立,其雜訊強度為: v 2 = 4 KTRΔf … … … … … … … … … … … … … … … … … … … … … … … … ( 2 ). i 2 = 4 KT. 1 Δf … … … … … … … … … … … … … … … … … … … … … … … ( 3 ) R. 3-1-2. S hot Noise:. 散 射 雜 訊 (shot noise) 是 由 於 電 子 或 電 洞 隨 機 性 的 穿 過 能 障 , 和 元 件中的電流或外加的電壓有關,一旦電流或電壓消失,散射雜訊也會隨 著消失。在電子元件中,尤其是在半導體元件,當載子要跨越過具有不 同 能 量 間 隙 界 面 時,載 子 跳 躍 路 徑 非 平 滑 連 續 的,而 是 隨 機 獨 立 的 事 件 。 一 般 常 見 的 半 導 體 元 件 如. p-n junction 、 Schottky barrier 、. H e t e r o - j unction 等 所 造 成 的 雜 訊 , 其 雜 訊 強 度 為 : i 2 = 2qI dc Δf ………………………………………………………………………( 4 ). 3-1-3. Avalanche noise:. Avalanche noise 是 因 為 Zener breakdown 或 Avalanche breakdown 產生的雜訊,通常發生在接面。 3-1-4. Generation-Recombination noise (G-R noise):. G e n e ration-Recombination noise 是 另 一 種 出 現 在 半 導 體 元 件 中 的 雜訊型式,在大部份的情況下是由於元件中的雜質與缺陷所引起的,屬 於半導體材料及場效應電晶體裡主要的低頻雜訊之一。 在半導體材料與元件中,存在著能夠發射或補捉電荷載子的缺陷與 16.

(30) 雜 質 , 由 於 載 子 在 Conduction band 與 Valence band 間 , 隨 機 的 產 生 與 複 合 , 即 形 成 所 謂 的 產 生 -複 合 雜 訊 , 其 雜 訊 強 度 為 : SN (ΔN 2 ) 4τ = ………………………………………………………………(5) N2 N 2 1 + ω 2τ 2 Ic i2 = K Δf …………………………………………………………………..(6) f 2 1+ ( ) fc. 3-1-5. Low frequency noise (Flicker noise):. Low frequency noise一 般 認 為 與 缺 陷 擾 動 有 關 連 , 如 MOSFET之 汲 極 電 流 雜 訊 或 與 載 子 遷 移 率 有 關 , 如 BJT的 集 極 和 基 極 電 流 雜 訊 ; 有 時 此 一 雜 訊 擾 動 與 材 料 表 面 或 鍵 結 顆 粒 邊 界 有 關 , 如 金 屬 的 電 阻 電 流 雜 訊 。 Low f r e q u e n c y noise為 在 低 頻 時 主 要 發 生 的 雜 訊 , 最 先 被 發 現 於 真 空 管 時 代 【 68】 。L ow frequency noise經 常 被 稱 為 Flicker noise,或 是 1 / f n o i s e , 其 產 生 n oise 的 原 因 為 Oxide traps 或 Crystal defect 捕 捉 或 釋 放 載 子 所 造 成 的 雜 訊 , 因 此 , 對 於 研 究 S i O 2 、 High-k 閘 極 氧 化 層 的 q u a l i t y 與 r e l i a b i l ity , Flicker noise 變 成 一 種 很 重 要 的 特 徵 工 具 【 69~77 】。 有 關 於 F l i c ker noise的 理 論 , 從 研 究 文 獻 中 發 現 , 有 許 多 不 同 的 理 論 模 型 去 解 釋 F l icker noise在 MOSFET 中 的 物 理 現 象,主 要 的 理 論 模 型 有 三:(1 ) Carrier number fluctuation model (McWhorter number fluctuation t h e o r y ) 【 7 8 】、 ( 2 ) M o b i l i t y f l u ct u a t i o n m o d e l ( Ho o g e m o bi l i t y f l u c t u a t ion theory) 【 79】 、( 3) Unified noise model 【 80】 。Mc W h o r t e r 提 出 在 M OSFET 中 , 因 為 Oxide traps 會 與 通 道 中 的 載 子 引 起 Trapping 與 D e t r a p p i ng的 物 理 現 象 , 因 此 造 成 載 子 Number的 fluctuation, 進 而 產 生 雜 訊 , 又 稱 為 Δ N theory。 而 Hooge則 提 出 因 為 載 子 在 晶 格 中 運 動 會 與 晶 格 引 起 L a ttice scattering或 與 雜 質 引 起 Impurity scattering, 因 此 造 成 的 載 子 Mobility的 fluct u a t i o n, 進 而 產 生 雜 訊 , 又 稱 為 Δ μ t h e o r y 。 17.

(31) 這兩大理論模型一直被研究者廣泛的探討,亦各有其支持者,而且其兩 大 理 論 之 間 有 其 關 聯 性 。 1990 年 , Kwok K. Hung 提 出 了 Unified noise m o d e l 【 8 0】, 將 C a r r i e r n u m b e r f l u c t u a t i o n m o d e 與 S u r f a c e m o b i l i t y fluctuation mechanism 結 合 起 來 , 主 要 說 明 由 於 Oxide traps 對 通 道 載 子 的 T r a p p i n g 與 De t r a p p i n g 現 象 造 成 了 Carrier number fluctuation ; 此 外 , 當 載 子 被 O x i d e t r a p s 捕 捉 後 , 其 對 通 道 中 載 子 的 C o u lo m b i c s c a t t e r i ng effect 也 造 成 表 面 載 子 mobility 的 fluctuation , 這 兩 項 物 理 機 制 皆 可 使 Drain current產 生 擾 動 , 而 且 也 只 有 當 電 子 被 分 佈 大 約 在 Q u a s i - F e rmi Lever 附 近 (~ ± kT) 的 traps 捕 捉 時 , 此 fluctuation 才 有 貢 獻 , 如 圖 3-1-1 【 81】。 因 此 我 們 可 將 Drain current 的 變 化 分 量 以 下 是 表示:. δI d Id. ⎡ 1 δΔN 1 δμ eff ⎤ = −⎢ ± ⎥δΔN it … … … … … … … … … … … … … … … … … … ( 7 ) ⎣ ΔN δΔN it μ δΔN it ⎦. 3-2 Flicker noise 量測結果分析. 3-2-1. 實驗量測方式. 本 實 驗 所 使 用 到 的 儀 器 有 : ( 1) HP4145 Precision Semiconducto r P a r a m e t e r Analyzer、 ( 2) HP35670A Dynamic Signal Analyzer、 及 ( 3 ) B T A 9 8 1 2 B F E T N o i s e A n a l y z e r ; 而 軟 體 有 :( 1) Cadence NOISEPro、( 2 ) BSIMPRO。 為了防止元件提前進入飽和區,導致通道夾止,故我們將元件操作 在 線 性 區 進 行 量 測 ; 閘 極 電 壓 (VG) 我 們 設 定 在 略 大 於 臨 限 電 壓 (VT) 確 保 元 件 通 道 在 反 轉 區 , 而 汲 極 電 壓 (VD)則 設 在 0.05V, 使 元 件 進 入 線 性 區 ;. 18.

(32) 而 頻 率 從 1Hz~100KHz。 此 外 我 們 也 針 對 元 件 進 行 飽 和 區 之 low frequenc y n o i s e 量 測 , 用 以 探 討 在 通 道 夾 止 時 , CESL應 力 層 對 元 件 所 造 成 的 缺 陷 分 佈 機 制 ; 在 飽 和 區 電 壓 之 量 測 設 定 為 : 閘 極 電 壓 (VG) 我 們 一 樣 設 在 略 大 於 臨 限 電 壓 (VT) 以 確 保 元 件 通 道 在 反 轉 區 , 而 汲 極 電 壓 ( V D) 則 設 在 1.0V, 使 通 道 夾 止 。. 3-2-2. 實驗結果. 由上一章節,我們針對傳統的低伸張應力、高伸張應力、及高壓縮 應 力 三 種 試 片 進 行 I - V 與 C - V 基 本 電 性 分 析 , 從 實 驗 結 果 得 知 , 運 用 CESL 應 變 技 術 引 起 單 軸 應 變 矽 元 件 因 Strained-Si Channel中 應 變 層 結 構 , 減 少了載子的有效質量與散射率,使得載子的遷移率能夠有效的提升。在 比 較 不 同 CESL 應 力 層 厚 度 時 , 觀 察 到 當 CESL 層 厚 度 較 傳 統 CESL 層 厚 時 , 元件的驅動能力及轉移電導確實能夠有效提升,但也由於高應力的影響 下 造 成 了 閘 極 氧 化 層 缺 陷 (gate oxide defect)及 閘 極 氧 化 層 與 矽 基 板 界 面 缺 陷 ( o xide/Si interface defect)。 由 圖 3-2-1可 見 , 在 NMOS元 件 中 , 經 由 low frequency noise量 測 後 證 實 在 高 伸 張 應 力 CESL 層 對 元 件 造 成 了 閘 極 氧 化 層 缺 陷 及 閘 極 氧 化 層 與 矽 基 板 界 面 缺 陷 的 確 較 低 伸 張 應 力 CESL 層 來 得 高 ; 而 高 壓 縮 應 力 CESL 層 與 低 伸 張 應 力 CESL 層 對 元 件 所 造 成 的 閘 極 氧 化 層 缺 陷 及 閘 極 氧 化 層 與 矽 基 板 界 面 缺 陷 相 較 之 下 則 沒 有 太 大 的 差 異 , 見 圖 3-2-2。 我 們 針 對 相 同 的 元 件 進 行 飽 和 區 時 之 low frequency noise 量 測 , 其 結 果 可 見 圖 3-2-3 與 3-2-4。. 19.

(33) 3-3 電 荷 幫 浦 (Charge Pumping). 另 一 種 研 究 電 晶 體 界 面 狀 態 的 方 法 早 在 196 9 年 時 就 已 經 被 學 者 B r u g l a r 和 Jespers 所 提 出 了 , 最 主 要 是 依 據 電 子 電 洞 在 表 面 的 複 合 過 程 對 界 面 陷 阱 做 量 測 , 此 方 法 為 電 荷 幫 浦 (charge pumping) 的 方 式 【 6 3 ~ 6 4 】。 Bruglar和 Jespers二 位 學 者 還 發 現 若 在 閘 極 處 給 予 一 連 續 的 脈衝下,在矽基板將會有一淨電荷流動,研究結果認為主要是由於界面 陷阱中的少數載子與矽基板上的多數載子複合所引起的。. 3-3-1. C harge Pumping 基 本 原 理. C h a r ge Pumping 技 術 是 以 電 性 的 方 法 針 對 界 面 陷 阱 做 數 量 與 電 性 上 的 量 測 方 式 。 其 運 作 原 理 為 施 加 一 連 續 的 脈 衝 電 壓 (pulse voltage) 於 MOSFET之 閘 極 端 , 並 將 汲 極 與 源 極 接 地 , 另 外 在 基 板 外 接 一 電 流 計 。 我 們 將 這 一 連 續 脈 衝 電 壓 之 基 底 電 位 (Vbase) 設 在 低 於 電 晶 體 平 帶 電 壓 ( V F B ) 之 下,而 將 峰 值 電 位 (Vpe ak)設 在 電 晶 體 臨 限 電 壓 (V T )之 上,由 能 帶 圖 我 們 可 以 發 現 在 電 晶 體 矽 基 板 表 面 變 化 將 從 聚 積 (Accumulation)變 化 到 反 轉 ( Inversion) 最 後 又 回 到 聚 積 狀 態 , 正 好 為 一 個 脈 衝 週 期 , 見 圖 3-3-1。 以 一 N-type MOSFET為 例 , 當 閘 極 脈 衝 電 壓 由 基 底 電 位 慢 慢 升 高 至 峰 值 電 位 時 , 也 就 是 MOSFET 從 聚 積 狀 態 慢 慢 變 成 反 轉 狀 態 時 , 在 矽 基 板 表 面會有過渡變化發生,即通道表面之電洞會因為閘極的脈衝電壓而被排 離至基板流出,而在汲極與源極將會經由脈衝電壓吸引出電子流經通道 表 面 , 形 成 反 轉 層 , 在 這 樣 的 過 程 中 , 將 會 出 現 一 暫 態 電 流 I 1。 同 樣 地 , 當閘極之脈衝電壓由峰值電位慢慢降低到基底電位的同時,通道表面的. 20.

(34) 狀態將由反轉變成聚積狀態,導致原本在通道上的電子被迫回到汲極與 源極,而將矽基板的電洞又吸引到通道表面來,在這樣的過程中,一樣 也 會 有 另 一 暫 態 電 流 I2。 如果說在氧化層與矽基板之界面沒有任何的陷阱,而載子的速度又 可以跟的上脈衝信號的速度,那麼在一整個脈衝週期內,不應該會有淨 電 流 的 產 生 ; 因 為 I1將 會 等 於 I2。 反 之 , 若 存 有 界 面 陷 阱 , 那 麼 將 會 引 起一連串表面複合的現象發生;那麼基板將會有某些程度的電流出現。. 3-3-2. C harge Pumping 量 測 方 式 與 設 定. 一 般 而 言 , Charge Pumpi ng量 測 方 法 有 三 種 , 分 別 為 : (1)固 定 振 幅 ( F i x e d Amplitude) 的 方 式 ; 此 方 法 為 改 變 基 底 電 位 並 保 持 脈 衝 振 幅 固 定 , 使 元 件 從 反 轉 狀 態 慢 慢 變 成 聚 積 狀 態 , 藉 此 來 獲 得 汲 引 電 流 。 (2)固 定 基 底 電 位 (Fixed Base) 的 方 式 : 藉 著 固 定 脈 衝 電 壓 的 基 底 電 位 , 讓 矽 基板表面維持在積聚狀態,並且慢慢增加脈衝振幅,迫使矽基板表面漸 漸 變 成 反 轉 狀 態 , 藉 此 獲 得 汲 引 電 流 。 (3)固 定 峰 值 電 位 (Fixed Peak)的 方式:此方式與固定基底電位的方式相類似,藉由固定脈衝電壓的峰值 電位使得矽基板表面維持在反轉狀態,並改變脈衝振幅,迫使矽基板表 面慢慢轉變成聚積狀態,藉此獲得汲引電流。 此 外 , Charge Pumping 量 測 元 件 的 接 法 也 有 二 種 方 式 , 一 種 為 雙 端 電荷汲引的方式,另一種為單端電荷汲引的方式。雙端電荷汲引是將元 件 之 源 極 與 汲 極 均 接 地,將 脈 衝 電 壓 由 閘 極 注 入,並 在 基 極 接 上 電 流 表 , 利用基極汲引電流即可獲得整個通道界面陷阱密度。而單端電荷汲引的 方式則是將源極端浮接,而基極端接地,脈衝電壓由閘極注入,並從汲 極端量測汲引電流,藉此獲得整個通道界面陷阱密度。. 21.

(35) 圖 3 - 3-2 為 本 實 驗 基 本 的 量 測 裝 置 及 設 定 。 我 們 利 用 HP-81110A 脈 衝 產 生 器 來 產 生 1MHz 之 連 續 脈 衝 電 壓 , 並 將 之 施 加 於 MOSFET 閘 極 端 , 固 定 振 幅 在 1 V , 而 上 升 時 間 (Risin g Time)與 下 降 時 間 (Falling Time)均 設 為 80nsec, 並 採 用 雙 端 電 荷 汲 引 的 方 式 以 獲 得 整 個 通 道 界 面 陷 阱 密 度 。. 3-3-3. 實驗結果. 由 本 論 文 3-2節 我 們 已 經 知 道 經 由 高 應 力 應 變 機 制 的 影 響 下,將 會 造 成 元 件 閘 極 氧 化 層 與 氧 化 層 及 矽 基 板 界 面 之 缺 陷 產 生 ; 本 節 透 過 Charge Pumping 電 荷 汲 引 的 方 式 來 量 測 在 不 同 應 力 機 制 下 對 元 件 所 產 生 的 界 面 缺陷進行探討。 由 圖 3-4-1 可 見 高 應 力 元 件 在 氧 化 層 與 矽 基 板 之 界 面 造 成 較 高 的 電 荷 汲 引 電 流 ( I C P ), 另 外 我 們 將 之 代 入 下 式 : Nit =. ICP … … … … … … … … … … … … … … … … … … … … … … … … … (8) qAGf. 將 電 荷 汲 引 電 流 換 算 為 界 面 缺 陷 數 量 , 其 中 q為 基 本 電 荷 而 AG為 元 件 之 閘 極 面 積 , f 為 頻 率 , 其 N i t 換 算 結 果 可 見 圖 3-4-2, 而 Charge Pumping量 測 結 果 與 上 述 Flicker noise所 量 測 得 到 的 結 果 能 相 互 印 證 , 見 圖 3-4-2。. 22.

(36) 第四章 元件可靠度量測結果與分析. 隨著半導體製程技術不斷地演進,各種半導體元件的尺寸面積都不 斷的微縮、運作速度也不斷的加快,關於元件可靠性的研究領域,一直 扮演著極重要的角色。基於以往對元件可靠度的分析,本研究將把可靠 度 分 析 延 伸 到 具 有 高 、 低 應 力 應 變 元 件 上 , 並 對 N-/P-MOSFET進 行 可 靠 度 的探討。. 4-1 元 件 退 化 機 制. M O S FET 元 件 特 性 的 退 化 是 由 缺 陷 產 生 所 造 成 的 , 而 造 成 缺 陷 的 原 因 除了材料本身製作時所產生的,另外還有電子以及電洞的注入所引起, 由於此二種載子的注入所造成的電子補捉陷阱與電洞補捉陷阱和界面缺 陷將會分別對元件產生不同的影響,導致元件有不同的電性表現。界面 陷阱的產生需要電子與電洞同時作用形成,電洞先注入氧化層處,電子 隨後注入中和電洞,造成缺陷轉移到氧化層與矽基板界面處,形成所謂 的 i n t e r face states 。 另 外 一 種 缺 陷 是 由 衝 擊 游 離 所 造 成 的 , 此 缺 陷 在 橫 向 電 場 夠 強 時 會 發 生 , 橫 向 電 場 賦 予 電 子 足 夠 的 能 量 時 (超 過 1.4eV), 電子便會在接近汲極端處撞擊出電子電洞對,這些擁有高能量的載子被 通稱為熱載子,一旦被撞擊出的電子被閘極或汲極的正電壓所吸引後, 將會成為閘極或汲極電流的一部份,而電洞被基板吸收後,將變成基板 電流的主要來源。 熱 載 子 的 能 量 如 果 超 過 矽 的 鍵 結 力 1 . 4 e V, 便 會 經 由 衝 擊 離 子 化 的 效 應在汲極端撞擊出電子電洞對,造成基板電流或載子注入汲極端的閘氧 化層,將對元件造成破壞性。如果載子能量更高,將有可能跨越閘氧化 23.

(37) 層的能障,造成界面陷阱,使元件特性退化更多。相關的熱載子引起退 化 與 可 靠 度 可 見 文 獻 【 3 0 、 3 8 、 82~87 】。 近 年 來 有 關 負 偏 壓 溫 度 的 不 穩 定 性 ( N B TI)也 常 被 用 來 探 討 元 件 之 可 靠 度 ; NBTI是 在 1995年 由 學 者 Ogaw a 以 電 化 學 式 子 所 描 述 元 件 在 負 偏 壓 溫 度 下 發 生 的 機 制 【 88】。 之 後 , 此 說 法 逐 漸 被 說 成 所 謂 的 矽 表 面 斷 鍵 反 應 -氫 粒 子 漂 移 模 型 。 有 關 NBTI引 起 退 化 與 可 靠 度 可 見 文 獻 【 3 0 、 3 8、 89~98】。 負 偏 壓 不 穩 定 性 主 要 是 針 對 PMOSFET元 件 閘 極 操 作 在 負 偏 壓 , 其 在 高 溫度的環境下隨著時間的增加,界面陷阱與固定氧化層陷阱亦隨之增 加 ; 由 於 NBTI 所 造 成 元 件 退 化 的 程 度 會 隨 元 件 尺 寸 不 斷 的 微 縮 而 增 加 , 因 此 元 件 的 生 命 週 期 將 是 由 NB TI來 主 宰 。. 4-2 可 靠 度 實 驗 設 計. 本 論 文 中 , 我 們 將 對 元 件 進 行 的 退 化 機 制 有 二 種 型 式 :( 1 ) 元 件 作 用 在 閘 極 與 汲 極 同 時 給 予 高 電 場 逼 迫 下 引 致 熱 載 子 效 應 (Hot-carrier e f f e c t ) ;( 2 ) 另 一 種 型 式 為 僅 針 對 閘 極 給 予 高 電 場 進 行 電 性 逼 迫 之 正 / 負 偏 壓 不 穩 定 性 (Positive / Negative Bias Instability, P/NBI)。 圖 4 - 2-1為 本 電 性 逼 迫 實 驗 之 流 程 圖 , 圖 4-2-2為 閘 極 端 給 予 正 /負 偏 壓 條 件 並 在 室 溫 下 進 行 正 /負 偏 壓 不 穩 定 性 可 靠 度 量 測 ; 此 外 , 我 們 也 對 元 件 閘 極 與 汲 極 同 時 給 予 正 /負 偏 壓 在 室 溫 下 進 行 熱 載 子 可 靠 度 量 測,見 圖 4-2-3。. 24.

(38) 4-3 實 驗 結 果 分 析. 4-3-1. H ot-Carrier Stressi ng 實 驗 結 果. 從先前的文獻我們可以得知短通道元件其熱載子退化最嚴重的情況 是 發 生 在 閘 極 電 壓 (Vg) 等 於 汲 極 電 壓 (Vd) 時 , 因 此 我 們 將 H o t - C a r r i e r S t r e s s 的 條 件 設 在 閘 極 電 壓 等 於 汲 極 電 壓 等 於 臨 限 電 壓 +1V 進 行 電 性 逼 迫 , 見 圖 4-2-3。 圖 4 -3-1-1 是 90nm BC-SOI NMOSFET 在 不 同 CESL 應 力 層 下 stress 條 件 在 閘 極 與 汲 極 電 壓 操 作 在 臨 限 電 壓 + 1V 下 1 0 0 分 鐘 前 後 汲 極 電 流 對 汲 極 電 壓 的 關 係 圖 , 經 過 100 分 鐘 的 stress 之 後 , 元 件 的 汲 極 飽 和 電 流 Idsat 出 現 明 顯 的 退 化 , High Tensile device經 過 100分 鐘 stress後 其 Idsat退 化 了 9 4 ( u A /um) 較 Low Tensile d evice 退 化 了 54(uA/um) 來 得 多 , 此 外 我 們 可 以 發 現 到 在 線 性 區 的 汲 極 電 流 改 變 了 , 這 是 因 為 stress 後 interface states 的 增 加 導 致 載 子 遷 移 率 降 低 而 引 起 串 聯 電 阻 升 高 所 致 。 由 圖 4 - 3 - 1 - 2 轉 移 電 導 (Gm)對 閘 極 電 壓 (Vg)的 關 係 圖 , 由 此 圖 我 們 亦 可 見 Hig h T e n s i l e device 之 Gm 峰 值 退 化 量 也 較 Low Tensile device 退 化 量 還 要 來 得 高 , 而 G m 峰 值 的 代 表 意 義 是 Id-Vg圖 形 中 臨 界 區 的 最 大 斜 率 , 這 個 值 的 下降也代表著次臨界區的最大斜率降低,同時也能夠反應出元件遷移率 的 降 低 , 這 乃 是 由 於 界 面 狀 態 產 生 所 造 成 的 。 圖 4-3-1-3 是 90nm BC-SOI N M O S F E T 在 不 同 C E S L 應 力 層 下 stress 條 件 在 閘 極 與 汲 極 電 壓 操 作 在 臨 限 電 壓 +1V 下 100 分 鐘 前 後 汲 極 電 流 對 閘 極 電 壓 的 關 係 圖 , 經 過 1 0 0 分 鐘 的 stress之 後 , 可 見 到 圖 形 之 斜 率 變 化 以 及 向 右 移 動 的 趨 勢 , 我 們 認 為 這 是 因 為 i n terface states 增 加 與 電 荷 注 入 氧 化 層 造 成 氧 化 層 缺 陷 的 結 果 , stress 後 因 為 熱 載 子 效 應 所 造 成 的 interface states 與 電 子 注 入 的. 25.

數據

相關文件

Due to larger declines in prices in men’s and women’s clothing and footwear, in house renovations and in outbound package tours, in order to promote this kind of tours, the indices of

exegetes, retrospectively known as the Shan-chia and the Shan-wai. In this essay I argue that one especially useful way of coming to understand what was truly at stake in

maintenance and repair works should be carried out by school and her maintenance agent(s) to rectify defect(s) as identified in routine and regular inspections. Examples of works

To reduce the leakage current related higher power consumption in highly integrated circuit and overcome the physical thickness limitation of silicon dioxide, the conventional SiO

To reduce the leakage current related higher power consumption in highly integrated circuit and overcome the physical thickness limitation of silicon dioxide, the conventional SiO 2

If the resulting image is a blank image, it means that the test image is free of defects; otherwise, any thing left in the image is regarded as a defect.. In the research, we

This research tries to understand the current situation of supplementary education of junior high school in Taichung City and investigate the learning factors and

This purpose of study was to realize, as well as the factors of influence of information technology integrated in teaching by junior high school special education teachers in