國立高雄大學 電機工程學系碩士在職專班

碩士論文

平面縮小化與濾波型跨接耦合器設計

Design of Planar Miniaturized and Filtering Crossovers

研究生:吳銘麟 撰

指導教授:龎一心 博士

致謝

不知不覺,研究所的生活已到尾聲,這三年來,工作、學業兩頭燒的生活雖然很累,但 我非常高興能完成我想做的事。還記得第一次發表論文(也是到目前惟一一次),第一次用英 文作口頭報告,非常緊張,也因為準備不足而報得不好,但因為這次經驗,讓我的報告技巧 長進不少,這算是一次非常不錯的經歷。 在研究所的生涯,要感謝很多人,首先是要感謝我的父母,允許我留在台灣,做我想做 的事情。然後是公司的上司,常常幫我擋下各種事情,讓我有時間去學校上課,也允許我常 常早退去處理學業上的事情。接著是龎老師,感謝從大學到現在的指導,也感激就算我的東 西拖到最後一刻才寄出,也會仔細地幫我修改。最後要謝謝205-1 實驗室的伙伴們,雖然我 沒有很常去實驗室,但仍謝謝各位在這三年來的協助,很高興能成為205-1 實驗室的一份 子!平面縮小化與濾波型跨接耦合器設計

指導教授:龎一心 博士 國立高雄大學電機工程學系 學生:吳銘麟 國立高雄大學電機工程學系碩士在職專班 摘要 本論文目的為提出平面小型化跨接耦合器設計,共有兩種類型。第一種是利用雙傳輸線 實現的小型化跨接耦合器,另一種則是運用耦合共振腔理論設計的濾波型跨接耦合器。 第一種電路為由兩個枝幹線耦合器組成的4-Port 平面跨接耦合器,並應用雙傳輸線設計 來進行電路縮小化。雙傳輸線由兩條平行的高阻抗但不同電氣長度的傳輸線所組成,將原本 的單傳輸線換成等效雙傳輸線,將有利於電路佈局,增加基板使用率,減少電路的面積。與 未經過縮小化之由兩個枝幹線耦合器組成的平面跨接耦合器比較,可減少21%的面積。 第二種電路為由耦合共振腔所組成的4-Port 濾波璀跨接耦合器,在奇、偶模態分析時, 耦合共振腔作為帶通濾波器,但通過共振腔的訊號會有180°的相位差,從而形成一跨接耦合 器。此電路可取代一個跨接耦合器及與其4 個 Port 連接的 4 個帶通濾波器,達到節省空間 的目的。除此之外,此設計容易發展成多階的設計。 關鍵字:枝幹線耦合器、縮小化跨接耦合器、雙傳輸線、濾波型跨接耦合器、耦合共振腔Design of Planar Miniaturized and Filtering Crossovers

Advisor: Dr. Yi-Hsin Pang Department of Electrical Engineering

National University of Kaohsiung

Student: Ming-Lun Ng

Department of Electrical Engineering National University of Kaohsiung

ABSTRACT

The main purpose of this thesis is to propose planar crossovers of reduced size. Two kinds of circuit will be presented. One is a miniaturized planar crossover utilizing dual transmission lines, and the others are filtering crossovers designed by coupled resonator theory.

The first kind of circuit is a miniaturized four-Port crossover consisting of two cascaded branch-line couplers implemented by dual transmission lines. A dual transmission line is composed of two parallel-connected transmission lines with high impedance and different electrical lengths. It has the advantage of circuit layout flexibility and size reduction by replacing each single

transmission line with the equivalent dual transmission line. The electrical size is 21% reduced comparing with the size of a crossover utilized with two cascaded branch-line couplers.

The second kind of circuit is a four-Port crossover with filtering property consisting of coupled resonators. In even-odd modes analysis, the coupled resonators perform as band-pass filters but the

signals passed through the resonators will have phase difference of 180°. Hence, a crossover is obtained. This circuit can replace a crossover and 4 filters connecting at the 4 Ports of crossover in purpose of reducing area. Moreover, the proposed structure can be extended to multiple orders design easily.

Keywords: branch-line couplers, miniaturized crossover, dual transmission line, filtering crossover, coupled resonators

目錄

第一章 導論 ... 1 1.1 研究動機 ... 1 1.2 甚麼是跨接耦合器 (Crossover)? ... 1 1.3 文獻探討 ... 1 1.4 章節介紹 ... 2 第二章 以雙傳輸線設計縮小化平面跨接耦合器 ... 4 2.1 雙傳輸線介紹 ... 4 2.2 設計原理 ... 4 2.2.1 平面跨接耦合器結構 ... 4 2.3 電路模擬 ... 7 2.3.1 雙傳輸線參數計算 ... 7 2.3.2 縮小化前與縮小化後之電路模擬比較 ... 7 2.4 電磁模擬與實作 ... 10 第三章 以耦合共振腔原理設計二階濾波型平面跨接耦合器 ... 13 3.1 濾波型平面跨接耦合器簡介 ... 13 3.2 濾波型平面跨接耦合器設計原理 ... 13 3.3 電路模擬 ... 16 3.4 電磁模擬與實作 ... 19 第四章 以多個耦合共振腔設計多階濾波型平面跨接耦合器 ... 26 4.1 設計原理 ... 26 4.2 電路模擬 ... 264.3 電磁模擬與實作 ... 29 第五章 結論 ... 41 參考文獻 ... 42

圖目錄

圖 1. 1 跨接耦合器電路模型圖 ... 1 圖2. 1 使用枝幹線耦合器傳輸相位特性設計之平面跨接耦合器的設計原理[5] ... 5 圖 2. 2 縮小化前之平面跨接耦合器電路圖 ... 5 圖2. 3 以雙傳輸線設計縮小化後之平面跨接耦合器電路圖 ... 6 圖2. 4 一條傳輸線及與其等效之電路模型圖[7] ... 6 圖2. 5 以理想傳輸線設計之縮小化前平面跨接耦合器電路圖 ... 8 圖2. 6 以理想傳輸線設計之縮小化前平面跨接耦合器頻率響應 ... 8 圖2. 7 以理想傳輸線設計之雙傳輸線設計平面跨接耦合器電路圖 ... 9 圖2. 8 以理想傳輸線設計之雙傳輸線設計平面跨接耦合器頻率響應 ... 9 圖2. 9 雙傳輸線設計平面跨接耦合器電路佈局 ... 10 圖2. 10 以雙傳輸線設計縮小化後之電路圖 ... 11 圖2. 11 雙傳輸線設計平面跨接耦合器之模擬與量測的 S11與S31 ... 11 圖2. 12 雙傳輸線設計平面跨接耦合器之模擬與量測的 S21 ... 12 圖2. 13 雙傳輸線設計平面跨接耦合器之模擬與量測的 S41 ... 12 圖3. 1 以濾波型跨接耦合器取代傳統跨接耦合器與濾波器之應用的示意圖 ... 13 圖3. 2 以 TT'作為對稱平面的 4-Port 耦合器 ... 13 圖3. 3 二階 4-Port 對稱耦合器之耦合情況 (a)偶模態 (b)奇模態 ... 14 圖3. 4 濾波形跨接耦合器的原始架構 ... 15 圖3. 5 以導納轉換器模擬二階帶通濾波器的半電路 (a)偶模態 (b)奇模態 ... 16 圖3. 6 以導納轉換器模擬二階帶通濾波器的半電路之頻率響應 (a)偶模態 (b)奇模態 (c)奇、 偶模態的相位差 ... 18 圖3. 7 二階 4-Port 跨接耦合器之電路模擬結果 ... 18 圖3. 8 共振腔之電路佈局 ... 19圖3. 9 弱耦合饋入下,共振腔之奇、偶模態穿透係數 ... 20 圖3. 10 兩個共振腔之電路佈局與尺寸 ... 21 圖3. 11 弱耦合饋入下,兩共振腔電路之奇、偶模態穿透係數 ... 21 圖3. 12 弱耦合饋入下,兩共振腔電路之奇、偶模態穿透係數相位差 ... 22 圖3. 13 二階濾波型跨接耦合器之饋入位置 ... 22 圖3. 14 共振腔之奇、偶模態在不同頻率之外部阻抗 ... 23 圖3. 15 二階濾波型平面跨接耦合器電路佈局 ... 23 圖3. 16 二階濾波型平面跨接耦合器電路圖 ... 24 圖3. 17 二階濾波型平面跨接耦合器之模擬與量測的 S11與S31 ... 24 圖3. 18 二階濾波型平面跨接耦合器之模擬與量測的 S21 ... 25 圖3. 19 二階濾波型平面跨接耦合器之模擬與量測的 S41 ... 25 圖4. 1 四階 4-Port 對稱耦合器之耦合情況 (a)偶模態 (b)奇模態 ... 26 圖4. 2 以導納轉換器模擬四階帶通濾波器的半電路 (a)偶模態 (b)奇模態 ... 27 圖4. 3 以導納轉換器模擬四階帶通濾波器的半電路之頻率響應 (a)偶模態 (b)奇模態 (c)奇、 偶模態的相位差 ... 28 圖4. 4 四階 4-Port 跨接耦合器之電路模擬結果 ... 29 圖4. 5 第 2、第 3 個共振腔之電路佈局與尺寸 ... 30 圖4. 6 弱耦合饋入下,第 2、第 3 個共振腔之奇、偶模態穿透係數 ... 31 圖4. 7 第 1、第 2 個共振腔之電路佈局與尺寸 ... 31 圖4. 8 弱耦合饋入下,第 1、第 2 個共振腔之奇偶模態穿透係數 ... 32 圖4. 9 訊號通過第 1、2 個共振腔後奇、偶模態的相位差 ... 32 圖4. 10 訊號通過第 2、3 個共振腔後奇、偶模態的相位差 ... 33 圖4. 11 訊號通過第 3、4 個共振腔後奇、偶模態的相位差 ... 33 圖4. 12 四階濾波型跨接耦合器之饋入位置 ... 34 圖4. 13 共振腔之奇、偶模態在不同頻率之外部阻抗 ... 34

圖4. 14 四階濾波型跨接耦合器電路佈局 ... 35 圖4. 15 四階濾波型平面跨接耦合器的頻率響應 (電磁模擬) ... 36 圖4. 16 四階濾波型平面跨接耦合器奇、偶模態的頻率響應 (電磁模擬) ... 36 圖4. 17 調整後之四階濾波型平面跨接耦合器電路佈局及尺寸 ... 37 圖4. 18 四階濾波型平面跨接耦合器電磁模擬結果 ... 38 圖4. 19 四階濾波型平面跨接耦合器電路圖 ... 38 圖4. 20 四階濾波型平面跨接耦合器之模擬與量測的 S11與S31 ... 39 圖4. 21 四階濾波型平面跨接耦合器之模擬與量測的 S21 ... 39 圖4. 22 四階濾波型平面跨接耦合器之模擬與量測的 S41 ... 40

表目錄

表2. 1 雙傳輸線縮小化平面跨接耦合器之電路參數值... 7 表3. 1 二階帶通濾波器半電路參數值... 17 表3. 2 二階濾波器之規格與對應的參數值... 19 表4. 1 四階帶通濾波器電路參數值... 27 表4. 2 四階濾波器之規格與對應的參數值... 29第一章 導論

1.1 研究動機

現今的科技發展愈來愈快,產品講求多功能,使得電路的體積愈來愈小,才能在有限的 空間內放入更多的電路。因此,電路設計縮小化被廣泛討論,濾波器、功率分配器、天線等 射頻電路之縮小化,都有大量的文獻可以參考。本論文考量通訊元件中的跨接耦合器 (Crossover),提出一個以雙傳輸線設計的縮小化跨接耦合器,以及一個結合濾波器的濾波型 跨接耦合器模組電路,達到節省空間的目的。1.2 甚麼是跨接耦合器 (Crossover)?

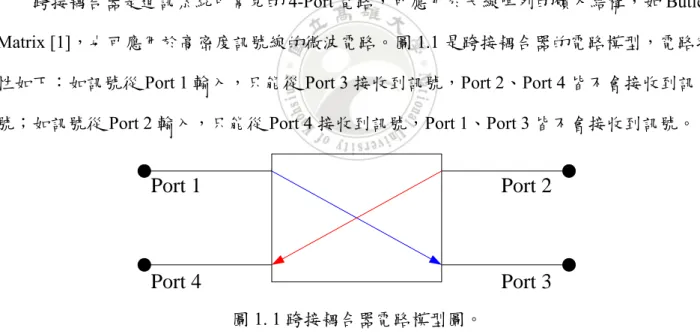

跨接耦合器是通訊系統中常見的4-Port 電路,可應用於天線陣列的饋入結構,如 Butler Matrix [1],也可應用於高密度訊號線的微波電路。圖 1.1 是跨接耦合器的電路模型,電路特 性如下:如訊號從Port 1 輸入,只能從 Port 3 接收到訊號,Port 2、Port 4 皆不會接收到訊 號;如訊號從Port 2 輸入,只能從 Port 4 接收到訊號,Port 1、Port 3 皆不會接收到訊號。圖1. 1 跨接耦合器電路模型圖。 以前人們是以「天橋」的方式來製作跨接耦合器,但是這種電路需要第三維空間,為節省空 間,平面跨接耦合器被提出。

1.3 文獻探討

在1976 年,J. S. Wight 等人提出了以兩個帶線或微帶線枝幹線耦合器組成的平面跨接耦 合器[2],自此,平面跨接耦合器被廣泛地討論,不少文獻都是以此架構作為設計基礎,加 以改良。在[3]中,Y. Che 等人提出了一個雙環狀平面對稱跨接耦合器,此設計具有 20%頻Port 1

Port 4

Port 3

Port 2

寬 (0.92 GHz 到 1.12 GHz)。Y.-C. Chiou 等人則在[4]提出了一單環狀設計的平面對稱跨接耦 合器,環內以垂直線連接對稱的Ports,此設計與[3]中的雙環狀設計相比,結構上較簡單, 也易於計算分析。在[5]中,Z.-W. Lee 等人以[2]所提出的微帶線枝幹線耦合器組成的平面跨 接耦合器為基礎,加上開路短線(Open stubs),組成一個雙頻平面跨接耦合器。F. Lin 等人在 [6]中提出了首個可調式跨接耦合器,以兩段式耦合線及可變電容組成[2]所提出的平面跨接 耦合器,使其操作頻率可以調整(1.2 GHz 到 2.4 GHz)。以上之文獻提出了各種跨接耦合器的 設計,各個設計都有其特別之處,但是,這些電路的體積大多都不小。 針對電路縮小化這個議題,C.-W. Teng 等人以及 C.-H. Lu 等人分別把雙傳輸線設計應用 在枝幹線耦合器[7]以及功率分配器[8]上並有效地減少電路體積,但這設計目前還沒有嘗試 用在跨接耦合器上。除了個別電路的縮小化外,也有不少文獻提出以兼具兩種電路特性的電 路模組來取化多個電路做法,以達到節省空間的目的,目前的作法大多為讓某種電路兼具濾 波特性為主。在[9]中,J.-Y Shao 提出了一個帶有四階類橢圓濾波器特性的威爾金森功率分 配器,以耦合共振腔組成。一個以耦合線來組成的具有高隔離特性的濾波型威爾金森功率分 配器,則為P.-H. Deng 等人的研究[10]。也有具有濾波特性的跨接耦合器的研究,X.-Y. Zhang 等人在[11]提出以環形短線負載共振腔(Stub-Loaded Ring Resonator)組成的濾波形跨接 耦合器,但這種設計難以發展成多階的形式。 本論文提出了兩個不同的跨接耦合器架構─縮小化跨接耦合器及濾波型跨接耦合器,這 兩個架構的目的皆為節省空間,但它們節省空間的形式並不相同。前者是針對單一電路作縮 小化設計;後者則是以一個電路取代多個電路。在上述的文獻探討有提到,雙傳輸線的縮小 化設計並未曾應用於跨接耦合器上,因此,本論文提出了一個以雙傳輸線設計的縮小化跨接 耦合器;至於濾波型跨接耦合器,本論文利用耦合共振腔理論,提出一個計算簡單,易於發 展成多階電路的架構。

1.4 章節介紹

本論文共分為五章,第一章為緒論,簡述研究動機,何謂跨接耦合器,探討現有的文獻並訂定研究方向。第二章的主題為以雙傳輸線設計縮小化平面跨接耦合器,把雙傳輸線設計 應用在跨接耦合器上,以達到電路縮小化的目的,闡述設計原理、模擬過程、量測結果以及 縮小的效果。第三章的主題是以耦合共振腔原理設計二階濾波型跨接耦合器,先以電路模擬 驗證可行性,接著進行電磁模擬、實作,並比較模擬與量測結果之差異。第四章為第三章的 延伸,把二階濾波型跨接耦合器發展成四階濾波型跨接耦合器,先提出理論與限制,再以電 路模擬驗證其可行性,接著進行電磁模擬與闡述在設計時所遇到之問題和解決方式,最後製 作電路,比較模擬與量測結果。最後,在第五章會針對本論文所提出的兩種電路作結論。

第二章 以雙傳輸線設計縮小化平面跨接耦合器

2.1 雙傳輸線介紹

雙傳輸線是一種以兩條高阻抗傳輸線取代一條低阻抗傳輸線,以方便電路佈局 (Layout),增加電路板單位面積的使用率,使電路總面積減少的一種縮小化概念。此概念有 別於其他的縮小化理論,以兩條高阻抗線取代一條低阻抗線的方式逐一變換,縮小化前與縮 小化後的電路架構基本上是不變的,理論上縮小化後的電路的頻寬不會受到影響,與縮小化 前的頻寬是一樣的。2.2 設計原理

2.2.1 平面跨接耦合器結構 平面跨接耦合器的結構有很多種,本文選用的是由兩個枝幹線耦合器組成[2]。根據枝 幹線耦合器的傳輸相位特性,兩個枝幹線耦合器便能組成一個跨接耦合器。如圖2.1 所示, 訊號從Port 1 進入,通過第 1 個枝幹線耦合器到達 Port A 及 Port B 時,兩個 Port 接收到的 訊號相差90°,Port 4 則為隔離埠 (Isolation Port)(枝幹線耦合器之特性),不會接收到訊號; 而當訊號通過第2 個枝幹線耦合器後,Port 3 能接收到來自 Port A 和 B 同相位的訊號,Port 2 會接收到相位差為 180°的訊號而互相相消,Port A 與 Port B 則互為隔離埠。由此可得,訊 號從Port 1 進入,通過兩個枝幹線耦合器後,只有 Port 3 能收到訊號,此為跨接耦合器之特 性[5]。Port 1 Port A Port 4 Port B 枝幹線耦合器1 0° -90° Port 2 Port 3 -180° Port 2 Port 3 -360° Port A Port B 枝幹線耦合器2 枝幹線耦合器2 Isolation Isolation -270° -90° -270° -180° -180° Isolation 圖2. 1 使用枝幹線耦合器傳輸相位特性設計之平面跨接耦合器的設計原理[5]。 2.2.2 以雙傳轉線設計縮小化之原理及計算方式 章節2.1 有提到雙傳輸線設計是以兩條高阻抗線取代一條低阻抗線,所以,決定了平面 跨接耦合器的結構後,便能進行替換的步驟。圖2.2 為縮小化前的平面跨接耦合器電路圖, 圖中Z0 = 50 Ω、θ0 = 90°,圖 2.3 則為以圖 2.2 的結構為基楚,應用雙傳輸線設計後之縮小 化跨接耦合器的電路圖,圖中Zn為各傳輸線的特徵阻抗,θn1、θn2則為電氣長度,n = 1, 2, 3。圖 2.4 為以雙傳輸線等效一條傳輸線(特徵阻抗為 Z0,電氣長度為θ0 = 90°)的電路 模型圖,圖中Zn是傳輸線的特徵阻抗,θn1、θn2則為電氣長度,以此方式把圖2.2 中的每 一條傳輸線等效成雙傳輸線,便能得到圖2.3 所示的電路圖。 Port 1 Port 2 Port 3 Port 4 圖 2. 2 縮小化前之平面跨接耦合器電路圖。

Port 1 Port 4 Port 3 Port 2 圖2. 3 以雙傳輸線設計縮小化後之平面跨接耦合器電路圖。

Port 1

Port 2

Port 1

Port 2

等效

圖2. 4 一條傳輸線及與其等效之電路模型圖[7]。 根據[7]分析方式,(2.1)是特徵阻抗 Z0、四分之一波長傳輸線的ABCD 矩陣,(2.2)、(2.3)則 是組成雙傳輸線設計的兩條線各自的ABCD 矩陣(Yn = 1/Zn為各線段特徵導納): [𝐴 𝐵 𝐶 𝐷] = [ 0 𝑗𝑍0 𝑗𝑌0 0 ] (2.1) [𝐴𝐶1 𝐵1 1 𝐷1] = [ cos 𝜃𝑛1 𝑗𝑍𝑛sin 𝜃𝑛1 𝑗𝑌𝑛sin 𝜃𝑛1 cos 𝜃𝑛1 ] (2.2) [𝐴𝐶2 𝐵2 2 𝐷2] = [ cos 𝜃𝑛2 𝑗𝑍𝑛sin 𝜃𝑛2 𝑗𝑌𝑛sin 𝜃𝑛2 cos 𝜃𝑛2 ] (2.3) 而四分之一波長傳輸線的Y 矩陣會等於雙傳輸線的 Y 矩陣相加,利用 Y 矩陣和 ABCD 矩陣 之間的轉換式[12],可得(2.4)[

𝐷 𝐵 𝐵𝐶−𝐴𝐷 𝐵 −1 𝐵 𝐴 𝐵]

=

[

𝐷1 𝐵1+

𝐷2 𝐵2 𝐵1𝐶1−𝐴1𝐷1 𝐵1+

𝐵2𝐶2−𝐴2𝐷2 𝐵2 −1 𝐵1−

1 𝐵2 𝐴1 𝐵1+

𝐴2 𝐵2]

(2.4)根據(2.4)可得到 A=𝐴1𝐵2+ 𝐴2𝐵1 𝐵1+ 𝐵2 (2.5) B= 𝐵1𝐵2 𝐵1+ 𝐵2 (2.6) C=(𝐴2− 𝐴1)(𝐷1−𝐷2) + (𝐵1−𝐵2)(𝐶1− 𝐶2) 𝐵1+ 𝐵2 (2.7) D=𝐷1𝐵2+ 𝐷2𝐵1 𝐵1+ 𝐵2 (2.8) 把(2.1) – (2.3)代入(2.5)和(2.6),並取最小電氣長度,可得到:

θn1 + θn2 = 180° (2.9) Zn = 2Z0cscθn1 (2.10) 選取適當Zn,根據上述兩條算式便可算出圖2.3 之平面跨接耦合器的各個參數值。

2.3 電路模擬

2.3.1 雙傳輸線參數計算 本章節所設計的平面跨接耦合器操作頻率為2.5 GHz,使用在 50 Ω 的系統(Z0 = 50 Ω)。 根據(2.10)及(2.11),圖 2.3 的各個參數如表 2.1 所示: 表2. 1 雙傳輸線縮小化平面跨接耦合器之電路參數值 2.3.2 縮小化前與縮小化後之電路模擬比較 本論文之電路模擬皆使用Agilent ADS 電路模擬軟體來完成。圖 2.5 為縮小化前的平面 n Zn θn1 θn2 1 101.54 Ω 80° 100° 2 100 Ω 45° 135° 3 53.21 Ω 70° 110°跨接耦合器電路模型,以理想傳輸線組成,操作頻率為2.5 GHz,連接 50 Ω 的負載。 Port 4 Port 1 Port 3 Port 2 圖2. 5 以理想傳輸線設計之縮小化前平面跨接耦合器電路圖。 圖2.6 為其頻率響應,從這張圖可得出這個平面跨接耦合器的-3 dB 頻寬為 42.08%。 圖2. 6 以理想傳輸線設計之縮小化前平面跨接耦合器頻率響應。 圖2.7 則是以雙傳輸線設計平面跨接耦合器電路模型,為了保持電路的左右對稱性,電路正 中間的傳輸線以雙傳輸線替換後,較長的一條會再以兩條兩倍阻抗的並聯傳輸線取代。 -50 -40 -30 -20 -10 0 0.5 1.5 2.5 3.5 4.5 大小 (dB ) 頻率 (GHz) S11 S21 S31 S41

Port 1 Port 4 Port 3 Port 2 圖2. 7 以理想傳輸線設計之雙傳輸線設計平面跨接耦合器電路圖。 圖2.8 為其頻率響應,中心頻率 S31 = 0 dB,S11、S21與S41皆為零,由此可見,以雙傳 輸線設計縮小化後的電路依然有跨接耦合器之特性。除此之外,從這張圖也可得知這個設計 的-3 dB 頻寬為 36.68%,頻寬只比縮小化前窄了 5.4%。雖然沒法達到頻寬完全不減少,但 與其他結構相比,是相對比較理想的[13]。因此,雙傳輸線設計應可有效減少電路的尺寸並 維持原有的頻寬。 圖2. 8 以理想傳輸線設計之雙傳輸線設計平面跨接耦合器頻率響應。 -50 -40 -30 -20 -10 0 0.5 1.5 2.5 3.5 4.5 大小 (dB ) 頻率 (GHz) S11 S21 S31 S41

2.4 電磁模擬與實作

本次實作是透過Agilent ADS 中內建的 Momentum 電磁全波分析軟體把章節 2.3 所計算 出來的參數轉換成實際電路的電路佈局,先進行電磁模擬加以分析,再透過化學顯影蝕刻實 作電路。圖2.9 為電路佈局,從此圖可看出電路的長寬為各組雙傳輸線中較短的線的尺寸, 而比較長的線可透過轉折的方式利用電路板的其他空間來達到所需的電氣長度。

圖2. 9 雙傳輸線設計平面跨接耦合器電路佈局。

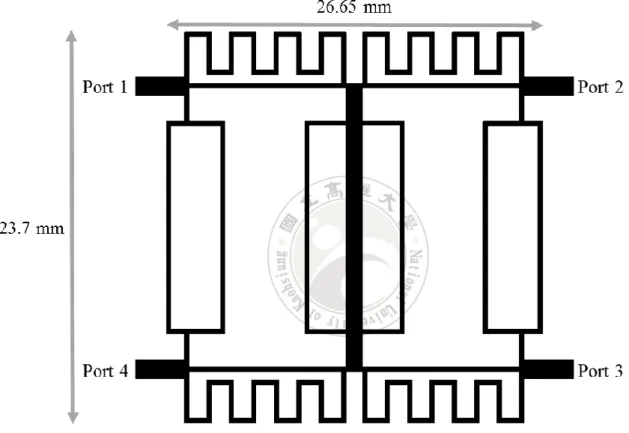

這次實作使用的基板為 Roger RO4003C,基板厚度為 0.508 mm,介電常數為 3.55,loss tangent 為 0.0027。圖 2.10 為實作電路圖,電路的尺寸為 23.7 mm x 26.65 mm,與縮小化前 (圖 2.2 之架構)相比,其面積減少了 21%。

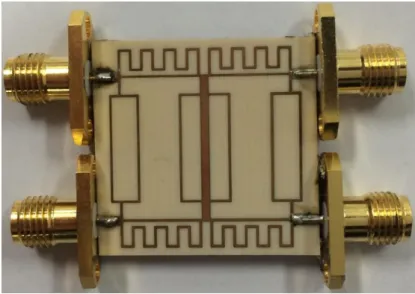

圖2. 10 以雙傳輸線設計縮小化後之電路圖。 電路製作完成後,使用Agilent E5071C 向量網路分析儀量測其從 0.5 GHz 到 4.5 GHz 實際的 頻率響應。圖2.11 為模擬與量測的 S11及S31結果,從這張圖可看出,電路的中心頻率從 2.5 GHz 偏移到 2.46 GHz,此現象應是因為實際基板特性的誤差所造成。在中心頻率,S11的 量測值為-21.9 dB,S31的量測值為-0.88 dB,而-3 dB 頻寬則為 28.9%,比以理想傳輸線設計 之36.68%僅減少了 7.78%,考慮到實際製作電路板所存在的各種誤差,此減少的幅度應是 在可接受的範圍。 圖2. 11 雙傳輸線設計平面跨接耦合器之模擬與量測的 S11與S31。 -40 -30 -20 -10 0 0.5 1.5 2.5 3.5 4.5 大小 (dB ) 頻率 (GHz) 模擬 S11 量測 S11 模擬 S31 量測 S31

S

31S

11圖2.12 及圖 2.13 分別表示了 S21與S41的模擬和量測結果。從2.26 GHz 到 2.61 GHz,S21的 量測值均小於-20 dB,而 S41則在2.46 GHz 到 2.54 GHz 小於-20 dB。 圖2. 12 雙傳輸線設計平面跨接耦合器之模擬與量測的 S21。 圖2. 13 雙傳輸線設計平面跨接耦合器之模擬與量測的 S41。 綜合以上結果,實作的電路具有平面跨接耦合器之特性,與傳統的雙枝幹線耦合器組成 之平面跨接耦合器相比,面積有減少,頻寬的影響也在可接受之範圍內。 -40 -30 -20 -10 0 0.5 1.5 2.5 3.5 4.5 大小 (dB ) 頻率 (GHz) 模擬 S21 量測 S21 -40 -30 -20 -10 0 0.5 1.5 2.5 3.5 4.5 大小 (dB ) 頻率 (GHz) 模擬 S41 量測 S41

第三章 以耦合共振腔原理設計二階濾波型平面跨接耦合器

3.1 濾波型平面跨接耦合器簡介

濾波器與跨接耦合器都是通訊系統常用的元件。使用到這兩種元件時,一般都是在跨接 耦合器的4 個 Port 接上濾波器,如此的使用方式一共需要 3 個電路來完成,浪費不少空 間。此章節所提出的電路,則是同時具備濾波器與跨接耦合器的特性,以1 個電路完成原本 需要3 個電路才能完成的事情,如圖 3.1 所示。 傳統跨接耦合器 帶通濾 波器 帶通濾 波器 濾波型跨接耦合器 圖3. 1 以濾波型跨接耦合器取代傳統跨接耦合器與濾波器之應用的示意圖。3.2 濾波型平面跨接耦合器設計原理

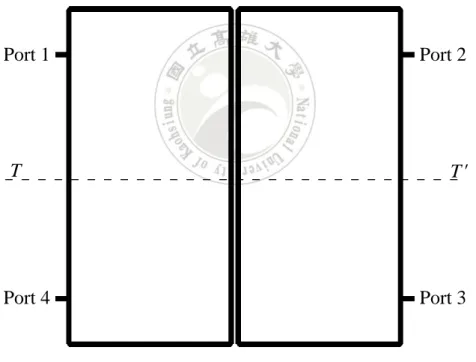

圖3.2 為一個一般的耦合器,假設它是對稱的,TT'為它的對稱平面。由於具有對稱 性,可以運用奇偶模分析方法。Port 1

Port 2

Port 3

Port 4

T

T

'

圖3. 2 以 TT'作為對稱平面的 4-Port 耦合器。在偶模態分析時,對稱平面TT’為一個完美的磁導體,而偶模態之 2-Port S 參數為𝑆11𝑒 、 𝑆12𝑒 、𝑆21𝑒 及𝑆22𝑒 ;在奇模態分析時,對稱平面TT’為一個完美的電導體,而奇模態之 2-Port S 參數為𝑆11𝑜 、𝑆 12𝑜 、𝑆21𝑜 及𝑆22𝑜 。4-Port 耦合器之 S 參數則可寫成: 𝑆11= 𝑆44 = 1 2(𝑆11 𝑒 + 𝑆 11𝑜 ) (3.1) 𝑆22= 𝑆33= 1 2(𝑆22 𝑒 + 𝑆 22𝑜 ) (3.2) 𝑆21= 𝑆12 = 𝑆34= 𝑆43= 1 2(𝑆21 𝑒 + 𝑆 21𝑜 ) (3.3) 𝑆31= 𝑆13 = 𝑆24= 𝑆42= 1 2(𝑆21 𝑒 − 𝑆 21𝑜 ) (3.4) 𝑆41= 𝑆14 = 1 2(𝑆11 𝑒 − 𝑆 11𝑜 ) (3.5) 𝑆32= 𝑆23= 1 2(𝑆22 𝑒 − 𝑆 22𝑜 ) (3.6) 一個4-Port 無損的平面跨接耦合器的 S 參數為特性為 Sii = 0 (i=1,....4)、S21 = S41 = S32 = 0,要滿足以上條件,根據(3.1) – (3.6),奇、偶模態之 2-Port S 參數特性必須為:𝑆11𝑒 = 𝑆 11𝑜 = 𝑆22𝑒 = 𝑆22𝑜 = 0、𝑆21𝑒 = −𝑆21𝑜 及 |𝑆21𝑒 | = |𝑆 21𝑜 | = 1。 對於圖3.2 所示之 4-Port 對稱耦合器,把它的耦合情況設計成圖 3.3(a)(偶模態)及圖 3.3(b) (奇模態)的模式,圖中標示 S、1、2、L 的黑點分別為來源訊號、共振腔 1、共振腔 2 以及負載,Qei及Qeo為Port 1 與 Port 2 之外部品質因子,至於 M12則為兩個共振腔之間的耦 合係數。 (a) (b) 圖3. 3 二階 4-Port 對稱耦合器之耦合情況。 (a)偶模態 (b)奇模態。

圖3.3(a)所示的半電路就像一個在 2-Port S 參數𝑆11𝑒 = 𝑆 22𝑒 =0 及|𝑆21𝑒 | = 1的情況下的帶通 濾波器;同樣地,圖3.3(b)所示的半電路就像一個在 2-Port S 參數𝑆11𝑜 = 𝑆 22𝑜 = 0 及|𝑆21𝑜 | = 1的 情況下的帶通濾波器。由於圖3.3(a)、(b)的耦合係數大小一樣但相位相反,所以𝑆21𝑒 = −𝑆21𝑜 。綜合以上結果,把一個4-Port 的耦合器的耦合方式設計成圖 3.3(a)、(b)的模式可得到 具有帶通濾波特性的跨接耦合器。除此之外,這種概念也可以運用在低通或高通特性的跨接 耦合器設計上。 圖3.4 所示的架構為本章節所提出的濾波形跨接耦合器的原始概念,由兩個相同、相鄰 的矩形共振腔所組成,每個共振腔的電氣長度為1 個波長,Port 1 與 Port 4 連接一個共振 腔,Port 2 及 Port 3 則連接另一個共振腔。 Port 1 Port 4 Port 2 Port 3 T T

'

圖3. 4 濾波形跨接耦合器的原始架構。 在偶模態,對稱平面TT'為開路,其半電路包含兩個尾端開路的共振腔,在相鄰的區域 的耦合主要為電耦合;在奇模態,對稱平面TT'為短路,其半電路包含兩個尾端短路的共振 腔,在相鄰的區域的耦合主要為磁耦合。由於此結構在不作任何調整的情況下磁耦合遠大於 電耦合,要滿足M12 (偶模態) = -M12(奇模態)的條件,電路的結構必須加以微調。 除此之外,要使奇、偶模態的耦合量相同,它們的外部品質因子𝑄𝑒𝑜與𝑄 𝑒𝑒也必須相同。要使𝑄𝑒𝑒 = 𝑄 𝑒𝑜,可透過調整共振腔的饋入位置使得在奇、偶模態從饋入位置看出去的外部阻 抗相等[14]:

𝑍

𝐿𝑒= 𝑍

𝐿𝑜= 𝑄

𝑒𝑒 𝜔0 2 𝜕𝐵𝑒 𝜕𝜔|

𝜔0= 𝑄

𝑒 𝑜 𝜔0 2 𝜕𝐵𝑜 𝜕𝜔|

𝜔0 ( 3 . 1 ) 𝑍𝐿𝑜與𝑍𝐿𝑒為奇、偶模態的外部阻抗,ω0為中心角頻率,

𝐵𝑜與𝐵𝑒為從饋入位置看進去共振腔的 奇、偶模態輸入導納的虛部。如果 𝑍𝐿𝑒 = 𝑍 𝐿𝑜 ≠ 50 Ω ,4 個 Port 均須設計匹配電路,讓𝑍𝐿𝑒和 𝑍𝐿𝑜匹配到50 Ω的負載。3.3 電路模擬

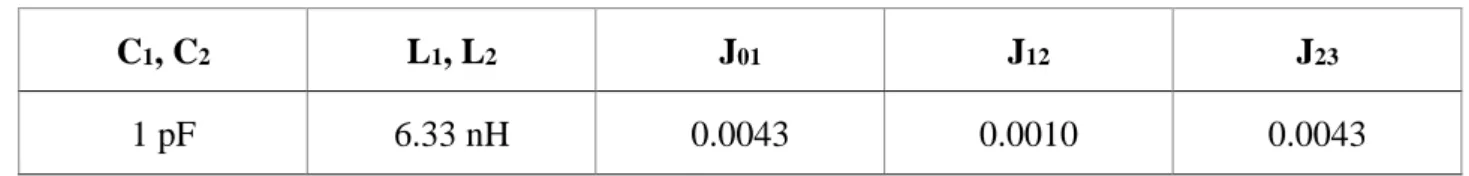

為驗證章節3.2 提出之理論是否可行,先進行電路模擬。以集總元件 L、C 模擬共振 腔,兩組共振腔之間以導納轉換器(J-Invertor)作連接,模擬它們之間的耦合情況。圖 3.5(a)、(b)分別為以導納轉換器模擬奇、偶模態的二階帶通濾波器,其規格為中心頻率 = 2 GHz,頻寬百分比 = 5%,表 3.1 為電路的參數值。 Port 1 Port 2 (a) Port 1 Port 2 (b) 圖3. 5 以導納轉換器模擬二階帶通濾波器的半電路。 (a)偶模態 (b)奇模態。表3. 1 二階帶通濾波器半電路參數值 圖3.6 為電路的頻率響應,從此圖可看出,以此結構組成的奇、偶模態半電路具有帶通濾波 器的特性,而且奇、偶模態的相位差為180°。 (a) (b) -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 偶模態 S11 偶模態 S21 -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 奇模態 S11 奇模態 S21 C1, C2 L1, L2 J01 J12 J23 1 pF 6.33 nH 0.0043 0.0010 0.0043

(c) 圖3. 6 以導納轉換器模擬二階帶通濾波器的半電路之頻率響應。 (a)偶模態 (b)奇模態 (c) 奇、偶模態的相位差。 圖3.7 是將奇、偶模態 S 參數根據(3.1) – (3.6)計算出 4-Port 跨接耦合器的 S 參數之結 果,在操作頻率2 GHz 時,S21 = S41 = S32 = 0,S31 = 0 dB 且具有濾波的特性,驗證章節 3.2 提出的理論是可行的。 圖3. 7 二階 4-Port 跨接耦合器之電路模擬結果。 -90.00 90.00 -180 -90 0 90 180 1.0 1.5 2.0 2.5 3.0 相位 (度 ) 頻率 (GHz) 偶模態 S21 奇模態 S21 -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) S11 S31

31.45mm

3.4 電磁模擬與實作

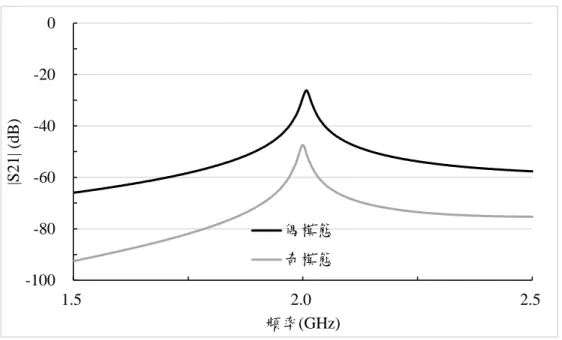

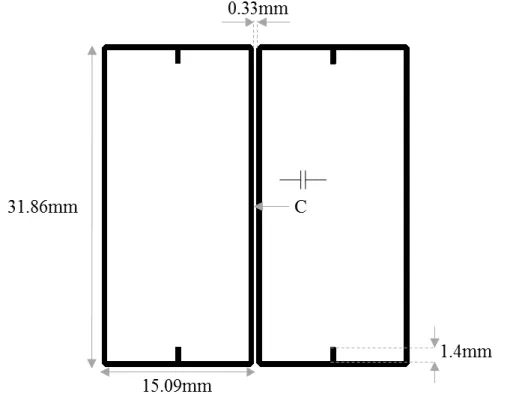

本次實作之電路製作過程與第二章相同,使用的基板與特性也一樣,採用Chebyshev 濾 波器頻率響應,共振腔之間的耦合係數與外部品質因子如表3.2 所示[15]: 表3. 2 二階濾波器之規格與對應的參數值 項目 數值 中心頻率 2 GHz 濾波器階數 2 帶通漣波 0.05 dB 頻寬百分比 5% 輸入端外部品質因子 Qei 13.85 輸出端外部品質因子 Qeo 13.85 耦合係數 M12 0.08 首先,需找出共振腔的尺寸。本次實作以寬度為0.5 mm 之傳輸線來製作一個波長的環 形共振腔,圖3.8 為共振腔之電路佈局,調整其尺寸,使其奇偶模態的中心頻率都在 2 GHz,如圖 3.9 所示。 圖3. 8 共振腔之電路佈局。圖3. 9 弱耦合饋入下,共振腔之奇、偶模態穿透係數。 接著是要透過調整兩個共振腔之間的距離,使奇偶模態的耦合係數相同並且達到所需的 數值。由於本章節所提出之電路結構的偶模態的耦合係數會比奇模態小,單靠調整兩個共振 腔的距離是無法讓兩者相等,因此,此章節的設計方法是透過在兩個共振腔之間加上0.3 pF 的電容(C)來加強偶模態的耦合係數,電容之型號為 Johanson 0402S-Series,如圖 3.10 所示。 由於對於奇模來說,連接兩個共振腔的電容是虛短路,所以透過調整電容值便能增加或減少 偶模的耦合係數而不影響奇模態。而在每個共振腔往內凸出的兩條傳輸線則是調整奇模態的 共振頻率,因為對於偶模態來說,這兩條傳輸線位在虛短路位置,其共振頻率並不會受到影 響。圖3.11 為弱耦合饋入下,兩共振腔電路的穿透係數,奇、偶模態的中心頻率皆為 2 GHz,奇模態的耦合係數為𝑀12𝑜 = 𝑓2𝑜−𝑓1𝑜 𝑓2𝑜+𝑓1𝑜= 0.08,偶模態的耦合係數則為𝑀12 𝑒 =𝑓2𝑒−𝑓1𝑒 𝑓2𝑒+𝑓1𝑒 = 0.08,與奇模態相同,符合設計需求。要達到奇偶模態耦合係數相等且中心頻率在 2 GHz 的 需求,可先調整共振腔的距離,讓奇模態的耦合係數先達到所需的值,再調整電容值,使偶 模態的耦合係數與奇模態相同。如調整上述兩者都無法達到需求,則需微調共振腔之尺寸甚 至形狀。 -100 -80 -60 -40 -20 0 1.5 2.0 2.5 |S21| ( dB ) 頻率(GHz) 偶模態 奇模態

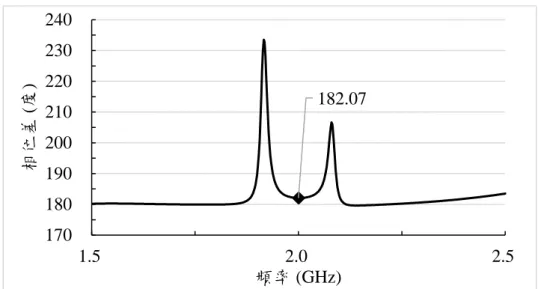

圖3. 10 兩個共振腔之電路佈局與尺寸。 圖3. 11 弱耦合饋入下,兩共振腔電路之奇、偶模態穿透係數。 圖3.12 為奇、偶模態穿透係數的相位差,從此圖可得到,在中心頻率 2 GHz,偶模態和 奇模態具有反相的耦合係數,符合章節3.2 所提出的條件。 -120 -100 -80 -60 -40 -20 0 1.5 2.0 2.5 |S 21| (dB ) 頻率 (GHz) 奇模態 偶模態

𝑓

1𝑜𝑓

2𝑜𝑓

1𝑒𝑓

2𝑒圖3. 12 弱耦合饋入下,兩共振腔電路之奇、偶模態穿透係數相位差。 下一步是找出饋入位置。用一個共振腔連接兩條饋入線,透過不斷微調饋入線之距離, 找出能讓奇、偶模態的外部阻抗在中心頻率2 GHz 相等的位置作為饋入位置。圖 3.13 顯示 設計的饋入位置,圖3.14 則為此饋入位置下奇、偶模態的外埠阻抗對頻率作圖,可以發現 兩模態在2 GHz 有同樣的外埠阻抗,符合設計所須條件。 圖3. 13 二階濾波型跨接耦合器之饋入位置。 182.07 170 180 190 200 210 220 230 240 1.5 2.0 2.5 相位差 (度 ) 頻率 (GHz)

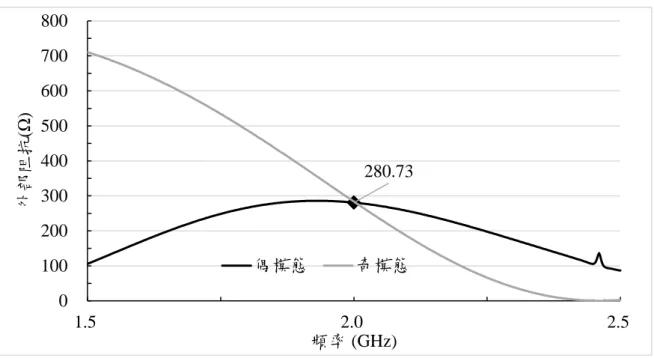

圖3. 14 共振腔之奇、偶模態在不同頻率之外部阻抗。

最後是做阻抗匹配,根據上一個步驟找到的饋入位置,分別在4 個 Port 設計單株匹配 電路將外部阻抗280.73 Ω 匹配到 50 Ω 的負載,圖 3.15 為完整的電路佈局,圖 3.16 則為實 際的電路圖,使用的基板為 Roger RO4003C,基板厚度為 0.508 mm,介電常數為 3.55,loss tangent 為 0.0027,連接兩個共振腔之電容值為 0.3 pF。 圖3. 15 二階濾波型平面跨接耦合器電路佈局。 280.73 0 100 200 300 400 500 600 700 800 1.5 2.0 2.5 外部阻抗 (Ω ) 頻率 (GHz) 偶模態 奇模態

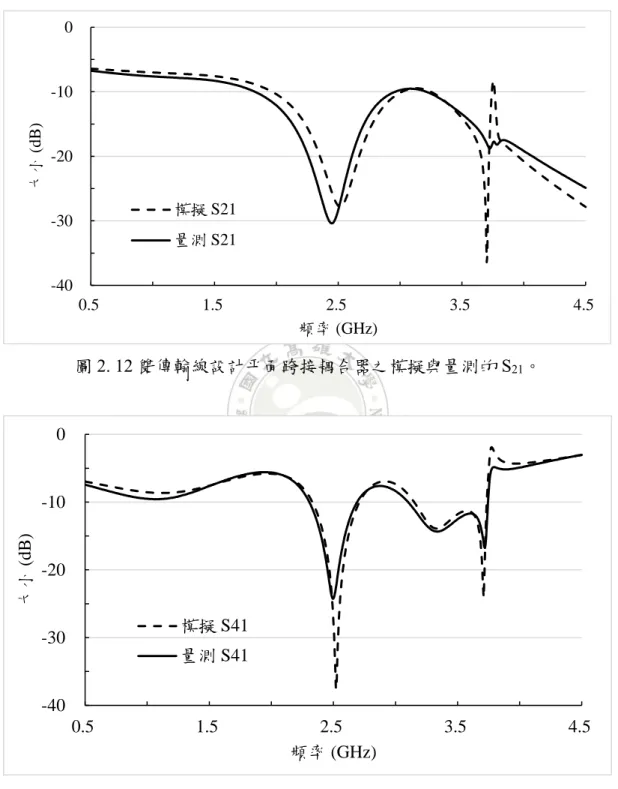

圖3. 16 二階濾波型平面跨接耦合器電路圖。 電路製作完成後,使用Agilent E5071C 向量網路分析儀量測其從 1 GHz 到 3 GHz 實際 的頻率響應。圖3.17 為模擬與量測的 S11及S31結果,從這圖可看出,此電路的S31具有濾 波的特性,與章節3.3 之電路模擬結果相符。在中心頻率 2 GHz 時,S31的量測值為 -1.68 dB,而 S11的量測值則為 -15.1 dB。與電磁模擬的結果相比,S11及S31的趨勢皆與電磁模擬 相同。 圖3. 17 二階濾波型平面跨接耦合器之模擬與量測的 S11與S31。 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 模擬 S11 量測 S11 模擬 S31 量測 S31

S

31S

11圖3.18 與圖 3.19 分別是 S21與S41的模擬與量測結果,在中心頻率2 GHz 時,S21與S41 皆小於-20 dB。 圖3. 18 二階濾波型平面跨接耦合器之模擬與量測的 S21。 圖3. 19 二階濾波型平面跨接耦合器之模擬與量測的 S41。 綜合以上結果,此電路同時具有濾波器與跨接耦合器的特性,模擬與量測結果皆與理論 相符。 -80 -60 -40 -20 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 模擬 S21 量測 S21 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 模擬 S41 量測 S41

第四章 以多個耦合共振腔設計多階濾波型平面跨接耦合器

4.1 設計原理

此章節為第三章之延伸,使用奇、偶模態相位差的特性去設計四階濾波型平面跨接耦合 器。訊號從一個共振腔傳送到另一個共振腔,奇、偶模態的相位就會相差180°,由於要形成 跨接耦合器,奇、偶模態的相位差必須為180°,所以,基於第三章去設計的多階濾波形跨接 耦合器的階數必須為2、4、6 等偶數階,如圖 4.1 所示。 (a) (b) 圖4. 1 四階 4-Port 對稱耦合器之耦合情況。 (a)偶模態 (b)奇模態。 與第三章所提出的二階濾波型跨接耦合器相同,每個共振腔之間須加上電容來加強偶模 態之耦合量。這種設計對多階電路的設計過程非常有幫助,因為這些電容只會影響偶模態的 耦合量,對奇模態不會有影響,設計者可先設計奇模態的耦合量,使其達到所須的數值,再 調整電容值,使偶模態的耦合量與奇模態一樣便可,這樣的設計可大幅減少微調電路或更改 結構的時間。4.2 電路模擬

在此,依然會先進行電路模擬來驗證章節4.1 提出的理論是否可行。以集總元件 L、C圖4.2(a)、(b)分別為以導納轉換器模擬奇、偶模態的四階帶通濾波器,其規格為中心頻率 = 2 GHz,頻寬百分比 = 10%,表 4.1 則為電路的參數值。 Port 1 Port 2 (a) Port 1 Port 2 (b) 圖4. 2 以導納轉換器模擬四階帶通濾波器的半電路。 (a)偶模態 (b)奇模態。 表4. 1 四階帶通濾波器電路參數值 圖4.3 為電路的頻率響應,從此圖可得出,以此結構組成的奇、偶模態半電路具有四階 帶通濾波器的電路特性,在中心頻率2 GHz 時,奇、偶模態的相位差為 180°。 (a) -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB) 頻率 (GHz) 偶模態 S11 偶模態 S21 C1, C2, C3, C4 L1, L2, L3, L4 J01 J12 J23 J34 J45 1 pF 6.33 nH 0.0034 0.00052 0.00041 0.00052 0.0034

(b) (c) 圖4. 3 以導納轉換器模擬四階帶通濾波器的半電路之頻率響應。 (a)偶模態 (b)奇模態 (c) 奇、偶模態的相位差。 圖4.4 是將奇、偶模態半電路 S 參數根據(3.1) – (3.6)計算出跨接耦合器 S 參數之結果, 在操作頻率2 GHz 時,S21 = S41 = S32 = 0,S31 = 0 dB 且具有濾波的特性,顯示章節 4.1 提出 的理論是可行的。 -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 奇模態 S11 奇模態 S21 90.00 -90.00 -180 -90 0 90 180 1.0 1.5 2.0 2.5 3.0 相位 (度 ) 頻率 (GHz) 偶模態S21 奇模態S21

圖4. 4 四階 4-Port 跨接耦合器之電路模擬結果。

4.3 電磁模擬與實作

由於第三章已完成了二階的電磁模擬與實作,本章節將直接使用第三章的電路佈局,延 展成4 個共振腔,分別調整間距、電容值,達到所需的電路特性。 這次實作的電路規格、各共振腔之間的耦合係數與外部品質因子如表4.1 所示。 表4. 2 四階濾波器之規格與對應的參數值 項目 數值 中心頻率 2 GHz 濾波器階數 4 帶通漣波 0.1 dB 頻寬百分比 10% 輸入端外部品質因子 Qei 11.09 輸出端外部品質因子 Qeo 11.09 耦合係數 M12 0.08 耦合係數 M23 0.07 耦合係數 M34 0.08 -70 -60 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) S11 S31Johanson 0402S-Series 這系列的電容最小值為 0.2 pF,從第三章尋找 M 值的過程中,可 得知以此設計,就算用0.2 pF 的電容連接兩個共振腔,其耦合係數依然大於 M23,因此,共 振腔的電路佈局必須稍作修改。圖4.5 為電路的第 2、3 個共振腔的電路佈局與尺寸,電容 的連接處有作調整,以減少耦合量,並得到足夠的空間串聯兩顆電容,增加設計的彈性。以 此設計,串聯1 顆 0.4 pF(C2)及 1 顆 0.6 pF(C3)的電容便可達到所須的耦合係數 M23,且中心 頻率為2 GHz,如圖 4.6 所示。為增加設計的效率,在尋找 M12、M23、M34的設計過程會先 以理想電容進行。 圖4. 5 第 2、第 3 個共振腔之電路佈局與尺寸。

圖4. 6 弱耦合饋入下,第 2、第 3 個共振腔之奇、偶模態穿透係數。 接著繼續設計第1、2 與第 3、4 個共振腔。由於電路是對稱的,兩者的耦合係數 M12與 M34相等,在此,只需針對其中一組共振腔去設計,另外一組的電路佈局則是它的鏡面反 射。在設計的過程中,必須注意第2、3 個共振腔的尺寸不得調整。圖 4.7 為電路的第 1、2 個共振腔的電路佈局與尺寸,中間連接0.2 pF 的電容 C1(C4),即可得到所需的耦合係數 M12 (M34),如圖 4.8 所示。 圖4. 7 第 1、第 2 個共振腔之電路佈局與尺寸。 -120 -100 -80 -60 -40 -20 0 1.5 2.0 2.5 |S 21| (dB ) 頻率 (GHz) 奇模態 偶模態

𝑓

1𝑜𝑓

2𝑜𝑓

1𝑒𝑓

2𝑒 31.86mm圖4. 8 弱耦合饋入下,第 1、第 2 個共振腔之奇偶模態穿透係數。 圖4.9、4.10、4.11 分別為第 1 和第 2、第 2 和第 3 以及第 3 和第 4 個共振腔的奇、偶模 態的相位差,從這3 張圖可得出,訊號從一個共振腔傳輸到另一個共振腔,奇、偶模態的相 位就會相差180°,到達第 4 個共振腔後,它們的相位差為 180°,符合第三章所提出的濾波 型平面跨接耦合器的設計條件,也驗證了章節4.1 的理論。 圖4. 9 訊號通過第 1、2 個共振腔後奇、偶模態的相位差。 -120 -100 -80 -60 -40 -20 0 1.5 2.0 2.5 |S 21| (dB ) 頻率 (GHz) 奇模態 偶模態

𝑓

1𝑜𝑓

2𝑜𝑓

1𝑒𝑓

2𝑒 181.32 160 170 180 190 200 210 1.5 2.0 2.5 相位差 (度 ) 頻率 (GHz)圖4. 10 訊號通過第 2、3 個共振腔後奇、偶模態的相位差。 圖4. 11 訊號通過第 3、4 個共振腔後奇、偶模態的相位差。 下一步便是找出饋入位置,作法與第三章相同,圖4.12 為電路的饋入位置,圖 4.13 則 為相對應的外部阻抗。 176.83 80 100 120 140 160 180 200 1.5 2.0 2.5 相位差 (度 ) 頻率 (GHz) 181.32 160 170 180 190 200 210 1.50 2.00 2.50 相位差 (度 ) 頻率 (GHz)

圖4. 12 四階濾波型跨接耦合器之饋入位置。 圖4. 13 共振腔之奇、偶模態在不同頻率之外部阻抗。 最後依照上述各個共振腔的間距、所用的電容把4 個共振腔連接起來,再分別於 4 個 Ports 設計單株匹配網路,將共振腔外部阻抗 210.77 Ω 匹配到 50 Ω 的負載,圖 4.14 為完整 210.77 0 100 200 300 400 500 600 700 1.5 2.0 2.5 外郭阻抗 ( Ω ) 頻率 (GHz) 偶模態 奇模態

圖4. 14 四階濾波型跨接耦合器電路佈局。 圖4.15 為電路的頻率響應,從此圖可看出,把 4 個共振腔連接起來之後,其頻率響應跟預 期的完全不同,尤其是隔離度很差。要解決這問題,可透過奇、偶模分析,分別針對奇、偶 模的頻率響應作處理。圖4.16 為電路的奇、偶模態 S21 的頻率響應,從這兩張圖可看出, 電路確實是有濾波器的特性,但奇、偶模態的中心頻率並不一樣,造成電路的頻率響應不如 預期。奇模態的中心頻率是2 GHz,沒有問題;問題在於偶模態的中心頻率只有 1.9 GHz, 從2 GHz 往低頻偏移了 0.1 GHz。由此現像可推論,問題的原因是連接 4 個共振腔的電容對 偶模態的頻率造成了影響。

圖4. 15 四階濾波型平面跨接耦合器的頻率響應 (電磁模擬)。 圖4. 16 四階濾波型平面跨接耦合器奇、偶模態的頻率響應 (電磁模擬)。 在設計電路時,4 個共振腔是分成 3 組,個別去調整,每一組的電容的效應其實是有被 考慮到,但是當每組的共振腔都調整完畢,組合成一個完整的電路時,3 顆電容連接起來後 -80 -60 -40 -20 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) S11 S21 S31 S41 -80 -60 -40 -20 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 偶模態 S21 奇模態 S21

會受到影響,因此,偶模態的頻率出現了偏差。 在此,電路的尺寸必須再作出調整。要把偶模態的中心頻率從1.9 GHz 調整到 2 GHz, 可把各個共振腔的尺寸縮小,讓中心頻率回到2 GHz。此時,由於共振腔的尺寸變小了,奇 模態的中心頻率會從2 GHz 往高頻偏移,要讓它回到 2 GHz,可增加每個共振腔中間往內凸 出的傳輸線的長度,如同第三章所述,調整這些傳輸線的長度只會影響奇模態的頻率,偶模 態的頻率會維持不變,此舉便能把偶模態的中心頻率固定在2 GHz 同時把奇模態的中心頻率 調整回2 GHz,讓兩者相同。圖 4.17 為調整後的電路佈局及尺寸,把理想電容換成 Johanson 0402S-Series 的電容模型,第 2、3 個共振腔之間的兩顆電容需調整為兩顆 0.7 pF 電容(C2、 C3,第1、2 個與第 3、4 個共振腔之間的電容(C1、C4)維持 0.2 pF,以得到較佳的頻率響 應。圖4.18 為電磁模擬的頻率響應結果,S31具有濾波的特性,S11、S21及S41在中心頻率2 GHz 皆小於-15 dB,與預期的結果相符。 圖4. 17 調整後之四階濾波型平面跨接耦合器電路佈局及尺寸。

圖4. 18 四階濾波型平面跨接耦合器電磁模擬結果。 圖4.19 則為實際的電路圖,使用的基板為 Roger RO4003C,基板厚度為 0.508 mm,介 電常數為3.55,loss tangent 為 0.0027。 圖4. 19 四階濾波型平面跨接耦合器電路圖。 與第三章一樣,電路製作完成後,使用Agilent E5071C 向量網路分析儀量測其從 1 GHz 到 3 GHz 實際的頻率響應。圖 4.20 為模擬與量測的 S11及S31結果,從這圖可看出,此 電路的S31具有濾波的特性,與章節4.2 之電路模擬結果相符。在中心頻率 2 GHz 時,S31的 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) S11 S21 S31 S41

量測值為 -3 dB,而 S11的量測值則為 -21.63 dB。與電磁模擬的結果相比,S11及S31的趨勢 皆與電磁模擬相同,量測值在中心頻率比電磁模擬差,這應是因為手動焊接元件所造成的誤 差,與第三章的情況相同。 圖4. 20 四階濾波型平面跨接耦合器之模擬與量測的𝑆11與𝑆31。 圖4.21 與圖 4.22 分別是 S21與S41的模擬與量測結果,在中心頻率2 GHz 時,S21與S41 分別為-18 dB 與-20 dB。 圖4. 21 四階濾波型平面跨接耦合器之模擬與量測的 S21。 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 量測 S31 量測 S11 模擬 S31 模擬 S11 -80 -60 -40 -20 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 模擬 S21 量測 S21

S

11S

31圖4. 22 四階濾波型平面跨接耦合器之模擬與量測的 S31。 綜合以上結果,此電路同時具有濾波器與跨接耦合器的特性,模擬與量測結果皆與理論 相符。 -50 -40 -30 -20 -10 0 1.0 1.5 2.0 2.5 3.0 大小 (dB ) 頻率 (GHz) 模擬 S41 量測 S41

第五章 結論

本論文所提出的兩種跨接耦合器設計的目的階為節省空間,但它們節省空間的方式卻不 大相同。第二章提出的以雙傳輸線設計之縮小化跨接耦合器為單一電路的縮小化,而第三、 四章所提出的以二/多個耦合共振腔設計二/多階濾波型跨接耦合器則是以一個電路取代多個 電路的方式達到節省空間的效果。 把雙傳輸線設計應用在跨接耦合器上,能夠有效地縮小電路的尺寸,而且對頻寬的影響 不大,模擬與量測皆有一致的結果。除了跨接耦合器與[7]、[8]所提出的電路外,應也可有 效地應用在其他的電路上。可是這樣的設計須使用高阻抗的傳輸線,金屬損耗不小,比較不 適合應用在非常高頻的電路上。 第三、四章所提出的濾波型跨接耦合器,探討這議題的文獻並不多,目前只有一篇文獻 有發表到期刊,算是較新的議題,而且本論文所提出的設計理論簡單,模擬與量測皆得到一 致的結果。不過這種設計的頻寬非常有限,即使把它發展成多階的設計,也無法有效地拉大 頻寬,未來可朝這方向繼續探討。參考文獻

[1] C.-C. Chang, R.-H. Lee, and T.-Y. Shih, “Design of a beam switch-ing/steering butler matrix for phased array system,” IEEE Trans. Antennas Propagat., vol. 58, no. 2, pp. 367–374, Feb. 2010.

[2] J. S. Wight, W. J. Chudobiak, and V. Makios, “A microstrip and stripline crossover structure,” IEEE Trans. Microw. Theory Tech., vol. MTT-24, no. 5, pp. 270, May 1976. [3] Y. Che and S.-P. Yeo, “A symmetrical four-Port-microstrip coupler for crossover

application,” IEEE Trans. Microw. Theory Tech., vol. 55, no. 11, pp. 2434-2438, Nov. 2007. [4] Y.-C. Chiou, J.-T. Kuo, and H.-R. Lee, “Design of compact symmetric four-Port crossover

junction,” IEEE Microw. Wirel. Compon. Lett., vol. 19, no. 9, pp. 545-547, Sep. 2009. [5] Z.-W. Lee and Y.-H. Pang, “Compact planar dual-band crossover using two-section

branch-line coupler,” IET Electron. Lett., vol. 48, no. 21, pp. 1348-1349, Oct. 2012.

[6] F. Lin, S.-W. Wong and Q.-X. Chu, “Compact design of planar continuously tunable

crossover with two-section coupled lines,” IEEE Trans. Microw. Theory Tech., vol. 62, no.3, pp. 408-415, Mar. 2014.

[7] C.-W. Teng, M.-G. Chen, and C.-H. Tsai, “Miniaturization of microstrip branch-line coupler with dual transmission lines,” IEEE Microw. Wirel. Compon. Lett., vol. 18, no. 3, pp. 185-187, Mar. 2008.

[8] C.-H. Lu, P.-H. Tu and C.-H. Tseng, “A miniaturized rat-race coupler with arbitrary power division using dual transmission lines,” in Proc. Asia Pacific Microw. Conf., Dec. 2012, pp. 1007-1009.

[9] J.-Y. Shao, S.-C. Huang and Y.-H. Pang, “Wilkinson power divider incorporating quasi-elliptic filters for improved out-of-band rejection,” IET Electron. Lett., vol. 47, no. 23, pp. 1288-1289, Nov. 2011.

high-isolation using coupled-line filter transformers,” IEEE Trans. Microw. Theory Tech., vol. 60, no.6, pp. 1520-1529, Jun. 2012.

[11] X.-Y. Zhang, Q.-Y. Guo, K.-X. Wang, B.-J. Hu and H.-L. Zhang, “Compact Filtering Crossover Using Stub-Loaded Ring Resonator”, IEEE Microw. Wirel. Compon. Lett., vol. 24, no. 5, pp. 327-329, May 2014.

[12] D.M Pozar, Microwave Engineering, 4th ed., John Wiley & Sons, Inc., 2011, chap. 4.

[13] T. Kim, J. Lee and J. Choi, “Analysis and design of miniaturized multisection crossover with open stubs”, Microwave and Optical Technology Letters, vol. 57, issue. 11, pp. 2673-2677, Nov. 2015.

[14] S. Zhang and L. Zhu, “Synthesis design of dual-band bandpass filters with λ /4 stepped-impedance resonators”, IEEE Trans. Microw. Theory Tech., vol. 61, no. 5, pp. 1812-1819, May 2013.

[15] J.-S. Hong, Microstrip Filters for RF/Microwave Applications, 2nd ed., John Wiley & Sons, Inc., 2011, chap. 3.