報告題名:

氮氣熱退火處理對矽氧化鉿高介電

質可靠度之研究

Effects of N

2RTA Treatment on Reliability of

HfSiO

XHigh-K Gate Dielectrics

作者:賴逸修 系級:電子四甲 學號:D9530185 開課老師:林成利 老師 課程名稱:專題研究(二) 開課系所:電子工程學系 開課學年:98 學年度 第一學期

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

摘要

矽氧化鉿(HfSiOx)是目前最有希望用來取代二氧化矽(SiO2)材料

的選擇之一。本實驗將研究矽氧化鉿介電層經過氮氣環境下的快速熱

退火(Rapid Thermal Annealing,RTA)處理,並與未經過氮氣熱退火處

理的矽氧化鉿介電層做比較,探討其電性與可靠度分析。結果發現經

過氮氣熱退火處理後的元件,由於氧空位缺陷被修復,因此在電流電

壓(I-V)特性圖上,呈現較低的漏電流與較高的崩潰電壓(Voltage

Ramp Dielectric Breakdown,VRDB)。同時也在電容對電壓(C-V)特性

圖上發現較小的遲滯現象與遲滯電壓偏移量。最後藉由韋伯分佈

(Weibull Distribution)曲線預測,經過 N2 RTA 處理後的元件具有較高

的TBD63.2%值,同時也有較佳的TDDB 可靠度。

針對HfSiOx崩潰機制的研究,依據 TDDB 特性圖推測,由於高

介電質內帶負電的電子電荷捕捉,使得漏電流隨著測試時間增長而有

降低的現象,當陷阱(Oxide Trap)產生,元件便伴隨著時間增加導致

永久性崩潰(Hard Breakdown,HBD)。另外,經過高溫 N2 RTA 處理

後的HfSiON 介電層,由於微結晶現象導致初期漏電流較高,當電子

捕捉行為發生後,便隨時間產生少數的暫時性崩潰(Soft Breakdown,

SBD )或漸進式崩潰(Progressive Breakdown,PBD),最後產生多數的

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 最後本專題提出介電層的崩潰模式,在累積模式(Accumulation Mode)下,電子由閘極端注入,在高介電係數材料上產生缺陷,當缺 陷隨時間變多後產生漏電流路徑,最後大電流使高介電係數材料與介 面層同時發生崩潰。因此推測介電層的崩潰是先由高介電係數材料先 發生崩潰,緊接著發生介面層(Interfacial Layer)崩潰。而此現象也是 造成TDDB 特性圖上,崩潰發生時直接產生永久性崩潰的原因。 關鍵字:矽氧化鉿、依時性介電層崩潰、可靠度分析、崩潰機制

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

Abstract

As device dimension scaling to nanometer regime, the ultra-thin gate oxide (SiO2) reveals large leakage current. This large leakage current will degrade device

performance and increase the power consumption. High-k gate dielectric, such as hafnium-based dielectric, possesses higher dielectric constant. Thus thicker thickness of dielectric can be used and reveals low gate leakage current. In this work, we study the effects of rapid thermal annealing of hafnium silicate (HfSiOx). These include the

electrical characteristics (IV and CV analysis) and reliability of time dependent dielectric breakdown (TDDB). We use the constant voltage stress to investigate the TDDB reliability.

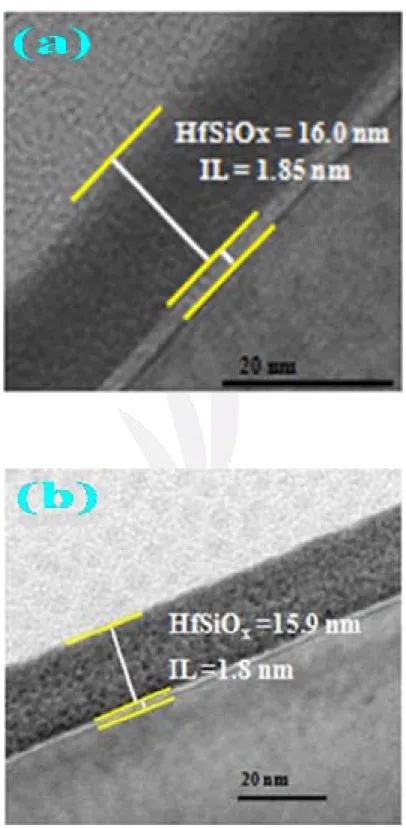

From the TEM analysis, we found an interfacial layer about 1.85 nm between the HfSiOx and p-type substrate. There is not obvious increase the thickness of

interfacial at higher RTA temperature. For reliability testing, the time to breakdown (TBD63.2%) of Weibull plot and ramp voltage breakdown (VRDB) will increase with

RTA temperature. In CV analysis, we found the hysteresis of CV is decrease with increasing RTA temperature. This because the oxide trap decreased by the RTA annealing. And the breakdown behavior shows more clear hard breakdown and better reliability at higher RTA temperature.

For breakdown mechanism of HfSiOx gate dielectric, we presume that charge

trapping in High K film resulted in the gate leakage current is decrease with increasing testing time. After continuing TDDB testing, the percolation of oxide trap will lead to the conductive path in the film, and result in the hard breakdown happen. In other hand, the effect of N2 RTA annealing treatment on HfSiOx gate dielectric,

there are soft breakdown and/or progressive breakdown phenomenon happen at higher temperature of RTA treatment. Presumably, the microstructure has changed after RTA treatment, and the charge trapping and/or de-trapping resulted in the breakdown behavior. Finally, when the oxide trap or defects form the conductive path in the film, it will reveal the hard breakdown phenomenon.

For the breakdown mechanism of HfSiOx with interfacial layer (SiOx) under

accumulation testing mode under various RTA annealing, we presume the electron inject from the metal gate, and produce the oxide trap or defects in the film. The interfacial layer (SiOx) reveals lower dielectric constant (~3.9), than that of the

HfSiOx (~ 12). When negative gate bias applied the gate electrode, the lower

dielectric of interfacial layer will reveal larger electrical field. This large electrical field will let the interfacial layer produce breakdown earlier than the bulk HfSiOx

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

soft breakdown happening, the larger leakage current through the gate stack. This will lead to the hard breakdown happen in the I-t plot.

In conclusion, we found the nitrogen rapid thermal annealing is beneficial to increase the time to breakdown (TBD) and breakdown detection in the I-t plot. The N2

RTA treatment also reduces the hysteresis of CV curve. But the higher temperature annealing will change the microstructure or crystalline phase happen in the film. These will degrade the CV characteristics. So the gate dielectric performance and reliability need to be trade-off. Finally, we propose a breakdown model to explain the TDDB behavior. We presume the interfacial layer is firstly breakdown, and the HfSiOx occurs immediately the breakdown.

Keywords:time dependent dielectric breakdown (TDDB)、Silicon Dioxide (SiO2)、

Hafnium Silicate (HfSiOX)、Nitrided Hafnium Silicate (HfSiON) 、breakdown

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

誌謝

在開始著手進行專題撰寫之前,我從來不知道能夠學到如此豐富 的專業知識。專題研究就如同連鎖效應,一個問題所衍伸出更多、更 深的問題,能夠讓我如同挖掘知識寶庫般,充實我的大學生活。在此 必須感謝專題指導教授 林成利博士,在這一年多的專題研究當中指 導我正確的研究態度以及研究方向,同時也教導我許多專題上遇到的 各種問題,並且提供各項資源讓我們學習半導體元件製程技術。在老 師的指導下,我不僅是在專題研究上得到心得,同時對於各種做事態 度以及研究精神上也從老師身上得到許多榜樣。 在研究專題的過程中也得到許多學長姐的幫助,在這裡也要特別 感謝周美媛學姊、洪嘉駿學長、王凱盛學長、劉聖賢學長…等等,在 專題研究以及元件測量與製程上給予指導與建議。另外也要感謝逢甲 大學電子工程學系提供的半導體製程實驗室,讓我能學習元件製程技 術。 最後,感謝我的摯愛父母與家人 ,有你們的支持才有現在的我。 因此,往後的日子裡,我將會更加努力在自己的目標上,獻上我的成 就做為最好的感謝。氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

目錄

摘要 ··· i 誌謝 ··· v 目錄 ··· vi 第一章:緒論 ··· 1 1-1 前言 ··· 1 1-2 研究動機 ··· 2 第二章:高介電材料特性與量測方法 ··· 3 2-1 高介電材料的條件 ··· 3 2-2 氮氣熱退火處理 ··· 52-3 高介電材料氧空位缺陷(Oxygen Vacancies Trap)理論 ··· 7

2-4 韋伯分佈曲線 ··· 9 2-5 電性量測方法 ··· 11 第三章:實驗方法與分析 ··· 17 3-1 元件結構與製程 ··· 17 3-2 量測結果與可靠度分析 ··· 20 3-3 矽氧化鉿(HfSiOx)與氮氧化矽鉿(HfSiON)崩潰機制 ··· 24 第四章:結論 ··· 28

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

第一章 緒論

1-1 前言

現今金屬-氧化物-半導體(Metal Oxide Semiconductor,MOS)元 件的氧化層已經由其他高介電係數材料(High Dielectric Constant,

High-k)取代原本的二氧化矽(Silicon Dioxide,SiO2)材料。由於漏電

流以及等效氧化層厚度(Equivalent Oxide Thickness,EOT)問題導致

SiO2已經無法使用於極薄(Ultra-Thin)的閘極氧化層。

High-k 材料本身必須具有較高的 EOT,防止直接穿隧電流(Direct

Tunneling Current )。同時較大的能障高度也能阻止穿隧電流發生,因

此必須考慮材料的能隙 (Bandgap)。閘極介電層一般為 20<K<60、EG

>5eV。

目前有許多取代 SiO2的 High-k 材料,其中包含二氧化鈦(TiO2)、

二氧化鉿(Hafnium Dioxide,HfO2)、矽氧化鉿(Hafnium Silicate,HfSiOx)

等,其中HfO2與HfSiOx被認為是具有較高的介電常數,並可抑制直

接穿隧電流,同時具有較高的材料特性,如表1-1 所示。然而,TiO2

雖然有極高的介電係數,但較低的能隙使其相較於其他材料的情況

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 表 1-1 高介電係數材料介電常數與能隙寬度 Material Dielectric Constant(k) Band Gap △EG (eV) △EC (eV) to Si SiO2 3.9 8.9 3.2 TiO2 80 3.5 1.2 ZrO2 25 7.8 1.4 HfO2 25 5.7 1.5

1-2 研究動機

上述提到 HfO2 有較高的介電常數與 EOT,但崩潰電壓(VoltageRamp Dielectric Breakdown,VRDB)與漏電流特性依然不佳,因此取而

代之的是 HfSiOx材料。在基本特性分析上發現,HfSiOx除了具備較

大的 EOT 外還具有較大的 VRDB,且漏電流也較小。

另外,我們已經知道 HfO2介電層經過氮氣(N2)環境下的快速熱退

火(Rapid Thermal Annealing,RTA)處理後,崩潰電壓(VRDB)與崩潰時

間(TBD)皆有所提升[1]。而 HfSiOx在經過氮氣環境下的快速熱退火處

理後,是否會改善介電層的電性與可靠度將是本實驗的研究目標。因

此本實驗探討 HfSiOx 介電層的電容元件利用氮氣環境下快速熱退火

處理的特性,並與未經氮氣處理的 HfSiOx介電層的電容元件做比較,

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

第二章 高介電材料特性與測

量方法

2-1 高介電材料的條件

一般而言選擇High-k 材料通常必須具備幾項條件,才能取代 SiO2 材料。包含超薄的介面層、低漏電流、較高的能隙及導帶(Conduction Band)能帶偏移量、與矽基板直接接觸時具有熱力的穩定性、非晶晶 相等[2]。 雖然 High-k 材料可以提供較大的實際厚度降低穿隧電流,若能 隙與能帶偏移量(Band Offset)過小容易使穿隧效應法生。因此除了考 慮介電係數之外,也必須考量能隙大小與能帶偏移量,如圖 2-1.1, 2-1.2。 由於 High-k 材料是由金屬氧化物形成,可能與矽基板反應造成閘極漏電流增加、High-k 的有效介電常數下降、EOT 增加,當 High-k

材料在高溫製程下也有可能發生結晶化現象,產生極大的漏電流。因

此具有熱穩定性的High-k 材料對於元件的特性也是一項重要的關鍵。

使用 High-k 材料容易形成複晶晶相(Poly-Crystalline),或是後續

高溫熱退火處理時,容易使薄膜發生結晶化現象。複晶晶相的薄膜型

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

(amorphous phase)為佳。

圖2-1.1 能隙與介電係數關係圖[2]

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

2-2 氮氣熱退火處理

在半導體的製程中,由於 High-k 介電層與矽基板之間會產生一 介面層(Interfacial Layer),並影響元件的特性。而元件體積愈來愈小, 氧化層的厚度也必須跟著減少,為了減少氧化層厚度,介面層厚度成 為影響氧化層厚度的關鍵。目前最常使用的方法是利用氮化處理減少 介面層厚度,如圖 2-3 所示。雖然氮化處理將氧化層的厚度減少,卻 也造成了較大的漏電流,因此如何將介面層的厚度減少與特性提升將 成為另一項重要的研究方向。 影響元件可靠度的另一因素,由介電層的緻密度不均產生許多缺 陷(defects)或陷阱(traps)。這些缺陷與陷阱會導致漏電流的路徑,因 此利用熱退火處理能改善薄膜的緻密度與原子之間的鍵結,減少漏電 流產生。然而經過高溫熱退火會使氧化層薄膜內有微結晶化的現象, 並產生漏電流路徑。因此,以適合的溫度熱退火使元件得到最佳特性 也是未來重要的研究項目。 另 外, 氮 氣 環 境 下 熱 退 火 處 理 也 能 減 少 氧 空 位 缺 陷(Oxygen Vacancies Trap),避免漏電流路徑形成。關於氧空位缺陷的現象,會 在下面章節中加以探討。

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 2-3 TaN/HfSiOx (16 nm)/p-sub/Al-Si-Cu 之 MIS 電容結構,(a) No

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

2-3 高介電材料氧空位缺陷(Oxygen Vacancies Trap)理論

氧化層中包含許多缺陷與陷阱,其中氧空缺(Oxygen Vacancy, VO)也屬於陷阱的一種。在 HfSiOx氧化層中,氧空缺捕捉電子造成帶 負電的氧空缺(VO2-),而其它主鍵(Back-Bond)上的氧空缺能量會因 庫倫力減少,使得另外的氧空缺形成,經過氧空缺的連鎖效應後,崩 潰便會發生於氧化層[3],圖 2-3.1。因此也顯示了電子與上述的崩 潰機制有密切的關係。 藉由載子分離技術,得到穿隧電流密度對電場的關係曲線,電子 流與電場保持線性關係,而電洞流則與電場呈現非線性關係[3],因

此利用下列公式估計電子的有效位能障(Effective Barrier Height,

Φb)。

)

3

)

(

2

4

exp(

3 / 2 * 2E

q

q

m

AE

J

bh

Φ

−

=

由測量得到有效功函數(effective work function,Φeff),並與位能

障繪製而成曲線圖,證實 Φeff與 Φb的線性關係[3],且不同的 Φeff與

Φb卻得到共同的能階。上述的結果顯示由能階可以確定有效位能障在

真空能階(Vanuum Energy Level)以下 4.2eV 的位置,如圖 2-3.2 所示。

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 一致。由圖2-6 所示,電子以陰極注入在 HfSiOx氧化層中穿隧,伴隨 著由 VO決定的位能障,得知VO不只是電子捕獲位置,同時決定電子 流的有效位能障。 圖 2-3.1 氧空缺形成過程[3] 圖 2-3.2 電子穿隧伴隨著由氧空缺決定的效位能障[3]

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

2-4 韋伯分佈曲線

為了確認元件生命期與可靠度,必須依賴準確性高的可靠度評估 技術。韋伯分佈優點為即使樣本很少,依然能提供準確的分析與預 估,因此常被用於產品的壽命期與可靠度預估的統計模型。 在半導體產業中,由於元件的失效分佈圖必須呈現出多數元件擁 有較長的生命期,如此元件才具備較佳的可靠度。而這樣的分布特性 並非常態分佈,而是呈現出韋伯分佈型態,因此韋伯分佈曲線被廣泛 的使用於半導體元件閘極介電層可靠度的預測。韋 伯 分 佈 分 為 機 率 密 度 函 數 (Weibull Probability Density

Function , PDF) 與 累 積 分 佈 函 數 (Weibull Cumulative Distribution

Function,CDF),機率密度函數為利用數學式描述間隔時間內損壞件 數量。 β η β

η

η

β

( ) 1)

(

)

(

xe

x

t

F

− −=

(2-4.1) 而累積分佈函數則是由數學式描述隨時間增加元件損壞的累積數量。 β η ) (1

)

(

xe

x

F

−−

=

(2-4.2)其 中 x 為 隨 機 變 數 (Random Variable) 、 β 為 形 狀 參 數 (Shape

Parameter),而 η 為特徵壽命(Characteristic Life)。當元件達到 η 壽命

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 由於累積分佈函數在平面上為曲線,為了方面觀察,我們將累積 分佈函數取自然對數後再觀察其斜直線上的斜率。利用上述(2-4.2) 式經過移項後再對方程式兩邊同時取兩次自然對數後,方程式變為: β η ) (

)

(

1

xe

x

F

−=

−

)

(

)]}

(

1

[

{

η

β

n

x

x

F

n

n

l

l

l

−

−

=

⋅

)

(

)

(

)]}

(

1

[

{

n

F

x

n

n

x

n

l

l

l

l

−

−

=

−

β

⋅

η

+

β

⋅

(2-4.3) 因此令Y

=

l

n

{

−

l

n

[

1

−

F

(

x

)]}

,X

=

l

n

(x

)

將(2-4.3)式轉換為:Y

=

a

+

bX

對應後可得a

=

−

β

⋅

l

n

(

η

)

,b

=

β

當可靠度藉由韋伯分佈求得後,形狀參數 β 可決定元件故障型 態,表 2-1 為不同範圍的 β 值所對應的故障型態。因此當斜率愈大, 表示大多數元件的生命期均相同或相近,因此元件的可靠度也愈佳。 表 2-1 不同β 值所對應的故障型態 故障形態 Β<1 故障率遞減型 Β=1 故障率一定型 Β>1 故障率遞增型氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

2-5 電性量測方法

為了確保元件良率與特性同時加以改善,一般常利用短期測試評 估氧化膜的長期可靠度[6]。晶圓式可靠性評估技術的優點主要為測 試結構簡單、測試時間短、能在短時間內測得元件的特性參數、縮短 模組技術開發週期、降低成本等。 氧化膜的測試可分為電流應力或電壓應力,並依照與時間的關聯 性 又 可 再 細 分 為 長 定 模 式 與 斜 坡 模 式 。 其 測 試 包 含 定 電 壓 測 試(Constant Voltage Stress, CVS) 、 斜 坡 電 壓 測 試 (Ramped Voltage

Stress ,RVS)、定電流測試(Constant Current Stress,CCS),與斜坡

電流測試(Ramped Current Stress ,RCS)四種,如圖 2-5.1。

本實驗量測元件的電性中,電流對電壓(I-V)利用斜坡電壓測試 的方式,給予一個斜坡電壓,測量元件崩潰時的崩潰電壓(VRDB)。電 流對時間(I-t)主要利用定電壓測試,給予一個固定偏壓,測試元件的 崩潰時間(TBD)。而電容對電壓(C-V)同樣為斜坡電壓測試,量測斜 坡電壓的電容值。 其中 CVS 是測試氧化膜可靠與預測生命期、故障率的最傳統方 法,且擁有一次可測試大量樣品的優捷倫公司的 HP 4155C 與 4980A 半導體參數分析儀量測 CVS 與 RVS,如圖 2-5.2,分別得到 VRDB與 TDB參數並進行可靠度分析與比較其電性的優缺點。

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

其中安捷倫 4155C 的設定上,我們使用的 sweep mode 量測電流

對電壓(I-V)的特性圖,將電壓範圍設定於 0V~ -15V、取樣間距為

-100mV,且最大限流為 100mA,如圖 2-5.3、2-5.4 所示。而電流對

時間(I-t)特性圖的設定必須將 sweep mode 調整為 sampling mode,同

時探針均設定為接地,最後使用-9.4V 作為量測的偏壓,如圖 2-5.5、 2-5.6。接著以安捷倫4980A 量測電容對電壓特性圖,設定小訊號為 25mV、頻率為 100kHz、量測範圍為 4V~-4V,且最大電容為 600pF, 如圖 2-5.7。 當完成元件特性量測後,就可以利用特性圖分析元件電性與可靠 度,而可靠度分析將在下面章節中提到。 點,而我們也利用 CVS 量測元件的崩潰時間(TBD)。另外 RVS 可提供 缺陷密度的資料、VRDB與漏電流等資料,同時也是廣泛被應用在晶圓 的測試上。在此,我們使用安

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 2-5.1 氧化膜測試模式, I-V 與 C-V 量測為 RVS、I-t 量測為

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 2-5.3 CHANNELS 畫面 I-V 設定參數

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 2-5.5 CHANNELS 畫面 TDDB 設定參數

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

第三章 實驗方法與分析

3-1 元件結構與製程

此實驗主要探討氮氣熱退火處理對 HfSiOX的可靠度分析,因此 樣本使用六吋 P 型矽基板的電容結構,其中氧化層分別為經過氮化處 理與未經氮化處理的 HfSiOX介電層材料。首先將晶片(Si Wafer)經過 RCA 標準清洗,去除微塵粒、有機物、

無機物、金屬離子等雜質,再利用金屬有機化學氣相沉積(Metal

Organic Chemical Vapor Deposition,MOCVD)系統沉積 16nm 厚的介

電層,其中 MOCVD 的前驅物為(Precursor)Hf[CO(CH3)3]2 [CO(CH3)2

CH2- OCH3]2與Si[CO(CH3)3]2[CO(CH3)2CH2OCH3]2,同時腔體內通入

O2氣體,反應後形成HfSiOX薄膜。 將元件置於充滿氮氣的環境下以 900℃維持 30 秒的快速熱退 火 , 再 經 由 預 烤(Pre-Back) 去 除 晶 圓 上 的 水 氣 、 上 光 阻 、 軟 烤 (Soft-Back)、曝光(Exposure)、顯定影等步驟定義光阻圖案(Pattern), 最後由硬烤(Hard-Back)步驟方便後續的蝕刻製程。 接著利用反應式真空濺鍍(Reactive Sputtering)系統,沉積 50nm 的氮化鉭(Tantalum Nitrogen,TaN)薄膜作為金屬閘極層,並使用 Lift-Off 的製程技術定義閘極圖案。最後經由 B.O.E 去除晶片背面的

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

面作為背電極,完成了 MIS(Metal Insulator Semiconductor,MIS)的電

容結構。其流程如圖 3-3.1,3-3.2 所示。 RCA 標準清洗 MOCVD 沉積 HfSiOX 未經 N2 RTA 處理 900℃ N2 RTA 處理 定義光阻圖案 沉積 TaN 金屬閘極層 定義閘極金屬圖案 背鍍 Al-Si-Cu 電極 圖 3-1.1 HfSiOX MIS 結構簡易流程

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 圖 3-1.2 HfSiOXMIS 結構製作流程 置於充滿氮氣的環境下,以 900℃維持 30 秒的 RTA。 經過預烤、上光阻、軟烤、曝 光等步驟定義光阻圖案後,再 利用硬烤處理以便後續蝕刻。 由反應式真空濺鍍系統沉積50nm 的TaN 薄膜當作金屬閘極層。 利用lift-off 技術定義閘極圖 案。最後沉積200nm 的 Al-Si-Cu 薄膜於晶背,完成MIS 結構。 p-Sub p-Sub p-Sub p-Sub HfSiOX HfSiOX HfSiOX HfSiOX p-Sub p-Sub PR PR PR PR TaN 由MOCVD 系統沉積 16nm 厚的 HfSiOX薄膜。 將P 型矽基板進行 RCA 標準清洗步驟。 TaN TaN Al-Si-Cu HfSiOX

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

3-2 量測結果與可靠度分析

利用半導體參數分析儀量測結果,觀察到經過 N2 RTA 處理後的 元件,崩潰電壓明顯提高,如圖 3-2.1 所示。因此推測 N2 RTA 處理 後的薄膜,缺陷與氧空缺皆被氮原子修復,同時提高薄膜的緻密度。 然而,閘極偏壓(VG)約 0~3V 的漏電流卻隨著 N2 RTA 的處理而提高, 推測是由高溫熱退火使薄膜產生微結晶現象,造成漏電流路徑產生。 由量測結果得到電容對電壓(C-V)特性圖,如圖 3-2.2 所示,可以 發現經過 N2 RTA 處理後,△VFB 往正偏壓移動,同時遲滯效應(Hysteresis Effect)與遲滯電壓偏移量也明顯減少。推測是經過 N2 RTA

後,正陷阱電荷(Positive Trap Charge)與薄膜內的陷阱與缺陷皆有減少

的現象,降低薄膜內的電荷捕捉。 使用定電壓測試量測元件的電流對時間(I-t)特性圖。將閘極偏壓 固定於-9.4V,測量元件的崩潰時間,如圖 3-2.3,3-2.4 所示。經過 N2 RTA 處理後的崩潰電壓與崩潰時間有明顯的增加,同時漏電流也 被觀察到有減少的現象。 分析元件的生命期也是可靠度分析的重要項目之一,因此利用韋 伯分佈(Weibull Distribution)曲線可預測元件的生命期。圖 3-2.5 顯示

經過 N2 RTA 處理與未經 N2 RTA 的韋伯累積分佈函數(Weibull

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

理的元件有較高的 TBD63.2%值,因此此元件的TDDB 可靠度較佳。

圖 3-2.1 閘極介電層 HfSiOx (16nm),在累積模式(accumulation mode)

經過 900℃RTA 的 J-V 圖。

圖 3-2.2 為 TaN/HfSiOx (16 nm)/p-sub/Al-Si-Cu 之 MIS 電容結構經過

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖2-3.3 TaN/HfSiOx (16 nm)/p-sub/Al-Si-Cu 之 MIS 電容結構在累積模

式下固定偏壓測試 No RTA 的 I-t 圖

圖3-2.4 TaN/HfSiOx (16 nm)/p-sub/Al-Si-Cu 之 MIS 電容結構在累積模

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 3-2.5TaN/HfSiOx (16 nm)/p-sub/Al-Si-Cu 之 MIS 電容結構,閘極偏

壓為累積模式且固定偏壓(VG = -9.4V),900℃RTA 與 No RTA 之韋伯

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

3-3 矽氧化鉿(HfSiO

x) 與氮氧化矽鉿(HfSiON)崩潰機制

上述提到關於 HfSiOx與HfSiON 氧化層材料的崩潰行為,發現經 過氮氣環境下熱退火處理後的 HfSiON 氧化層得到較好的元件特性, 但其崩潰機制仍然需要進一步探討。 在 HfSiOx的崩潰機制方面,可由圖 3-2.1 推測,初期的閘極漏 電流是由電子的電荷捕捉所造成漏電流減少,而後電子的陷位產生(Electron Trap Creation),當測試時間增加,便造成永久性崩潰(Hard

Breakdown,HBD),其崩潰機制如圖 3-3.1 所示。而 HfSiON 則是在 電子捕捉後,發生少數暫時性崩潰(Soft Breakdown,SBD )與漸進式 崩潰(Progressive Breakdown,PBD),最後產生多數直接永久性崩潰, 如圖 3-3.2 所示。 另外,觀察 HfSiON 的崩潰機制,可由崩潰電壓做初步的分析。 由圖 3-3.3 觀察出 HfSiON 的崩潰行為,當正偏壓作用於元件時,

nMOS 的 反 轉 模 式 (Inversion Mode) 與 pMOS 的 累 積 模 式

(Accumulation Mode)皆崩潰於約 4V 的電壓,而 nMOS 的反轉模式卻

觀察出較為不同的崩潰行為。

由於 nMOS 反轉模式發現許多的崩潰行為在 4V 後發生,因此利

用穿透式電子顯微鏡(TEM)得到 nMOS 崩潰後反轉模式與累積模式

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

Induced Expitaxy,DBIE)現象[4]。圖 3-3.4(a)所示,反轉模式的磊晶

方向是由矽基板往閘極的方向進行,反之累積模式的磊晶方向由閘極 往矽基板的方向進行,如圖 3-3.4(b),且累積模式的崩潰區域大於反 轉模式。 另外,將反轉模式結構圖放大後可發現許多較小的崩潰點[4],推 測這是造成 nMOS 反轉模式下複數崩潰事件的原因。 圖 3-3.1 HfSiOx (16 nm)高介電層的崩潰機制 e -HfSiOX (IL) Si 由於電子電荷的捕捉現象,使 初期漏電流有降低現象。 當High-k 層路徑形成後,大電 流經由路徑至介面層(IL)。 隨電壓增加,缺陷在High-k 層 逐漸增加。 大電流導致介面層(IL)在 High-k 層崩潰瞬間同時發生崩潰。 帶正電的缺陷 捕捉電子的缺陷 本身存在及偏壓導致的缺陷 HfSiOX (IL) Si e -HfSiOX (IL) Si e -HfSiOX (IL) Si e

-氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究 圖 3-3.2 HfSiOx (16 nm)經過 900℃RTA 後的崩潰機制 初期的微結晶現象使漏電流 產生。 當High-k 層形成路徑後,大電 流經由路徑至介面層(IL)。 隨電壓增加, High-k 層產生缺 陷,並逐漸形成路徑。 High-k 層崩潰的同時,大電流使 介面層(IL)緊接著 High-k 層崩潰。 晶格 缺陷 HfSiON (IL) Si e- e -(IL) Si HfSiON HfSiON (IL) Si e -HfSiON (IL) Si e

-氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

圖 3-3.3 nMOS 與 pMOS 的 Jg-Vg曲線圖[4]

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

第四章 結論

由量測結果可發現,未經 N2 RTA 處理的元件,由於較多的陷阱 與缺陷在氧化層中導致較大的漏電流以及較低的崩潰電壓,也造成遲 滯效應與遲滯電壓偏移量增加。而經過 N2 RTA 處理後,氧化層中的 陷阱與缺陷均得到改善,漏電流也因此減少,同時遲滯效應與能帶偏 移量也因氧化層特性改善而得到較佳的結果。接著,利用韋伯分佈圖 觀察元件的可靠度,發現經過 N2 RTA 處理後的元件,其 TDDB 的特 性也較佳。 接著,由實驗推論 HfSiOx的崩潰機制,原先帶負電的電子電荷 捕捉,使最初的閘極漏電流減少,當電子陷位產生後,元件隨著時間 增加導致永久性崩潰。另外,經過N2 RTA 處理後的 HfSiON 氧化層, 由於微結晶現象,使初期漏電流稍微提升。當電子捕捉行為發生後, 接著便伴隨著少數的暫時性崩潰或漸進式崩潰,最後導致多數的直接 永久性崩潰產生。 由於累積模式下的氧化層,電子由閘極注入的方式在高介電係數 材料上產生缺陷,且缺陷隨時間而增加並產生漏電流路徑,當漏電流 過大會導致高介電係數材料與介面層同時崩潰。因此推測由高介電係 數材料先發生崩潰,緊接著發生介面層崩潰。此現象也是造成測量 TDDB 特性圖的崩潰發生時,直接產生永久性崩潰的原因。氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

參考文獻

[1]Hokyung Park,“The Effect of Nanoscale Nonuniformity of Oxygen Vacancy on Electrical and Reliability Characteristics of HfO2 MOSFET Devices,”IEEE ELECTRON DEVICE LETTERS,pp.54-56(2008)

[2]陳宏瑋、趙天生,“高介電係數閘極介電層材料在奈米電子元件上之應用~材料 特性與製程的挑戰,”電子月刊,第九卷,第九期,pp.126-134(2003)

[3 ] Motoyuki Sato,“CATHODE ELECTRON INJECTION BREAKDOWN MODEL AND WORK FUNCTION DEPENDENT TDDB LIFETIME FOR HIGH-K / METAL GATE STACK PMOSFETS,” IEEE CFP08RPS-CDR 46th Annual International Reliability Physics Symposium, Phoenix, pp.335-340(2008) [4] Motoyuki Sato,“Impact of Polarity of Gate Bias and Hf Concentration on Breakdown of HfSiON/SiO2 Gate Dielectrics,”IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 54, NO. 9, SEPTEMBER 2007

[5] R. Duschl, “Reliability aspects of Hf-based capacitors: Breakdown and trapping effects,” Microelectronics Reliability 47 ,pp.497–500 (2007)

[6]張冠群,“晶圓式氧化膜可靠性評估技術之發展與應用,“電子發展期刊,176 期,pp.46-59(1993)

氮氣熱退火處理對矽氧化鉿高介電質可靠度之研究

![圖 2-1.1 能隙與介電係數關係圖[2]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8922272.263652/12.892.225.664.200.986/圖211能隙與介電係數關係圖2.webp)

![圖 2-5.1 氧化膜測試模式, I-V 與 C-V 量測為 RVS、I-t 量測為 CVS[6]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8922272.263652/21.892.160.735.115.1093/圖251氧化膜測試模式IV與CV量測為RVSIt量測為CVS6.webp)

![圖 3-3.3 nMOS 與 pMOS 的 J g -V g 曲線圖[4]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8922272.263652/35.892.215.672.166.429/圖333nMOS與pMOS的JgVg曲線圖4.webp)