底膠填充於金對金覆晶接合高頻元件封裝可靠度影響之研究

全文

(2) 底膠填充於金對金覆晶接合高頻元件封裝可 靠度影響之研究. 研究生:劉伯俊. 指導教授:張翼博士. 國立交通大學半導體材料與製程設備專班 摘. 要. 由於近來行動通訊品質的提高,通訊頻寬的需求量大增,衍生而出許多 的通訊規格,例如:GPRS、3G、Bluetooth、802.11n…等,且於終端的使用 者對於產品之輕、薄、短、小、久(產品可靠度)的要求越來越重視,所以使 射頻積體電路封裝技術的挑戰越來越大。封裝對元件的功能主要在於傳遞電 源能量及電路訊號、保護元件結構、提供散熱管道,其中又以電能、電訊的 傳輸為射頻積體電路相當重要的考量。由於射頻電路工作頻率相當高,其原 有的低頻電路特性則因頻率的增加而有所改變,以簡單的單一導線為例,原 為傳輸訊號導通與不導通的判定,隨著工作頻率的提升其寄生電感 (Parasitic Inductance)、肌膚效應(Skin Effect)及寄生電阻(Parasitic Resistance) …等現象。但是利用覆晶的方式連結射頻積體電路與基板,其 I.

(3) 覆晶接合封裝的單晶微波積體電路與裸晶的電性表現幾乎相同,固有許多研 究單位投入覆晶封裝技術。 本論文研究方向是針對 Gold-to-Gold 之覆晶封裝高頻元件,做高頻特 性、可靠度及機械強度之試驗,並且分析各種不同條件下,特性之變化。. II.

(4) Effects of Underfills on Gold-to-Gold Reliability for High Frequency Flip-Chip Packaging. Student:Po-Chun, Liu. Advisors:Dr. Yi, Chang. Master Degree Program of Semiconductor Material and Processing Equipment of National Chiao Tung University. ABSTRACT. As the proliferation of high-quality mobile communication increased recently, the demand of large bandwidth of communication increased recently, too. As a result, several communication specifications was developed, such as GPRS、3G、Bluetooth、 802.11n…etc. Furthermore, miniature and durable portable products are more and more valued by ender users. The challenge of high frequency package is more and more tough. The main functions of package are Power Distribution、Signal Distribution、Protection and Heat Dissipation. The most important function of them is Signal. III.

(5) Distribution. Due to the high work frequency of high frequency device, the alterations of frequency have modified the characteristic of normal device. The statuses including Parasitical Inductance、Skin Effect、Parasitical Resistance are different in different working frequency devices. With the application of utilizing the Flip-Chip package to connect the high frequency device and substrate, this joint development represents the almost same result of Power Distribution in SOT and Die. Therefore, the result attracts a lot of research units to develop and study the tech of Flip-Chip package. The thesis directions are to test the Gold-to-Gold Flip-Chip package of high frequency devices in the first section. The tests include high frequency property、reliability、and mechanical test. In the second section, are to analyze the variations of property in different conditions.. IV.

(6) 誌謝 本論文得以完成,首先要感謝我的指導教授--張翼博士的悉心指導。 在經歷六年的職場生活後回到學校重拾書本,對於學生的生活變的有點陌生,幸 賴張教授於忙碌之餘,仍然抽空給予學識上的指正並分享他在於科學與工 程專業領域上的智慧與經驗。從研究方向的擬定、研究方法的啟發與指導,不 斷督促精進,對我實在是受益匪淺,由衷感謝浩瀚恩師。另外感謝諸位口試委 員抽空遠從各地趕來參與口試,並在我的研究上 給予諸多寶貴的建議與 指正,使本論文更臻完整。 此外,我要感謝化合物半導體元件實驗室(CDS. Lab)的成員,其. 中準博士吳偉誠、許立翰不厭其煩細心指導我完成碩士論文,胡吟竹…等CSD Lab的各個成員於實驗上的協助及共同討論,感謝之意無法用三言兩語道盡。另 外,我要感謝葉坤泰先生協助切割我們實驗的樣本、謝翰坤先生協助測試元 件可靠度的相關實驗,解決了我們許多的困擾,以及其他我所無法一一提 到協助我的人。 最後,我還要衷心感謝我的家人,感謝他們關懷與支持,提供我生活所 需的一切,讓我能得以無後顧之憂地沈浸於學術領域中,順利完成碩士學 位。謹將此研究論文獻給支持我的家人。. V.

(7) 目. 錄. 中文摘要……………………………………………………………….Ⅰ 英文摘要………………………………………………………………Ⅲ 誌謝…………………………………………………………………….Ⅴ 目錄…………………………………………………………………….Ⅵ 表目錄………………………………………………………………….Ⅷ 圖目錄………………………………………………………………….Ⅸ 一、 緒 論 … … … … … … … … … … … … … … … … … … … … … … … … 1 1.1. 前言…………………………………………………………1. 1.2. 研究動機與目的……………………………………………2. 二、 Introduction……………………………………………………….3 2.1 Chip-level interconnect techniques………………………..3 2.1.1 打線接合(Wire bonding)……………………………4 2.1.2 覆晶(Flip chip)……………………………………….6 2.2 Interconnections in flip-chip packaging system…………..9 2.2.1 錫鉛凸塊(Solder bumps)…………………..……...9 2.2.2 異方性導電膠膜(ACF)…………...…………..…….11 2.2.3 金凸塊(Gold-to-Gold bumps)……………..………13 2.3 可靠度概論…………………………………………..……..15. VI.

(8) 2.3.1 瞬間故障曲線………………………………..……...15 2.3.2 可靠度測試方法…………………………….………16 三、 實 驗 步 驟 與 分 析 分 法 … … … … … … … … … … … … … … … … … 1 9 3.1 實驗步驟及試片準備………………………………………19 3.1.1 Substrate gold circuits and gold bumps ………….20 3.1.2 Chip gold circuits……………………………..……..22 3.1.3 Flip-chip assembly…………………………………23 3.1.4 Underfilling………………………………………….25 3.2 Mechanical and reliability tests…………………………..26 3.2.1 Shear force test.……………………………………26 3.2.2 Thermal cycling test…………………..……………28 3.2.3 吸濕測試…………………………………………….29 3.2.4 爆米花測試(Popcorn test)...……………………….30 3.2.5 Electric resistance measurement…………………32 3.2.6 RF measurement…………………………………...33 四、 實 驗 結 果 討 論 … … … … … … … … … … … … … … … … … … … … 3 5 五、 結 論 … … … … … … … … … … … … … … … … … … … … … … … … 4 6 六、 參 考 文 獻 … … … … … … … … … … … … … … … … … … … … … … 4 8. VII.

(9) Table Captions. 二、Introduction Table 2.1 覆晶接合及打線接合比較 Table 2.2 各種方式覆晶接合優缺點比較. 三、實驗步驟與分析方法 Table 3.1 常用材料熱膨脹係數 Table 3.2 Moisture Sensitivity Levels. 四、結果與討論 Table 4.1 Electric resistance of flip chip without underfill Table 4.2 Electric resistance of flip chip with underfill Table 4.3 Without underfill 覆晶接合吸濕重量變化 Table 4.4 With underfill 覆晶接合吸濕重量變化. VIII.

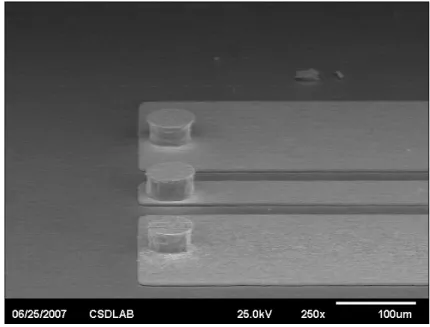

(10) Figure Captions. 二、Introduction Figure 2.1 電子構裝層級 Figure 2.2 打線接合流程 Figure 2.3 覆晶接合流程 Figure 2.4 電鍍法錫鉛凸塊製作流程 Figure 2.5 錫鉛凸塊覆晶接合 Figure 2.6 異方性導電膠膜接合流程 Figure 2.7 電鍍法金凸塊製作流程 Figure 2.8 故障發生率函數曲線. 三、實驗步驟與分析方法 Figure 3.1 實驗步驟 Figure 3.2 基板金屬線路製作 Figure 3.3 SEM image of the thick PR Figure 3.4 基板金凸塊製作 Figure 3.5 基板金屬線路及金凸塊完成 Figure 3.6 SEM image of the gold circuits and gold bumps. IX.

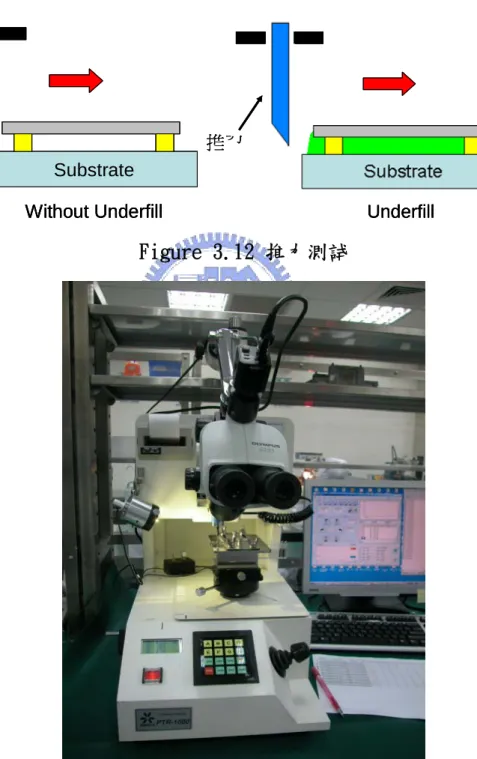

(11) Figure 3.7 晶粒表面金屬線製作 Figure 3.8 金凸塊覆晶接合 Figure 3.9 SEM image of the gold bumps flip-chip Figure 3.10 底膠填充流程 Figure 3.11 SEM image of the flip-chip structure after underfill Figure 3.12 推力測試 Figure 3.13 PHESCA bonding tester Figure 3.14 Thermal cycling test 升降溫曲線 Figure 3.15 KSON thermal cycling tester Figure 3.16 吸濕測試流程 Figure 3.17 KSON 恆溫恆濕機 Figure 3.18 爆米花試驗流程 Figure 3.19 電阻值量測 Figure 3.20 DC 阻抗量測器 Figure 3.21 RF 測試機. 四、結果與討論 Figure 4.1 TCT 前後有/無底膠填充 shear force 比較 Figure 4.2 無底膠填充覆晶接合於 TCT 測試電阻值變化. X.

(12) Figure 4.3 有底膠填充覆晶接合於 TCT 測試電阻值變化 Figure 4.4 有/無底膠填充覆晶接合高頻特性(S11)差異 Figure 4.5 有/無底膠填充覆晶接合高頻特性(S21)差異 Figure 4.6 高頻元件線路設計變更 Figure 4.7 高頻元件線路設計變更後之高頻特性 Figure 4.8 TCT 前後,有底膠填充覆晶接合高頻特性(S11)差異 Figure 4.9 TCT 前後,有底膠填充覆晶接合高頻特性(S21)差異 Figure 4.10 無底膠填充覆晶接合時間 VS 重量 Figure 4.11 有底膠填充覆晶接合時間 VS 重量 Figure 4.12 Popcorn 測試前後之電阻值變化. XI.

(13) 一、緒論 1.1 前言 隨著電子資訊產品效能表現不斷的提升、體積日益輕薄短小的發展趨 勢,現階段各封測產業積極朝向高腳數、高功率、體積小的方向演進。由於 這個緣故,所以近年來覆晶技術(Flip-Chip)已經廣泛運用在電腦資訊、光 通訊及消費性電子等模組零件封裝。應用覆晶封裝技術除了可以有效增加 I/O接腳數外,還可以縮小晶圓封裝後尺寸,有效降低系統組裝面積而達到 輕薄短小的目標。 在行動通訊品質要求的提高,通訊頻寬的需求量大增,因應而生的各項 新的通訊規範如GPRS、W-CDMA、CDMA-2000、Bluetooth、802.11n紛紛出籠, 其規格不外乎:更高的資料傳輸速率、更有效的調變方式、更嚴謹的雜訊規 格限定、通訊功能的增強及擴充,另外再加上消費者除了對終端產品“輕、 薄、短、小、功能多樣、外表美觀"的訴求為必要條件,另外對於產品的使 用壽命也是越來越重視。為了達成這些目的,各家廠商在產品射頻(Radio Frequency)、中頻(Intermediate Frequency)與基頻(Base Band)電路的整 合設計、主動元件的選擇應用、被動元件數目的減少、多層電路板內線路善 加運用等,投注相當的心血及努力,以求達到消費者的需求。尤其於產品的 可靠度上的提升也是不餘遺力,因為可靠度較佳的產品不僅可提升產品的競. 1.

(14) 爭力與附加價值,同時也可以提升製造產商的形象。. 1.2 研究動機與目的 封裝對元件的功能主要在於傳遞電源能量及電路訊號、保護元件結構、 提供散熱管道,其中又以電能、電訊傳輸為目的之高頻元件為相當重要的考 量。影響高頻元件覆晶封裝後高頻特性的因子有相當多,例如覆晶封裝方法 的選用(迴銲接合Re-flow bonding、熱壓接合Thermo-Compression bonding…)、製程參數(溫度、壓力、選用材料…)、封裝材料…等。本次研 究目的在於選用Gold-to-Gold覆晶的封裝方式並且填入底膠,分析並比較其 對高頻元件覆晶封裝特性、高頻應用極限、機械強度及可靠度之影響。另外, 針對高頻元件線路作設計變更,期待能夠解決底膠填充對於高頻特性的影 響,並且測試其高頻特性的極限。. 2.

(15) 二、Introduction 2.1 Chip-level interconnect techniques 於電子工業之中,除了半導體製造產業外,電子構裝工業也是不可或缺 的一塊,因為電子構裝的主要目的就是利用一個封裝體為一個引接的介面, 使內部電氣訊號可以透過封裝材料將之連接到基板而向外傳遞,並且提供矽 晶片免於受到外力與水/濕氣之破壞與腐蝕、並且提供電子元件所產生熱能 的散失途徑,避免元件過熱。 電子構裝依據與積體電路的遠近,分為幾個不同的層級[1],層級之間 的定義如下(Figure 2.1): 1. First level package:主要是將從晶圓切割下來的積體電路晶粒經 過線路接合之流程,將晶粒的電子訊號傳遞出去。此層級的代表接 合方式有打線接合、覆晶接合、捲帶式自動接合。 2. Second level package:將first level接合封裝好的電子元件,將 其接合到PCB上,形成電路卡或是電路板。此層級接合重要的考量為 印刷電路板的製作及電子元件與電路板的連接技術。其代表的接合 方式為SMT、PTH接合。 3. Third level package:此層級為將second level構裝出來的PCB板 或是驅動卡,構裝到主板上。. 3.

(16) Figure 2.1 電子構裝層級[2] 於first level package之接合技術中提供電氣傳導路徑有金線(使用於 wire-bonding)、bump(使用於Flip-chip)…等,藉由此不同連接的方式讓微 細的IC電路彼此作連結。由於所有的chip均需藉由此接合將訊號傳遞至外 界,故此次之研究即以first level interconnect為主要的研究重點。 2.1.1 打線接合(Wire bonding) 打線接合技術為最早被應用在電子元件封裝的技術,其首先為貝爾實驗 室於1957所發表,如今已經成為最主要的電路連接方式。打線的主要目的為 將晶粒上的接點以極細的金線(或是鋁線)連結到導線架上的內引腳,藉而將 IC晶粒之電路訊號傳輸到外界。打線接合所用的金屬線,主要有鋁線與金 線,金線線徑約20μm到100μm,使用於大部分的塑膠構裝銲線接合;鋁線 4.

(17) 線徑約在100μm到500μm,其主要應用於功率電晶體產品上。 打線接合分為二種方式:楔形接合(Wedge bonding) and 球點接合(Ball bonding)。楔形接合為使用頻率20~60kHz,振幅為20~200mm的超音波,藉音 波振動與迫緊壓力產生冷銲效應來進行銲接;球形接合為將金線(或鋁線)穿 過毛細管狀接合工具(Capillary tip,一般稱為瓷嘴或是鋼嘴),然後在金 屬線末端以電子點火燒灼成球,透過接合工具引導金屬球到第一銲點的位置 藉熱擴散接合效應完成球形接合(Ball bonding)。[3] 基本打線接合流程簡述如下(Figure 2.2): 1. 金線穿過Capillary tip(瓷嘴或是鋼嘴),然後燒結成一個金球; 2. 將燒結的金球置放於晶片銲墊上,加壓&給予超音波,使金球與銲墊 連接; 3. 將Capillary tip移至第二銲點,加壓&給予超音波,並且切斷金線, 完成連結。 Gold wire. Gold pad. Chip. Lead frame Press to make contact with heat and ultrasonic. Formation of molten metal ball. 5.

(18) Clamp closed with heat on to break the wire. Lead contact with pressure and heat. Figure 2.2 打線接合流程 打線接合有以下之優點: 1. 打線接合的參數可以被精準的控制。 2. 只要適當控制製程條件,其可靠度的問題大多可以被解決。 3. 每條線連接打線的速度可以達到100-125ms。 4. 全自動打線機器被發展完備,打線容易。 5. 每根打線pitch間距可達50μm。 6. 可以依據不同的工程、製造需求,選擇不同的打線工具及材料。 7. 技術成熟、價格低廉。 不過,隨著電子產品的不斷創新及進步,打線接合漸漸不能符合高I/O、 較小的體積、較快的熱量散失…等特性,所以目前僅能適用於一般傳統的接 合封裝。 2.1.2 覆晶(Flip chip) 由於近年來電子產品強調輕、薄、短小、高速、高腳…數等特性,以導 線架為基礎的傳統金屬線接合封裝型態將漸漸不適用,所能應用的範圍也漸 6.

(19) 漸僅限用於低階、低單價、體積大的封裝產品。使用覆晶封裝技術可大幅縮 小IC封裝後的體積,減少訊號的延遲及雜訊的產生…等優點。因此漸漸地取 代了傳統打線接合(Wire bonding)技術,此技術也被廣泛使用在需要高傳輸 速度的處理器、行動通訊元件(例如藍芽模組)…等較高階的封裝需求上。 覆晶封裝(Flip chip package)技術的概念為IBM於1960年代首先提出, 其利用蒸鍍法將5Sn/95Pb沈積於Cr/Cr-Cu/Cu之UBM上形成高溫錫鉛凸塊,並 應用在最新的System/360之連結上,IBM稱此技術為控制破裂晶片接合 (Controlled collapse chip connection),通常以C4簡稱之。C4製程以蒸 鍍法製作高鉛含量的凸塊,將晶片與耐高溫的陶瓷基板直接接合。由於其封 裝的型式為晶粒正面翻覆朝下,藉由在晶粒上所植之凸塊與陶瓷基板直接連 接,故稱為覆晶。(Figure 2.3). Substrate. Substrate. 於substrate上長bump(Gold or solder). 將Chip上的pad對準substrate上的bump. Substrate. Substrate. 對準接合. Flip-chip complete. Figure 2.3 覆晶接合流程 綜合以上所述,覆晶封裝有以下的優點[4]: 1. 可以縮小封裝後的尺寸:晶片封裝前後的大小差不多,可應用於需 7.

(20) 要輕、薄、短小的產品。 2. 可降低晶片與基板間的電子訊號傳輸距離,改良電性功能,可應用 於高速元件的封裝。 3. 可改善高頻訊號的傳輸:覆晶接合應用於高頻元件上,其有較低的 寄生效應,可以大幅的改善高頻訊號的傳輸特性。 4. 其他的優點: a. 解決電磁相容(EMC)與電磁干擾(EMI)等問題。 b. 適用於高I/O需求的裝置。 c. 可解決散熱的問題。 綜合以上所述,比較覆晶接合及打線接合的優缺點如下(Table 2.1): Table 2.1 覆晶接合及打線接合比較 覆晶接合. 打線接合. 晶 片 尺 寸 (Chip 封裝後體積. 傳統大小 scale) 散熱途徑較長:透過 散熱途徑較短:利用. 散熱性. 環氧樹脂、晶片、金 凸塊及底膠散熱 線來散熱. 製程適用性 適用I/O數. 製程複雜. 技術發展較成熟. 低腳數~1000pin以 上 一般為300pin以下 8.

(21) 均可適用 由於覆晶封裝有以上的特點,並且由於訊號傳遞的路徑較短,故擁有較 低高頻訊號的損失。所以此次高頻元件的封裝接合,即選擇覆晶接合封裝為 此次的chip-level接合的方式[5]。. 2.2 Interconnections in flip-chip packaging system 目前覆晶接合封裝主流接合方式有三種:錫鉛凸塊(Solder bumps)、異 方性導電膠膜(ACF)接合、金凸塊(Gold-to-Gold bumps),此三種接合方式 的流程與接合特性,將於下詳述。 2.2.1 錫鉛凸塊(Solder bumps) 錫鉛凸塊為最早應用於覆晶技術中,由於錫鉛接合技術已經發展許久, 故此也為最成熟、最廣泛應用的接合技術。於錫鉛凸塊覆晶接合技術中,錫 鉛凸塊的製作為覆晶技術的成敗關鍵,目前常見的製作方式為電鍍法 (Electroplate)及印刷法(Printing),其製作方式如下(Figure 2.4): 電鍍法: 1. 晶片清洗:清洗晶片表面,使其乾淨不受污染。 2. UBM沈積:UBM主要的功能為a.附著(Adhesion)/擴散阻絕(barrier) layer;b.潤濕(Wetting) layer及保護(Protection) layer。 3. 微影成像:光阻塗佈、曝光、顯影,將需要的圖像轉印到wafer上面。 9.

(22) 4. 錫鉛電鍍:利用電鍍法獲得高密度(高品質)與細間距的錫鉛凸塊。 5. 回銲成球:將光阻去除,同時去除底層的UBM,把錫鉛凸塊過回銲並 清洗,得到錫鉛凸塊。 Mask. Passivation Pad Wafer清洗. Sputter UBM Layer. PR coating & exposure. 有電鍍法&印刷法. 曝光&顯影. Electroplated Solder Bump. PR Stripping. 後續使用此Solder bumps 去做Solder flip chip bonding UBM Remove. After Reflow. Figure 2.4 電鍍法錫鉛凸塊製作流程 印刷法: 1.晶片清洗:清洗晶片表面,使其乾淨不受污染。 2.UBM沈積:UBM主要的功能為a.附著(Adhesion)/阻絕(barrier) layer;b.潤濕(Wetting) layer及保護(Protection) layer。 3.錫膏印刷轉印:利用鋼版印刷(Stencil Printing)的方式將錫鉛凸塊 轉印到pad上。 4.回銲成球:將錫鉛凸塊迴銲,即得所需要的錫鉛凸塊。 完成錫鉛凸塊後,即可將其應用在覆晶接合上如下(Figure 2.5):. 10.

(23) UMB Passivation. TSM. Solder bump. Pad. Flip process. Bonding process Figure 2.5 錫鉛凸塊覆晶接合 錫鉛凸塊優點: 1. 自動對位:使用錫鉛凸塊,當晶片放置在排列好之溶解銲料上,晶片 會自動對位,擴大製程誤差的容許範圍。 2. 製造性良好。 2.2.2異方性導電膠膜(Anisotropic conductive film, ACF)[6] 異方性導電膠膜(ACF),兼具單向導電及膠合固定的功能。其組成主要 包含導電粒子及絕緣膠材兩部分,上下各有一層保護膜來保護主成分。使用 時先將上膜(Cover Film)撕去,將ACF膠膜貼附至Substrate的電極上,再 把另一層PET底膜(Base Film)也撕掉。在精準對位後將上方物件與下方板 材壓合,經加熱及加壓一段時間後使絕緣膠材固化,最後形成垂直導通、橫 11.

(24) 向絕緣的穩定結構。異方性導電膠膜使用在Flip chip上的製程流程如下 (Figure 2.6): 導電粒子. 保護膠材 ACF Substrate. 異方性導電膠膜. 溫度、壓力、時間. 導通. Substrate. Substrate. 壓合. Bump & Chip導通. Figure 2.6 異方性導電膠膜接合流程[7] ACF有以下的優點: 1. 製程溫度較低。 2. 減低環境對flip chip的影響。 3. 改善製程的特性:製程中不使用flux,故無清潔之問題。 ACF的缺點: 1. 較低的電子導電率。 2. 較不穩定的連結阻抗:ACF中之導電粒子扮演垂直導通的關鍵角色, 膠材中導電粒子數目越多或導電粒子的體積越大,垂直方向的接觸 電阻越小,導通效果也就越好。但是,過多或過大的導電粒子可能 會在壓合的過程中,在橫向的電極凸塊間彼此接觸連結,而造成橫 12.

(25) 向導通的短路,使得電氣功能不正常。 3. 重工困難。 4. IC腳距小的使用困難:隨著IC的腳距(Pitch)持續微縮,橫向腳位 電極之凸塊間距(Space)也越來越窄,大大地增加ACF在橫向絕緣 的難度。 2.2.3金凸塊(Gold-to-Gold bumps) 由於以錫鉛凸塊來進行覆晶接合,其存在著製程複雜、需使用助焊 劑導致迴銲製程後的殘留雜物需以清洗劑清洗排除、鉛的物染…等缺點;且 於高頻的應用上,錫鉛凸塊的性質較不穩定,容易影響高頻的特性,故後續 有金凸塊的技術發展應用於高頻元件上。金凸塊[8]基本製程如下(Figure 2.7): Mask. Passivation Pad Wafer清洗. Sputter UBM Layer. 曝光&顯影. PR coating & exposure. Au. Au. Electroplated Gold Bump. PR Stripping. 後續使用此Gold bumps去做 Gold-to-gold flip chip bonding. Au UBM Remove. Figure 2.7 電鍍法金凸塊製作流程 金凸塊(Gold-to-Gold bumps)有以下的優點[9]: 13.

(26) 1. 電子傳導性佳。 2. 與高頻元件表面銲墊材料相同,較無表面接合介面之問題。 3. 較少的擴散與合金反應問題。 4. 性質較穩定,表面不易生成氧化物,有利高頻訊號的傳遞,避免訊 號損失。(由於高頻訊號的傳遞大多於導線的表面,故表面若有氧化 物的生成,將對訊號的傳遞產生不良的影響。 綜合以上所述,比較錫鉛凸塊、異方性導電膠膜以及金凸塊三種覆晶接 合的優缺點如下(Table 2.2): Table 2.2 各種方式覆晶接合優缺點比較 錫鉛凸塊. ACF. 金凸塊. 無須使用助銲劑. 無須使用助銲劑. 製程較簡單. 製程複雜. 需使用助銲劑,容易造 成污染 製程較複雜. 接點容易有硬脆的問 接點導電性較低,且連 接點導電性良好 題. 接電阻不穩定 可重工. 重工困難. 不可重工. 比較以上錫鉛凸塊、異方性導電膠膜以及金凸塊三種覆晶接合的方式, 由於錫鉛凸塊有清潔及污染的問題以及異方性導電膠膜有不穩定的連結阻 抗,故此兩種接合技術不適用於高頻元件的覆晶連結使用。金凸塊由於有電 14.

(27) 子傳導性佳、性質穩定,不易產生氧化物、低訊號的損失…等優點,故適合 使用在高頻元件覆晶連結的使用。. 2.3 可靠度概論 可靠度的觀念起始於二次大戰期間,德國在研製 V-1 火箭時,對於主要 設計理念已有系統強度決定其中最弱環節的觀念,而個別元件的良莠會直接 影響到整個系統的表現,所以在當時被視為相當重要的課題。自從 1952 年 美國電子設備可靠顧問團(AGREE)提出報告之後,其以對電子裝備進行研究 所得到的結論為基礎,並依此結論定義可靠度:產品於既定的時間內,在特 定的使用環境條件下,執行特定的功能,成功完成工作目標的機率。 2.3.1 瞬間故障率曲線 一般而言,產品的故障發生率函數曲線(Figure 2.8),呈現出類似浴缸 的形狀,又稱之為浴缸曲線[10]。該曲線大致可分為三個階段,首先是(a) 初始故障期(period of early failures),於此初期產品故障率較高的原 因,主要源自生產缺陷,初始故障率也會隨開始使用時數漸增而急速下降。 接著到達(b)偶發故障期(period of random failures),在此期間,產品 在某一時段內的故障率,一直維持不變。最後進入(c)老化故障期(period of aging failures),產品在某一時段內的故障率會隨時間而持續增加,直到 所有的產品全部故障為止。 15.

(28) Figure 2.8 故障發生率函數曲線 2.3.2 可靠度測試方法 可靠度測試的目的主要是為瞭解產品於設計階段中,藉由許多不同的試 驗,瞭解產品當時之可靠度水準,並將其提供決策者參考,以掌握產品的特 性。但是由於各國與各個產業之間,其測試方式與標準均不同,故有許多國 際標準組織制定了測試的標準,如電子設備工程聯合委員會(Joint Electron Device Engineering Council,簡稱JEDEC)[11]、日本電子工業協會 (EIAJED)[12]…等,其以過去長久以來IC設計、製造和使用的經驗為基礎, 制定了IC測試條件,如溫度、濕度、電壓、偏壓、測試方法…等。藉由這些 標準獲得測試結果,使得IC測試變得有章可循,有法可依。 以下簡介各項不同可靠度試驗的方法: 1.. 使用壽命測試(Life test items):測試產品的穩定性&耐久性。 16.

(29) 適用規範JESD22-A-108/EIAJED-4701-D101。 2.. 環境測試項目(Environment test items): a. 預處理測試(Precondition Test):測試IC使用前在一定的濕度、 溫度條件下儲存的可靠度,也就是IC從生產到使用之間儲存的可 靠度。適用規範JEDEC-JSTD-020。 b. 加速式溫濕度及偏壓測試(Temperature Humidity Bias Test, THB):評估IC產品在高溫、高濕偏壓條件下,對濕氣抵抗能力。 適用規範JESD22-A101/EIAJED-4701-D122。 c. 高加速溫濕度及偏壓測試(Highly Accelerated Stress Test, HAST):評估IC產品在偏壓下高溫、高濕、高氣壓條件下對濕度 的抵抗能力。適用規範JESD22-A110。 d. 高溫蒸煮試驗(Pressure Cook Test, PCT):評估IC產品在高溫、 高濕、高氣壓條件下對濕度的抵抗能力。適用規範 JESD22-A102/EIAJED-4701-B123。 e. 高低溫循環試驗(Thermal Cycling Test, TCT):評估IC產品中 具有不同熱膨脹係數的金屬之間界面的接觸良率。適用規範 JESD22-A104/EIAJED-4701-B-131。 f. 高低溫衝擊試驗(Thermal Shock Test, TST):透過快速溫度的 切換,評估IC產品中具有不同熱膨脹係數的金屬之間界面的接觸 17.

(30) 良率。適用規範JESD22-B106/EIAJED-4701-B-141。 g. 高溫儲存試驗(High Temperature Storage Life Test):評估IC 產品於實際使用之前,在高溫條件下保持幾年不工作條件下的生 命時間。 由於電子元件對於濕氣相當的敏感,濕氣吸收到內部為半導體構裝最大 的問題。當元件吸收濕氣後,其若暴露於回流銲接的環境中,當溫度升高, 其內部的濕氣將會產生足夠的蒸氣壓,進而損傷元件。於一些嚴重的狀況 下,蒸氣會使構裝元件內部產生裂紋,最嚴重的狀況會使元件鼓脹或是爆 裂,一般稱之為爆米花效應(Popcorn effect)。故於實驗中,特別針對構裝 元件的吸濕狀況、爆米花效應、高低溫循環等項目做測試,以期瞭解元件吸 濕的效應及晶片與基板之間填充底膠對其金屬接觸的影響狀況。. 18.

(31) 三、實驗步驟與分析方法 3.1 實驗步驟及試片準備 本論文的研究,是將高頻元件利用金凸塊來做覆晶接合,然後填入底 膠,利用推力機來測試覆晶接合的力量大小,瞭解其機械強度。之後再利用 一連串的可靠度測試方法來瞭解此金凸塊覆晶接合後的高頻元件是否可以 符合可靠度中的環境測試。實驗步驟如下(Figure 3.1):. Figure 3.1 實驗步驟. 19.

(32) 3.1.1 Substrate gold circuits and gold bumps 本實驗利用氧化鋁作為基板[13],首先於氧化鋁基板表面先鍍上擴散阻 絕層,然後再來將需要的金屬線及金凸塊轉印到基板表面,製作的步驟如下 (Figure 3.2、Figure 3.4、Figure 3.5): o. o. 1. 於Al2O3基板上先鍍上一層Au(500A )&Ti(300A )。Ti主要的功能為附 著層及diffusion barrier;Au主要作為金屬導線及金凸塊的seed layer。 2. 於晶片上塗佈上一層薄光阻(S818), 3. 利用電鍍法於光阻未覆蓋的位置鍍上金屬。 Mask Au(500A°) Ti(300A°) Substrate. Thin PR (S1818). Al2O3. Substrate. PR coating & exposure. Au. Substrate. Substrate. 曝光&顯影 (光阻去除). Gold electroplate (Substrate gold line). Figure 3.2 基板金屬線路製作 4. 移去光阻,即完成金屬導線之圖案轉移。 5. 於晶片上塗佈上一層厚膜光阻(PR type:S818,Figure 3.3),經過曝 光、顯影,定義出金凸塊的位置。(此位置連接金屬導線的一端) 20.

(33) 60μm. Figure 3.3 SEM image of the thick PR 6. 利用電鍍法將未有光阻覆蓋的位置鍍上金凸塊。. Mask Thick PR (S1818) Substrate. Substrate PR coating & exposure. Substrate. Substrate. 曝光&顯影(光阻去除). Gold electroplate (Bump). Figure 3.4 基板金凸塊製作 7. 移去光阻,即完成金凸塊。 o. o. 8. 去除未有金屬導線及金凸塊覆蓋的Au(500A )&Ti(300A )層。(去除 o. o. Au(500A )使用KI/I2溶液;去除Ti(300A )使用HF/H2O(1:100)溶液). 21.

(34) Substrate. Substrate. 光阻去除. 去除Au(500A°):KI/I2,solution 去除Ti(300A°):HF/H2O(1:100). Figure 3.5 基板金屬線路及金凸塊完成 經過以上步驟,即完成Al2O3基板金屬導線及金凸塊的製程(Figure 3.6)。. Figure 3.6 SEM image of the gold circuits and gold bumps 3.1.2 Chip gold circuits 取用高頻元件,使其經過一連串的微影、電鍍等製程,將所需要的金屬 線圖案轉印到高頻元件的表面。其製程流程如下(Figure 3.7): 1. 將高頻元件晶粒表面覆蓋上一層光阻(S818)。 2. 經過曝光、顯影,定義出金屬導線的位置。 3. 利用電鍍法於光阻未覆蓋的位置鍍上金屬。. 22.

(35) 4. 去除光阻後,晶粒表面的金屬導線線路即完成。. Mask PR (S1818) High frequency chip. High frequency chip. PR coating & exposure. Au. High frequency chip 曝光&顯影 (光阻去除). High frequency chip Gold electroplate (Substrate gold line). Au. High frequency chip. Chip side view Chip top view. Figure 3.7 晶粒表面金屬線製作 3.1.3 Flip-chip assembly 取用完成金屬線路&金凸塊的基板及chip,進行覆晶接合,使chip的訊 號得以傳遞出去。我們選用熱壓法來做覆晶接合,製作方式如下(Figure 3.8、Figure 3.9): 1. 將上述所完成金屬導線的晶粒及完成金屬導線&金凸塊的基板各自 放於300℃的熱板上。 2. 晶粒翻轉倒置,且將晶粒上的金屬導線對準基板的金凸塊。 23.

(36) 3. 利用熱壓法,將晶粒壓在基板的金凸塊上180~240秒(使用的壓力為 10g/bump,故總共施加壓力為60g),使晶粒上得金屬導線與基板上 的金凸塊接合。(覆晶接合後的高度約20~30μm) Bonding force: 6ea bump * 10g/ea = 60g. Gold bump. Hot plate High frequency chip. Up hot plate T:300℃ Bump高度20~30μm. Substrate Down hot plate T:300℃. Hot plate. Figure 3.8 金凸塊覆晶接合. Figure 3.9 SEM image of the gold bumps flip-chip. 24.

(37) 3.1.4 Underfilling[14] 將完成覆晶接合後的元件,利用點膠的方式來填滿晶片與基板之間的空 隙。其利用毛細現象的原理,讓膠流動並且填滿空隙,此種製程稱為底膠填 充(Underfill)(Figure 3.10、Figure 3.11)。. Substrate. Substrate. 利用毛細現象,將underfill膠材吸附至chip底下,直至填滿為止. Underfill Complete Figure 3.10 底膠填充流程. Figure 3.11 SEM image of the flip-chip structure after underfill 25.

(38) 底膠填充除了可以固定晶片外,還有保護晶片與基板的接合,不受外界 影響破壞、提高元件的機械強度與可靠度(避免濕氣入侵及熱膨脹係數不同所 造成的破壞,常用材料熱膨脹係數如Table 3.1)…等功能。 Table 3.1 常用材料熱膨脹係數 Materials. CTE(ppm/oC) Chip. Si. 2.5. GaAs. 5.7 Bump. Au. 14.3. Cu. 17. Solder. 20~24 Substrate. Al2O3. 4. FR4. 18 Underfill. Epoxy resin. 20~40. 3.2 Mechanical and reliability tests 完成底膠填充的覆晶接合元件,我們將利用一連串機械力及可靠度試 驗,來瞭解經過此製程流程的高頻元件,其可靠度的狀況為何。 3.2.1 Shear force test[15] 覆晶接合封裝我們可使用晶粒推力機來測試其覆晶接合強度及底膠填充 黏著的強度,也可藉此方式來瞭解其抵抗外界的能力是否符合我們所預期。 測試的方式如下(Figure 3.12):. 26.

(39) 1. 將元件固定在治具上,調整推刀的位置,使推刀位於晶粒的前方適當 位置。 2. 推力測試:按測試鍵,推刀開始往晶粒方向移動,推動晶粒而獲得推 力的測試數值。(Bonding tester如Figure 3.13). 推刀. 推刀. Substrate Without Underfill. Underfill. Figure 3.12 推力測試. Figure 3.13 PHESCA bonding tester. 27.

(40) 3.2.2 Thermal cycling test (TCT)[16] 於溫度循環測試(TCT)中,我們將依照依據電子設備工程聯合委員會 JEDEC JESD22-A104國際標準,測試覆晶接合元件於125℃~-55℃的溫度循環 中,分別於200、400、600、800及1000 cycles下,高頻元件阻抗及高頻特性 的變化狀況。溫度循環測試溫度與時間的變化曲線(Profile)說明如下 (Figure 3.14): 1. 溫度於-55℃下,停留15分鐘。 2. 於5分鐘內,溫度由-55℃升溫至125℃。 3. 溫度於-125℃下,停留15分鐘。 4. 於5分鐘內,溫度由125℃降溫至-55℃。 重複上述1~4的步驟,即為一個循環。(TCT tester如Figure 3.15) 15 min. 125℃. 5 min. -55℃. 5 min 15 min. 15 min. Figure 3.14 Thermal cycling test升降溫曲線. 28.

(41) Figure 3.15 KSON thermal cycling tester 3.2.3 吸濕測試[17][18] 由於濕氣對於電子元件的不良影響相當大,故藉由吸濕測試瞭解元件覆 晶接合封裝的材料的吸濕狀況,測試步驟如下(Figure 3.16):. Figure 3.16 吸濕測試流程 1. 將元件置放在125℃的烤箱內,烘烤24小時,將元件內所有的濕氣全 部去除,然後置於電子天秤測量完全乾燥元件的重量多少。 2. 把已經去除濕氣的元件放置於設定為85℃/85%的恆溫恆濕chamber. 29.

(42) 內(恆溫恆濕chamber如Figure 3.17),使其吸收濕氣。 3. 每隔一段時間使用電子天秤量測重量,繪製元件重量與時間的關係 圖,即可瞭解吸濕量與時間的變化關係。. Figure 3.17 KSON恆溫恆濕機 3.2.4 爆米花測試(Popcorn Test) 由於元件完成封裝後,暴露於一般環境會持續吸濕,此吸收的濕氣於一 般的使用環境溫度下,還不會產生太大的問題。但在此元件完成封裝後出廠 到下游SMT廠使用,將會因為需經過紅外線迴銲爐的高溫(溫度約220℃),致 使吸收的濕氣體積急速膨脹,元件可能膨脹凸起或是產生裂縫。故透過爆米 花測試(Popcorn test)可以模擬元件完成覆晶接合封裝後,其離開乾燥的 環境後,多久時間內必須完成SMT的製程,以免發生因為吸收濕氣,而後續經 過SMT製程的高溫,造成構裝元件膨脹凸起或產生裂縫的情況。爆米花測試的 30.

(43) 流程如下(Figure 3.18):. Figure 3.18 爆米花試驗流程 1. 將元件置放在125℃的烤箱內,烘烤24小時,將元件內所有的濕氣全 部去除。 2. 依照JEDEC JSTD-020 Level 3的測試標準(各Level的測試標準參照 Table 3.2),將元件置放在設定為60℃/60%恆溫恆濕的chamber內, 使其連續吸收濕氣40個小時。. 31.

(44) Table 3.2 Moisture Sensitivity Levels. 3. 將連續吸收濕氣40小時的元件,使其連續三次經過220℃的紅外線迴 銲爐(IR reflow)。 4. 檢視覆晶封裝元件的外觀,確認是否有膨脹變形。 5. 將此元件測試DC阻值狀況,藉此可確認是否有開路/短路的狀況。 (Open/short test) 3.2.5 Electric resistance measurement 我們可以透過電阻值的量測(電阻值測試機如Figure 3.20),瞭解各階段 完成測試的sample其電阻值變化的狀況,且也可以藉此瞭解高頻訊號傳輸之 線路的狀況是否有產生任何的變化。電阻值測試的原理如下(Figure 3.19): 1. 於金屬線路兩端給予一定的電流值。 32.

(45) 2. 由step 1中給予的定電流,可以於金屬線路的兩端量測到電壓。 3. 將給予的電流值與量測到的電壓值,藉由R(電阻值)=V(電壓)/I(電 流),即可以計算出此金屬線路的電阻值。. 1.給予定電流 2.量測電壓. Substrate Figure 3.19 電阻值量測. Figure 3.20 DC阻抗量測器 3.2.6 RF measurement RF的測試使用VNA(Vector Network Analyzer),利用On-wafer probing measure method來量測高頻元件的S11(Return loss)及S21(Insertion 33.

(46) loss)。(RF特性量測機台如Figure 3.21). Figure 3.21 RF測試機. 34.

(47) 四、結果與討論 4.1 覆晶連接封裝推力比較 將3.1.3無底膠填充及3.1.4有底膠填充的覆晶接合元件,使用晶粒推力 機測試有/無底膠填充的覆晶接合的機械強度結果如下: Shear force(g). Without underfill. With underfill(Capillarity). 190.4. 2052. 後續將此組覆晶接合封裝送入如3.2.2的TCT chamber內(使用溫度條 件:-55℃~-125℃)放置1000 cycles,之後測試其覆晶接合的機械強度為: Shear force(g). Without underfill. With underfill(Capillarity). 19. 1584. 比較TCT前後 & without/with underfill的覆晶接合之機械強度如下 (Figure 4.1): Befor TCT Shear force(g) After TCT Shear force(g) 2052. 2500. Shear force(g). 2000 1584 1500 1000 500. 190.4. 19. 0 Without underfill. With underfill(Capillarity). Figure 4.1 TCT前後有/無底膠填充shear force比較 由 Figure 4.1 shear force 比較之數據中可得知有/無底膠填充的覆 晶接合的機械強度差異甚大,尤其是在 TCT 1000 cycles 後,無底膠填充 35.

(48) 的覆晶接合其機械強度更是大幅衰退了 10 倍之多,相較於有底膠填充的覆 晶接合機械強度僅衰退 22.8%。故底膠填充對於覆晶接合的機械強度影響相 當大。. 4.2 經TCT測試後,覆晶接合的電阻值的變化 將分別完成3.2.2 TCT測試(0、200、400、600、800、1000 cycles)的 測試樣本,量測金屬線路的電阻值,其變化狀況如下: 1. Electric resistance of flip chip without underfill 由無底膠填充的覆晶接合電阻值測試數據(Table 4.1)可知,#2 & #3 樣本於TCT第1000 cycles測試時電阻值急遽升高,顯示此兩個樣本於 此階段發生了線路損壞或是開路的情況。 Table 4.1 Electric resistance of flip chip without underfill Electric Resistance (Ω) of Flip Chip Without Underfill Cycles. #1. #2. #3. #4. #5. Avg.. Fail rate. 0. 0.5214. 0.5013. 0.5107. 0.5128. 0.5047. 0.51018. 0%. 200. 0.474. 0.457. 0.463. 0.46. 0.454. 0.4616. 0%. 400. 0.5297. 0.5197. 0.527. 0.5335. 0.5196. 0.5259. 0%. 600. 0.5267. 0.5128. 0.5315. 0.5223. 0.5128. 0.52122. 0%. 800. 0.5515. 0.5127. 0.528. 0.5444. 0.5151. 0.53034. 0%. 1000. 0.5229. 6.02E+06. ∞. 0.5133. 0.5024. 0.512867. 40%. 比較各個樣本於不同 TCT 階段之電阻值變化的狀況並繪製成比較圖 (Figure 4.2)。由電阻值變化趨勢來看,其幾乎都維持一定的數值, 並無發生太大變化。(除#2、#3 於第 1000 cycles 電阻值急遽升高 36.

(49) 除外) Electric Resistance (Ω) of Flip Chip Without Underfill #1 #4. 電阻值(Ω). 0.8. #2 #5. #3. 0.6 0.4 0.2 0 0. 200. 400. 600. 800. 1000. Cycles. Figure 4.2 無底膠填充覆晶接合於TCT測試電阻值變化 2. Electric resistance of flip chip with underfill 由有經過底膠填充的覆晶接合電阻值測試數據(Table 4.2)可知,#4 於 TCT 第 800 cycles 測試時,其電阻值急遽的升高,顯示此樣本於 此階段發生了線路損傷或是開路的情況。 Table 4.2 Electric resistance of flip chip with underfill Electric Resistance (Ω) of Flip Chip With Underfill Cycles. #1. #2. #3. #4. #5. Avg.. Fail rate(%). 0. 0.4944. 0.5142. 0.499. 0.4919. 0.5021. 0.50032. 0%. 200. 0.44. 0.452. 0.477. 0.474. 0.471. 0.4628. 0%. 400. 0.5035. 0.5111. 0.5345. 0.5356. 0.5452. 0.52598. 0%. 600. 0.5036. 0.5181. 0.5532. 0.5766. 0.5557. 0.54144. 0%. 800. 0.5093. 0.5281. 0.5389. 6.7. 0.5642. 0.535125. 20%. 1000. 0.4912. 0.5033. 0.5249. 8.73. 0.5659. 0.521325. 20%. 比較各樣本於不同 TCT 階段之電阻值變化的狀況並繪製成比較圖 (Figure 4.3)。其電阻值於 TCT 各個階段測試的數值幾乎維持一定, 37.

(50) 並無發生太大的變化。(#4 於第 800 cycles 電阻值急遽升高除外) Electric Resistance (Ω) of Flip Chip With Underfill #1 #4. 電阻值(Ω). 10. #2 #5. #3. 8 6 4 2 0 0. 200. 400. 600. 800. 1000. Cycles. Figure 4.3 有底膠填充覆晶接合於TCT測試電阻值變化. 4.3 有/無底膠填充覆晶接合高頻特性變化狀況比較 比較無填充底膠及有填充底膠的覆晶接合之高頻特性,由實驗數據可 知有填充底膠的覆晶接合於 S11(return loss)的 depth peak 變動了,且整 體高頻特性曲線也變差了(Figure 4.4);另外於 S21(insertion loss)的特 性表現上,有底膠填充也比無底膠填充的覆晶接合差了許多(Figure 4.5)。. 38.

(51) Figure 4.4 有/無底膠填充覆晶接合高頻特性(S11)差異. Figure 4.5 有/無底膠填充覆晶接合高頻特性(S21)差異. 39.

(52) 此結果可能為底膠填充改變了高頻元件整體的介電常數,致使高頻的特 性變差。所以我們將有底膠填充的高頻元件變更其線路設計(Figure 4.6), 並測量其高頻特性(Figure 4.7),結果如下:. Chip side. Sub side. Figure 4.6 高頻元件線路設計變更. Figure 4.7 高頻元件線路設計變更後之高頻特性. 40.

(53) 由高頻特性量測的結果可知,經過線路設計之高頻元件,其S11(20dB以 下) & S21(0.5dB以內)皆可以測到65GHz,比無線路設計之高頻元件的結構還 要好很多。 4.4 TCT測試前後覆晶接合RF變化狀況比較 比較有底膠填充覆晶接合於 TCT 1000 cycles(-55℃~125℃)前後高頻 特性的變化,由 Figure 4.8 及 Figure 4.9 可得知,樣本在經過 TCT 1000 cycles 後,其 S11 & S21 高頻特性的表現變化不大。. Figure 4.8 TCT前後,有底膠填充覆晶接合高頻特性(S11)差異. 41.

(54) Figure 4.9 TCT前後,有底膠填充覆晶接合高頻特性(S21)差異. 4.5 Moisture absorption test 依循 3.2.3 之吸濕測試步驟,來測試有/無底膠填充之覆晶接合材料吸 濕的狀況,測試的結果如下: 1. Without underfill 無底膠填充覆晶接合吸濕的數據如 Table 4.3,將其繪製時間 VS 重 量的關係圖(Figure 4.10),便可瞭解無底膠填充覆晶接合吸濕的趨 勢。. 42.

(55) Table 4.3 Without underfill 覆晶接合吸濕重量變化 小時. 0. 1. 4. 5. 6. 7. 8. 重量(g). 0.0134. 0.0135. 0.0137. 0.0136. 0.0134. 0.0137. 0.0135. 小時. 9. 23. 24. 25. 27. 28. 29. 重量(g). 0.014. 0.0136. 0.0138. 0.0137. 0.0135. 0.0136. 0.0138. 小時. 32. 33. 48. 49. 53. 57. 72. 重量(g). 0.0137. 0.0136. 0.0136. 0.0138. 0.0132. 0.0145. 0.0135. 小時. 76. 78. 81. 96. 100. 103. 105. 重量(g). 0.0132. 0.0139. 0.0141. 0.014. 0.0138. 0.0136. 0.0141. 小時. 120. 124. 127. 129. 144. 148. 172. 重量(g). 0.0134. 0.0134. 0.0136. 0.0133. 0.014. 0.0135. 0.0136. 小時. 176. 192. 196. 199. 216. 220. 223. 重量(g). 0.0135. 0.0138. 0.0134. 0.014. 0.0133. 0.0135. 0.0138. Without underfill. 0.015. Without underfill. 重量(g). 0.0145 0.014 0.0135 0.013. 22 0. 19 2. 14 4. 12 0. 96. 72. 48. 28. 23. 6. 0. 0.0125. 時數. Figure 4.10 無底膠填充覆晶接合時間VS重量 由上列的數據內容,可得知經過 223 小時吸濕後,無底膠填充的覆晶 接合的重量由原本的 0.0314g 增加到 0.0318g。增加了 2.4%。 2. With underfill 有底膠填充覆晶接合吸濕的數據如 Table 4.4,將其繪製時間 VS 重 43.

(56) 量的關係圖(Figure 4.11),便可瞭解有底膠填充覆晶接合吸濕的趨 勢。 Table 4.4 With underfill 覆晶接合吸濕數據 小時. 0. 1. 4. 5. 6. 7. 8. 重量(g). 0.0122. 0.0128. 0.0129. 0.013. 0.0129. 0.0131. 0.013. 小時. 9. 23. 24. 25. 27. 28. 29. 重量(g). 0.0128. 0.0126. 0.0128. 0.0129. 0.0128. 0.013. 0.0132. 小時. 32. 33. 48. 49. 53. 57. 72. 重量(g). 0.0127. 0.0128. 0.013. 0.0129. 0.0129. 0.0133. 0.0131. 小時. 76. 78. 81. 96. 100. 103. 105. 重量(g). 0.0129. 0.0135. 0.0128. 0.0131. 0.0126. 0.0129. 0.0136. 小時. 120. 124. 127. 129. 144. 148. 172. 重量(g). 0.0128. 0.0128. 0.0131. 0.0128. 0.0132. 0.0132. 0.0129. 小時. 176. 192. 196. 199. 216. 220. 223. 重量(g). 0.0131. 0.0128. 0.0128. 0.0131. 0.0129. 0.0127. 0.0131. Capillarity. Capillarity underfill. 0.014 重量(g). 0.0135 0.013 0.0125 0.012. 22 0. 19 2. 14 4. 12 0. 96. 72. 48. 28. 23. 6. 0. 0.0115. 小時. Figure 4.11 有底膠填充覆晶接合時間VS重量 由上列的數據內容,可得知經過 223 小時吸濕後,有底膠填充的覆晶 接合的重量由原本的 0.0122g 增加到 0.0131g。增加了 6.87%。 44.

(57) 4.6 Popcorn test 依循 3.2.4 Popcorn test 測試流程,量測 popcorn test 前後電阻值 的變化狀況如下: Before popcorn test. After popcorn test. Without underfill (Ω). 0.6363. 0.68. With underfill (Ω). 0.3692. 0.52. 將以上數據繪製成關係圖(Figure 4.12) Without underfill (Ω) With underfill (Ω). 電阻值(Ω). 0.8 0.6 0.4 0.2 0 Before popcorn test. After popcorn test. Figure 4.12 Popcorn測試前後之電阻值變化 無底膠填充的覆晶接合經過 popcorn test 後,其電阻值幾乎不變;有 底膠填充的覆晶接合其電阻值略為上升。. 45.

(58) 五、結論 由於覆晶接合用於高頻元件的連接有許多的好處,但若單單只有覆晶接 合時,其機械強度相當小,僅為有底膠填充的覆晶接合的十分之一左右,故 於應用上會有許多的限制。經過TCT 1000 cycles測試後,發現無底膠填充 之覆晶接合其機械強度衰退了10倍左右,比起有底膠填充之覆晶接合的機械 強度還要小很多;另外,我們測試於0、200、400、600、800、1000 cycles 的樣本電阻值,發現不管有/無底膠填充的覆晶接合其電阻值之變化皆不 大。綜合以上覆晶接合之機械強度測試 & TCT電阻值測試的實驗數據來看, 若欲將覆晶接合技術應用於高頻元件的連接上且欲使其有較高的可使用性 與可靠度,底膠填充是必需的。 因我們欲將底膠填充應用在高頻元件覆晶接合中,故我們必須由實驗測 試中,瞭解底膠填充對於高頻元件覆晶接合會產生何種影響?藉由實驗測試 有/無底膠填充的高頻元件覆晶接合之高頻特性,發現有底膠填充的覆晶接 合其S11 & S21均會變得比原本沒有底膠填充的覆晶接合還要差。其可能因 為底膠的填充而改變了整體的介電常數,故使測得的高頻特性變差,其無法 展現初始設計所預期的結果。此部份可以藉由高頻元件的設計來改善(材 料、線路、layout…等)。此次實驗即變更高頻元件及基板的線路設計,量 測高頻特性,其S11(20dB以下) & S21(0.5dB以內)皆可以測到65GHz,此結 果比無線路設計之底膠填充高頻元件還要好許多。另外,實驗也同時測試TCT. 46.

(59) 前後對於有底膠填充覆晶接合之高頻特性影響為何?藉由實驗的數據來 看,經過TCT 1000 cycles測試的樣本,其高頻特性並無較劇烈的變化。 由於欲瞭解使用底膠填充的覆晶接合可否於後續SMT的製程中所使用, 故設計吸濕及popcorn兩項測試來進行試驗,試驗結果如下: 1. 吸濕測試:有底膠填充的覆晶接合於完成223小時的吸濕後,其總重 量上升了6.87%,較無底膠填充的覆晶接合高了4.47%。 2. Popcorn test:將有底膠填充的覆晶接合依循JEDEC JSTD-020 level 3的測試標準進行測試。於完成測試後,檢視覆晶接合元件外觀上並 無凸起或是裂痕,且經過電阻值的量測,確認電阻值的上升於可接 受的範圍內。 經由以上兩點證實,有底膠填充的覆晶接合可以pass JEDEC JSTD-020 level 3的吸濕測試標準,可應用於後續的SMT製程。. 47.

(60) 六、參考文獻 1. Takaaki Ohsaki,“Electronic Packaging in the 90s – A Perspective from Asia" 2. http://elearning.stut.edu.tw/teach/electron/coat.htm 3. L. Gehman, “Bonding Wire Microelectronics Interconnections," IEEE Trans. On Comp. 4. 陳信文、陳立軒、林永森、陳志銘,電子構裝技術與材料 P135,2004 5. Katarina Boustedt, Ericsson Microwave Systems, “GHz Flip Chip – An Overview" 6. Electrically Conductive Adhesives (ECAs):J.M.Kim et al.Journal of Electronic Materials,Vol.33(11),2004 7. Myung Jin Yim, Associate Member, IEEE, In Ho Jeong, Hyung-Kyu Choi, Jin-Sang Hwang, Jin-Yong Ahn, Woonseong Kwon, and Kyung-Wook Paik, Member, IEEE , “Flip Chip Interconnection With Anisotropic Conductive Adhesives for RF and High-Frequency Applications" 8. The process and equipment technology of thermosonic flip-chip bonding P219:徐嘉彬,劉俊賢,機械工業雜誌258期。 9. L.K.Cheah,Y.M.Tan,J.Wei and C.K.Wong, “Gold to Gold Thermosonic Flip-Chip Bonding". 48.

(61) 10. 荻本 英二,CSP技術 P146,2000 11. http://www.jedec.org/ 12. http://www.eia.org/ 13. Manfred Boheim, Uhland Goebel, “Low Cost Packages for Micro- and Millimeterwave Circuits" 14. Zhping Feng, Wenge Zhang, Bingzhi Su, K. C. Gupta, Fellow, IEEE, and Y. C. Lee, “RF and Mechanical Characterization of Flip-Chip Interconnects in CPW Circuits with Underfill 15. L. K. Cheah, Y. M. Tan, J. Wei and C. K. Wong, “Gold to Gold Thermosonic Flip-Chip Bonding" 16. T Braum *, K. –F. Becker, M. Koch, V. Bader, R. Aschenbrenner, H. Reichl, “High-temperature reliability of Flip Chip assemblies" 17. Zhuqing Zhang, Jicun Lu*, C.P. Wong, “A Novel Approach for Incorporating Silica Filler into No-Flow Underfill" 18. L. K. The, M. Teo, E. Anto. C. C. Wong, S. G. Mhaisalkar, P. S. Teo, and E.H. Wong, “Moisture-Induced Failure of Adhesive Flip Chip Interconnects". 49.

(62)

數據

![Figure 2.1 電子構裝層級[2]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8435364.181484/16.892.209.745.111.709/Figure21電子構裝層級2.webp)

![Figure 2.6 異方性導電膠膜接合流程[7] ACF有以下的優點: 1. 製程溫度較低。 2. 減低環境對flip chip的影響。 3. 改善製程的特性:製程中不使用flux,故無清潔之問題。 ACF的缺點: 1](https://thumb-ap.123doks.com/thumbv2/9libinfo/8435364.181484/24.892.123.753.197.776/Figure有以下製程溫度較低減低環境影響改善製程中不使用故無清潔之問.webp)

![Figure 2.7 電鍍法金凸塊製作流程 金凸塊(Gold-to-Gold bumps)有以下的優點[9]:](https://thumb-ap.123doks.com/thumbv2/9libinfo/8435364.181484/25.892.124.781.541.1060/Figure27電鍍法金凸塊製作流程金凸塊GoldtoGoldbumps有以下的優點9.webp)

相關文件

The function f whose graph is shown in Figure 9 is defined on the closed interval [0, 2] but has no maximum value. The function takes on values arbitrarily close to 3, but

Then we can draw a right triangle with angle θ as in Figure 3 and deduce from the Pythagorean Theorem that the third side has length.. This enables us to read from the

You can see that initially the graphs of y = and y = ln x grow at comparable rates, but eventually the root function far surpasses the logarithm. Figure 5

Figure 3: Comparison of the partitioning of the hemisphere effected by a VQPCA-based model (left) and a PPCA mixture model (right). The illustrated boundaries delineate regions of

塑合板並配合五金配件製成建築用之門、窗、框及 1 至 3 階之樓梯 或其相關結合體等。試題分別由 2 至 3

依獎懲及 法定程序 予以書面 懲處 暫時讓學 生與其他 同學保持 距離..

第二級失能 生活補助金 滿第一年 15萬元 11.25萬元 滿第二年 20萬元 15.00萬元 滿第三年 25萬元 18.75萬元 滿第四年 30萬元

2-1 化學實驗操作程序的認識 探究能力-問題解決 計劃與執行 2-2 化學實驗數據的解釋 探究能力-問題解決 分析與發現 2-3 化學實驗結果的推論與分析

![Figure 2.8 故障發生率函數曲線 2.3.2 可靠度測試方法 可靠度測試的目的主要是為瞭解產品於設計階段中,藉由許多不同的試 驗,瞭解產品當時之可靠度水準,並將其提供決策者參考,以掌握產品的特 性。但是由於各國與各個產業之間,其測試方式與標準均不同,故有許多國 際標準組織制定了測試的標準,如電子設備工程聯合委員會(Joint Electron Device Engineering Council,簡稱JEDEC)[11]、日本電子工業協會](https://thumb-ap.123doks.com/thumbv2/9libinfo/8435364.181484/28.892.163.637.139.444/Figure是由於各國與各個產業之間其測試方式與標準同故如電子日本電子.webp)