國 立 交 通 大 學

電機學院 IC設計產業研發碩士班

碩 士 論 文

數位式脈波寬度調變控制電壓轉換電路

Digitally Controlled PWM for DC-DC Converter

研 究 生:林晏生

數位式脈波寬度調變控制電壓轉換電路

Digitally Controlled PWM for DC-DC Converter

研 究 生:林晏生 Student:Yen-Sheng Lin 指導教授:陳科宏 Advisor:Ke-Hong Chen 國 立 交 通 大 學 電機學院IC 設計產業研發碩士班 碩 士 論 文 A Thesis

Submitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master in

Industrial Technology R & D Master Program on IC Design

September 2007

Hsinchu, Taiwan, Republic of China

數位式脈波寬度調變控制電壓轉換電路

學生:林晏生 指導教授:陳科宏

國立交通大學電機學院產業研發碩士班摘要

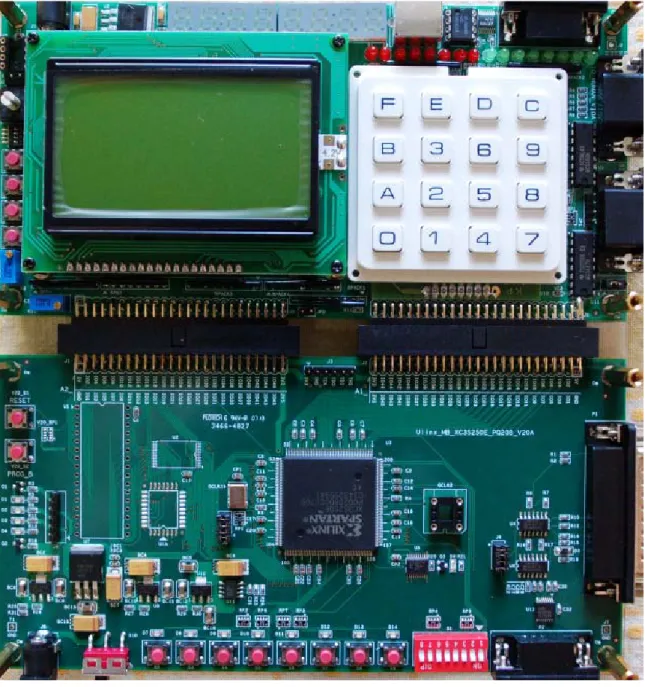

本論文研製一個以可規劃邏輯閘陣列(FPGA)為基礎之全數位控制 脈波寬度調變控制電壓轉換電路,針對數位式脈波寬度調變控制電壓轉 換器建立其數學等效模型,並探討電路特性、脈寬調變控制方式、與實 現方法。控制架構以PID控制器之原理為設計基礎,包含比例控制器、 積分控制器及微分控制器設計,以增加低頻增益及相位邊限,改善系統 閉迴路的相對穩定度,使暫態響應較快,減少穩態誤差。模擬平台本文 採用ModelSim及MATLAB/Simulink軟體工具進行系統整合模擬,驗證 其功能正確性。在實驗方面,使用設計FPGA/CPLD 或嵌入式系統的 Xilinx ISE 發 展 軟 體 及 為 希 科 技 公 司 所 推 出 的 系 統 發 展 實 驗 板 (ULINX_MB_XC3S250E_PQ208_V20A),利用硬體描述語言(Verilog) 來完成數位電路系統之設計,並透過Buck 電壓轉換器之系統電路驗證 所設計數位控制器之功能與性能。Digitally Controlled PWM for DC-DC Converter

stuudent:Yen-Sheng Lin Advisors:Dr.Ke-Hong Chen

Industrial Technology R & D Master Program of Electrical and Computer Engineering College

National Chiao Tung University

Abstract

The purpose of this thesis is to study and produce a full digitally controlled PWM for DC-DC converting circuit based on FPGA.This thesis is aimed at building a mathematically effective module equal to a Digitally Controlled PWM for DC-DC Converter; therefore, to explore the circuit quality, the pulse-width modulating fashion, and the way of realizing the converter. The controlling structure is based on the PID controller as its designing model, including the designing of the proportional controller, the integral controller, and the derivative controller, to enhance low frequency gain and phase margin, and to upgrade the relative stability at close loop system circuit, in order to expedite the transient response and minimize Steady state error. Simulating platform takes the ModelSim/Simlink software to simulate system integration to examine its function correctness. At the experiment, either FPGA/CPLD or inserting style system Xilinx ISE development software and ULINX_MB_XC3S250E_PQ208_V20A has been used, by the system circuit of the Buck voltage converter, to examine the function and quality of the designed digital controller.

誌謝

二年多的研究所求學過程即將結束,不論在學業及待人處事上,師 長及實驗室同學都給予很多的建議及鼓勵,讓我受益良多。本論文得以 順利完成,首先要感謝指導教授 陳科宏老師對學生的諄諄教誨,在研 究期間不辭辛勞的悉心指導與啟發,在此深表誠摯的謝意。同時由衷的 感謝口試委員,王清松博士及黃立人博士對本論文提供寶貴的意見與指 正,使本論文更加完善。 此外我要感謝實驗室的同學們在課業與生活上的相互提攜與關 懷,尤其是數位組的豐煜、國葆,在課業與研究上一起學習,以及在實 驗上的協助與討論,讓我感受到深刻的情誼,並留下了許多一同走過的 美好回憶。 最後我要感謝我的家人及所有關心我的人,你們的支持與無怨無悔 的付出,讓我能一一克服難關,順利完成這段求學歷程,在此僅將這份 榮耀與喜悅與你們分享。目錄

摘要 ... I Abstract ... II 誌謝 ... III 目錄 ... IV 圖錄 ... VI 表錄 ... VIII 第1 章 緒論... 1 1.1 研究動機與目的 ... 1 1.2 切換式直流至直流轉換器簡介 ... 1 1.3 論文架構 ... 3 第2 章 數位脈波寬度調變控制電路之 介紹 ... 4 2.1 控制電路介紹 ... 4 2.2 輸出電壓取樣電路 ... 6 2.2.1 ADC0820 的操作模式 ... 6 2.3 數位補償器電路 ... 7 2.3.1 查表法(Look-up Table)介紹 ... 8 2.4 數位脈波寬度調變器... 9 2.4.1 數位脈波寬度調變器之架構 ... 11 2.5 數位顫抖控制(Digital Dither)設計 ... 18 2.5.1 數位顫抖控制(Digital Dither)電路實現 ... 21 2.6 盲時(Dead-time)最佳化實現 ... 22 2.6.1 Dead-time最佳化理論 ... 23 2.6.2 低通濾波器 LP(z)... 25 2.6.3 Dead-time最佳化演算法 ... 26 第3 章 數位控制器設計與系統模擬 ... 28 3.1 數位控制器介紹 ... 28 3.1.1 Z轉換 ... 28 3.1.2 數值積分等效法 ... 29 3.1.3 離散系統穩定性分析 ... 33 3.2 數位PID控制器設計 ... 34 3.2.1 數位PID控制器介紹 ... 34 3.2.2 Ziegler-Nichols 調整法... 363.2.3 數位PID控制器參數設計 ... 38 3.3 系統模擬 ... 41 第4 章 數位脈波寬度調變控制電壓轉換電路硬體實現 ... 46 4.1 Verilog 硬體描述語言簡介 ... 47 4.2 A/D 轉換器 ... 48 4.2.1 Verilog 描述A/D 轉換器控制信號 ... 50 4.3 數位補償器 ... 53 4.3.1 Verilog 描述數位補償器 ... 56 4.4 數位脈波寬度調變器... 61 4.4.1 Verilog 描述數位數位脈波寬度調變器 ... 62 4.5 數位顫抖控制電路 ... 68 4.5.1 Verilog 描述數位數位顫抖控制電路 ... 68 4.6 低通濾波器 LP(z)之實現 ... 70 4.7 盲時(Dead-time)最佳化實現 ... 71 4.7.1 Verilog 描述盲時(Dead-time)最佳化電路 ... 71 4.8 實驗結果 ... 74 第5 章 結論與未來研究方向 ... 78 5.1 結論 ... 78 5.2 未來方向 ... 79 參考文獻 ... 80

圖錄

5 圖 1-1 降壓型直流電源轉換器 ... 2 圖 2-1 數位式降壓型直流電源轉換器方塊圖 ... 4 圖 2-2 數位式降壓型直流電源轉換器架構圖 ... 5 圖 2-3 ADC0820 寫入-讀取模式下Stand-Alone 時序圖 ... 7 圖 2-4 查表法PID 結構圖 ... 9 圖 2-5 resolution(DPWM)< resolution(ADC)波形圖 ... 11 圖 2-6 resolution(DPWM)> resolution(ADC)波形圖 ... 11 圖 2-7 3-bits的計數型數位脈波寬度調變產生器(DPWM) 架構圖 .. 12 圖 2-8 計數型數位脈波寬度調變產生器(DPWM) 波形圖 ... 13 圖 2-9 Delay-line形式的數位脈波寬度調變產生器(DPWM) 架構圖 . 14 圖 2-10 Delay-line形式的數位脈波寬度調變產生器(DPWM)控制波形 1 圖 2-11 混合式數位脈波寬度調變產生器(DPWM) 的架構圖 ... 16 圖 2-12 混合式數位脈波寬度調變產生器(DPWM) 控制波形 ... 17 圖 2-13 1-bit dither ... 18 圖 2-14 2-bit dither ... 19 圖 2-15 數位顫抖控制電路內部架構 ... 22 圖 2-16 dead-time最佳化在數位控制器內部之結構 ... 22 圖 2-17 v ts( )、dead-time與責任週期命令關係圖 ... 24 圖 2-18 低通濾波器實現方塊圖 ... 25 圖 2-19 dead-time控制示意圖 ... 26 圖 2-20 dead-time最佳化演算法流程圖 ... 27 圖 3-1 三種面積近似的方法從 kT 到 kT+T. 近似的方法有(a) Tustin rule (b) Forward rectangular rule (c) Backward rectangular rule. ... 30 圖 3-2 閉迴路離散資料系統方塊圖 ... 33 圖 3-3 z-平面 ... 33 圖 3-4 具有控制器之閉迴路控制系統 ... 37 圖 3-5 離散時間閉迴路系統 ... 38 圖 3-6 MATLAB Code ... 40 圖 3-7 根軌跡圖 ... 41 圖 3-8 Simulink之切換式降壓型直流至直流轉換器電路 ... 42 圖 3-9 Simulink之Buck converter之內部架構圖 ... 43圖 3-10 Simulink之ADC ... 43 圖 3-11 Simulink之PID compensator區塊圖 ... 44 圖 3-12 Simulink之DPWM區塊圖 ... 45 圖 3-13 由啟動至穩定之模擬圖形(電感電流、輸出電壓及輸出電流) 45 圖 4-1 Xilinx發展環境 ... 46 圖 4-2 Xilinx系統發展實驗板 ... 47 圖 4-3ADC0820 電壓取樣的特性圖 ... 49 圖 4-4ADC0820 取樣電路方塊圖 ... 50 圖 4-5 ADC0820 控制時序電路Verilog程式 ... 53 圖 4-6 補償器 Verilog 描述程式 ... 60 圖 4-7 PID輸入與輸出模擬圖 ... 61 圖 4-8 混合式(Hybrid)DWPM架構圖 ... 62 圖 4-9 數位脈波寬度調變器Verilog 描述程式 ... 66 圖 4-10 DPWM 輸入與輸出模擬圖 ... 67 圖 4-11 數位數位顫抖控制電路 Verilog 描述程式 ... 69 圖 4-12 Digital Dither之輸入與輸出的模擬波形 ... 69 圖 4-13 低通濾波器Verilog 描述程式 ... 70 圖 4-14 低通濾波器LP(z)之輸入與輸出的模擬 ... 71 圖 4-15 盲時(Dead-time)最佳化電路 Verilog 描述程式 ... 73 圖 4-16 盲時(Dead-time)最佳化電路之輸入與輸出的模擬波形 .... 74 圖 4-17 實驗系統接線示意圖 ... 75 圖 4-18 輸出電壓及PWM波形 ... 75 圖 4-19 一般無Dead-time最佳化之電路 ... 76 圖 4-20 使用dead-time最佳化之dead-time輸出波形 ... 77

表錄

表2-1 二種DPWM的優缺點比較 ... 15 表 2-2 一般的數位顫抖控制序列 ... 20 表 2-3 最小漣波數位顫抖控制序列 ... 21 表 3-1 三種近似方法的互相映射關係在從 s-domain到z-domain ... 32 表 3-2 z-domain 到 s-domain的取代表示法整理 ... 32 表 3-3 Ziegler-Nichols 調整公式 ... 37 表 4-1 a=32 之查表 ... 54 表 4-2 b=-62 之查表 ... 55 表 4-3 c=30 之查表 ... 56第1章 緒論

1.1 研究動機與目的

一般嵌入式系統中經常包括很多不同規格需求電源電路,傳統電源 供應器的控制晶片主要以類比方式實現,其優點是成本低、電路實現容 易、反應速度快,但缺點是通常只能提供特定功能,控制迴路補償不易 調整,較不適用複雜電源系統整合等等。近年來,隨著消費性電子產品 市場快速成長,電源的要求越來越高,其必須是省電、適用、高效能、 高可靠。為了能提供這些功能,電源控制的數位化及可程式化將成為未 來發展的趨勢,而在可控因素較多、即時反應速度更快、需要多個系統 電源管理的高性能系統應用中,數位電源則具有更大的優勢,數位電源 將可提供電源控制與系統應用進一步的整合,達到更佳的整體效能。 切換式直流至直流轉換器被廣泛應用在切換式直流供應器、直流 馬達驅動器及各種消費性電子產品。電源轉換器最重要的功能是提供穩 定的輸出電壓,因此對於切換式直流至直流轉換器的控制使其在輸入電 壓與輸出負載變動的情況下,能夠調整使輸出電壓維持在一定的位準, 實為研究的重要課題,也是本論文要實現的目標。1.2 切換式直流至直流轉換器簡介

圖1-1為一降壓型直流電源轉換器,此為電壓控制型電源轉換器,即(Duty),在控制器方面我們是使用數位控制系統,因為數位式控制器具 備多項優點,如可程式化、可以減小對製程參數、溫度參數變化造成的 影響,當利用現成工具(EDA)可以使設計所需時間縮短..等等。 在外部電路方面,電感(L)、電容(C)及負載電阻(R)可以稱為LCR plant。這一個LCR plant的轉移函數就是控制器要補償的受控體。當輸出 電壓經ADC與參考電壓比較產生一差值e(error),將送至數位控制電路產 生週期性的方波來控制功率電晶體(Power MOS)的開與關。當其中一個 功率電晶體導通,另一個電晶體就會關閉。我們藉由控制功率電晶體開 關的比率(Duty Ratio),可以決定輸出電壓的大小。 g

V

oV

refV

圖 1-1 降壓型直流電源轉換器1.3 論文架構

本論文共分五個章節說明,第一章為概論,說明本論文之研究動機與 目的及電源轉換器簡介。第二章將介紹數位脈波寬度調變控制器系統架 構及運作方式。第三章為數位控制器介紹其中包含控制理論與設計方 法。第四章為數位脈波寬度調變電路實現,利用硬體描述語言(Verilog) 來設計。第五章為結論及未來方向,對整體的研究做總結並討論未來可 能的研究方向。第2章 數位脈波寬度調變控制電路之

介紹

2.1 控制電路介紹

在本論文中,我們將介紹一個數位脈波寬度調變控制電路來控制一 個切換式降壓型直流至直流轉換器電路。控制電路中包含了一些主要元 件 : 類 比 至 數 位 轉 換 器 (ADC ) 、 數 位 PID 補 償 器 ( Digital PID Compensator ) 、數位脈波寬度調變器(Digital Pulse-Width Modulator)、 數 位 顫 抖 控 制(Digital Dither) 電 路 、 盲 時 最 佳 化 電 路 (Dead-Time Optimizer)。整個控制積體電路再加上直流至直流轉換器的方塊圖,如 圖 2-1所示。 s v ref

V

gV

oV

圖 2-1 數位式降壓型直流電源轉換器方塊圖由圖 2-1知,數位脈波寬度調變控制積體電路與切換式降壓型直流 至直流轉換器形成了一個閉迴路的回授控制系統,而控制電路的主要功 能就是調整直流至直流轉換器的輸出電壓(Vo)。當切換式降壓型直流 至直流轉換器的輸出電壓因為輸入電壓(Vi)或負載電流(Io)的變動 而改變時,此時,控制電路所送出的訊號(Duty Ratio)便會對轉換器 做調整的動作,使得轉換器的輸出電壓又能夠穩定地保持在我們所要的 參考電壓( )設定。整個數位脈波寬度調變控制電路的內部架構如圖 2-2 所示。 ref V 1 Z− 1 Z− 1 Z− ref V o V 圖 2-2 數位式降壓型直流電源轉換器架構圖 首先,控制電路中的類比至數位轉換器(ADC)會對轉直流至直流 轉換器的輸出電壓做取樣而得到一個取樣電壓(Vsense),一般的情況下, Vsense = Vo。

考電壓(Vref)做比較,其比較後的差值即為誤差信號(e[n])。這個誤 差訊號被送至數位補償器做運算,其運算的結果為責任週期命令 (d[n]),將分別送至數位顫抖控制 (Digital Dither)、數位低通濾波器 LP(z),其中數位顫抖控制將產生責任週期命令序列,而責任週期命令經 過數位低通濾波器會產生責任週期命令的平均值D再送至盲時最佳化電 路 (Dead-Time Optimizer)計算最佳dead-time資訊,數位顫抖控制及盲時 最佳化電路輸出分別為 、 、 ,這些是數位脈波寬度調變器的輸入, 調變器會根據輸入訊號的值,而送出二組頻率固定的脈波信號 、 , 其脈波寬度即是由 、 、 值所決定的。最後,產生的脈波寬度訊號 會再送至切換式降壓型直流至直流轉換器的開關元件而做切換,使轉換 器轉換不同的輸出電壓。經由這樣不斷的取樣、比較、補償,所以會使 切換式降壓型直流至直流轉換器的輸出電壓穩定。 d 1 d t 1 d t 2 d t 2 d t 1 g g2 d

2.2 輸出電壓取樣電路

由圖2-1 所示,一開始類比至數位轉換器(ADC)要對轉換器的輸 出電壓取樣,這在整個控制積體電路中是相當重要的一個電路。我們根 據系統的要求再去選擇一顆適合的類比至數位轉換器。我們選擇了 ADC0820 這顆類比至數位轉換器。2.2.1 ADC0820 的操作模式

類比至數位轉換器(ADC0820)我們使用 Stand-Alone 這一種操作 模式,在寫入-讀取模式下使用Stand-Alone 操作時,CS腳跟RD 腳可以同時為〝0〞,當WR 腳由1 變0 時,ADC0820 開始轉換,大約800 ns 後資料就會送至輸出。Stand-Alone 模式時序圖如2-3 所示。 圖 2-3 ADC0820 寫入-讀取模式下 Stand-Alone 時序圖

2.3 數位補償器電路

數位脈波寬度調變控制電路中第二個部份的電路是數位補償器電 路。當類比至數位轉換器取樣到直流至直流轉換器的輸出電壓(Vo)並與Vref 比較得到一個誤差信號(error signal)值e[n]後,會把這誤差值送

到此補償器。

本論文的補償器所要實現的控制理論是根據PID 控制器的觀念所 設計,其所實現的關係式如下列式子所表示之:

[ ] [ 1] [ ] [ 1] [ 2]

其中d[n]代表的是補償器目前的責任週期(duty ratio)輸出值,e[n]則是 代表目前的誤差信號(error signal)輸出值。e[n-1]、d[n-1]則為該信號 前一次週期的誤差信號(error signal)及責任週期輸出值。e[n-2]則為該 信號前二次週期的值,另外 a、b、c 均為常數。PID 控制器的觀念與 詳細設計方法將會在下一章中說明。 由(2-1)式可知,設計一個補償器需要使用到數個加法器與乘法器, 然而對於一個積體電路設計者而言,乘法器的使用是非常佔用晶片面積 且又有速度上的考量,所以可以改用查表的設計的方式,來實現 PID控 制器。

2.3.1 查表法(Look-up Table)介紹

查表法(look-up table)[1, 2, 3],顧名思義就是利用查表的方式來 代替許多複雜的運算。簡單來說,查表法是利用一張儲存資料的表,通 常是設計者事先將計算好的數值結果存在記憶體中,這樣的方式可以用 簡單的架構來完成乘法的動作。 我們以式(2-1)來說明,我們可以發現 a e n⋅ [ ]、b e n⋅ [ −1]、 這三個是簡單的乘法運算,由於A/D 轉換器所輸出的e 值為很小的有限 值,加上a、b、c 是常數,所以我們可以把它們的乘積事先運算出結果, 然後再儲存成係數為a、b、c 的三張查表。此時,ADC所輸出的誤差信 號 e[n]或 e[n-i]就可以當作是此張查表的位址。當每一個 e[n]值與其前i 次週期的 e[n-i]值被送到補償器時,補償器的相對應a、b、c三張表之

位址的內容就會馬上被查出來,因此就不需要再經過乘法的運算,不但

[ 2

提高了效率也因為沒有使用到乘法器而大大的降低晶片面積。 利用查表法設計 PID控制器還有另一項優點,因為使用查表法保留 了可調整、規劃的彈性,當應用在不同的電源轉換器時,不必重新設計 控制電路,僅需調整表內數值即可完成。利用查表法實現的 PID控制器 電路結構如圖2-4所示。 1 Z− 1 Z− 1 Z− 1 Z− 圖 2-4 查表法 PID 結構圖

2.4 數位脈波寬度調變器

目前大多數的交換式電源轉換器的控制電路都採用脈波寬度調變 (PWM)方式控制,在整個系統中,數位脈波寬度條變器所提供的功能其 實就是一個數位至類比的轉換器(D/A Converter)。因為它所輸出的是一個頻率固定寬度可依據 d[n]值而調變的信號(Duty Ratio)。這個固 定頻率的脈波信號會輸出至切換式直流至直流轉換器的開關元件,利用 不同的寬度調變,決定功率電晶體(Power MOS)導通與截止時間的長 短,如此就可以調整我們所要的輸出電壓。 由於Duty Ratio 可以調整直流至直流轉換器的輸出電壓,因此數位 脈波寬度調變器的解析度就格外顯得重要。假如數位脈波寬度調變器的 解析度不夠高時,直流至直流轉換器的輸出電壓便會振盪,如圖2-5所示 輸出電壓在穩態的情形下有一震盪現象而不會趨於穩定,這種現象稱 limit cycle [4]。這是因為數位脈波寬度調變器所調整的輸出電壓增量值

沒有落在相對應於前端ADC參考電壓(

Vref

)的輸出電壓改變量(ΔVo

)的範圍內,因此就會造成輸出電壓值的振盪。解決的方式就是對應於 d[n]

值最小位元(Least significant bit, LSB)的

Vo

增量值必須小於ΔVo

。即resolution(DPWM)> resolution(ADC) (2-2) DPWM 所能調整的電壓變化量必須小於ADC的電壓取樣量。如此 才能使輸出電壓穩定,如圖2-6所示。

圖 2-5 resolution(DPWM)< resolution(ADC)波形圖

圖 2-6 resolution(DPWM)> resolution(ADC)波形圖

2.4.1 數位脈波寬度調變器之架構

生開關比率(Duty Ratio)的方波,藉由計數器計數的值與命令週期(Duty command)做比較,來決定方波大小。圖 2-7 為計數型 DPWM 的架構圖,

當CLK 為正緣時,計數器就會加 1。當計數器狀態為 0 時開關比率(Duty

Ratio)波形就會為 ON 的狀態,而計數器會跟比較器做比較。當比較器

輸入Duty Command 也就是開關比率(Duty Ratio)的輸入數值跟計數器狀

態相等的時候,比較器將輸出 1 使 RS 正反器 Reset,讓 PWM output 呈

現OFF 的狀態,所以我們可以用比較器的輸入 Duty Command 來指定相

對應開關比率(Duty Ratio)的方波輸出。在圖 2-7 中,當 n=3 時即可得到 8 bits 的解析度。Duty Command 為三個 bits , CLK 所用的頻率是輸出

頻率的8 倍。圖 2-8 為 3-bits 的計數型數位脈波寬度調變產生器(DPWM) 波形圖。 圖 2-7 3-bits 的計數型數位脈波寬度調變產生器(DPWM) 架構圖 計數型的 DPWM 需要相當高的頻率來除頻,若一個切換頻率 s f =1MHz 要達到 8 bits 的解析度(Resolution),系統頻率就需要 256 MHz 來做除頻。由此可知要將工作頻率在 fs的方波達到 n-bits 的解析度就需

要2n s f 的除頻頻率。所以要增加 DPWM 的解析度可以用增加除頻頻率 來達成,可是過高的除頻頻率將會造成極大的功率消耗。 圖 2-8 計數型數位脈波寬度調變產生器(DPWM) 波形圖 第二種DPWM 是採用 Delay Line 與多工器的架構來產生 DPWM 的 開關比率(Duty Ratio)輸出。電路架構圖為圖 2-9,當 CLK 為正緣的時候 開關比率(Duty Ratio)的方波輸出就為 ON,設定 RS 正反器的輸出為 1。

另外test 波形會輸入到 Delay-Line 中,並利用多工器去選取適當的重置

(Reset)的時間將 RS 正反器 Reset,讓 PWM output 波型為 OFF。因此多 工器輸入就可以決定開關比率(Duty Ratio)來得到相對應的方波輸出。 Delay-line 形式的 DPWM 控制波形控制波形如圖 2-10。

32 :1

圖2-9 Delay-line 形式的數位脈波寬度調變產生器(DPWM) 架構圖

Delay-line 形式 DPWM 雖然不需要太高的頻率就可以達到高解析度 (Resolution)。但其高解析度的代價是需要多級的 Delay 元件及龐大 bits

的多工器來完成Delay Line 解碼工作。例如要達到 5 bits( )的解析

度,就需要 32 級 Delay-Cells 的 Delay-Line 架構與 32 bits 的多工器。相

較於除頻式雖然節省功率消耗但是卻需要更多的硬體成本。

5 2 = 23

圖2-10 Delay-line 形式的數位脈波寬度調變產生器(DPWM)控制波形 將上述兩種 DPWM 的優缺點做一個整理,如表 2-1。 Type 缺點 優點 Delay-line Fast-counter 解析度越高所需 晶片面積越大 解析度越高所需 計數頻率越高 低時脈頻率 低電源消耗 小面積 表 2-1 二種 DPWM 的優缺點比較 第三種是混合式(Hybrid)的DWPM [3],此種DPWM是將計數型及 Delay-line型相結合,其擁有兩者的優點,可以使 DPWM在面積與功率 消耗取得一個平衡。圖 2-11 為混合式的數位脈波寬度調變器的架構圖。

c n c n c n 2 :1nd c n d n n c n 圖 2-11 混合式數位脈波寬度調變產生器(DPWM) 的架構圖

這 一 個 8 bits 混 合 式 DPWM 採 用 了 4 bits 計 數 型 DPWM 與 4 bits

Delay-line型的DPWM,其中包括了一個2nd×1多工器、16個D型正反器

( )、4-bit 計數器(nc=4)、二個4-bit 比較器、二個AND 閘及

一個RS 正反器。在此電路中用4 bits的計數器去將頻率除以為1/16。而 用多工器去選取這1/16頻率的1/16的重置(Reset) RS暫存器的時間。工作 原理說明如下,補償器的輸出(d[n])分成兩部份輸入至數位脈波寬度 調變器,較高的4-bit(d[7:4])輸入至比較器,較低的4-bit(d[3:0])輸 入至多工器的選擇端。當電路啟動時,數位脈波寬度調變器的輸出 (PWM output)先被RS 正反器設為〝1〞。計數器的輸出送至當4-bit 比 2nd = 61

較器去與d[7:4]作比較,當兩數相同時,比較器輸出一個信號至RS 正反 器R 端的AND 閘。而多工器亦會輸出信號至RS 正反器 R端的AND 閘,假如這兩者信號皆為〝1〞時,RS 的R 端就會被設定為〝1〞。此 時,RS 正反器處為重置狀態,PWM output 被設為〝0〞。所以當d[7:0] 不同時,PWM output就會不同寬度的調變。控制波形如圖2-12,最下面 的波形為開關比率(Duty Ratio)在35/256= 13.67 % 的時候的輸出波形。 0 1 2 3 4 15 0 CLK Counter 0 15 15 1 0 1 2 2 0 1 2 15 35/256=13.67% Multiplexer Output 圖 2-12 混合式數位脈波寬度調變產生器(DPWM) 控制波形

2.5 數位顫抖控制(Digital Dither)設計

數位顫抖控制是一種增加DPWM解析度的方法[4],與類比顫抖控制 相比較為容易產生及控制,數位顫抖控制是藉由在數個開關週期內LSB 變化來改變開關比率(Duty Ratio),使得平均的開關比率(Duty Ratio)可以 落在二相鄰位準之間。而〝平均〞動作是由外部的LC濾波器實現。 數位顫抖控制動作說明如圖 2-13, 與 分別表示二相鄰 DPWM產生的開關比率(Duty Ratio)位準,其中 = +LSB,若每一次 開關週期 與 輪流產生,則平均的開關比率(Duty Ratio)可表示成: 1 c D Dc2 c D 2 c D 1 1 c D Dc2 ( + )/2= +(1/2)LSB。由此可知,藉由二個開關週期的平均,可以 得到一個介於 與 二者中間(1/2)LSB的位準,相當於增加了DPWM 一位元有效的解析度。利用相同的方法,在四個開關週期中可產生 (1/4)LSB及(3/4)LSB位準如圖 2-14,相當於增加二位元DPWM有效解析 度。 1 c D Dc2 Dc1 Dc1 Dc2 圖 2-13 1-bit dither

圖 2-14 2-bit dither 因此,在2Ndith開關週期中可得到有效的DPWM解析度: dith dpwm eff dpwm N N N , = + (2-3) 其中Ndpwm為DPWM解析度,Ndith為數位顫抖控制位元數。 雖然數位顫抖控制可以增加DPWM有效解析度,但由於數位顫抖平 均效果是藉由外部LC濾波器實現,所以在數位顫抖過程中會在外部LC 濾波器上產生額外的AC漣波效應,因此數位顫抖控制位元數必須有所 限制。 另外,在實現數位顫抖控制時,有些不同的數位顫抖控制序列會產 生相同平均DC位準,如圖 2-14中(1/2)LSB位準可以由二種不同順序的形

率,在外部低通濾波器的特性下,可降低輸出電壓的漣波,相較之下是 比較建議使用的。 以3-bit數位顫抖控制為例,其序列表如表2-2,其中〝1〞表示在開 關比率(Duty Ratio)加入一LSB,表2-2 表示一般直觀的數位顫抖控制序 列[5],表2-3 是針對產生最小漣波加以變形的數位顫抖控制序列,二表 比較結果可發現表2-3 產生漣波效應較小,以1/8即{0,0,0,0,0,0,0,1}為 例,在表2-3 是最差的狀況卻等於表2-2 最好的狀況,所以我們將採用 表2-3 的數位顫抖控制序列設計。 0 1/8 2/8 3/8 4/8 5/8 6/8 7/8 Sequence Average 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1

Dither Sequence Ripple

none lowest

highest

lowest

0 1/8 2/8 3/8 4/8 5/8 6/8 7/8 Sequence Average 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1

Dither Sequence Ripple

none highest lowest highest 表 2-3 最小漣波數位顫抖控制序列

2.5.1 數位顫抖控制(Digital Dither)電路實現

圖 2-15為一數位顫抖控制電路內部架構,可以產生最小漣波的數位 顫抖控制如表2-3,其內部電路包含一Ndith −bit之計數器、 容量 的表格及一個加法器,其中表格儲存 個數位顫抖控制序列,每個序 列有 位元長度。 dith diyh N N 2 2 × dith N 2 dith N 2 PID補償器輸出分成二個部份輸入至數位顫抖控制電路,較低的 LSB’s位元決定數位顫抖控制序列,再依據計數器的輸出值選擇適當的 LSB與高位元 MSB’s相加產生Dc’送至DPWM。 dith N dpwm N

dith dith N N

2

2

×

圖 2-15 數位顫抖控制電路內部架構2.6 盲時(Dead-time)最佳化實現

本論文使用之dead-time最佳化方法[6],最大的特色是執行dead-time 最佳化過程中,不需要任何額外的感測器去感測外部電路信號,只需觀 察責任週期命令(duty cycle command)平均值D之變化來調整dead-time大 小使系統達到最大的效率。此方法尤其適用數位控制電路,因為其不需 要增加任何類比元件或改變驅動電路,只須少量的數位電路即可完成。 dead-time最佳化在數位控制器內部之結構如圖 2-16。 s v ref V o V g V 圖 2-16 dead-time最佳化在數位控制器內部之結構2.6.1 Dead-time最佳化理論

在考量電壓轉換器最大效能η( ,td1 td2)我們可以得到下列式子: 1, 2 1 2 1 2 ( , )| , out ref d d d d V V d opt d opt t t Max η t t = ⇒t t (2-4) 同時在最佳的dead-time情況下可以的到最小的責任週期命令(duty cycle command)平均值D即: 1, 2 1 2 1 2 ( , )| , out ref d d d d V V d opt d opt t t Min D t t = ⇒t t (2-5) 原理說明如下,在圖 2-17中分別表示切換點電壓(switch node voltage)、閘極輸出波形在 (a)最佳dead-time、(b)過長dead-time、(c)不 足dead-time情況下之圖形,責任週期命令(duty cycle command)平均值D 必須增加(〝+〞區域)去補償dead-time不佳所造成的損耗(〝-〞區域)。 當dead-time 太長(圖 2-17 (b)),會導致body diode效應產生一負 電壓於1

d

t

s

v 上,如此將使平均切換點電壓(switch node voltage)<vs>下降,

為維持電路要求即 ,責任週期命令(duty cycle command)平均值D

將會增加去補償平均切換點電壓(switch node voltage)<

o =Vref

V

s

v >的損耗。

在圖 2-17 (b)中平均切換點電壓(switch node voltage)<vs>損耗可表示成:

d D s s t V V T − Δ = − (2-6) 其中:Ts是開關週期,VD是body diode的電壓降。 同理,不足dead-time情況時,因為閘極驅動信號的overlap,將會造 成v ts( )的損耗,使平均切換點電壓(switch node voltage)<vs>下降,責任

週期命令(duty cycle command)平均值D增加。在圖 2-21 (c)中平均切換 點電壓(switch node voltage)< >損耗可表示成:

1 2 1 2 on g d s on on s R V t V R R T − Δ = − + (2-7) 其中: Vg為輸入電壓,Ts是開關週期,Ron1、Ron2分別為為 及 之 on-resistances。 1 Q Q2 由以上分析可知,在非理想的情況下(即dead-time非最佳化時),責 任週期命令(duty cycle command)平均值D必須增加以補償平均切換點電

壓<vs>造成之損耗。由此特性可知最佳的dead-time值將發生在責任週期

命令(duty cycle command)平均值D最小時。我們將根據此特性,利用演 算法來求出最佳的dead-time值,相關說明於之後的章節介紹。 ( ) s v t s v < > ( ) s v t ( ) s v t s v < > s v < > 1 g v 2 g v 2 g v 2 g v 1 g v 1 g v 1 d opt t 2 d opt t 1 d t 1 d t 2 d t 2 d t min D>D min D>D min D=D 圖 2-17 v ts( )、dead-time與責任週期命令關係圖

2.6.2 低通濾波器 LP(z)

低通濾波器的功用是要計算出責任週期命令(duty cycle command) 平均值D,其表示式如下: ] [ ] 1 [ ) 1 ( ] [n D n d n D = −α − +α⋅ (2-8) 將(2.8)式取z轉換可得轉移函數: ) 1 ( ) ( α α − − ⋅ = = z z d D z LP (2-9) 再將(2-8)式整理可得 ] 1 [ ] [ ] 1 [ ] [n =D n− + ⋅d n − ⋅D n− D α α (2-10) 取α為1 2p ,p為一正整數,則(2-10)式乘法計算可由移位運算所取代, 實現方塊圖如下: Subtractor Multipler Adder D Flip Flop α D[n-1] d[n] D[n] D[n-1] 圖 2-18 低通濾波器實現方塊圖

2.6.3 Dead-time最佳化演算法

DPWM共有三個輸入:責任週期命令(d)、dead-time時間命令 及 ; 二個輸出:控制信號 及 ,送給功率電晶體(Power MOS) Q1及Q2,其 操作示意圖如圖 2-19 所示: 1 d t td2 1 g g2 1 d t 2 dt

圖 2-19 dead-time控制示意圖 2 g 於d +td1時啟動,在1−td2時重置, 及 由dead-time最佳化演算 法求得。 1 d t td2 依據前面介紹的觀念,我們可以利用dead-time最佳化演算法,從最 小的穩態責任週期命令D中,尋找最佳的dead-time時間來獲得系統最好 的效能。演算法流程圖如圖 2-20 所示,在輸入電壓及負載固定的條件 下執行dead-time的尋找,一開始由一觸發信號啟動, 初始值設為 , 在演算法過程中 將減一 後再比較D的數值大小,在 減少的過程 中,D值亦逐漸變小,直到發現一旦D值變大此時即結束演算法。 d t tdmax d t Δtd td結束演算法後,將產生的最佳化dead-time數值 送至DPWM,此 演算法將執行二次,第一次先求出 ,第二次再求出 。模擬波形範例 如圖 2-21。 dopt t 2 d t 1 d t max d d t t = d dopt t t = D Dold = d d d t t t = −Δ w n old D D≤ dopt d t t = old D D < 圖 2-20 dead-time最佳化演算法流程圖

第3章數位控制器設計與系統模擬

3.1 數位控制器介紹

數位控制器可以利用電腦、微處理器、數位訊號處理器(DSP)等 來實現,與類比的控制器相比較,使用數位控制器最大的優點,就是數 位控制器可以藉由改變程式容易地修改,而類比的控制器一旦建立之 後,便很難改變其元件。 一般數位控制器的Z-轉移函數寫成(4.1)式的形式[7]。 1 0 1 1 0 1 ( ) m m n n b b z b z D z a a z a z − − − + + ⋅⋅⋅ + = + + ⋅⋅⋅ − (3-1) 其中n 和m 為正整數,若輸出並未搶先在輸入之前發生,則轉 移函數D(z)稱為實際可實現。此表示D(z)的級數展開不能有任何z 的正冪次。在(4.1)式的D(z)項中,若b0 ≠0,則 a0 ≠0。若D(z)表 示為 1 0 1 1 0 1 ( ) m m n n b b z b z D z a a z a z + + ⋅⋅⋅ + = + + ⋅⋅⋅ (3-2) 則實際可實現性的條件為n ≥ m。3.1.1 Z轉換

對於一離散或數位資料的線性系統及線性差分方程式,適合使用 k),k=0,1,2,…,其中y(k)代表一連串的數字 Z 轉換[7]。 考慮一序列y( 或事件。則y(k)的z 轉換定義為Y(Z)=y(k)的z轉換= [ ( )] ( 1 0 ) k Z y k y k ∞ z− = =

∑

(3-3)3.1.2 數值積分等效法

一般的控制系統轉移函數(Transfer Function),大多是用來描述連續 (cont 其中z 是具有實部和虛部的複變數。 inuous)訊號的系統。如果系統要以數位方式來呈現就必須要將轉移 函數改寫成離散(discrete)訊號的系統來做分析。根據A/D轉換器取樣 (Sample)的頻率,離散的轉移函數也許不會完全近似連續的轉移函數。 如果取樣頻率愈高,我們所得到離散轉移函數就會近似於連續的控制系 統。本節主要探討如何將連續的轉移函數利用數學等效的方式得到離散 的轉移函數,以方便後續章節的轉移函數補償與控制器設計。以下介紹 三種數值積分等效方法,如圖 3-1所表示。t

kT kT-T

e(t)

(b) Forward Rectangular Rule

(c)Backward Rectangular Rule

圖 3-1 三種面積近似的方法從 kT 到 kT+T. 近似的方法有(a) Tustin rule (b) Forward rectangular rule (c) Backward rectangular rule.

1.Tustin方法: Tustin方法或稱雙線性近似(bilinear approximation)是將函數e(t)以下 的區域以一系列的梯型來近似,如圖 3-1(a)所示,在二個取樣值間,以 直線來近似e(t)。假設 ( ) 1 ( ) ( ) U s D s E s = = s (3-4) 其為積分,故

0 ( ) kT T ( ) kT ( ) kT T u kT − e t dt e t dt − =

∫

+∫

(3-5) 其可被改寫為 ( ) ( ) ( ) u kT =u kT −T +e t 在一個T時間下的面積 為簡便起見,將u(kT)寫成u(k),u(kT-T)寫成u(k-1),如此我們可將(4.4) 式改寫為 ( ) ( 1) [ ( 1) ( )] 2 T u k =u k− + e k− +e k (3-6) 對(3-6)式取其z-轉換可得 1 1 ( ) 1 1 ( ) 2 1 2 1 U s T z T z E s z z − − ⎛ + ⎞ ⎛ = ⎜ ⎟= ⎜ − ⎝ − ⎠ ⎝ ⎠ + ⎞ ⎟ (3-7) 即 2 1 1 z s T z − ⎛ = ⎜⎝ + ⎠⎞⎟ ,將s代入任意D(s)中即可求得基於梯型積分近似之離散函 數D(z)。 2.Forward-rectangular方法: 這一個表示在圖3-1 (b) Forward Rectangular 方法,是將取樣的兩點 面積取前一點的大小為長,取樣時間為寬所得到的面積近似成長方形。 如公式: ( ) ( 1) ( ) u k =u k− +Te k (3-8) 對 式取其z-轉換可得 1 ( ) ( ) 1 1 U s T Tz E s = −z− = z− (3-9) 2.Backward-rectangular方法: 而 Backward Rectangular 方法在 圖 3-1(c). 他將長方形的長從後面一點看過來,e(t)在 t=Kt 時的積分近似為 ( ) ( 1) ( 1) u k =u k− +Te k− (3-10) 對 式取其z-轉換可得 1 1 ( ) ( ) 1 1 U s Tz T E s z z − − = = − − (3-11) 以上可以做一個總結,s-domain 到 z-domain 的映射關係在表 3-1 1 z s T − ← 1 z s Tz − ← 2 1 1 z s T z − ← + 表 3-1 三種近似方法的互相映射關係在從 s-domain 到 z-domain 同樣的我們也可以將這幾種方法的 z-domain 到 s-domain 的映射。 這一個用z 取代 s 的的關係,我們整理在表 3-2 Method Approximation Forward Rule Backward Rule Bilinear Rule 1 z= +Ts 1 1 z Ts = − 1 2 1 2 Ts z Ts + = − 表 3-2 z-domain 到 s-domain 的取代表示法整理

3.1.3 離散系統穩定性分析

對於一個離散系統而言,要判斷該系統是否穩定,我們可以從它 特性方程式的根落在z-平面上的位置去判定[7]。 現假設有一個離散資料系統,其系統轉換函數如圖 3-2所示。 圖 3-2 閉迴路離散資料系統方塊圖 由圖3-3 知,該系統的閉迴路轉移函數為: ( ) ( ) ( ) ( ) 1 ( ) ( ) Y z D z G z R z = +D z G z 0 = (3-12) 為了討論此一閉迴路系統的特性,我們必須算出離散特性方程式(4.10 式)的根。 1+D z G z( ) ( ) (3-13) 當特性方程式的所有根均落於z平面的單位圓 |z|=1 之內,如圖 3-3 所示,則我們可以說該系統為穩定。 圖 3-3 z-平面3.2 數位PID控制器設計

3.2.1 數位PID控制器介紹

PID控制器的歷史非常悠久,它的構思首見於1922年Minorsky的文 獻[8],而PID控制器的原型出現在Callender等人1936年的文獻上[9]。著 名的Ziegler and Nichols則在1942年提出PID控制器的調整法[10],歷經半 世紀,它一直是現今產業界裡應用廣泛、實用性相當高的控制器。 PID 控制器是由比例增益、積分、微分三個動作組合而成的控制器, 其結合PI 和PD 控制器的優點,能改善系統閉迴路的相對穩定度,使暫 態響應較快,減少穩態誤差。在連續時間的PID 控制法如下式 ( ) p ( ) i ( ) d d ( ) u t K e t K e t dt K e t dt = +

∫

+ (3-14) 其中,u t( ):控制訊號 e t( ):誤差訊號 Kp:比例增益 Ki:積分增益 Kd:微分增益 而類比PID控制器轉移函數可以在s-domain下表示為 ( ) ( ) ( ) i p K U s D s K K s E s s = = + + d (3-15) 為了得到數位式PID控制器,我們用梯型面積之和近似積分項,並以二 不同時間點誤差的差值來近似微分項,Ts為取樣時間(Sampling Time), 則可推導出離散時間PID控制器,推導過程如下:(0) (1) (1) (2) ( 1) ( ) ( ) ( ) ... 2 2 2 ( ) ( 1) p i s d s e e e e e k e k u k K e k K T e k e k K T + + − + ⎛ ⎞ = + ⎜ + + + ⎟ ⎝ ⎠ + − + h=1 ( ) ( 1) ( ) [ ( ) ( 1)] 2 k d p i s s K e h e h K e k K T e k e k T + − = +

∑

+ + − (3-16) 定義 ( ) ( ) ( 1) (0) 0 2 e h e h f h = + − , f = 將上式做z轉換,可得 1 h=1 h=1 ( ) ( 1) 1 1 [ ] [ ( )] [ ( ) (0)] 2 1 1 k e h e h k 1 ( ) Z Z f h F z f F z z− z + − = = − = − −∑

∑

− (3-17) 其中 ( ) [ ( )] 1 1 ( ) 2 z F z Z f h E z − + = = 因此 11 h=1 ( ) ( 1) 1 [ ] 2 2(1 ) k e h e h z ( ) Z E z z − − + − + = −∑

將 式做z轉換可得 1 1 1 1 1 ( ) [ (1 )] ( ) 2 1 d p i s s K z U z K K T z E z z T − − − + = + ⋅ ⋅ + − − 1 1 1 [ (1 2 1 i s d p i s K T K K K z E z T − − ⋅ = − + + − − )] ( )z 所以 1 1 ( ) 1 (1 ) ( ) 2 1 i s d p i s K T K U z K K z E z z T − − ⋅ ⎛ ⎞ =⎜ − ⎟+ + − − ⎝ ⎠ 1 1 (1 ) 1 I P D K K K z z − − = + + − − (3-18) 其中, 1 2 P p K =K − Ki s ,為數位PID控制器比例增益。 KI =K Ti⋅ ,為數位PID控制器積分增益。 = K 為數位PID控制器微分增益。由上式可知,將連續時間之PID控制器離散化,其數位PID控制器之參數 會隨著取樣時間改變而改變。若是應用於數位控制上,則PID控制器的 差分方程表示式如下: ( ) ( 1) P[ ( ) ( 1)] I ( ) D[ ( ) 2 ( 1) ( 2)] u k =u k− +K e k −e k− +K ⋅e k +K e k − e k− +e k− (3-19) 上式整理可得 ( ) ( 1) ( P I D) ( ) ( P 2 D) ( 1) D ( 2) u k =u k− + K +K +K e k + −K − K e k− +K e k− (3-20) 我們定義: A=KP +KI +KD B=−KP−2KD C=KD 所以可寫成(3-21)式: ( ) ( 1) ( ) ( 1) ( 2) u k =u k− + ⋅A e k + ⋅B e k− + ⋅C e k− (3-21) 當K 、P KI、KD設計決定後,A、B、C 便可決定。 由式(3-18)可看出,數位控制器是以乘積來表示,因而必須用到乘法 器。由於數位控制器中的A、B、C為已知的固定係數,所以可以建立一 個查表法將乘法的動作簡化為查表、加法,如此可以大幅提高運算速 度,並節省面積。

3.2.2 Ziegler-Nichols 調整法

在1942年Ziegler和Nichols提出一種實用的PID控制經驗公式,可以 容易的計算出PID控制器的相關參數,其應用說明如下,圖 3-4為具有 控制器之閉迴路控制系統,令控制器為比例積分微分控制器(PID),連續 時間的PID控制式如下:( ) ( ) ( ) ( ) 1 ( ) ( ) ( ) c p i d p d i d G t K e t K e t dt K e t dt d K e t e t dt T e t T d = + + ⎡ = ⎢ + + ⎥ ⎣ ⎦

∫

∫

t ⎤ (3-22) 其中: p , i d p i K K K K T = = ⋅ Td ( ) c G s G sp( ) 圖 3-4 具有控制器之閉迴路控制系統 Ziegler-Nichols補償法求控制器係數步驟為: 1. 先設G s =c( ) K ,p 將Kp調整至系統達臨界穩定,此時Kp值即為Kp0,而 震盪的週期記為T 。 0 2. 將步驟1計算所得代入表3-3中,即可設計出PID控制器的參數 p K Ti Td 0 0.5 p p K = K 0 0.83 i T = T 0 0.6 p p K = K 0 0.5 p p K = K 0 0.5 i T = T Td =0.125T0 表 3-3 Ziegler-Nichols 調整公式3.2.3 數位PID控制器參數設計

對於我們所設計的數位脈波寬度調變器中所含的數位PID補償器, 它的型式如下列式子所表示:[ ]

[

1]

[ ]

[

1]

[

2]

d n

=

d n

− + ⋅

a e n

+ ⋅

b e n

− + ⋅

c e n

−

(3-23) 只要系數a、b、c 求出來,就可以用查表法來實現該補償器。 首先我們先考慮由數位脈波寬度調變控制積體電路與切換式直流 至直流轉換器所組成的一個離散時間閉迴路系統[3],如圖 3-5所示。 1 2047 1 4 1 z 1 q V 2 1 az bz c z + + − 2 2 2 2 1 s g s s s T V LC T T T z z RC LC RC ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ ⎛ ⎞ ⎛ ⎞ − −⎜ ⎟ + +⎜ − ⎟ ⎝ ⎠ ⎝ ⎠ ˆ 0 rref V = ˆ o V ˆd 圖 3-5 離散時間閉迴路系統 其中PID 補償器是由(4-20)式取Z 轉換而得到的。 1 1 ( ) ( ) ( ) ( ) ( ) D z =D z z− +aE z +bE z z− +cE z z−2 (3-24)把 式整理移項: 1 1 ( )(1 ) ( )( ) D z −z− =E z a bz+ − +cz−2 1 2 2 2 1 2 ( ) 1 ( ) 1 1 D z a bz cz az bz c az bz c E z z z z z z − − − + + + + + + = = = − − − (3-25) 因為其他的值皆為已知: 5 g V = V, 2 3 2.128 10 s T LC − = × Ts 7.88 10 3 RC − = × 所以Control to output 轉移函數 為: 2 ^ ^ 2 2 2 ( ) ( ) (2 ) (1 ) 0.0109 1.992 0.984 Ts Vg Vo LC Gvd z Ts Ts Ts d Z Z RC LC R Z Z = = − − + + − = − + C (3-26) 利用 Ziegler-Nichols調整法,令KI=KD=0,即設控制器為K,整個 切換式降壓型直流至直流轉換器的閉迴路轉移函數為: 2 3 3 2 1 1 1 1 ( ) ( ) 4 2047 1 1 0.0109 1 1 4 2047 1.992 0.984 19.5 3.5 10 1.992 0.984 T z K Gvd z Vq Z K Z Z m K Z Z Z − = ⋅ ⋅ ⋅ ⋅ ⋅ = ⋅ ⋅ ⋅ ⋅ ⋅ − ⋅ + ⋅ = ⋅ − ⋅ + ⋅ V Z (3-27) 利用根軌跡觀念找出系統臨界穩定之K值(即系統的閉迴路極點位於z平 面的單位元上),此時的K=Km,三個參數分別是 0.6 1.75 P m K = K = (3-28) 0.25 p m I K K ω π = = (3-29) 30 p K π = = (3-30)

其中ωm為系統的震盪頻率,可由極點位於單位圓上的角度得到。 最後可得: a=KP+KI +KD=32 b=−KP −2KD=-62 c=KD=30 我們可以使用MATLAB計算各項參數,MATLAB Code及根軌跡圖 如圖圖 3-5及圖 3-5。 num=[3.5e-3] den=[1 -1.992 0.984 0] g=tf(num,den,-1) rlocus(g) [k,pole]=rlocfind(g) k=2.9 kp=0.6*k wm=angle(pole(1)/1e6) ki=kp*wm/pi kd=kp*pi/(4*wm) 圖 3-6 MATLAB Code

圖 3-7 根軌跡圖

3.3 系統模擬

本 論 文 我 們 使 用 模 擬 軟 體MATLAB中的Simulink來進行系統模 擬,並同時觀察輸出結果是否穩定及符合我們所設計的要求。 Simulink是一種對動態系統進行模型化、模擬和分析的軟體。它支 援連續、離散或是二者混合使用在線性及非線性系統。Simulink提供了 圖形化的使用者介面(GUI),只要使用時點選和拖曳滑鼠就可以操作及用,如電源系統的模擬(SimPowerSystems),圖3-8 即為用Simulink建立 的切換式降壓型直流至直流轉換器電路。 圖 3-8 Simulink之切換式降壓型直流至直流轉換器電路 圖3-8中可分成四大區塊,依序為Buck converter、ADC、PID compensator及DPWM,其各區塊之功能介紹如下: 圖3-9為Buck converter之內部架構圖,模擬5V降至2.7V之直流電源 轉換器,我們將量測電感電流、輸出電壓及輸出電流並用Scope功能來 觀察電壓及電流的變化。

圖 3-9 Simulink之Buck converter之內部架構圖 圖3-10為ADC,輸出電壓會與參考電壓相比,產生的誤差值經過取 樣並量化,即可獲得轉換後的數位誤差信號。 圖 3-10 Simulink之ADC 圖3-11為PID compensator區塊,其作用及執行(3-23 )式,d[n-1]是前

差信號,e[n-1]為前一週期的數位誤差信號,e[n-2]為前二週期的數位誤 差信號,在此區塊中我們會代入之前利用 Ziegler-Nichols 調整法算出的 PID 控制器參數,最後這些資料經處理並相加後即可得到新的 d[n]責任 週期命令值,並送至DPWM。 圖 3-11 Simulink之PID compensator區塊圖 圖3-12為DPWM區塊,此區塊是接收來自PID compensator的責任週 期命令值 d[n],並依DPWM解析位元數輸出一相對應之責任週期,進而 控制開關切換。

圖 3-12 Simulink之DPWM區塊圖

圖3-13為由啟動至穩定及改變負載時之模擬圖形,由上而下依序 是電感電流、輸出電壓及輸出電流波形。

由圖 3-13中可以看出由啟動至穩定所需時間約0.002秒。

第4章 數位脈波寬度調變控制電壓轉

換電路硬體實現

本章主要在利用硬體去實現整個數位脈波寬度調變控制電路。使用 的硬體描述語言(HDL)為Verilog 硬體描述語言。撰寫程式的工作環境為 使用Xilinx ISE 發展軟體。這是一套由Xilinx 公司所推出用來設計 FPGA/CPLD 或嵌入式系統的發展軟體,其操作畫面如圖4-1 所示。另 外在硬體功能方面亦使用了為希科技公司所推出的系統發展實驗板 (ULINX_MB_XC3S250E_PQ208_V20A),如圖4-2 所示。

圖 4-2 Xilinx系統發展實驗板

.1 Verilog 硬體描述語言簡介

Verilog 是一個標準化的硬體描述語言,它被廣泛地使用在積體電

4

次的專用語言,在同一個模組中可以有不同層次的表示法共同存在。所

以設計者可以在同一模組中混合使用邏輯閘層次模型(Gate Level

Model)、暫存器轉移層次模型(Register Transfer Level Model)以及行 為模型(Behavioral Model)等三種不同的層次的表示法來描述所設計的 電路。 Verilog 有下列有幾項特色: 法。 路。 數庫。

.2 A/D 轉換器

我們所使用的ADC型號為ADC0820,其參考電壓由第11腳(Vref(-)) 與第 因此,ADC0820 的每一位元的解析度計算公式如下列所表示之: z 提供多種不同的設計方 z 不同的製程特性也不用考量。 z 可以用來設計各式各樣的數位電 z 一般的邏輯合成工具普遍支援Verilog。 z 許多的製造廠商也都有提供Verilog 的函4

12腳(Vref(+))所決定。所以參考電壓如可以由下列式子表示之:Vref = Vref(+) – Vref(-)

256 ref V LSB= 由上面公式知道,當我們輸入Vref(+)=5V、Vref(-)=0V 時,這時候 ADC0820 每位元(bit)之解析度即為:

5 0 0.0195 256 LSB= − = mV 當ADC0820 的第一腳(Vin)取樣到5V 電壓時,ADC0820的輸出 資料 壓的取樣,而該轉換器的輸出 電壓 (DB0~DB7)即為〝11111111〞。 由於我們要對直流至直流轉換器做電 規格可為0V~5V,所以符合我們ADC0820 的規格。另外,根據我 們目標所設計的控制積體電路規格,我們重新規劃了ADC0820電壓取樣 的特性圖,如圖4-3 所示。

e

oV

refV

max(

Δ

V

o)

19.6

qV

=

mV

oV

Δ

圖 4-3ADC0820電壓取樣的特性圖表中的Vq 即為ADC0820 的解析度,V = 5 =19.6mV。 256 q 由上表可知,當切換式直流至直流的輸出電壓大於或小於Vref 的值時, ADC0820 會輸出誤差信號(e[n])值(+16~-16)。 ADC0820我們操作在WR-RD模式下的stand-alone的工作模式,所以 4-4所示。 ADC0820的控制接腳如圖 圖 4-4ADC0820 取樣電路方塊圖

.2.1 Verilog 描述A/D 轉換器控制信號

下為我們使用 erilog 去描述ADC0820 的控制信號,使ADC0820 能正常動作。,datain,countin,e,wrout); clk,reset;

4

圖4-5 即為控制ADC0820的Verilog 描述程式,以 V module adc0820(clk,reset,intin input input [7:0]datain;input [7:0]countin; input intin; ; g [8:0]e; count; reg [1:0]count_div4; = (countin==0)? 1 : 0; ways@(negedge reset or posedge count_divact)

if(!reset)

if(count_div4 == 2'd3) ount_div4 <= 0;

e

4 + 1;

_act = (count_div4==0) & (~intin); ways@(negedge reset or posedge clk)

if(!reset) output [8:0]e; output wrout reg wrout; re reg [3:0]adc assign count_divact al begin count_div4 <= 0; else begin c els count_div4 <= count_div end end assign adc al begin adccount <= 0;

begin

if(adc_act == 1)

dccount <= adccount + 1; e

egedge reset or posedge clk) egin

if(!reset)

if((adccount>132) && (adccount<288))

end set or posedge clk) if(!reset) if(adccount==24) egin datain > 8'd154) 000; (datain < 8'd122) 0; a els adccount <= 0; end end always@(n b wrout <= 0; else begin wrout <= 1; else wrout <= 0; end always@(negedge re begin e<= 0; else begin b if( e<=9'b111110 else if e<=9'b00001000 else

e<=(9'd138) + {1'b1,(~datain)} + 1; 圖 4-5 ADC0820控制時序電路Verilog程式

4.3 數位補償器

我們利用查表法來實現數位脈波寬度調變器中的補償器。在3.2.2章 a、b 及c 的值,現在我們就利用這些值來建立 end end end endmodule 節中,我們已經求得了 一個查表。我們所需求的誤差信號(e[n])其值為+16~-16,其中代表負 數的二進位值,我們以2補數法表示之。我們取a=32、b=-62、c=30建立 此查表。其中負數的值皆使用2補數的做法。表4-1到表4-3即為所建立的 查表。表 4-3 c=30之查表

4.3.1 Verilog 描述數位補償器

以下為我們使用Verilog 去描述數位補償器的實現方式。由之前建立 之查表,將這些數值帶入硬體描述語言中。圖4-6 即為數位補償器的

Verilog 描述程式。 module pid_lut(adc_clk,reset,e,e_n1,e_n2,dutycom); input adc_clk,reset; input [8:0]e; output [8:0]e_n1,e_n2; output [10:0]dutycom;

reg [8:0]e_n1,e_n2; //e(n-1) reg [11:0]d_n1; //d(n-1)

reg [11:0]lut_mam1[0:32]; //TABLE_1 reg [11:0]lut_mam2[0:32]; //TABLE_2 reg [11:0]lut_mam3[0:32]; //TABLE_3 reg [11:0]ae,be,ce; reg [10:0]dutycom; wire[8:0]e; wire [11:0]d; assign d=d_n1+ae+be+ce; always@(d) begin if(d[11]==0) begin if(d[11:0]>11'b01110000100) dutycom<=11'b11111010110; else dutycom<=d[10:0]+11'b10001010001 ; end else begin if((~d[11:0]+1'b1)>11'b10000000000) dutycom<=11'b00001010001; else dutycom<=d[10:0]+11'b10001010001 ; end end

always@(posedge adc_clk or negedge reset) begin

if (~reset) begin e_n1<=0; e_n2<=0;

else begin e_n1<=e; e_n2<=e_n1; d_n1<=d; end end always@(e) begin case(e[5:0]) 6'b110000: ae=lut_mam1[0]; 6'b110001: ae=lut_mam1[1]; 6'b110010: ae=lut_mam1[2]; 6'b110011: ae=lut_mam1[3]; 6'b110100: ae=lut_mam1[4]; 6'b110101: ae=lut_mam1[5]; 6'b110110: ae=lut_mam1[6]; 6'b110111: ae=lut_mam1[7]; 6'b111000: ae=lut_mam1[8]; 6'b111001: ae=lut_mam1[9]; 6'b111010: ae=lut_mam1[10]; 6'b111011: ae=lut_mam1[11]; 6'b111100: ae=lut_mam1[12]; 6'b111101: ae=lut_mam1[13]; 6'b111110: ae=lut_mam1[14]; 6'b111111: ae=lut_mam1[15]; 6'b000000: ae=lut_mam1[16]; 6'b000001: ae=lut_mam1[17]; 6'b000010: ae=lut_mam1[18]; 6'b000011: ae=lut_mam1[19]; 6'b000100: ae=lut_mam1[20]; 6'b000101: ae=lut_mam1[21]; 6'b000110: ae=lut_mam1[22]; 6'b000111: ae=lut_mam1[23]; 6'b001000: ae=lut_mam1[24]; 6'b001001: ae=lut_mam1[25]; 6'b001010: ae=lut_mam1[26]; 6'b001011: ae=lut_mam1[27]; 6'b001100: ae=lut_mam1[28]; 6'b001101: ae=lut_mam1[29]; 6'b001110: ae=lut_mam1[30]; 6'b001111: ae=lut_mam1[31]; 6'b010000: ae=lut_mam1[32]; endcase end always@(e_n1)

begin case(e_n1[5:0]) 6'b110000: be=lut_mam2[0]; 6'b110001: be=lut_mam2[1]; 6'b110010: be=lut_mam2[2]; 6'b110011: be=lut_mam2[3]; 6'b110100: be=lut_mam2[4]; 6'b110101: be=lut_mam2[5]; 6'b110110: be=lut_mam2[6]; 6'b110111: be=lut_mam2[7]; 6'b111000: be=lut_mam2[8]; 6'b111001: be=lut_mam2[9]; 6'b111010: be=lut_mam2[10]; 6'b111011: be=lut_mam2[11]; 6'b111100: be=lut_mam2[12]; 6'b111101: be=lut_mam2[13]; 6'b111110: be=lut_mam2[14]; 6'b111111: be=lut_mam2[15]; 6'b000000: be=lut_mam2[16]; 6'b000001: be=lut_mam2[17]; 6'b000010: be=lut_mam2[18]; 6'b000011: be=lut_mam2[19]; 6'b000100: be=lut_mam2[20]; 6'b000101: be=lut_mam2[21]; 6'b000110: be=lut_mam2[22]; 6'b000111: be=lut_mam2[23]; 6'b001000: be=lut_mam2[24]; 6'b001001: be=lut_mam2[25]; 6'b001010: be=lut_mam2[26]; 6'b001011: be=lut_mam2[27]; 6'b001100: be=lut_mam2[28]; 6'b001101: be=lut_mam2[29]; 6'b001110: be=lut_mam2[30]; 6'b001111: be=lut_mam2[31]; 6'b010000: be=lut_mam2[32]; endcase end always@(e_n2) begin case(e_n2[5:0]) 6'b110000: ce=lut_mam3[0]; 6'b110001: ce=lut_mam3[1]; 6'b110010: ce=lut_mam3[2]; 6'b110011: ce=lut_mam3[3]; 6'b110100: ce=lut_mam3[4];

6'b110110: ce=lut_mam3[6]; 6'b110111: ce=lut_mam3[7]; 6'b111000: ce=lut_mam3[8]; 6'b111001: ce=lut_mam3[9]; 6'b111010: ce=lut_mam3[10]; 6'b111011: ce=lut_mam3[11]; 6'b111100: ce=lut_mam3[12]; 6'b111101: ce=lut_mam3[13]; 6'b111110: ce=lut_mam3[14]; 6'b111111: ce=lut_mam3[15]; 6'b000000: ce=lut_mam3[16]; 6'b000001: ce=lut_mam3[17]; 6'b000010: ce=lut_mam3[18]; 6'b000011: ce=lut_mam3[19]; 6'b000100: ce=lut_mam3[20]; 6'b000101: ce=lut_mam3[21]; 6'b000110: ce=lut_mam3[22]; 6'b000111: ce=lut_mam3[23]; 6'b001000: ce=lut_mam3[24]; 6'b001001: ce=lut_mam3[25]; 6'b001010: ce=lut_mam3[26]; 6'b001011: ce=lut_mam3[27]; 6'b001100: ce=lut_mam3[28]; 6'b001101: ce=lut_mam3[29]; 6'b001110: ce=lut_mam3[30]; 6'b001111: ce=lut_mam3[31]; 6'b010000: ce=lut_mam3[32]; endcase end endmodule 圖 4-6 補償器 Verilog 描述程式

圖4-7為PID之輸入與輸出的模擬結果。 圖 4-7 PID輸入與輸出模擬圖

4.4 數位脈波寬度調變器

我們要設計一個數位脈波寬度調變器,其電路方塊如圖4-8所示,其 中包含一個4-bit計數器、二個4-bit比較器、16個D型正反器、16×12的多 工器、二個AND閘及一個RS正反器。c n c n c n 2 :1nd c n d n n c n 圖 4-8 混合式(Hybrid)DWPM架構圖

由圖可知,此混合式(Hybrid)DWPM中4 bits Delay-line型的DPWM 與一個4-bit 計數型DPWM合成,讓這個數位脈波寬度調變器可以提供 8-bit的解析度。

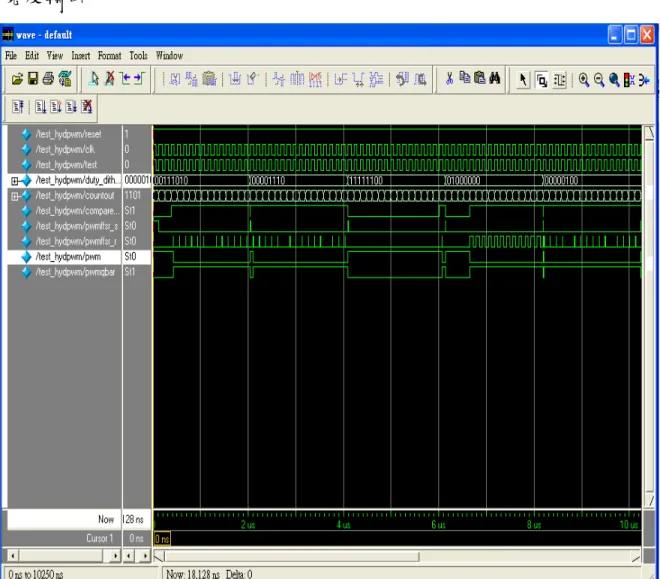

4.4.1 Verilog 描述數位數位脈波寬度調變器

圖4-9所示,為我們使用Verilog 去描述數位數位脈波寬度調變器的 控制信號及功能。

`include "delayline.v" `include "counter.v"

module hydpwm(clk, ,reset,duty_dith,pwmout); input clk,,reset; input [7:0]duty_dith; output pwmout; reg compareout; reg pwmffsr_s; reg pwmffsr_r; reg cc; reg [7:0]duty_dith_reg; wire pwmqbar,pwm; wire [7:0]duty_dith; wire [3:0]countout; wire [16:0]delay; wire [14:0]q; wire q15; counter u1(clk,reset,countout); delayline delayline1(reset,delayin,delay,q,q15,delayreset);

assign delayin = test; assign delayreset =0;

//-- SET RS_Flip-Flop at counter=0 ----

always@(negedge reset or countout or duty_dith[6:0] or q15) begin if(~reset | (countout[3:0]==3'b000)&(q15==1)&(cc==0)) begin pwmffsr_s<=1; duty_dith_reg[7:0] <= duty_dith[7:0]; end else pwmffsr_s<=0; end //-- Counter Compare --- always@(countout or duty_dith_reg[7:4]) begin if(countout[3:0]>=duty_dith_reg[7:4]) compareout <= 1; else

//----Counter Check (set=1 one times in switch cycle)

always@(negedge reset or negedge fsw_clk or negedge pwmffsr_s) begin if(~reset | ~fsw_clk) cc<=0; else if(~pwmffsr_s) cc<=1; end //-- Delayline Multiplexer ---

always@(duty_dith_reg[3:0] or q or delay or compareout) begin

case(duty_dith_reg[3:0])

4'b0000 : pwmffsr_r <= delay[0] & compareout; 4'b0001 : pwmffsr_r <= q[1] & compareout; 4'b0010 : pwmffsr_r <= q[2] & compareout; 4'b0011 : pwmffsr_r <= q[3] & compareout; 4'b0100 : pwmffsr_r <= q[4] & compareout; 4'b0101 : pwmffsr_r <= q[5] & compareout; 4'b0110 : pwmffsr_r <= q[6] & compareout; 4'b0111 : pwmffsr_r <= q[7] & compareout; 4'b1000 : pwmffsr_r <= q[8] & compareout; 4'b1001 : pwmffsr_r <= q[9] & compareout; 4'b1010 : pwmffsr_r <= q[10] & compareout; 4'b1011 : pwmffsr_r <= q[11] & compareout; 4'b1100 : pwmffsr_r <= q[12] & compareout; 4'b1101 : pwmffsr_r <= q[13] & compareout; 4'b1110 : pwmffsr_r <= q[14] & compareout; 4'b1111 : pwmffsr_r <= q15 & compareout; endcase end

//-- SR Flip-Flop with non-clock --- nor norqbar(pwmqbar,pwmffsr_s,pwm); nor norq(pwm,pwmffsr_r,pwmqbar); Endmodule module counter(clk,reset,countout); input clk,reset; output [3:0]countout; reg [3:0]countout;

![圖 2-10 Delay-line 形式的數位脈波寬度調變產生器(DPWM)控制波形 將上述兩種 DPWM 的優缺點做一個整理,如表 2-1。 Type 缺點 優點 Delay-lineFast-counter 解析度越高所需 晶片面積越大解析度越高所需計數頻率越高低時脈頻率低電源消耗小面積 表 2-1 二種 DPWM 的優缺點比較 第三種是混合式(Hybrid)的DWPM [3],此種DPWM是將計數型及 Delay](https://thumb-ap.123doks.com/thumbv2/9libinfo/8504570.185438/25.918.186.730.104.454/解析度越高所晶片面積越大解析度越高所需計數頻優缺是混合式Hybrid.webp)

![圖 3-9 Simulink之Buck converter之內部架構圖 圖3-10為ADC,輸出電壓會與參考電壓相比,產生的誤差值經過取 樣並量化,即可獲得轉換後的數位誤差信號。 圖 3-10 Simulink之ADC 圖3-11為PID compensator區塊,其作用及執行(3-23 )式,d[n-1]是前](https://thumb-ap.123doks.com/thumbv2/9libinfo/8504570.185438/53.918.140.776.121.454/相比誤差值經過取樣並量化即可獲得轉換後的數位誤差信號區塊其作.webp)