國立高雄大學電機工程學系(研究所)

碩士論文

扇出型球閘陣列封裝凸塊焊接及平面度問題改進研究

The Improvement of Bump Joint and Coplanarity of

Fan-out Ball Grid Array Package

研究生:劉瑋淮

指導教授:施明昌教授

ii

扇出型球閘陣列封裝凸塊焊接及平面度問題改進研究

指導教授:施明昌 博士 國立高雄大學 電機工程學系 學生:劉瑋淮 國立高雄大學電機工程所 摘要 由於半導體晶圓製造技術的進步,隨著單位面積中電晶體密度的提高,高 接腳(I/O)數、窄線距在高階 IC 封裝技術上一直以來都是一個不斷向前邁進 的挑戰。不同應用領域的IC 裝置尺寸隨著性能的提升,朝著兩個不同的極端推 進:應用於計算機技術的高效能運算、圖形處理器、網路技術等的IC 裝置朝大 尺寸的方向前進;而應用於3C 產品、移動式裝置、穿戴式裝置則往輕薄短小 的目標設計。裝置尺寸的兩極化,標誌著產品對於IC 性能提升的要求更高,對 於封裝技術的挑戰也越大。而所謂扇出型(Fan-out)晶圓技術即在這樣的需求 下產生,在高接腳數、窄線距的條件下,能大幅降低半導體元件封裝的失效風 險。扇出型晶圓技術在晶圓級(FO WLP, fan-out wafer level package)元件封裝 製程的技術較為成熟,而將扇出型晶圓應用在球閘陣列(BGA, ball grid array) 形式的元件,封裝製程上則有許多挑戰。本論文研究即針對扇出型晶圓於球閘 陣列(BGA)形式 IC 裝置的封裝製程做評估,並針對晶圓凸塊焊接失效模式 (Failure mode)及元件平面度不良等問題提出解決方法。iii

The Improvement of Bump Joint and Coplanarity of

Fan-out Ball Grid Array Package

Advisor(s): Dr. Ming Chang Shih Department of Electrical Engineering

National University of Kaohsiung

Student: WeiHuai Liu

Department of Electrical Engineering National University of Kaohsiung

ABSTRACT

With the development of the technologies of semiconductor manufacturing, high density chip package, in which, high I/O and fine-pitch/ ultra-fine pitch had been challenging the technology of advanced IC assembly. In various areas of applications, package sizes of integrated circuits such as high performance computing, graphic processor units, and networking which package size goes to bigger and denser, such that the technology of fan-out which can remarkably reduce the risk of failure on the assembly processes. This study we will focus on the evaluations of substrate assembling of BGA with the fan-out wafers, and by analyzing the failure modes to develop solutions of improving bump joint and package co-planarity.

1

目錄

摘要---ii ABSTRACT---iii 圖目錄---2 表目錄---3 第一章 研究動機---4 1.1 覆晶封裝產品窄線距需求趨勢---4 1.2 扇出型晶圓製程介紹---6 第二章 扇出型晶圓覆晶封裝製程評估---8 2.1 覆晶封裝製程介紹---8 2.2 覆晶封裝製程能力指標---9 2.2.1 封裝製程測試樣品資訊及結構---9 2.2.2 封裝製程測試結果---11 2.3 失效模式分析---11 第三章 實驗設計與結果---14 3.1 材料結構的熱膨脹因子---14 3.2 溫度變化因子---15 3.3 實驗對照及結果---16 第四章 結論---23 參考文獻---242

圖目錄

圖1-17 奈米晶圓 60 微米凸塊間距切片 SEM---5 圖1-27 奈米晶圓 60 微米凸塊間距 IC 元件橋接缺點切片 SEM---5 圖1-3 扇出型晶圓及凸塊結構圖---6 圖1-4 扇出型晶圓製程流程---7 圖2-1 覆晶封裝製程流程---8 圖2-2 測試樣品結構示意圖---10 圖2-3 未焊失效模式 X-ray---12圖2-4 晶粒切片 SEM die gap 量測---12

圖2-5 熱變形表面陰影疊紋分析晶粒部分---13 圖2-6 熱變形表面陰影疊紋分析基板部分---13 圖2-7 晶粒及基板熱變形行為---14 圖3-1 半導體封裝產品結構各部分材料熱膨脹係數---15 圖3-2 產品熱膨脹因子之控制---16 圖3-3 8mil 及 10mil 厚度晶粒及基板之表面陰影疊紋分析結果---18

圖3-4 8mil 晶粒凸塊未焊及 10mil 晶粒無異常 X-ray 撿驗圖片---19

圖3-5 10mil 晶粒切片 die gap 量測---19

圖3-6 元件封裝後平面度分佈(25C)---20

圖3-7 元件封裝後平面度分佈(260C)---20

圖3-8 信賴度測試預處理結果 T-SAM---22

3

表目錄

表1-1 線徑/線距趨勢---4 表2-1 封裝製程指標---9 表2-2 測試樣品資訊及結構---10 表2-3 封裝置成測試結果---11 表3-1 熱膨脹因子的控制對產品翹曲的影響---16 表3-2 凸塊未焊及元件平面度改善之實驗設計---18 表3-3 最適晶粒厚度及成型模料之實驗結果---21 表3-4 最適晶粒厚度及成型模料之信賴度實驗結果---214

第一章 研究動機

1.1 覆晶封裝產品窄線距需求趨勢

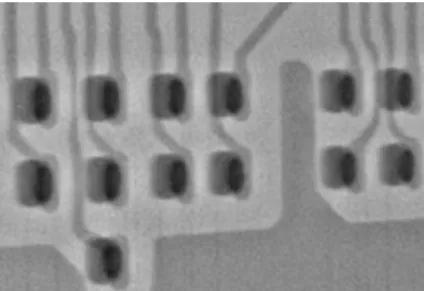

高接腳(I/O)數及窄線距的需求在覆晶封裝領域中一直不斷突破極限。隨 著IC 裝置性能的提升,單位晶粒面積中的 I/O 數量也相對的提高以應付高效能 的需求。而在單位面積中的I/O 數量越高,相應的在晶圓及基板的佈線就需要 以窄線距的設計才能達成這個需求。IC 封裝技術的演變從早期的拉線(wire bonding)發展為覆晶封裝,最主要的原因就是因為覆晶的方式可在單位面積晶 粒上開出更多的I/O 數,另一方面,銅柱凸塊(Cu pillar bump)的發明也是為 解決高I/O 密度下焊錫凸塊(solder bump)易造成橋接(bridging)的失效模 式。 見表 1-1 所示,目前已量產的 28 奈米晶圓,最小線徑/線距為 15 微米。而 7 奈米晶圓最小線徑/線距 7 微米。預估未來 5 奈米晶圓將會達到最小線徑/線距 5 微米。 表1-1 線徑/線距趨勢 從焊錫凸塊到銅柱凸塊的演變,可以看出越密集的的 I/O 數越是需要減少 凸塊錫量以降低橋接風險。在此,凸塊間距(bump pitch)可做為判斷 I/O 密集 度的一個指標。5 下圖 1-1 為 7 奈米晶圓 60 微米凸塊間距(bump pitch)的 IC 元件在迴焊後 的切片SEM 畫面。以目前量產的能力來說,凸塊間有線路(trace)通過的最小 凸塊間距為100 微米過兩條線,UBM-to-trace 距離 15 微米。顯然圖 1-1 這個 結構大大的挑戰了目前的封裝能力。 圖1-2 為 7 奈米晶圓 60 微米凸塊間距的 IC 元件橋接缺點的切片 SEM 畫 面。可看見凸塊的錫與線路橋接的狀況。 圖1-1 7 奈米晶圓 60 微米凸塊間距切片 SEM 圖1-2 7 奈米晶圓 60 微米凸塊間距 IC 元件橋接缺點切片 SEM

6 隨著晶圓技術的提升,更密集的 I/O 數的晶圓設計已是必然的趨勢。前面 的案例顯示銅柱凸塊的能力已不能應付未來高性能IC 元件的封裝。

1.2 扇出型晶圓製程介紹

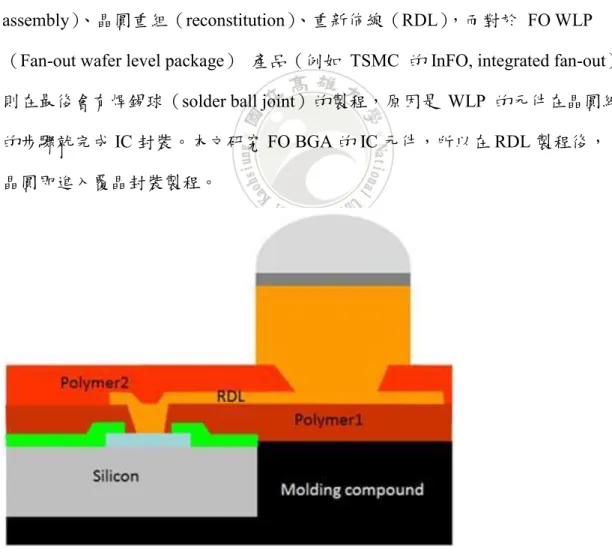

在單位晶粒面積中相同 I/O 數下,扇出型晶圓利用重新佈線(re-distribution)將原來的 I/O 位置往外拉出,如圖 3-1 所示,使凸塊生成於重新佈 線層(re-distribution layer, RDL)。這個方法使得凸塊間距在相同 I/O 密度下大 幅增加,而對於封裝製程上橋接的風險則大幅減少。圖 1-4 所示為扇出型晶圓製程流程圖,其製程可分為前封裝作業(pre-assembly)、晶圓重組(reconstitution)、重新佈線(RDL),而對於 FO WLP (Fan-out wafer level package) 產品(例如 TSMC 的 InFO, integrated fan-out) 則在最後會有焊錫球(solder ball joint)的製程,原因是 WLP 的元件在晶圓級 的步驟就完成IC 封裝。本文研究 FO BGA 的 IC 元件,所以在 RDL 製程後, 晶圓即進入覆晶封裝製程。

7 圖1-4 扇出型晶圓製程流程

前置作業部分包含晶圓研磨及切割。接著將切割開的晶粒置於金屬載板以 壓鑄成型(compression molding)完成重組晶圓。重組晶圓進入長凸塊

(bumping)製程,這個步驟即利用重新佈線層將原 I/O 位置拉出再於新的 I/O 位置電鍍凸塊。

8

第二章 扇出型晶圓覆晶封裝製程評估

2.1 覆晶封裝製程介紹

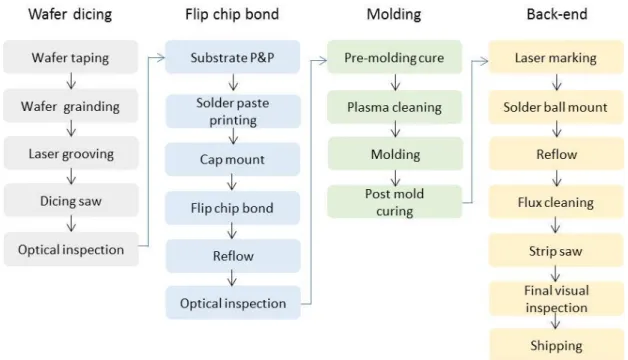

覆晶(Flip chip)封裝技術為目前高階 IC 封裝最主要的方式,較之以往的 打線封裝,其優點即在於可在單位晶粒面積上提供更多的接腳(I/O)數。用於 覆晶封裝的晶圓在長凸塊(bumping)製程即將焊錫電鍍在 I/O 位置上,每一個 凸塊即為一個接腳。長凸塊完成的晶圓接著進入覆晶封裝製程。 覆晶封裝製程主要分為四大部分:晶圓切割(Wafer dicing)、覆晶迴焊 (Flip chip bond)、壓模成型(Molding)、後段正印及植球(Back-end)。如圖 2-1 所示。圖2-1 覆晶封裝製程流程

晶圓切割部分包含晶圓研磨、雷射切割、晶圓切割等製程。完成切割的晶 圓即成為矽晶粒(silicon dice,或稱 die)。晶粒以膠膜固定與承載,供覆晶迴焊 取用。覆晶迴焊包含錫膏塗佈、被動元件置放、覆晶、及迴焊。迴焊後,晶粒 即已與基板線路接合完成。為強化元件結構,覆晶迴焊後,會以壓模成型方式 將晶粒及被動元件完整包覆,以達保護作用。接著後段製程包含雷射打印、焊 錫球及去框成型。去框成型後即完成半導體封裝。

9

2.2 覆晶封裝製程能力指標

封裝良率是指封裝製程的整體產出良率,而要有高封裝良率則需要有高製 程良率,高製程良率則要求製程能力之提升。覆晶封裝製程能力隨元件設計之 趨精密,製程能力也相應提升。下表2-1 依覆晶封裝各製程列出其能力指標, 其相應的規格為目前業界及國際規範所採用的。至於後段推球測試規格則是與 本研究中所採用的測試樣品結構有關。Stage Index Criteria

Wafer dicing

Target thickness 200 +/-15um

Roughness <0.08um

Kerf-width 30 ~ 50 um

Flip chip bond

Die gap 30um~70um

X-ray defect No defect allowed

Flux cleaning result No flux residue allowed

Molding

Contact angle <37degree

Strip warpage-short side(max-min) <3mm

Strip warpage-long side(max-min) <6mm

Mold void Not over 2 bumps

Back-end

Solder ball shear >200g

Ball shear fracture mode Solder residue>70%

T-SCAM No defect allowed

Co-planarity <80um 表2-1 封裝製程指標

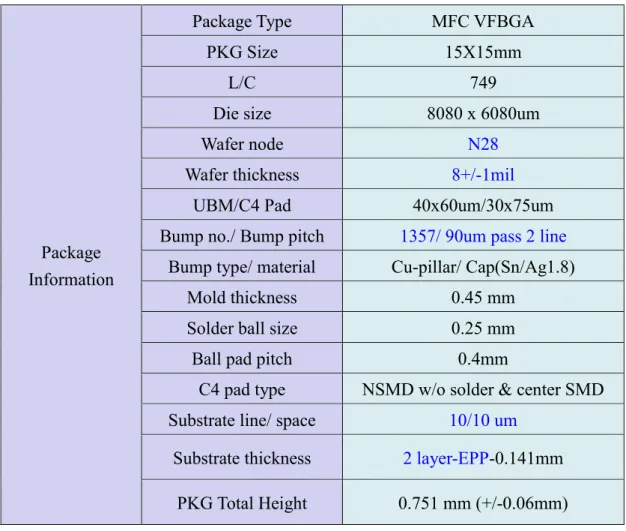

2.2.1 封裝製程測試樣品資訊及結構

下表 2-2 為本研究所使用的測試樣品的相關資訊,包含結構、尺寸、接腳 數、晶粒尺寸、晶圓厚度、凸塊間距及線距等資訊。其中需要特別注意的是本 研究使用的測試晶圓是28 奈米晶圓,另外,凸塊間距是 90um,凸塊間過兩條10

線,線徑10um、線距 10um,因此最小 UBM-to-trace 距離是 10um。晶圓(晶 粒)厚度為8mil(即 200um),mold thickness 為 450um。如圖 2-2 所示。

Package Information

Package Type MFC VFBGA

PKG Size 15X15mm

L/C 749

Die size 8080 x 6080um

Wafer node N28

Wafer thickness 8+/-1mil

UBM/C4 Pad 40x60um/30x75um Bump no./ Bump pitch 1357/ 90um pass 2 line

Bump type/ material Cu-pillar/ Cap(Sn/Ag1.8) Mold thickness 0.45 mm

Solder ball size 0.25 mm Ball pad pitch 0.4mm

C4 pad type NSMD w/o solder & center SMD Substrate line/ space 10/10 um

Substrate thickness 2 layer-EPP-0.141mm PKG Total Height 0.751 mm (+/-0.06mm)

表2-2 測試樣品資訊及結構

11

2.2.2 封裝製程測試結果

針對前列封裝製程指標,各結果如表 2-3 所列,覆晶迴焊製程 X-ray 檢驗 顯示高缺陷率(defect rate 24/138,17%),另外,在後段平面度部分,平面度最 大值79um,製程 Cpk<1.33,也就是說,平面度的變異太大、很不穩定,應改 善產品結構的平面度。而針對這兩種指標的改善將構成本研究的主要內容。 表2-3 封裝製程測試結果2.3 失效模式分析

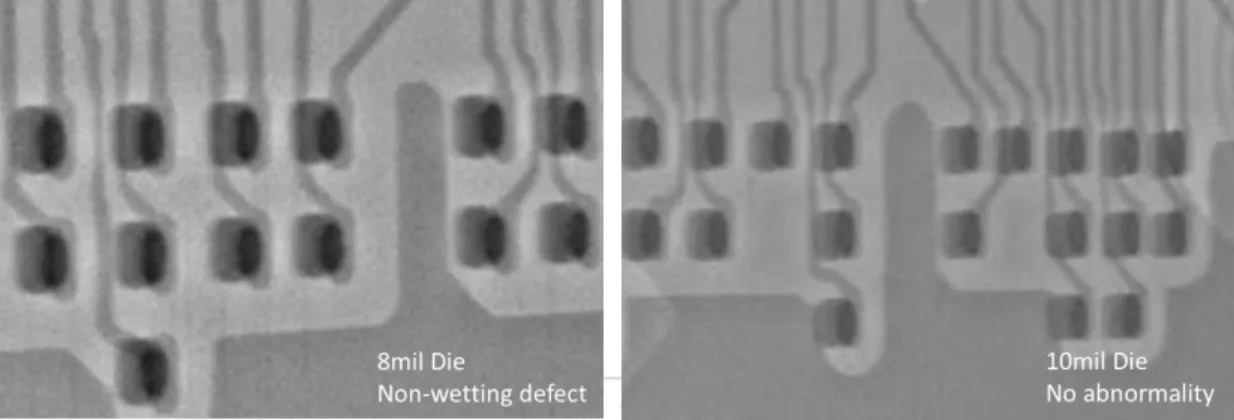

如上節所述,測試樣品在覆晶迴焊後,X-ray 檢驗顯示 17%的缺陷率,其 失效模式為未焊,如圖2-3 所示,未焊模式為一整排 bump 均未焊。由圖 2-4 所 示,針對晶粒做切片,未焊凸塊集中在晶粒中間部分且中間部分die gap 為 59.56um。12 圖2-3 未焊失效模式 X-ray

圖2-4 晶粒切片 SEM die gap 量測

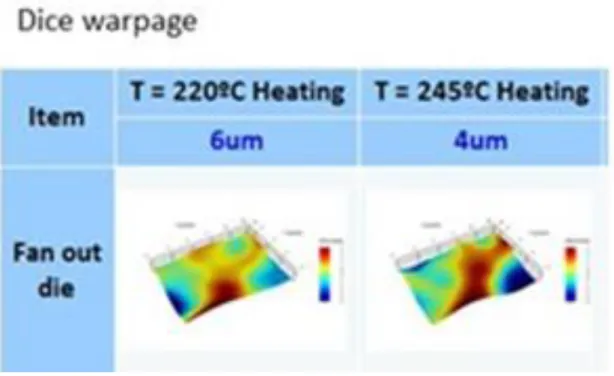

依上述分析,再針對失效之樣品做熱變形表面陰影疊紋(Shadow Moiré)分 析,得圖2-5 及圖 2-6 之結果,顯示晶粒及基板在迴焊溫度(220~245’C)下,

翹曲行為的不同,並可做如圖2-7 關於晶粒及基板熱變形行為的不匹配的判

斷,即晶粒為凸形(convex)而基板為凹形(concave)致使未焊凸塊集中於中 間部分。

13

圖2-5 熱變形表面陰影疊紋分析晶粒部分(凸形,convex)

14 圖2-7 晶粒及基板熱變形行為 目前為止,針對凸塊未焊的失效模式分析可判斷,晶粒及基板的翹曲行為 之不匹配性應為最主要的原因。另一方面,凸塊未焊對於封裝失效的嚴重性來 說,是高於平面度不良的,所以失效模式之改善將會以未焊為主要考量。並 且,為改善晶粒及基板翹曲行為的匹配性,整體結構的平面度亦應改善。

第三章 評估實驗設計

3.1

材料結構的熱膨脹因子

半導體封裝產品,如下圖3-1 所示,可以分為下列四個主要結構的組合: 成型模料(Epoxy Molding Compound, EMC. 或只稱 Compound)、晶粒(Dice/ Die)、底膠(Under-fill 也是ㄧ種環氧樹脂的材料,所以也稱 Epoxy)、及基板 (Substrate)。每一個組成部分的材料不同,有其各自的膨脹特性,圖 3-1 所列 出的α 數值為各別材料的參考膨脹係數,表示各別材料的膨脹係數約略落在哪 些範圍。因為這些不同膨脹特性的材料被封裝在一起,整個結構就形成一個不 同膨脹係數的材料應力相抗衡的整體,在經過熱製程後,產品結構因脹縮而產 生應力的抗衡下,使得結構翹曲及變形。產生這個現象的原因稱為膨脹係數不 匹配(CTE mis-match)。在本文第二章 2.3 節中即以熱變形表面陰影疊紋的方15 法來分析產品結構在熱變化過程中的翹曲行為,此即材料結構的熱膨脹因子的 效應。 圖3-1 半導體封裝產品結構各部分材料熱膨脹係數 產品材料的熱膨脹因子可對產品本身造成很大的影響,即如第二章2.3 節 的分析,熱膨脹因子造成未焊的失效模式。而高熱膨脹係數不匹配性亦會造成 產品結構過於翹曲變形,即平面度不良,如本文表2-3 所列,測試樣品的平面 度雖然都在規格之內,但製程能力指標卻很低(Cpk<1.33),顯示產品的翹曲變 形程度很大。所以,在選擇材料的時候勢必要考慮到材料的熱膨脹因子,即熱 膨脹係數的匹配性。而另一方面,我們也可以利用對熱膨脹因子的控制來改變 產品翹曲的型態。如下表3-1 所示,比較 compound 在不同晶粒厚度下對產品翹 曲行為的影響。參考圖3-2 所示,可對此表格有比較具象的理解,即透過改變 晶粒厚度以改變成型模料的體積從而增加或減少成型模料的熱膨脹因子對產品 翹曲的影響。可得如下結論: (1)在晶粒厚度從 6mil 增加到 8mil 時,產品的翹曲模式改變了,從凸凹凸變 成凹凸凹。 (2)晶粒厚度從 8mil 增加到 10mil,產品翹曲模式沒有改變,但是因為成型模 料的體積更小了,基板向下拉的效應更強。 (3)產品結構的翹曲模式可以透過調整成型模料的體積而改變。

16 表3-1 熱膨脹因子的控制對產品翹曲的影響 圖3-2 產品熱膨脹因子之控制

3.2

溫度變化因子

由第二章2.3 節失效分析之結果及 3.1 節所述得知,產品結構的翹曲特性 在溫度變化的過程中,事實上即是各材料熱應力抗衡的結果。而在本研究中 所使用的測試樣品的大量未焊失效模式即因晶粒與基板在迴焊溫度下的翹曲 模式的差異造成。覆晶迴焊製程是覆晶封裝的重要製程,而焊錫凸塊的熔點 約為221C(本研究之測試樣品使用銅柱凸塊錫-1.8 銀焊料/Cu pillar Sn-1.8Ag,見表 2-2),迴焊溫度的最高溫(peak temperature)為 245C,迴焊爐 溫從220C 升溫到 245C 再降回 220C 這段溫度稱為迴焊溫度(reflow temperature),而這段時間稱為迴焊時間(reflow time),依圖 2-6 及圖 2-7 所 示,晶粒及基板在迴焊時間中的翹曲行為是造成晶粒中間部分凸塊未焊的主 要原因。 另一方面,半導體元件最後的關鍵封裝指標,即平面度(co-planarity) 的表現的提升將決定元件上板(SMT)良率及板級信賴度(board level17 reliability)的表現。同樣的,當元件上板迴焊進入迴焊時間時,元件平面度 不良將導致上板失敗,另外,平面度不良將造成元件-焊錫-印刷電路板 (PCB)之間的結構在溫度循環測試中產生很大的應力以致不能通過信賴度 測試。當然,針對半導體元件封裝製程,目標是提升元件平面度之製程能力 指標(Cpk)。

3.3

實驗對照及結果

本研究針對凸塊未焊及元件平面度之改善,執行下述實驗以決定最適之晶 粒厚度及成型模料之種類: (1) 針對不同厚度之晶粒進行表面陰影疊紋分析,觀察並量測各別厚度之晶 粒於25C、220C、245C 等溫度下其翹曲之變化與基板翹曲之變化做比 較,以選擇最適之晶粒厚度。 (2) 比較使用不同熱膨脹係數之成型模料的封裝元件之封裝後的平面度及利 用表面陰影疊紋分析量測各別於260C 溫度下的產品翹曲,以選擇最適 之晶粒厚度。 針對上述之實驗計畫設計下表3-2。如表所示,對照組(POR)所使用晶粒 厚度為8mil(200um),實驗組則使用 10mil(250um)厚度。成型模料則有對 照組所使用的G311AC 及實驗組的 XB8732,相較於對照組所使用的成型模 料,實驗組所使用的是相對低熱膨脹係數的成型模料。18

Leg S.S. Die thickness Compound CTE(α1/α2)

Modulus (@260C) Remark POR 138 8 mil Sumitomo G311AC 10/40 ppm/C 950 1 10 mil 2 Sumitomo XB8732 9/31 ppm/C 1560 Low CTE 表3-2 凸塊未焊及元件平面度改善之實驗設計 不同厚度晶粒之表面陰影疊紋分析如下結果。 圖3-3 8mil 及 10mil 厚度晶粒及基板之表面陰影疊紋分析結果 由圖3-3 之量測結果得知,8mil 及 10mil 厚度晶粒在 25C 溫度下,翹曲模 式與基板的翹曲模式相符,皆為凸形。溫度升高到凸塊焊錫熔點(220C)時, 8mil 晶粒之翹曲模式仍為凸形,平面度從 10um 降為 6um。至於 10mil 晶粒, 其翹曲模式則轉換為與基板較一致的凹形,其與基板的平面度各別為-13um

及-19

11um。溫度升高到最高爐溫(245C)時,8mil 晶粒的翹曲模式還是凸形,平面 度降至4um。而 10mil 晶粒與基板仍為一致的凹形,平面度各別為-15um 及-11um。由此可以判斷,10mil 晶粒在覆晶迴焊時,應可改善凸塊未焊之失效模 式。而事實上,本實驗之結果亦證實10mil 晶粒無未焊發生。如下圖 3-4, 8mil 晶粒及 10mil 晶粒凸塊 X-ray 檢驗所示。如下圖 3-5 為 10mil 晶粒切片, die gap 量測為 45.11um。

圖3-4 8mil 晶粒凸塊未焊及 10mil 晶粒無異常 X-ray 撿驗圖片

圖3-5 10mil 晶粒切片 die gap 量測

針對不同熱膨脹係數之成型模料之比較結果如圖3-6 及圖 3-7 所示。元件 完成封裝製程後,在常溫下的平面度可見圖3-6,得知,使用 G311AC 成型模 料之樣品在晶粒厚度增加後平面度有改善,當晶粒從8mil(200um)增加到 10mil(250um),平面度平均值下降 13um(63um 降到 50um)。10mil 晶粒樣品 使用XB8732 成型模料,元件平面度相較使用 G311AC 的樣品平面度平均值下 降11um(50um 降到 39um)。並且,10mil 晶粒使用 XB8732 成型模料,平面度

20 的製程能力指標已達大於1.33 的目標。由此可判斷 XB8732 成型模料應為最適 之材料。 為清楚展示實驗結果,請見表3-3,針對 8mil 及 10mil 晶粒覆晶迴焊及使 用G311AC 及 XB8732 之元件平面度之結果如表列。 圖3-6 元件封裝後平面度分佈(25C) 圖3-7 元件封裝後平面度分佈(260C)

21 Leg S.S. Die thickness Compound Result Non-wetting Copl/ um

max min avg stdev Cpk

POR 138 8 mil Sumitomo G311AC 20/138 85 45 63 9.29 0.61 1 10 mil 0/138 70 28 50 12.5 0.8 2 Sumitomo XB8732 0/138 67 24 39 10.1 1.35 表3-3 最適晶粒厚度及成型模料之實驗結果 由表3-3 可知,10mil 晶粒可改善凸塊未焊之失效模式,並且使用低熱膨脹 係數之成型模料可提升平面度製程指標及平面度製程能力指標大於1.33。 針對10mil 晶粒搭配 XD8732 成型模料的信賴度測試結果如下表 3-4 所 示,通過1000 次溫度循環測試。並如圖 3-7 及圖 3-8 所示,預處理(pre-conditioning)及溫度循環(TCT)1000 次後各別的穿透式超音波掃描(T-SAM)之結果,皆無發現缺點或異常。

Compound Die thickness S.S. T0

REL MSL3 TCT 200 TCT 500 TCT 1000 XD8732 10mil (250um) 112 0/112 Pass (0/112) Pass (0/112) Pass (0/112) Pass (0/112) 表3-4 最適晶粒厚度及成型模料之信賴度實驗結果

22 圖3-8 信賴度測試預處理結果 T-SAM

23

第四章 結論

本研究分析高階半導體封裝隨著晶圓技術朝五奈米數發展的過程中,單位 晶圓面積中電晶體的密度提高,晶粒凸塊密度(I/O 數)亦隨之提高,對於封裝 製程產生的挑戰更鉅。高凸塊密度下對於窄線距之要求即更高。而當凸塊間距 (Bump pitch)只有 60 微米的情況下,封裝製程即面臨高焊錫橋接的風險。並 預估晶圓技術達五奈米的情況下,凸塊間距將小於60 微米。扇出型晶圓技術即 克服此封裝上之困難而使七奈米或五奈米晶圓之半導體元件之封裝失效風險大 幅降低。故而於第一章即針對扇出型晶圓之製程做一介紹。 第二章部分,介紹半導體覆晶封裝之製程,並較詳盡說明製程及其製程指 標,以為後續針對扇出型晶圓導入覆晶封裝之製程評估作準備。 封裝製程測試結果顯示,覆晶迴焊後產生大量凸塊未焊缺點及元件平面度 製程能力指標偏低,本研究即針對此兩項缺點提出解決及改善之方向。 根據本研究之結果得到下述結論: (1) 針對扇出型晶圓覆晶封裝製程,應採取低熱膨脹係數的成型模料配上厚 粒晶才能解決平面度及凸塊接合失效的問題。 (2) 以本研究為例,一個 15X15mm 產品尺寸, 8X6mm 晶粒尺寸,應以 CTE(α1/α2) 為 9/31 ppm/C,晶粒厚度 10mil 的結構才能通過 REL 驗證。 (3) 因未來對於高階扇出型晶圓產品會有產品趨於厚度更薄的需求,因此需24