行政院國家科學委員會專題研究計畫 成果報告

微機電技術整合金氧半場效電晶體射頻積體電路(2/2)

計畫類別: 個別型計畫 計畫編號: NSC92-2213-E-009-049- 執行期間: 92 年 08 月 01 日至 93 年 07 月 31 日 執行單位: 國立交通大學電信工程學系(所) 計畫主持人: 周復芳 計畫參與人員: 陳一宇、呂盈蒼、陳政良、劉炳宏、連偉誠 報告類型: 完整報告 處理方式: 本計畫可公開查詢中 華 民 國 93 年 12 月 16 日

行政院國家科學委員會補助專題研究計畫成果報告

※※※※※※※※※※※※※※※※※※※※※※※※※

※ ※

※

微機電技術整合金氧半場效電晶體

※

※

射頻積體電路

※

※※※※※※※※※※※※※※※※※※※※※※※※※

計畫類別:■個別型計畫 整合型計畫

計畫編號:NSC 91-2213-E-9-129

執行日期: 民國 91 年 8/1 至 民國 93 年 7/31

計畫主持人:周復芳

計畫參與人員:

陳一宇、呂盈蒼、陳政良、劉炳宏、連偉誠

執行單位:國立交通大學電信工程學系研究所

中華民國九十三年 08 月 01 日

行政院國家科學委員會專題研究計畫成果報告

微機電技術整合金氧半場效電晶體射頻積體電路

CMOS RFIC Transceiver integrate with MEMS technology

計畫編號: NSC 91-2213-E-9-129

執行日期: 民國 91 年 8/1 至 民國 93 年 7/31

主持人:周復芳 國立交通大學電信研究所副教授

研究生:陳一宇、呂盈蒼、陳政良、劉炳宏、連偉誠

一、中文摘要

關鍵字:RFIC,MEMS,TR Switch,Transformer, LNA,PA,VCO,Mixer

近年來由於短距離無線通訊的蓬勃發展,使 得射頻前端電路的設計受到重視,其中CMOS RFIC因為其具有可和基頻電路整合和良率高等 優點,越來越多設頻前端電路用CMOS來實現, 但由於矽基板在高頻時具有高損耗的缺點,許多 電路的高頻特性並不好,一種解決辦法就是將 MEMS的技術應用於矽製程中(例如將元件下的 矽基板挖空),可提升電路的高頻特性,另一優 點就是MEMS技術可製作立體結構的微波元件如 開關、立體電感及天線。在過去兩年,本實驗室 在MEMS微波開關方面的研究已有相當的經驗和 成果,並在國際期刊上發表。[1] 本計劃為兩年型計劃,利用本實驗室目前關 於MEMS方面的研究,整合至CMOS RFIC包括低 雜訊放大器(LNA),壓控震盪器(VCO),功 率放大器(PA),混波器(Mixer),低通濾波 器(LPF)及頻率合成器(Synthesizer)中,利用 MEMS技術增加CMOS RFIC元件所無法整合的 部份,以達到SOC(System On Chip)的目標。 Abstract

Keyword:RFIC,MEMS,TR Switch,Transformer, LNA,PA,VCO,Mixer

Recently because of the exploded development of short range wireless telecommunication, RF

transceiver circuits design is highly emphasized. Based on the CMOS RFIC advantages of integration of base-band circuits and high yield, more transceiver front-end circuits are widely realized by CMOS fabrication. However, silicon substrate inherent disadvantage of high high frequency loss condition, many circuit performances are decreased while operating in high frequency. One method to solve this phenomenon is to apply MEMS technology to silicon fabrication. For examples: etching lossy the silicon substrate under devices to enhance high frequency circuit characteristics, and having merit of manufacturing three-dimensional structure of microwave devices such as Switch, 3-D inductor, and antenna. In the past two years, our laboratory has been researching on microwave MEMS Switch and obtains extreme experiences and achievements. The results have been published on the international journals, such as IEEE, IEE, IEICE, and other famous journals.[1]

This project is a two years NSC project. Includes applying MEMS technology to CMOS Low Noise amplifier(LNA), Voltage-Controlled Oscillator(VCO), Mixer and Power amplifier(PA) circuit designs, and integrate MEMS microwave Switch, Balun and Antenna to CMOS RFIC to achieve fully SOC(System-On-Chip).

二、計畫緣由與目的

有鑒於傳統電晶體用來當微波開關,有較高 的功率損耗以及非線性動態響應,對於高頻傳輸 系統而言已經無法滿足所需要求,因此我們利用 微機械結構製作出的微波開關來改善此一問題。

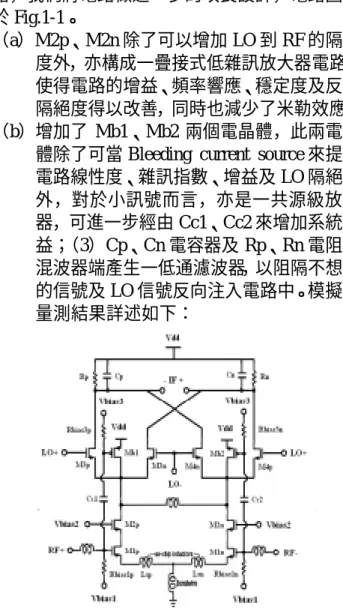

另外,在無線通訊系統的領域中,如何將所 有的電路置於IC之中是目前大家所努力的目標, 而天線的IC化在便成為了一個很重要的課題.以 往在高頻的領域中.微帶天線一直是大家所應用 以及發展的方向。 三、研究成果 .2.4GHz,0.25µm CMOS 雙平衡共電流低雜訊 放大器整合混波器 [2] 基於傳統式的雙平衡低雜訊放大器整合混波器電 路,我們將電路做進一步的改良設計,電路圖示 於 Fig.1-1。 (a)M2p、M2n 除了可以增加 LO 到 RF 的隔絕 度外,亦構成一疊接式低雜訊放大器電路, 使得電路的增益、頻率響應、穩定度及反向 隔絕度得以改善,同時也減少了米勒效應; (b)增加了 Mb1、Mb2 兩個電晶體,此兩電晶

體除了可當 Bleeding current source 來提昇 電路線性度、雜訊指數、增益及 LO 隔絕度 外,對於小訊號而言,亦是一共源級放大 器,可進一步經由 Cc1、Cc2 來增加系統增 益;(3)Cp、Cn 電容器及 Rp、Rn 電阻在 混波器端產生一低通濾波器,以阻隔不想要 的信號及 LO 信號反向注入電路中。模擬及 量測結果詳述如下:

Fig. 1-1 The Modified Merged LNA and Mixer Circuit schematic

Fig. 1-2 Die Photograph of Merged LNA and Mixer

Specification Simulation (TT)

Measurement RF Port Input RL (dB) 10.9 13.7 LO Port Input RL (dB) 25.9 15.3 IF Port Output RL (dB) 16.2 N/A Power Gain (dB) 10.5 9.0 Voltage Gain (dB) 20.3 18.2 NF (dB) 6.0 N/A P1dB (dBm) -26.0 -19.0 IIP3 (dBm) -4.6 -4.8 LO-to-RF Isolation (dB) -81.8 -48.4 Power Consumption (mW) &

Current Drawing @ Supply voltage: 2.5V Buffer: 6.4 (2.6mA) Core: 14.4 (5.8mA) Total: 20.8 (8.4mA) Buffer: 6.3 (2.5mA) Core: 18.8 (7.5mA) Total: 25.1 (10mA) Table.1 2.4GHz 雙平衡共電流低雜訊放大器整合 混波器模擬量測結果摘要

Fig. 1-3 Measured RF Port Input Matching

Fig. 1-4 Measured LO Port Input Matching

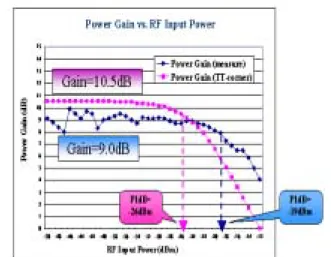

Fig. 1-5 Power Gain vs. LO Input Power Comparison

Fig. 1-4-6 Power Gain vs. RF Input Power Comparison

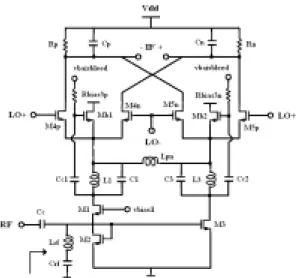

Fig. 1-4-7 Two-tone Test Measurement Result .2.4GHz,0.25µm CMOS 改良型射頻微混波器 [2] 在此改良型為混波器中我們保留了傳統式的雙對 稱 AB 型 RF 輸入級架構,因為此架構不僅可以 將單端輸入轉為差動輸出,更有較好的阻抗匹配 合較大的動態範圍。在輸入端的阻抗匹配部份, 我們使用串聯的 LC 諧振腔(Lrf、Crf)以消除輸 入端的虛部阻抗;除此之外,在混波器電路部份 加入了並聯的 LC 諧振腔(L1,C1 & L3,C3), 並將諧振頻率設計在 2.45GHz,能使 RF 端產生 的差動電流獲得較大的差動電壓增益;之後此高 電 壓 分 別 藉 由 旁 路 電 容 器 ( Cc1 、 Cc2) 注 入 Bleeding-current NMOS 電晶體中(Mb1、Mb2), 此兩電晶體能在高頻率時形成電流放大器,在不 需要太大的電流消耗的條件下依然能有很大的增 益,經過理論的推導,我們可以發現此時微混波 器的放大倍率為轉導的平方,因此能比傳統電路 有更大的增益,此特點為此電路最主要的特性。

Fig. 2-1 New RF CMOS MICROMIXER schematic

Fig. 2-2 Die Photograph of New CMOS MICROMIXER Specification Simulation (TT) Simulation (FF) Measurement RF Input RL (dB) 17.5 16.1 15.4 LO Input RL (dB) 14.1 14.6 16.1 IF Output RL (dB) 11.6 12.9 NA Power Gain (dB) 1.6 5.4 6.8 Voltage Gain (dB) 11.0 14.1 14.6 NF (dB) 11.8 10.6 NA P1dB (dBm) -10 -13.4 -15 IIP3 (dBm) +1.1 -3.7 -1.0 LO-to-RF Isolation (dB) > 50 > 50 32 Power Consumption (mW) Buffer: 4.7 (1.9mA) Core: 3.7 (1.5mA) Total: 8.4 (3.4mA) Buffer: 5.0 (2.0mA) Core: 4.4 (1.8mA) Total: 9.4 (3.8mA) Buffer: 5.0 (2.0mA) Core: 5.5 (2.2mA) Total: 10.5 (4.2mA) Table.2 2.4GHz 改良型射頻微混波器模擬量測結 果摘要

Fig. 2-3 Measured RF Port Input Matching

Fig. 2-4 Measured LO Port Input Matching

Fig. 2-5 Power Gain vs. LO Input Power Comparison

Fig. 2-6 Two-tone Test Measurement Result

Fig. 2-7 Power Gain vs. RF Input Power Comparison .2.4GHz,0.25µm CMOS 整合正交信號輸出之 頻率合成器 [3] 頻率合成器是通訊系統 IC 裡面相當重要的一環 節,因為我們使用的頻段較高,所以採用 PLL 架 構來實現我們的頻率合成器,電路包含 Phase detector、Charge pump、Loop filter、VCO、Divider 等部份。以下則為此電路的電路圖、晶片圖及量 測和模擬結果:

Fig. 3-1 Fully Programmable Frequency Divider schematic

Fig. 3-2 Whole chip die photo

Fig. 3-3 Measured locking spectrum at 2400MHz

Fig. 3-4 Settling time transient measurement between 2448 and 2480MHz

Simulation Measurement Power supply 2.5V 2.5V Tuning range of VCO2.373 ~ 2.513

GHz 2.392 ~ 2.514 GHz Phase noise -108dBc/Hz @1MHz -102dBc/Hz @1MHz Spurious tones N/A -40dB

Locking time About 80µs About 140µs Table.3 2.4GHz 整合正交信號輸出之頻率合成器

模擬量測結果摘要 -40dB

.MEMS Switch 本計畫中使用之MEMS開關有傳統的橋式 (bridge type)電容性(capacitive)開關,如圖4-1,藉 由靜電力之驅使,使懸浮薄膜(suspended membrane)結構下壓而等效成一個高電容值之電 容器,因而形成對地之低阻抗通路,換言之,對 地短路,因而阻絕訊號之通過。 圖4-1 橋式電容性開關 然而,由實驗發現此類型之MEMS開關有較 高之驅動電壓(∼40伏特以上),因而在與CMOS 電路上之整合有所困難。因此,本計畫中設計一 新式推挽式MEMS開關[1],如圖4-2,此開關以扭 力致動器(torsion actuator)驅動,也因此有較低 之驅動電壓,約在3~6伏特左右。整個開關由一扭 力臂所支撐,藉由兩側之驅動電極來決定該側之 開關狀態為開或關。 圖4-2 推挽式MEMS開關 以上所述之兩種MEMS開關之設計可用以作 為訊號饋入線路之切換以形成相移器電路,或是 純粹作為電壓可調式電容器(varactor)之用。因 此,十分適合與RF CMOS電路整合, 達成高品 質因素、低耗能與低雜訊…等等優點。 四、結論與展望 本計劃利用本實驗室目前關於 MEMS 方面 的研究[1], (微波開關,Balun 和天線),整合至 CMOS RFIC 包括低雜訊放大器(LNA),壓控震盪 器(VCO),功率放大器(PA),混波器(Mixer),低 通濾波器(LPF)及 Synthesizer 中,利用 MEMS 技 術增加原本 CMOS RFIC 所無法整合的部分,達 到更接近 SOC(System-On-Chip)的目標。 五、參考文獻 [1] 盧仁宸,”新型推挽式射頻微機電開關之設計 與應用”,國立交通大學電信工程所碩士論 文,Jun. 2003。 [2] 呂盈蒼,「使用0.25µm CMOS技術製作的一 個完全積體化共模三頻帶低雜訊放大器及兩 個改良型混波器電路設計」,國立交通大學 電信工程所碩士論文,Jun. 2004。 [3] 陳政良,「用CMOS 0.25µm來完成一個適用 藍芽規格具I/Q四相位輸出除整數架構之頻率 合成器及探討諧波混頻器在無線通訊方的應 用」,國立交通大學電信工程所碩士論文,Jun. 2004。

[4] Christina F. Jou, Pang-Ruei Huang and Kuo-Hua Cheng, "Design of a 0.25-µm CMOS 5.25GHz WLAN Transceiver Front-End”, Proceeding of the 14th VLSI Design/CAD Symposium 2003, pp. 485-488, Hualien, Taiwan, Aug. 12-15, 2003.

[5] Christina F. Jou, Kuo-Hua Cheng, Pang-Ruei Huang and Mei-Chien Chen, "Design of a Fully Integrated High Linearity Dual-Band CMOS LNA”, Proceeding of the 14th VLSI Design/CAD Symposium 2003, pp. 493-496, Hualien, Taiwan, Aug. 12-15, 2003.

[6] Cristina F. Jou, Pang-Ruei Huang and Kuo-Hua Cheng, "Design of a 0.25-µm CMOS 5.25GHz WLAN Transceiver Front-End”, The 10th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2003), pp. 1090-1093, Sharjah, United Arab Emirates, Dec. 14-17, 2003.

懸浮薄膜

傳輸線

驅動電極

扭力臂

驅動電極(右)

驅動電極(左)

傳輸線

[7] Christina F. Jou, Kuo-Hua Cheng, Pang-Ruei Huang and Mei-Chien Chen, "Design of a Fully Integrated High Linearity Dual-Band CMOS LNA”, The 10th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2003), pp. 978-981, Sharjah, United Arab Emirates, Dec. 14-17, 2003.

[8] Christina F. Jou, Kuo-Hua Cheng, Hsien-Cheng Hsieh, "An Ultra Low Power 2.4GHz CMOS VCO” , The 10th IEEE International Conference on Electronics,Circuits and Systems (ICECS 2003) ,pp. 1098-1100, Sharjah, United Arab Emirates, Dec. 14-17, 2003.

[9] Christina F. Jou, Kuo-Hua Cheng, Pang-Ruei Huang and Mei-Chien Chen, "Design of a Fully Integrated High Integrated High Linearity Dual-Band CMOS LNA”, IEEE Transaction on Microwave Theory and Techniques Mini-Special Issue on: Papers of Asia-Pacific Microwave Conference (APMC 2003) ,pp. 385-388, Seoul, Korea, Nov. 4-7, 2003.

[10] Christina F. Jou, Kuo-Hua Cheng, Eing-Tsang Lu and Yang Wang, ”A Fully Integrated High Linearity Concurrent Triple-Band CMOS LNA”, 2003 SOC Design Conference, pp. 629-634, Seoul, Korea, Nov. 5-6, 2003.

[11] Christina F. Jou, Kuo-Hua Cheng, Chia-Min Lin and Jia-Liang Chen, “Dual Band CMOS Power Amplifier for WLAN Applications”, The 46th IEEE International Midwest symposium on Circuits and systems (MWSCAS 2003), Cairo, Egypt, Dec. 27-30, 2003.

[12] Christina F. Jou, Kuo-Hua Cheng, Eing-Tsang Lu and Yang Wang, “Design of A fully integrated concurrent triple-band CMOS low noise amplifier,” The 46th IEEE International Midwest symposium on Circuits and systems (MWSCAS 2003) , Cairo, Egypt, Dec. 27-30, 2003.

[13] Kuo-Hua Cheng, Cheng-Hong Chen, Christina F. Jou, “A 0.25µm 900-MHz 1.5V Dual Band VCO with Quadrature Output”, The 46th IEEE International Midwest symposium on Circuits and systems (MWSCAS 2003), Cairo, Egypt, Dec. 27-30, 2003.

[14] Kuo-Hua Cheng, Christina F. Jou, ”2.4GHz CMOS VCO design with Verilog-A”, The 15th International Conference on Microelectronics (ICM 2003), Cairo, Egypt, Dec. 9-11, 2003. [15] Christina F. Jou, Kuo-Hua Cheng, Eing-Tsang

Lu and Yang Wang, “A Fully Integrated High

Linearity Concurrent Triple-Band CMOS LNA”, Progress In Electromagneties Research Symposium (PIERS 2004), Nanjing, China, Aug. 28-31, 2004.

![Fig. 2-7 Power Gain vs. RF Input Power Comparison .2.4GHz,0.25µm CMOS 整合正交信號輸出之 頻率合成器 [3] 頻率合成器是通訊系統 IC 裡面相當重要的一環 節,因為我們使用的頻段較高,所以採用 PLL 架 構來實現我們的頻率合成器,電路包含 Phase detector、Charge pump、Loop filter、VCO、Divider 等部份。以下則為此電路的電路圖、晶片圖及量 測和模擬結果:](https://thumb-ap.123doks.com/thumbv2/9libinfo/8448552.182340/7.892.480.806.136.605/Fig頻率合重要節因為我們使用的頻段較高所以採用架構來實現我們.webp)