報告題名:

二氧化鉿閘極高介電質之依時性

介電層崩潰機制研究

TDDB Reliability and Breakdown Mechanism of

HfO

2High-K Gate Dielectric

作者:蕭博修 系級:電子四甲 學號:D9530478 開課老師:林成利 老師 課程名稱:專題研究(二) 開課系所:電子工程學系 開課學年:九十八學年度 第一學期

摘要

本專題主要是研究以二氧化鉿(HfO2)為電容結構的介電層,經過

不同溫度的快速熱退火處理,探討閘極漏電流(I-V)、電容-電壓(C-V) 曲 線 分 析 、 依 時 性 介 電 層 崩 潰 測 試 (time dependent dielectric

breakdown,TDDB)及可靠度分析。 對於介電層崩潰機制的研究,專題中提出了介電層崩潰模型和載 子傳導路徑模型。HfO2 介電層相較於二氧化矽(SiO2)有較多的陷阱 (traps)和缺陷(defects)。另外,HfO2與矽基板之間的介面層(interfacial layer,IL)有較小的介電常數,當施加電壓時,介面層(IL)所承受的電 場較大,導致此區域介電層會先發生暫時性崩潰(soft breakdown, SBD)。持續施加電壓,此時在 HfO2 介電層中的陷阱(traps)、缺陷 (defects)會越來越多,最後形成漏電流傳導路徑,導致漸進式崩潰 (progressive breakdown,PBD)。在外加電壓於 HfO2介電層中,推測

可能因在介電層和閘極金屬氮化鉭(TaN)與介電層與矽基板兩界面 間,所產生的介面層(interfacial layer)之內電場分佈不相同,導致在介 電層中的陷阱、缺陷的產生速率不同,因此導致漏斗狀分佈的漏電流 通道,最後整個結構發生永久性崩潰(hard breakdown,HBD)。

Abstract

This work is to study the characteristics and effects of thermal annealing of hafnium dioxide (HfO2) as a gate dielectric layer. Which through the varied

temperature rapid thermal annealing (RTA) investigates the electrical characteristics and reliability behavior.

We propose a breakdown model for the mechanism of dielectric breakdown and the conduction path of breakdown for HfO2 dielectric. The hafnium dioxide (HfO2)

dielectric layer has more traps and defects than silicon dioxide (SiO2) layer. There is

an interfacial layer (IL) with smaller dielectric constant between the hafnium dioxide (HfO2) layer and the silicon substrate. When the electric field applied, the interfacial

layer (IL) will sustain the larger electric field resulting in the soft breakdown (SBD) behavior. As long as a continuous electric field is applied, traps and defects in the dielectric layer will increase. The formation of the leakage current’s conduction path leads to progressive breakdown (PBD). And then, the value of the electric field between the dielectric layer and the metal gate and that between the dielectric layer and the silicon substrate is different. In the dielectric layer, traps and defects will become the hour-shaped distribution pattern of channels. Finally, the structure leaded to the phenomenon of hard Breakdown (HBD).

Keywords:High-K dielectric, hafnium dioxide (HfO2), reliability, breakdown

mechanism, soft breakdown (SBD), progressive breakdown (PBD), hard breakdown (HBD).

目錄

中文摘要 ... i

英文摘要 ... ii

目錄 ... iii

第一章 緒論

1-1 前言 ... 1

1-2 研究動機 ... 3

第二章 元件製作

2-1 MIS 電容結構 ... 5

2-2 材料分析 ... 8

2-2-1 穿透式電子顯微鏡(Transmission Electron

Microscopy,TEM) ... 8

第三章 電性量測與分析

3-1 量測機台簡介 ... 10

3-2 電流-電壓曲線(I-V) ... 12

3-3 電容-電壓曲線(C-V) ... 15

3-4 依時性介電層崩潰(Time Dependent Dielectric

3-5-1 原理 ... 22

3-5-2 實驗結果分佈 ... 25

第四章 崩潰機制

4-1 崩潰行為介紹 ... 26

4-2 二氧化鉿(HfO

2)介電層崩潰機制 ... 30

4-3 載子傳輸路徑 ... 33

第五章 結論

5-1 電性分析 ... 36

5-2 崩潰機制 ... 37

參考文獻 ... 38

個人簡歷 ... 41

第一章 緒論

1-1 前言

在 I.C.製程技術的逐日進步下,根據摩爾定律(Moore’s Law)預 測,微處理器電晶體數目在價格不變的條件下,幾乎每 18 個月就增 加一倍,如圖 1-1.1。電路的集積度持續增加,元件尺寸不斷的縮小, 傳統的閘極氧化層使用二氧化矽(SiO2),當閘極厚度處於 1.2nm 以下 時,會面臨漏電流過大的問題[1-2]。 我們可藉由高介電係數材料(High-K dielectric)的取代,提升閘極 介電層的介電係數,達到在相同的電容值下,有較厚的實際厚度(Equivalent Oxide thickness,EOT),來降低直接穿隧(direct tunneling) 所導致的漏電流現象[3-4]。

選用高介電係數材料,需要考慮到幾個因素,一是與矽基板接觸 時能有良好的熱穩定性,另外要有穩定的介面,使高介電材料不易與 矽基板產生品質不佳的界面層。目前多以矽為基板材料,在使用高介 電係數材料時,能帶與矽相比較,如果有較小的能隙或能帶偏移量, 會導致因直接穿隧而引發漏電流產生。一般做為閘極高介電質所研究 的材料,其特性多為 20<K<60、Eg>5eV,如圖 1-1.2 和圖 1-1.3。相 符合的材料有:ZrO2 、HfO2 、HfSiO4、Al2O3 、Y2O3和 La2O3等。

[3, 6]

圖 1-1.3 不同高介電係數材料之能帶偏移量[6]

1-2 研究動機

傳統閘極氧化層是以 SiO2為介電層,但元件大小已縮小到奈米

尺寸,若以 SiO2為介電層,會有極大的漏電流情形。目前是以 High-K

材料來取代 SiO2,在有相同的電容值條件下,以較厚的實際厚度,來

減少漏電流的直接穿隧(direct tunneling)現象[3-4]。在 High-K 介電層 中,內部的缺陷(defects)、陷阱(traps)會比 SiO2 多,當施加電場時,

這些缺陷(defects)、陷阱(traps)與閘極漏電流有極大的關聯,進而導致 元件崩潰損毀。

構中,閘極介電層以 High-K 材料二氧化鉿(HfO2)取代傳統的二氧化

矽(SiO2)氧化層。在介電層沉積於矽基板之後,經過不同溫度的快速

熱退火處理(Rapid thermal annealing,RTA),施加測試電壓,探討不 同溫度對 High-K 介電層的影響,以及物理崩潰機制。

第二章 元件製作

2-1 MIS 電容結構

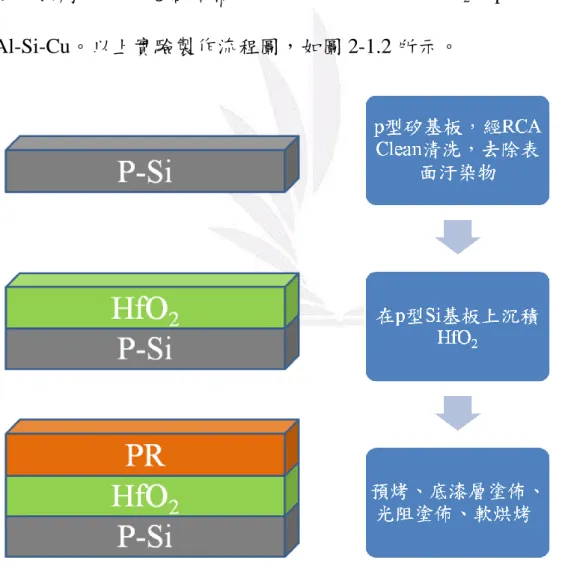

本實驗是以 p 型的矽晶圓為基板,經過標準溼式清洗(RCA Clean) 步驟,去除晶圓上的微粒子、有機物及金屬離子等汙染物後,再放入 金 屬 有 機 化 學 氣 相 沉 積 系 統 (Metal Organic Chemical Vapor

Deposition,MOCVD),沉積高介電係數材料二氧化鉿(HfO2),沉積厚

度為 16nm。接著將矽晶圓置入充滿氮氣(N2)的環境中,分別以溫度

400℃、500℃及 600℃,製程時間 30 秒進行快速熱退火處理(Rapid Thermal Annealing,RTA),修補 HfO2介電層因製程等因素所產生的

懸浮鍵、缺陷(defects)和陷阱(traps),使 HfO2介電層的結構更趨於完

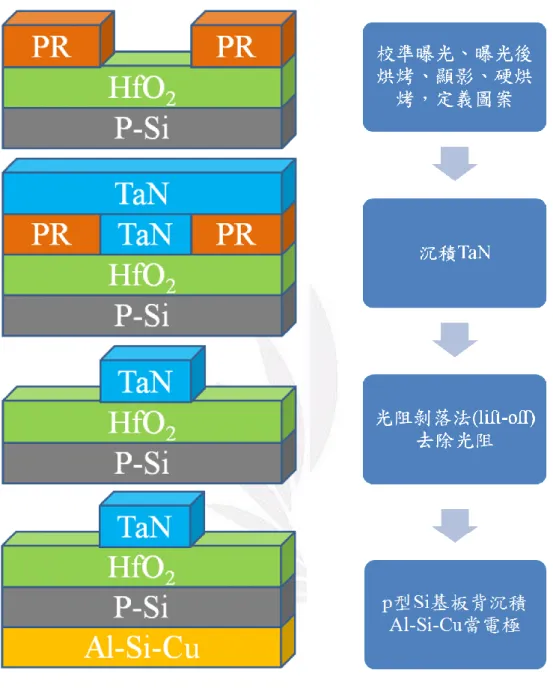

阻塗佈、軟烘烤、校準曝光、曝光後烘烤、顯影、硬烘烤,以定義出 光阻的圖案,接著使用反應式真空濺鍍系統沉積 50nm 的氮化鉭(TaN) 薄膜做為金屬電極,在以光阻剝落法(left-off)去除光阻,留下所需的

TaN 部分形成閘極電極,其面積為 5.4×4 μm2。

最後為了量測方便,在矽基板背面,以熱阻式蒸鍍機系統(Thermal

Evaporation Coater)沉積 200nm 的 Al-Si-Cu 當金屬背電極,使其形成 歐姆接觸,完成電容結構 50nm TaN / 16nm HfO2 / p-Si / 200nm

Al-Si-Cu。以上實驗製作流程圖,如圖 2-1.2 所示。

2-2 材料分析

2-2-1 穿透式電子顯微鏡(TEM)

穿透式電子顯微鏡(Transmission Electron Microscopy,TEM),使 用高能電子束,穿透極薄的樣品,電子在經過樣品過程中,會發生彈 性散射、非彈性散射。散射後的電子,再經過光圈、透鏡組合,可產 生明暗的繞射圖,再利用成像繞射對比,可製成明視野和暗視野。本 實驗中是利用明視野來觀察樣品的電子散射影像。[20]

電容結構為 50nm TaN / 16nm HfO2 / p-Si / 200nm Al-Si-Cu,利用

穿透式電子顯微鏡(TEM)觀察 HfO2 介電層和介面層的厚度。如圖

2-2-1.3 所示,可觀察到介電層厚度範圍 15.0nm~15.6nm,而介面層 的厚度範圍在 1.6nm~1.5nm 之間,所沉積結構不會因為熱退火處理

(RTA)的溫度不同,而使厚度相差甚遠。

圖 2-2-1.3 不同 PDA 溫度處理之 TEM 微結構圖(a) No PDA (b) PDA

第三章 電性量測與分析

3-1 量測機台簡介

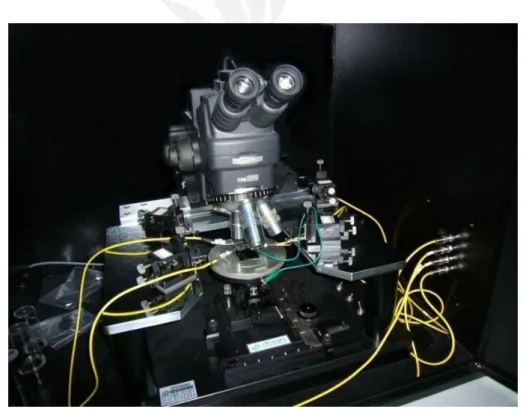

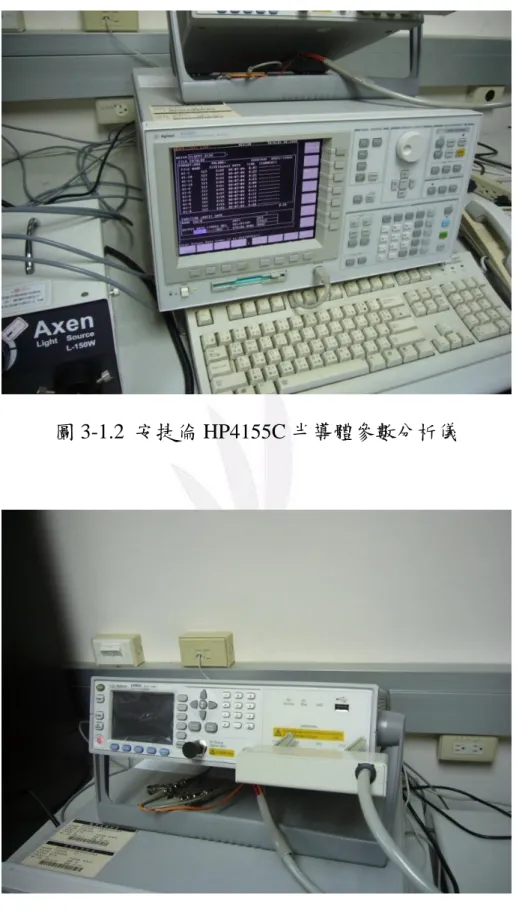

為了了解介電層沉積後,在不同溫度的快速熱退火處理(RTA), 對 HfO2介電層所造成的影響。我們將完成電容製程的晶圓,放至載 座與顯微鏡機台下,利用高倍率顯微鏡,查看電容元件的位置,再利 用兩支探針,一端當量測電極、另一端當接地,如圖 3-1.1。所使用 的量測儀器為安捷倫 HP4155C 半導體參數分析儀,如圖 3-1.2,用以 量 測 電 壓 - 電 流 (I-V) 特 性 、 依 時 性 介 電 層 崩 潰 (Time DependentDielectric Breakdown,TDDB)和安捷倫 E4980A 電壓電容分析儀,如 圖 3-1.3,量測電壓-電容(C-V)特性。

圖 3-1.2 安捷倫 HP4155C 半導體參數分析儀

3-2 電流-電壓曲線(I-V)

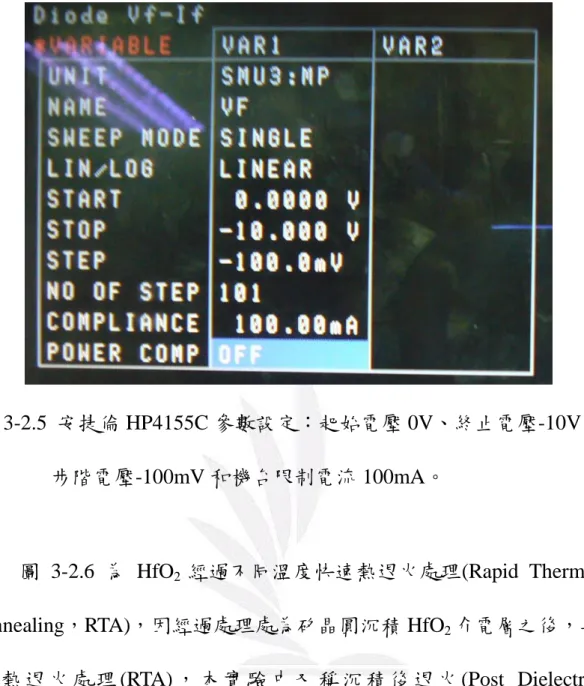

量測電流-電壓曲線(I-V)時,我們利用斜坡電壓(Ramp Voltage Stress,RVS)模式,對元件施加偏壓,設定參數步階電壓 100mV、最 大限制電流 100mA,進行閘極漏電流的分析,如圖 3-2.4 和圖 3-2.5。 圖 3-2.4 安捷倫 4155C 參數設定:SMU3 當作量測探針,SUM4 當接 地。(SMU3、SMU4 為探針編號)。圖 3-2.5 安捷倫 HP4155C 參數設定:起始電壓 0V、終止電壓-10V、 步階電壓-100mV 和機台限制電流 100mA。

圖 3-2.6 為 HfO2 經過不同溫度快速熱退火處理(Rapid Thermal

Annealing,RTA),因經過處理處為矽晶圓沉積 HfO2介電層之後,再

去 熱 退 火 處 理 (RTA) , 本 實 驗 中 又 稱 沉 積 後 退 火 (Post Dielectric

Annealing,PDA)。從圖中可看出,崩潰電壓(Voltage Ramp Dielectric Breakdown,VRDB)會隨著 PDA 的溫度提高而升高,推測原因可能是

因為在 PDA 的過程中,氮原子修補了存在 HfO2介電層內了陷阱(traps)

圖 3-2.6 累積模式下(acc. mode)的閘極偏壓經過 400C、500C 及

3-3 電容-電壓曲線(C-V)

為了研究介電層沉積後,在不同溫度的 PDA,對 HfO2介電的微 結構以及介電層內部的缺陷電荷變化,我們使用安捷倫 E4980A 量測 元件的電壓對電容值(C-V),參數設定頻率 100kHz,電壓掃描限制由 正電壓掃到負電壓,再從負電壓掃到正電壓,觀察曲線中的遲滯現象 (hysteresis)和缺陷電荷密度,如圖 3-3.7 所示。 圖 3-3.7 安捷倫 E4980A 設定頻率 100KHz、電壓掃過範圍±4V。 理想電壓與電容之間的關係,如圖 3-3.8 所示。高頻所對應的頻 率是 1MHz,低頻所對應的頻率為 5~100Hz 的範圍。偏壓在聚集區 的電容值為 Cox,會隨著表面空乏電容值的減小而減小。偏壓在反轉 區時,需有充分的時間來形成反轉層,在高頻交流訊號下,電子形成圖 3-3.8 NMOS 電容在低頻與高頻時,電容對電壓關係圖[21]。 本實驗是以高頻量測測電容,如圖 3-3.9 所示,隨著 PDA 的溫度 增加,平帶電壓偏移量有減少的現象。在 PDA 溫度為 400℃和 500℃ 時,平帶電壓往正偏壓移動,推測在經過 PDA 之後,High-K 介電層 內的正陷阱電荷會隨著 PDA 溫度上升而下降[7]。當溫度為 500℃時, 可觀察到曲線較為陡峭,其為介電層因 PDA 之後得到改善,使得缺 陷電荷密度減少。當 PDA 溫度為 600℃時,曲線明顯向負偏壓移動, 介電層中的正陷阱電荷有增加的現象,且因微結構的發生改變,造成 電容值有下降的現象。

3-4 依時性介電層崩潰(TDDB)

使用安捷倫 HP4155C 量測儀器,操作在此模式下-sampling

mode,給予固定的測試電壓(Vg= -4.8V),使元件操作在累積模式

(accumulation mode),偵測電流隨時間變化的情形(Constant Voltage Stress,CVS),畫出漏電流對時間(I-t)關係圖,設定如圖 3-4.10~圖 3-4.12 所示,進一步可看出電容結構中的介電層品質好壞,也可預測介電層 受電壓測試之後的生命期,亦稱依時性介電層崩潰(Time Dependent Dielectric Breakdown,TDDB)。 圖 3-4.10 安捷倫 HP4155C 參數設定:SMU3 當作量測探針,SUM4 當接地。

圖 3-4.11 安捷倫 HP4155C 參數設定:間隔時間 1.0s(秒) 、取樣數量 1000 點 圖 3-4.12 安捷倫 HP4155C 參數設定:固定電壓-4.8V、機台限流 100mA。 經過 PDA 處理後,MIS 電容在施加測試電壓初期,可以由圖 3-4.13~ 圖 3-4.16 可看出,漏電流有雜訊擾動的現象,其原因可能是位於介電 層內,陷阱(traps)與缺陷(defects)造成有捕捉、散逸的行為。但隨著 PDA 的溫度提升,初期漏電流雜訊擾動的現象有明顯改善,且崩潰 時間(Time to Breakdown,TBD)也有增加的現象。因在經過 PDA 之後,

處於 HfO2介電層內的陷阱(traps)與缺陷(defects)有得到修補,使得介

圖 3-4.13 No PDA 累積模式,固定偏壓 (Vg= -4.8V)之 TDDB 曲線圖。

圖 3-4.15 PDA 500℃累積模式下固定偏壓之 TDDB 特性圖。

3-5 韋伯分佈(Weibull distribution)

3-5-1 原理

韋伯分佈(Weibull distribution),是瑞典物理學家 Waloddi Weibull 提出一種描述數據分佈的函數。因半導體元件損壞分佈,為非常態分 佈曲線,在此以韋伯分佈來做統計分析,元件生命期檢測方面的問 題,韋伯分佈幾乎成了主要的工具。

Weibull 累積分佈函數(Weibull Cumulative Distribution Function,

CDF)如下:表示在某時間內發生故障之機率

其中 F(t)為累積故障率,而 c (Scale parameter,尺度參數)、m (Shape

parameter,形狀參數)、t0 (Location parameter,位置參數)稱韋伯三參

數。[10-11] 韋伯參數之物理意義 1. c (尺度參數):影響數據分布的範圍。 當 m 固定時,c 越大,數據分佈的峰值會下降,但涵蓋範圍 變大。表是說該元件故障所需的時間或應力分佈範圍變大。c 又稱 特徵參數,指當達到該壽命值時,有 63.2%的元件會發生故障。

2. m (形狀參數):決定實驗數據分佈型態。 m<1 初期故障期 元件使用初期便發生損毀,原因可能為製造過 程中造成的先天性缺陷產生 m=1 偶發故障期 元件故障率不受時間影響,而為一定值。可用 來評估產品的使用壽命。 m>1 磨耗故障期 元件受環境的影響,以及操作導致零件老化, 使產品的損壞率會隨著時間增加。 3. t0(位置參數):影響數據分佈的起始位置。 又稱為最小壽命。在 m 與 c 相同時,位置參數的改變,會對 曲線造成水平移動的影響。在本實驗中,元件施加偏壓後,元件 才會開始產生損壞的情形,所以是使用 t0=0 或 t0>0 這兩部分。 t0<0 元件未開始使用,即發生損壞的情形 t0=0 元件開始,才會開始發生損壞 t0>0 元件使用一段時間,或達到某特定條件才會有損壞發生

韋伯實驗參數取得

我們將累積分佈函數(CDF)移項,兩邊同時取自然對數可得:

由上式結果,可看出與直線方程式相類似

3-5-2 實驗結果分佈

從圖 3-5.-2.17 可看出,介電層 HfO2經過較高溫度的 PDA 處理, 韋伯分佈明顯向右偏移,元件的崩潰時間(TBD)有增加的現象。但隨著 PDA 的溫度升高,韋伯斜率有變小的現象,元件的品質有比較不均 勻的狀況。不過整體而言,經過高溫 PDA 處理過後的元件可靠度, 比沒有經過 PDA 處理的還要好。 圖 3-5-2.17 累積模式下,固定偏壓(VG = -4.8V),在不同 PDA 溫度下 之韋伯分佈圖。第四章 崩潰機制

4-1 崩潰行為介紹

介電層的崩潰行為,大致上可分成暫時性崩潰(soft breakdown, SBD)、永久性崩潰(hard breakdown,HBD)、漸進式崩潰(progressive breakdown,PBD)。 1. 暫時性崩潰(SBD) 在超薄的氧化層中外加電場,會因氧化層內的陷阱產生速率 不高,使得熱破壞的情形無法產生,所量測到的陡峭漏電流是受 到施加電場的影響,而氧化層還沒有完全崩潰,如圖 4-1.1 和圖 4-1.4。此現象會隨著氧化層的厚度減少、外加電場強度增加及閘 極氧化層面積縮小而增加,在元件越做越小的情況下,暫時性崩 潰(SBD)是氧化層受損的主要機制[8, 17]。 2. 永久性崩潰(HBD) 在施加電場的狀況下,氧化層會因外加電場影響,而有缺陷 產生。當缺陷多到足夠在氧化層內部形成載子的傳輸路徑,電場 持續增加的狀況,會在崩潰的位置累積夠大的熱崩潰,接著造成 崩潰區域往橫向電場方向傳播,引發更多區域崩潰,最後導致整 個氧化層崩潰,如圖 4-1.2 和圖 4-1.5[8, 18-19]。3. 漸進式崩潰(PBD) 以高介電係數材料(High-K)為氧化層時,會與矽基板表面形 成介面層(interfacial layer,IL)。當外加電場時,介面層(IL)內的 缺陷會變多,進一步形成漏電流傳導路徑,且有損傷的情形產生。 此時載子會沿著這些缺陷路徑進行傳導,穿過 High-K 層使之發 生崩潰,此過程稱為漸進式崩潰,如圖 4-1.3 和圖 4-1.6[9, 18-19]。 圖 4-1.1 暫時性崩潰(SBD) 圖 4-1.2 永久性崩潰(HBD) 圖 4-1.3 漸進式崩潰(PBD)

圖 4-1.4 n+

poly-Si/3.9 nm SiO2/p-Si,經斜坡電壓測試(Ramp Voltage

Stress,RVS),可看出 Soft Breakdown 漏電流密度情形。[17]

圖 4-1.5 PMOS poly-Si/2 nm oxide,基極注入、固定電壓量測(4.0V)。 由圖中可看出 Progressive Breakdown 和 Hard Breakdown 現 象,箭頭所指的部分為 Hard Breakdown。[18-19]

圖 4-1.6 PMOS poly-Si/2nm oxid,基極注入、固定電壓量測(-4.2V)、 限制電流 5mA。由圖中可看出 Progressive Breakdown 現象。 [18-19]

4-2 二氧化鉿(HfO2)介電層崩潰機制

根據文獻,在 TiN/TaN/HfO2/SiOx/Si-substrate 結構中,經由基極

注入方式施予偏壓。電子由基板注入,當漏電流過大時(~2μA),HfO2 介電層會有陷阱、缺陷產生。經由電子撞擊 Tan 金屬電極,在較脆弱 的地方會導致 TaN 游離形成 Ta/Ta+,再受到電場作用以及加速的影 響,游離的 Ta/Ta+隨著電場方向遷移,將 Ta/Ta+沿著缺陷、陷阱通道 帶往矽基板,使得在介電層之間形成金屬絲狀物(metal filament),造 成 PBD 和 HBD,如圖 4-2.7[9]。 圖 4-2.7 漏斗狀(Hour-glass)崩潰模型[9]

在本實驗中,當閘極介電層二氧化矽(SiO2)以 High-K 材料 HfO2

取代時,就介電層 HfO2而言,比傳統使用的 SiO2有較多的陷阱(traps)

和缺陷(defects)[7]。當外加電場時,電子會被陷阱和缺陷捕捉、散逸, 使得剛開始漏電流為雜訊擾動狀態,如圖 3-3.13~圖 3-3.16,隨著測試 時間的增加,這些電子會再產生許多陷阱、缺陷,形成漏電流的傳導 路徑,載子可經由這些漏電流路徑的傳導。介電層與矽晶圓的介面處 (interfacial layer,IL),因材料、晶格常數不相同,而有比較多的陷阱 (traps)和缺陷(defects),再加上介電常數較小,當外加電場時,介面層 (IL)能承受的電場強度較小,此區域易較為脆弱易形成弱區。閘極注 入(gate injection)的結果,電子碰撞介面層(IL)時,會將 H+離子撞擊 出,進而引發介面層(IL)發生 SBD。再隨著傳導路徑在介電層 HfO2 中的弱點產生,最後導致 PBD,使閘極漏電流上升。在 HfO2與 TaN 的介面層和 HfO2與矽基板的介面層中,電場分佈可能不相同,在較 大電場區域,陷阱和缺陷產生的速率會比較快,受到電場加速的影 響,使得陷阱、缺陷呈現漏斗狀分佈(Hour-glass)。最後缺陷陷阱會在 介電層內形成通道,使得閘及漏電流劇升導致 HBD。以上介電層崩 潰機制,如圖 4-2.8 所示。

4-3 載子傳導路徑

從圖 3-4.13~圖 3-4.16 可看出,隨著 PDA 溫度的增加,漏電流有 減少現象,在施加電壓初期的雜訊電流擾動有明顯改善,崩潰時間 (TBD)有隨著溫度增加而增加的趨勢。推測現象原因,在經過 400℃的 PDA 處理之後,HfO2有發生再結晶的現象,電子可經由結晶邊界傳 導路徑傳輸,導致漏電流產生,且介電層內部會有明顯的陷阱輔助穿 隧(Trap-assisted tunneling,TAT)現象發生[12-13],如圖 4-3.9,使得可 明顯觀察到初期的雜訊擾動電流情形。在 PDA 500℃時,溫度的提升 使得 HfO2介電層的結晶程度增加,結晶之間的緻密度上升,此行為 可減小因晶界所產生的漏電流路徑,使漏電流減小。經過高溫處理 後,介電層內部的陷阱(traps)、缺陷(defects)可得到較佳的修補效果, 使得陷阱輔助穿隧(TAT)所導致的漏電流減小,初期的雜訊擾動電 流,有得到改善的現象,如圖 4-3.10。若將 PDA 溫度提高到 600℃, 陷阱(traps)、缺陷(defects)得到較佳效果的修補,明顯改善了輔助穿隧 (TAT)現象,且因再結晶的影響,HfO2介電層結晶緻密度增加,使得 漏電流減少,此時主要的漏電流傳導方式,是電子透過結晶邊界來做 傳輸[14-15],如圖 4-3.11。 在沒有經過 PDA 的樣品,與經過 PDA 的樣品做比較。沒有經過積完成後,介電層處於穩定的狀態,內部的陷阱(traps)、缺陷(defects) 所存在的量較少。經過 PDA 400℃時,所提供的能量不足夠來完成完 整介電層內部缺陷的修補,使得有少許陷阱(traps)、缺陷(defects)產 生。隨著溫度的提高,陷阱(traps)、缺陷(defects)的修補效果越明顯, 使得陷阱輔助穿隧所引發的雜訊擾動電流現象降低,在 PDA 600℃ 時,可明顯看到雜訊擾動電流現象減少的情形。 圖 4-3.9 PDA 400℃介電層內部結晶狀況與漏電流傳導路徑示意圖

第五章 結論

5-1 電性分析

在 MIS 電容結構 TaN / 16nm HfO2 / p-Si /Al-Si-Cu,對介電層進行

熱退火處理(PDA)之後,從 I-V 曲線可觀察出,隨著 PDA 溫度的上升, 崩潰電壓(VRDB)跟著上升,推測原因為,PDA 溫度上升,HfO2介電層 中的陷阱(traps)與缺陷(defects)得到修補,使得結構更加穩固。在 C-V 曲線中,可看出經過 PDA 之後,遲滯現象有變小且平帶電壓往正偏 壓移動,原因為 PDA 處理後,介電層內的正陷阱電荷、缺陷陷阱電 荷有減少現象。但當 PDA 溫度過高時,會因介電層的微結構發生改 變,而使得電容值有下降的現象發生。在 TDDB 圖中,可看出施加 電壓初期會有雜訊擾動電流現象,其為 HfO2內有較多的陷阱和缺陷 存在,電子可藉由這些陷阱、缺陷部分進行傳導,漏電流成大幅度擾 動狀態。當 PDA 溫度越高,施加電壓初始的雜訊擾動電流有減少的 趨勢,且元件的崩潰時間(TBD)有上升的現象。

5-2 崩潰機制

整體而言,以 HfO2為介電層之電容結構,經過 PDA 處理過後, 整體的電性有得到改善,且閘極漏電流少許減少、結晶緻密度增加、 可承受的崩潰電壓提高,且遲滯的現象有減少,進而可看出介電層內 部的缺陷電荷密度有減少的現象。在可靠度分析中,從 TDDB 圖中 可看出,經過 PDA 處理之後,初期雜訊擾動電流有得到改善,崩潰 時間也有增加的現象。在 PDA 的處理過程中,最佳的溫度為 500℃ 到 600℃之間,若溫度太高,會導致 HfO2介電層的微結構發生改變, 電容有下降的情形發生。 在介電層崩潰機制方面,一開始介面層(IL)會因受到較大的電場 強度,而先發生 SBD 現象。在隨著測試時間的增加,HfO2介電層內 部的陷阱、電荷量會增多,導致在介電層內形成可供載子傳輸的漏電 流路徑,此時會發生 PBD 現象。在 HfO2與 TaN 之間的介面和 HfO2與矽基板之間的界面,因表面材質不同,可能會有不同的電場分佈。 介 電 層 內 部 的 缺陷 、 電 荷 受 到 電場 加 速 的 影 響 ,會 形 成 漏 斗 狀

參考文獻

[1]Thomas H. Lee, “微晶片的垂直躍進”科學人, 3 月, 82(2002)。

[2]D. A. Muller, T.Sorsch, S. Moccio, F. H. Baumann, K. Evans-Litterodt, and G. Timp, science, 399, 758(1999).

[3]陳宏瑋、趙天生, “高介電係數閘極介電層材料 在奈米電子元件上 之應用,”電子月刊, 第九卷, 第九期(2003)。

[4]S.-H. Lo、D. A. Buchanan、Y. Taur, “Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of

Ultra-Thin-Oxide nMOSFET’s” IEEE Electron device letters. Vol. 18, No.5, May 1997.

[5] 葉文冠、翁俊仁, “半導體製程技術與元件設計”,初版,第一章, 台灣東華書局股份有限公司, 2008 年 9 月。

[6]John Robertson, “Electronic structure and band offsets in High K oxides”Gate Insulator, IWGI 2001, p.76-77,2001.

[7] G. D. Wilk、R. M. Wallace、 J. M. Anthony, “High-k gate dielectrics: Current status and materials properties considerations,”J. Appl. Phy. Vol 89, 2001.

[8]Horng-Chih LIN、Da-Yuan LEE and Tiao-Tuan HUANG, “Breakdown Modes and Theor Evolution in Ultrathin Gate Oxide” J. Appl. Phy. Vol.41,2002.

[9]R Ranjan、KL Pey、CH Tung et al., ”Substrate injection induced ultrafast degradation in HfO2/TaN/TiN gate stack MOSFET”, IEDM,

2006

[10]鄭弘彬, 加熱溫度對真空任處理氫氣基磷灰石(HA)塗層鍵結強度 之效應探討, 碩士論文, 成功大學材料科學及工程學系, 2004.

[11]陳建銘, 無鉛錫球封裝晶片之掉落衝擊測試, 碩士論文, 中山大 學機械與機電工程學系, 2005。

[12]M. Houssa、M. Tuominen, “Trap-assisted tunneling in high permittivity gate dielectric stack”, JOURNAL OF APPLIED PHYSICS, VOLUME 87, NUMBER 12, 15 JUNE 2000.

[13] Ching-Wei CHEN, Chao-Hsin CHIEN, “Electrical Characteristics of Thin HfO2 Gate Dielectrics Prepared Using Different Pre-Deposition

Surface Treatments”, Japanese Journal of Applied Physics , Vol. 44, No. 1A, 2005, pp. 87–93.

[14]w. Zhu and T.P. Ma, “HfO2 and HfAlO for CMOS: Thermal Stability

and Current Transpost”, IEEE, 2001.

[15]黃國瑋, 熱處理條件對氧化鉿與矽酸鉿薄膜特性的影響, 碩士論 文, 成功大學電機工程研究所,2007年6月。

[16]楊永盛、楊慶宗,電子顯微鏡原理與應用,文京圖書,p.16 (1975). [17] Michel Depas, Tanya Nigam, and Marc M. Heyns, “Soft Breakdown

[18]F. Palumbo, S. Lombardo, “STRUCTRE OF THE BREAKDOWN SPOT DURING PROGRESSIVE BEAKDOWN OF ULTRA-THIN GATE OXIDES”, IEEE, 2004.

[19]S. Lombardo, F. Palumbo, “Breakdown transients in ultra-thin gate oxynitrides”, IEEE, 2004.

[20]國科會南區微系統研究中心, 高解析穿透式電子顯微鏡 儀器操 作手冊 TEM-2010, 2003.3.10.

[21]Donald A. Neamen、楊賜麟, 半導體物理元件, P500, 滄海書局。 [22]Richard S. Muller、Theodore I. Kamins、羅正忠, 半導體元件物哩,

![圖 1-1.2 不同高介電係數材料之介電常數與能隙比較[3]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8809423.227680/7.892.150.746.453.952/圖112不同高介電係數材料之介電常數與能隙比較3.webp)

![圖 1-1.3 不同高介電係數材料之能帶偏移量[6]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8809423.227680/8.892.230.661.158.519/圖113不同高介電係數材料之能帶偏移量6.webp)

![圖 2-2-1.3 穿透式電子顯微鏡與光學顯微鏡之比較[16]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8809423.227680/13.892.167.722.460.1083/圖2213穿透式電子顯微鏡與光學顯微鏡之比較16.webp)