國

立

交

通

大

學

電機資訊學院

電子與光電學程

碩

士

論

文

離子佈植對雙擴散汲極金氧半場效電晶體之影響

Impact of Ion Implantation Condition on the Characteristics

of Double-Diffusion Drain MOSFETs

研

究 生:沈啟誠

指導教授:崔秉鉞

教授

離子佈植對雙擴散汲極金氧半場效電晶體之影響

Impact of Ion Implantation Condition on the Characteristics

of Double-Diffusion Drain MOSFETs

研 究 生:沈啟誠 Student:Chi-Cheng Sheng 指導教授:崔秉鉞 Advisor:Bing-Yue Tsui 國 立 交 通 大 學 電機資訊學院 電子與光電學程 碩 士 論 文 A Thesis

Submitted to Degree Program of Electrical Engineering Computer Science College of Electrical Engineering and Computer Science

National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Electrics and Electro-Optical Engineering November 2004

Hsinchu, Taiwan, Republic of China

i

離子佈植對雙擴散汲極金氧半場效電晶體之影響

研究生:沈啟誠

指導教授:崔秉鉞

國立交通大學電機資訊學院 電子與光電學程(研究所)碩士班摘要

隨著半導體製程的發展,將高壓/高功率元件與傳統互補式金氧半 場效電晶體的製程技術整合在一起,已成為今日應用市場上最重要的 發展。其中雙擴散汲極金氧半場效電晶體是高壓元件中最早被運用的 方式,由於其構造簡單,在製程上並不需要加太多的製程條件及光罩 數。對於操作電壓在 20V 以下之元件而言,雙擴散汲極金氧半場效電 晶體,仍舊是所有高壓元件中的首選。 在本篇論文中,我們首先藉由模擬的方式去探討離子的植入條件 對雙擴散汲極金氧半場效電晶體在電性上的影響,藉此去了解其發生 的物理機制,並將由模擬出的結果及趨勢,選擇最適當的條件以改善 元件的特性。從過程中,我們發現將植入能量提高,可以提升元件的 耐壓能力,並減緩其突然折回的問題,但卻會降低其趨動能力;若提 高植入劑量,則可以改善其近似飽合的現象,提高其導通電流及降低 關閉漏電流,但其崩潰電壓卻會因此降低。因此,植入劑量及能量便 成為改善元件效能上的平衡機制,同時利用高劑量及高能量的條件, 將是本篇論文嘗試解決問題的方向。最後成功驗證高植入能量(240KeV)ii 及高植入劑量(1.4×1013cm-2)的條件可以大幅改善元件的特性,不僅緩和 了許多的效應,亦在不影響崩潰電壓太大的情況之下,提升了電流約 70%,關閉電流由原來 50pA 降至約 20pA。在此結果之下,尚可縮小 元件的尺寸,增加元件密度,並降低導通電阻,對於類似的元件極具 競爭力。

iii

Impact of Ion Implantation Condition on

the Characteristics of Double-Diffusion

Drain MOSFETs

Student:Chi-Cheng Sheng Advisor:Bing-Yue Tsui

Degree Program of Electrical Engineering Computer Science

National Chiao Tung University

ABSTRACT

With the progress of integrated circuit technology and the trend of system-on-a-chip (SOC), integrating high power devices with low power circuit is an important in the marketing of electronic application. The Double-Diffusion Drain MOS (DDDMOS) is the first device structure proposed to sustain high drain voltage. Although several advanced high voltage devices were developed in the past 20 years, DDDMOS is still the first choice for devices operating at voltage lower than 20 V due to its simple process.

In this thesis, we focus on the impact of ion implantation condition on the performance of DDDMOS. Using TCAD simulation tools, it is observed that with the increase of implantation energy, the breakdown

iv

voltage increases and the snapback issue is relaxed. However, the driving capability will be degraded due to the formation of non-converted p-type region on the drain surface. If the implant dosage is increased, the quais-saturation phenomenon at high gate voltage, the driving capability, and the turn-off leakage are all improved, but the breakdown voltage would be degraded. These results imply that high dose and high energy might be the better choice.

On the basis of TCAD simulation, the implantation energy was raised to 240 KeV and the implantation dose was raised to 1.4×1013cm-2. A 70% increase of saturation current and 75% reduction of turn-off current were obtained. Slightly decrease of breakdown voltage was observed due to the high dose. But the breakdown voltage is still higher than 18V. It is expected that with higher energy and higher dose device performance can be improved furthermore.

v

誌謝

當初決定進研究所之時,在工作上正好面臨了重大的轉變,從原 本屬於半導體供應鏈中的產品封裝測試工作,一下子跨到了最前端的 元件工程。對於一個跨領域的人來說,這是一個難得的經驗,所幸在 這段期間裡,有指導教授 崔秉鉞老師給予許多的協助,讓自己有機會 在不同的工作領域中,再次出發。對於已工作數年的我而言,研究學 問是一種與業界思考方式完全迥異的態度,崔老師對於實驗計劃、數 據分析乃至於論文的研討,不但謹慎求是,對於結果的論證亦要求學 生必須邏輯清楚,這些作學問的態度皆為我學習上的典範。 在進修的這段期間,感謝公司裡的長官們,給予時間及論文研究 所需的協助。當然更要感謝工作上的伙伴們,無論是協助幫我下實驗 的工程師,或是幫我分擔工作的同仁,讓我沒有後顧之憂的完成我的 學業。 最後,衷心感激我的妻子林秋秀女士,當我在工作與學業上應接 不暇的這些日子裡,必須忍受我早出晚歸,甚至負擔起教養小孩的責 任,使我得以全心投入工作及學業。僅以此論文感謝其辛勞及即將出 世的孩子。vi

目 錄

論文摘要(中文) ……….. i

論文摘要(英文) ……….. iii

誌謝 ……….

v

目錄 ……….

vi

表目錄 ………. viii

圖目錄 ………. ix

第一章 緒論

1.1 高壓金氧半場效電晶體簡介………. 1

1.2 論文研究動機………. 3

1.3 論文架構……… 5

第二章 漂移區對元件特性之影響

2.1 近似飽合現象……….

15

2.2 突然折回崩潰………

17

第三章 製程模擬與元件實作

3.1 前言……….

38

3.2 製程模擬結果之探討………

39

3.3 元件實作………

40

vii

第四章 元件電性量測結果與討論

4.1 汲極飽合電流(I

dsat)之探討……….. 53

4.2 崩潰電壓(BV

dd)之探討………

54

4.3 關閉電流(I

off)之探討………...

55

第五章 結論與展望

5.1 結論……….

73

5.2 後續工作………

74

參考文獻……….

76

viii

表 目 錄

第一章 緒論

第二章 漂移區對元件特性之影響

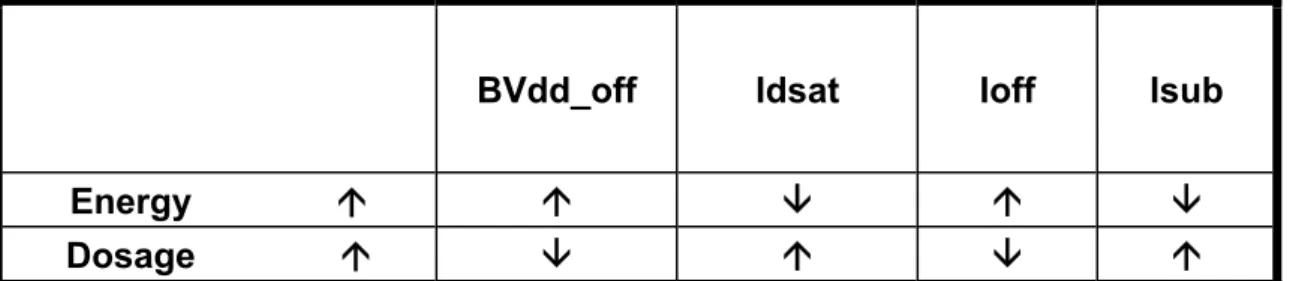

表2-1 改善近似飽合現象對元件特性之影響 表2-2 離子植入條件對元件特性之影響第三章 製程模擬與元件實作

表3-1 雙擴散汲極金氧半場效電晶體模擬參數值 表3-2 元件製作之離子植入條件分佈表第四章 元件電性量測結果與討論

表4-1 實驗結果統計值 表4-2 模擬關閉崩潰電壓及崩潰發生型式: (1)表面崩潰,及(2)接面崩潰ix

圖 目 錄

第一章 緒論

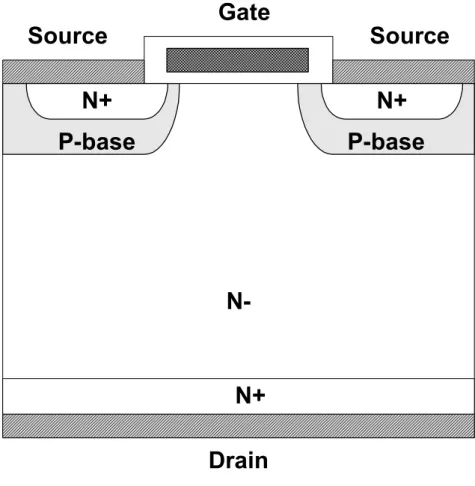

圖1-1 VMOS 電晶體結構表

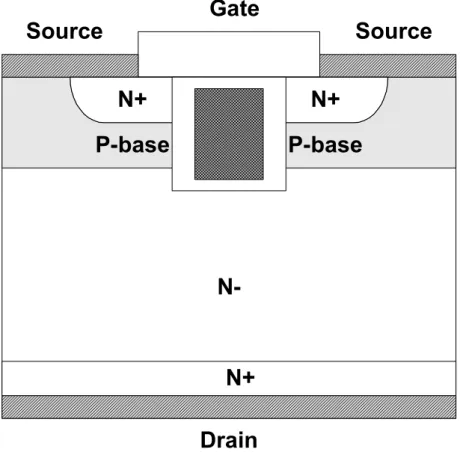

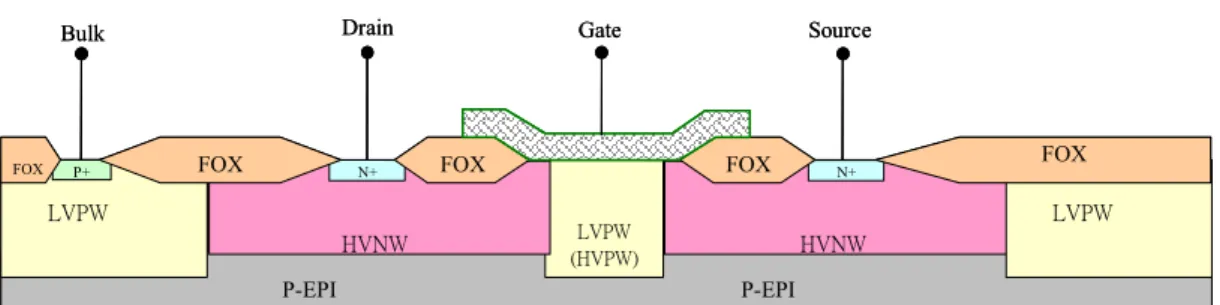

圖1-2 VDMOS 電晶體結構 圖1-3 UMOS 電晶體結構 圖1-4 DDDMOS 電晶體結構:(a)對稱型;(b)非對稱型 圖1-5 LDMOS 電晶體結構:(a)對稱型;(b)非對稱型 圖1-6 LDMOS 之自我生熱現象 圖1-7 高壓元件在高閘極偏壓時之近似飽合現象 圖1-8 高壓元件之寄生雙極性接面電晶體 圖1-9 高壓元件在基體電流-閘極電壓特性之雙峰現象第二章 漂移區對元件特性之影響

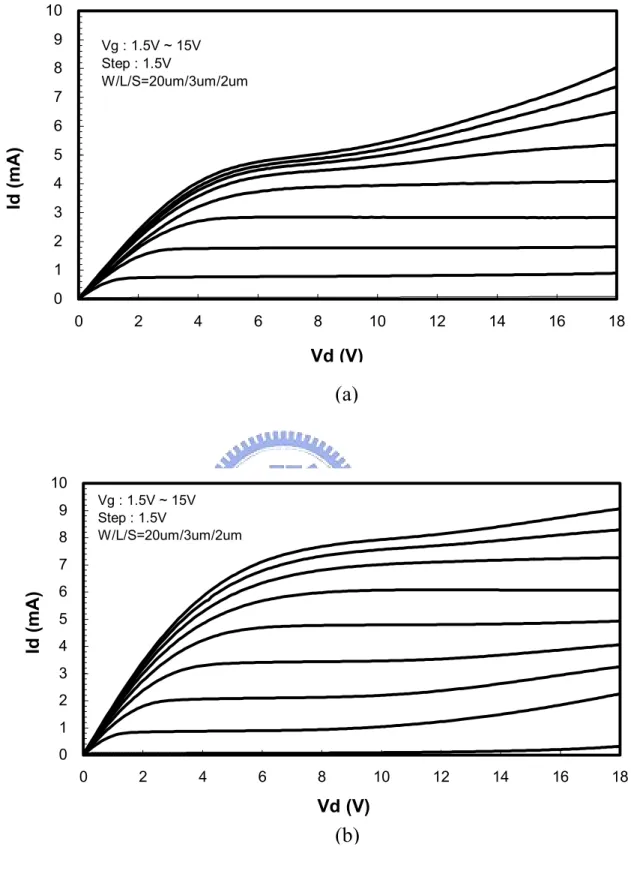

圖2-1 DDDMOS 之類型:(a)非對稱型,(b)對稱型其重要參數 圖2-2 DDDMOS 在操作電壓下,近似飽合現象之解釋 圖2-3 提高漂移區之濃度以改善近似飽合之現象:(a) 130KeV,6.5×1012 cm-2,(b)130KeV,8.5×1012 cm-2

圖2-4 提高漂移區之濃度對其片電阻之影響 (元件:W/L/S=20μm/3μm/1μm) 圖2-5 提高漂移區之濃度對汲極飽合電流之影響 (元件:W/L/S=20μm/3μm/1μm) 圖2-6 提高漂移區之濃度對元件崩潰電壓之影響 (元件:W/L/S=20μm/3μm/1μum)

x 圖2-7 非對稱元件寬度為 20μm,閘極至汲極端接點距離(S)之影響: (a)S=2μm,(b)S=1μm 圖 2-8 漂移區之閘極至汲極端接點距離(S)對關閉崩潰電壓之影響 圖 2-9 非對稱元件寬度為 20μm,通道長度(L)之影響: (a)L=20μm,(b)L=3μm

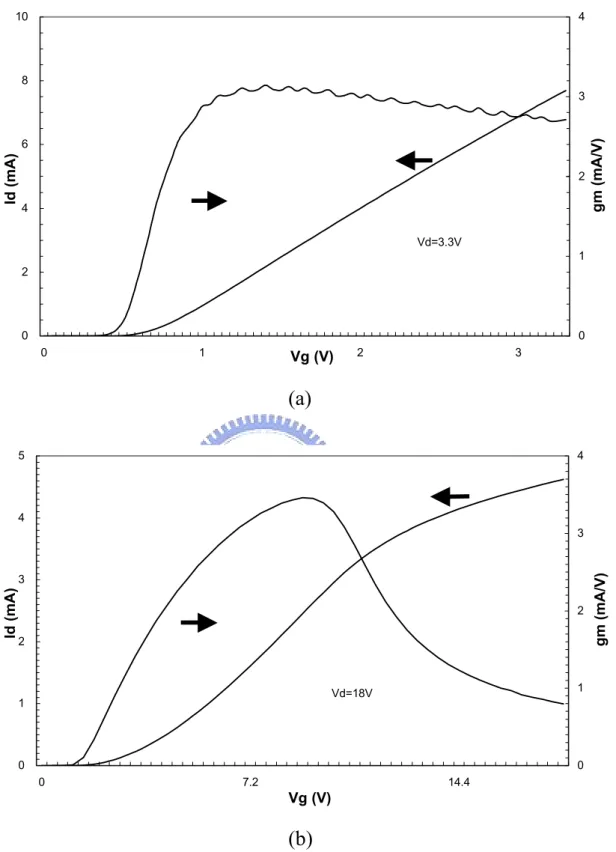

圖2-10 (a)傳統 MOS 元件與(b)DDDMOS 元件之互導比較

圖2-11 寄生雙接面電晶體所引起之突然折回現象

圖2-12 元件尺寸 W/L/S=20μm/1.2μm/1μm 之 DDDMOS,突然折回 崩潰發生於累增崩潰之前

圖2-13 雙擴散汲極區的濃度對寄生雙接面電晶體的影響:

(a) 170 KeV, 6.5×1012 cm-2,(b) 170 KeV, 1.0×1013 cm-2

圖2-14 不同劑量濃度對關閉崩潰電壓之影響 圖2-15 不同劑量濃度對導通崩潰電壓之影響 圖2-16 植入劑量對改善寄生雙接面電晶體效應之影響

第三章 製程模擬與元件實作

圖3-1 模擬元件(L/S=3μm/1μm)之電性特性 圖3-2 模擬元件(L/S=3μm/1μm)電性結果之趨勢圖: (a) 劑量:6.5×1012;(b) 能量:170KeV 圖3-3 不同植入條件對汲極飽合電流之趨勢圖, 電壓操作條件:Vg=13.5V,Vd=15V 圖3-4 雙擴散汲極區(漂移區)之濃度分佈圖:xi

圖3-5 在 Vg = 13.5V, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1×1013;(b) 240KeV, 1×1013 (元件:L/S=3μm/1μm)

圖3-6 在 Vg = 13.5, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1.4×1013;(b) 240KeV, 1.4×1013 (元件:L/S=3μm/1μm)

圖3-7 不同植入條件對關閉崩潰電壓之趨勢圖,電壓操作條件:

Vg=0V,Vd=15V

(元件:L/S=3μm/1μm)

圖3-8 在 Vg = 0, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1×1013;(b) 240KeV, 1×1013 (元件:L/S=3μm/1μm)

圖3-9 在 Vg = 0, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1.4×1013;(b) 240KeV, 1.4×1013 (元件:L/S=3μm/1μm) 圖3-10 DDD_NOS 之簡易製程流程圖

第四章 元件電性量測結果與討論

圖4-1 離子植入條件與汲極飽合電流之關係圖 圖4-2 離子植入條件與漂移區片電阻之關係圖 圖4-3 離子植入能量為 240KeV 之電性比較 劑 量:(a) 1×1013 cm-2,(b) 1.4×1013 cm-2 圖4-4 離子植入條件與崩潰電壓之關係圖 圖4-5 崩潰電壓發生及最大電場分布示意圖xii

圖4-6 模擬電場強度圖:Vg=0V,Vd=15V

(a) 240KeV, 1.4×1013cm-2,(b) 240KeV, 1×1013cm-2 圖4-7 模擬電場強度圖:Vg=0V,Vd=15V

(a) 120KeV, 1.4×1013cm-2,(b) 120KeV, 1×1013cm-2

圖4-8 離子植入條件對導通崩潰電壓之關係圖

圖4-9 離子植入條件與關閉電流之關係圖

圖4-10 植入劑量對 DDDMOS 之關閉電流的影響:

(a) 240KeV, 1×1013cm-2,(b) 240KeV, 1.4×1013cm-2

圖4-11 漂移區植入劑量對關閉電流之影響

圖4-12 漂移區植入劑量對基體漏電流之影響

圖4-13 汲極飽合電流與關閉電流之關係圖

1

第一章

緒論

1.1 高壓金氧半場效電晶體簡介

隨著半導體製程的發展,各類電子元件在商品化及市場機制的運 作下,其應用亦日趨多樣化。高壓金氧半場效電晶體(High Voltage MOS,或簡稱 HVMOS)亦逐漸受到重視,其應用範圍涵蓋電力應用 (如:汽車電子、控制馬達、電源供應器等)、平面顯示器應用(如:電 漿電視、薄膜電晶體液晶顯示器、有機電激光顯示器之驅動電路及控 制電路)及高頻通訊應用等等。 高壓金氧半場效電晶體在結構上,大致上區分為垂直式與水平式 兩大類。垂直式之結構,從過去到目前最常見的主要有三種類型:(1)V型 垂 直 通 道 金 氧 半 場 效 電 晶 體(V-shape Channel V-MOS 或 簡 稱 VMOS,如圖 1-1)[1-3],但因在 V 型尖端處易產生大電場聚集的現象, 而使得元件在該處發生崩潰(Breakdown),為改善此一問題因而有了可 靠 度 較 好 的 (2) 垂 直 式 雙 擴 散 金 氧 半 場 效 電 晶 體 (Vertical Double-diffused MOS 或簡稱 VDMOS,如圖 1-2)的出現[4],但由於雙

擴散金氧半場效電晶體兩側P 型基體區域(P-Body Region)與 N 型漂移

區(N-Drift Region)之間的空乏區會向內側擠壓,而造成接面場效電晶體 的 效 應(Junction Field Effect Transistor ; JFET) , 影 響 其 導 通 電 阻 [3-4,7-8]。若欲解決此問題,必須拉大兩 P 型基體間的距離,但此方式

2

有 了(3) 溝 槽 式 閘 極 功 率 金 氧 半 場 效 電 晶 體 (Trench Gate Power MOSFET 或稱 UMOS,如圖 1-3)的發展[5,7-8]。此類元件雖然在溝槽 兩端處會有較大電場聚集,而影響元件的崩潰電壓,但此結構可大大 降低導通電阻,並具有高輸入阻抗及高切換速率[2,5-8],因而逐漸取代 其它高功率元件而成為主流。綜合以上所述,垂直式金氧半場效電晶 體則除了要提升耐高電壓的能力之外,還要增加其導通電流,故著重 在提高元件功率之效能,故此類元件歸納為高功率元件(Power MOS)。 由於其易產生大電場及大電流,因此高功率元件多半為離散式元件, 其所占之面積亦相對較大以利散熱。 而水平式之結構主要著重在提高元件之耐壓能力,所使用之方法 為單純增加汲極區附近靠近通道(Channel)之漂移區域(Drift Region)的 長度,由於漂移區域為掺雜濃度較低的部分,因此這樣的結構將導致 電晶體的導通電阻(On-Resistance)偏高,但其優點為易與低電壓之互補 式金氧半場效電晶體(CMOS)製程技術整合在一起,故適合應用於操作 在 100 伏特以下之元件,而常見的類型主要有兩種:(1)一種是用於操 作在 20 伏特以下之雙擴散汲極金氧半場效電晶體(Double-Diffused

Drain MOSFET 或簡稱 DDDMOS,如圖 1-4)[9-10],但當汲極電壓增 加時,會有寄生的雙接面電晶體(Bipolar Junction Transistor,BJT)效應 的產生,甚至易產生所謂突然折回(Snapback)的現象,此一現象對於電 路設計者而言,是極不欲見到且不易掌握的特性;(2)另外一種則為操 作 在 20 伏 特 以 上 之 側 邊 雙 擴 散 金 氧 半 場 效 電 晶 體 (Lateral Double-Diffused MOSFET 或簡稱 LDMOS,如圖 1-5)[11-12],由於此

類元件主要操作在 20 伏特以上,為了避免影響低電壓之週邊電路元

件,並降低因高電場所引起的基體(Substrate)漏電現象,往往會在元件 之下多一道阻障層(Buried Layer),但此方式結構較為複雜,將導致其

3 寄生元件過多,甚而當閘極及汲極操作在高電壓時,其輸出電阻(Rout) 成為負值,即所謂的自我生熱(Self-Heating)的現象如圖 1-6,基於這些 有別於一般金氧半場效電晶體的特性,將會增加此類元件在模型化 (modeling)的困難度。

1.2 論文研究動機

針對雙擴散汲極金氧半場效電晶體(DDDMOS),其結構雖然簡 單,但特殊的電壓-電流特性,使得電路設計者在設計的過程中,增添 了許多的困難度及不確定性。雖然如此,但對於操作在 20 伏特以下之 高壓元件而言,雙擴散汲極金氧半場效電晶體在製程上所需的光罩數 比起其它的高壓或高功率元件要來得少,極易與一般的互補式金氧半 場效電晶體製程整合在一起,成本相對也較低,因此如何改善其存在 的問題,為本論文主要探討之重點。 目前工業界普遍使用的金氧半場效電晶體模型工具,以柏克萊大 學所提出之模型 BSIM3(Berkeley Short-Channel IGFET Model)為主 [13]。但 BSIM3 主要是針對低電壓(<10V)之一般金氧半場效電晶體所 設計,對於高功率或高電壓特殊結構之金氧半場效電晶體,則無法提 供適當且足夠之模型及參數以滿足所有高功率元件之一般性模型 (General Model)。目前在模型化的過程中,遭遇的幾個問題主要有: (1)BSIM3 並無提供所謂非對稱性(Asymmetric)元件之參數粹取及模 型,但對於雙擴散汲極場效電晶體而言,在其汲極端所增加之漂移區 是影響及改變電晶體特性最主要的因素,而此區域因屬於摻雜濃度較 低之區域,且所接收之電壓亦屬高電壓端,所以此區域不但成為元件 的高電阻(〜7.5KΩ/um)來源,且易受汲極端電壓之影響而改變,因此 如何掌握此區域之變化將決定模型化的準確性。(2)當元件操作在高汲4 極 電 壓 , 且 閘 極 電 壓 逐 漸 增 加 時 , 其 電 壓-電 流 特 性 有 趨 近 飽 合 (Saturation)的現象,此現象將導致元件之互導(Transconductance,gm) 降低,而影響其電壓增益(Voltage Gain),如圖 1-7 所示。藉由場效電晶 體的簡單電流與電壓關係,可歸納出下列特性: α ) ( gs t d V V I ∝ − 對於一般正常的長通道MOS 元件:α≧2.0 對於一般正常的短通道MOS 元件:α≧1.0 對於高壓MOS 元件:α<1.0 因此在電晶體的操作過程中,隱含了一般正常 MOS 元件及高壓 MOS 元件的雙重特性,現有的 BSIM3 主要是針對傳統的金氧半場效電 晶體所發展出來的模型,對於高電壓/高功率元件的複雜結構與特性, 則明顯不足以描述(fitting)其電性上的特性,僅能單獨描述其中一種特 性,而無法同時兼顧到數種特性的存在。(3)基體電流(Substrate Current)

對閘極電壓(Id-Vg)的特性是判斷元件熱載子效應(Hot Carrier Effect)的

重要指標,但很不幸的雙擴散汲極的結構常會使金氧半場效電晶體產

生寄生的雙接面電晶體如圖 1-8,使得基體電流所引起之基體效應

(Substrate- Current-induce Body Effect,SCBE)趨於嚴重,若在基體電流 對閘極電壓的特性上會觀察到有雙峰(Double-hump)的產生(圖 1-9),此 雙峰現象亦為目前BSIM3 模型尚無法描述之處。造成此一現象,其主 要因素亦來自於漂移區仍存在強大之電場,導致撞擊游離(Impact Ionization)所致,此一現象不單是元件模型不足的問題而已,影響最大 的恐將是其可靠度(Reliability)問題。 基於上述雙擴散汲極金氧半場效電晶體在電性上的特殊性質,就 目前所能提供的元件特性模型相當有限,因此本論文將探討如何從製 程上著手,藉此降低元件的特殊性質,以提高其可靠度及可設計性。

5

1.3 論文架構

本論文一開始主要是大略概述高電壓/高功率元件的結構及其優缺 點,以及其發展演進。並針對高壓元件特殊的性質,在模型化過程所 遭遇到的困難,大略簡述。至於後述章節,將針對雙擴散汲極金氧半 場效電晶體進行幾部分的探討: 在第二章裡,將探討漂移區對元件特性的影響。針對漂移區的濃 度及元件佈局,依據目前所擁有之電性上的數據,加以比較,及探討 其影響的因素。並藉由文獻上所探討之現象,及高壓元件中常見之寄 生效應,予以解釋及比較,以作為後續元件模擬及實作時之參考。 第三章則將利用製程及元件模擬軟體(TSUPREM4 及 MEDICI),針 對漂移區予以不同的植入劑量及能量進行模擬。並依據模擬所得之電 性上的結果加以比較,再藉由模擬出之元件結構(Profile)、電場分佈及 濃度分佈等工具,加以分析並解釋其在電性上的趨勢。最後再依模擬 之趨勢決定出最佳化的劑量及能量條件,再予以元件實際製作。 第四章將依據第三章以不同的離子植入條件所模擬出之結果,實 際製作出元件,藉著電性上的量測及分析,並配合第二章及第三章所 探討之現象加以驗證及解釋。 最後將整個論文做一總結並對未來此類元件可持續進行改善的部 分做探討。6 圖1-1 VMOS 電晶體結構

Gate

Source

Source

Drain

N+

N-P-base

N+

N+

P-base

7 圖1-2 VDMOS 電晶體結構

Gate

Source

Source

Drain

N+

N-N+

N+

P-base

P-base

8 圖1-3 UMOS 電晶體結構

Gate

Source

Source

Drain

N+

N-P-base

N+

N+

P-base

9 N+/P+ NDD/PDD Poly Gate

Drain

Source

N+/P+ N+/P+ NDD/PDD N+/P+ NDD/PDD Poly GateDrain

Source

N+/P+ N+/P+ NDD/PDD 圖1-4 DDDMOS 電晶體結構: (a)對稱型;(b)非對稱型N+/P+

NLDD/PLDD N+/P+NDD/PDD

Poly Gate

Drain

Source

N+/P+

NLDD/PLDD N+/P+NDD/PDD

Poly Gate

Drain

Source

(a) (b)10

P-EPI

LVPW HVNW LVPW

P+ FOX N+ FOX N+

FOX FOX

Bulk Drain Gate Source

P-EPI

LVPW HVNW LVPW

P+ FOX N+ FOX N+

FOX FOX

Bulk Drain Gate Source

P-EPI P-EPI LVPW (HVPW) HVNW LVPW LVPW HVNW

P+ FOX N+ FOX FOX N+

FOX FOX

Bulk Drain Gate Source

P-EPI P-EPI LVPW (HVPW) HVNW LVPW LVPW HVNW

P+ FOX N+ FOX FOX N+

FOX FOX

Bulk Drain Gate Source

圖1-5 LDMOS 電晶體結構: (a)對稱型;(b)非對稱型

(a)

11

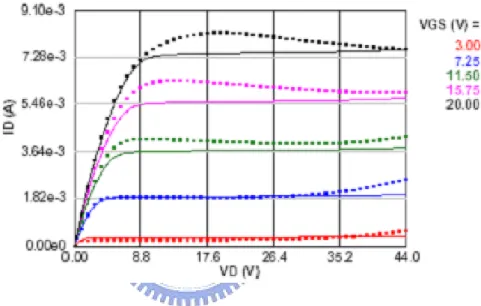

圖1-6 LDMOS 之自我生熱現象

……… : Measurement Data : Simulation Data

12 圖1-7 高壓元件在高閘極偏壓時之近似飽合現象 0 1 2 3 4 5 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd(V) Id(mA )

13 圖 1-8 高壓元件之寄生雙極性接面電晶體

Gate

Source

Drain

N-

N-P-sub

14 圖 1-9 高壓元件在基體電流-閘極電壓特性之雙峰現象 0 5 10 15 20 25 30 35 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

Vg(V)

Ib(

μ

A)

15

第二章

漂移區對元件特性之影響

2.1 近似飽合現象

雙擴散汲極金氧半場效電晶體早已被廣泛運用,隨著半導體製程 的發展,整合了高壓與低壓電路的設計,同時具備邏輯電路與類比電 路的應用,因此電晶體的工作範圍就不侷限在低壓範圍或僅高壓應 用。圖 2-1 是雙擴散汲極金氧半場效電晶體常見的兩種結構:非對稱型 (Asymmetric)及對稱型(Symmetric)元件,其在元件尺寸上的幾個基本參 數亦標示在圖中。當電晶體操作在高電壓及高電流區域時,會受制於 近似飽合現象的影響,以致於當閘極電壓增加到一臨界值時,汲極電 流會被限制而使得電流增加緩慢,甚至無法藉增加閘極電壓而繼續增 加。造成此現象的原因是:[13] 1.當汲極電壓(Vds)增加時,在漂移區與基體間的空乏區會逐漸擴增 如圖 2-2 所示,如此將使得漂移區的區域逐漸縮小,當汲極電壓 達到一電壓值時,通道和汲極開始被分離開(separation)。 2.當閘極電壓(Vgs)增加時,通道電阻會逐漸下降,與漂移區的阻抗 相比小到幾乎可忽略,因此,閘極電壓的增加對元件阻抗的降 低變得較為緩慢,使得汲極電流的增加趨於緩慢。 欲改善此一現象,解決方式有三種: 1. 增加漂移區的濃度,由圖 2-3 可觀察到此一問題的改善。由於漂 移區的濃度增加,其片電阻會下降,因此可提高元件的導通電16 流,如圖2-4、圖 2-5 所示。但是濃度的增加將使得空乏區寬度 縮減,電場強度增加,明顯將導致關閉狀態下的崩潰電壓下降, 參考圖2-6。 2. 縮短閘極(Gate Edge)至汲極接點(Contact)之距離 S,亦即縮短漂 移區的長度,可以降低漂移區的阻抗。由圖2-7 可比較出當 S=2 μm 時,閘極電壓逐漸增加至 8V,其汲極電流即開使趨近飽合; 但當S=1μm 時,閘極電壓約增加至 9V,其汲極電流才開使趨 近飽合現象。由於通道至汲極端的距離縮短,再加上阻抗的降 低,使得此區域的電場大幅提高,而導致元件的導通崩潰將提 早發生,由圖2-8 即可觀察出此一現象。 3. 增加元件的通道長度(Channel Length),由圖 2-9 可明顯看出, 當通道長度增加,其導通阻抗亦將增加,因為漂移區的阻抗不 變,此時施加在漂移區的電壓亦會減少,如此即可避免夾止作 用的提早發生。但由於通道阻抗的增加,將使得元件的汲極電 流( Id)明顯下降;另外在電路設計時,為補償汲極電流降低,只 得增加元件通道寬度,將使晶片面積(Chip Size)無形中增加許 多,而增加製造上的成本。 上述使用的方法,其主要目的皆是要使漂移區的空乏寬度能夠儘 量窄,而不使其進入夾止狀態。但無論以何種方式來改善近似飽合的 現象,對於元件的特性多少有些副作用,尤其是崩潰電壓的影響甚為 明顯從表2-1 的比較表中,約略可窺視出其影響的特性。僅管如此,近 似飽合的現象對於元件的可靠度而言,並不構成問題,但對於設計者 而言,所要面臨的問題是其驅動能力較不足,原因在於漂移區的濃度 較低,其阻抗較高所致。從圖 2-10 之互導(Transconductance,gm)的比 較中可看出,當元件同時操作在高閘極電壓及高汲極電壓下,對於 18V

17 的高壓元件而言,其 gm將隨著閘極電壓的增加,而從最大值約為 3.5 mA/V,迅速衰減至 1 mA/V 以下;但對於傳統金氧半場效電晶體而言, 其gm似乎並沒有太大變化。由關係式: α ) ( gs t d V V I ∝ − gm = gs d V I ∂ ∂ ∝α( − )α−1 t gs V V 對於傳統 MOS 元件而言,α≧1.0,其 gm會隨著 Vgs的增加而增 加,或維持在某一固定值。但對於高壓 MOS 元件而言,其α<1.0, 所以 gm將隨著 Vgs的增加而降低。換句話說,針對高壓元件的驅動能 力而言,當元件操作在飽合區時,其對於提升元件的導通電流是有限 的,對於設計者而言,將縮小元件的操作範圍,而降低其可設計性。 然而在提升驅動能力、崩潰電壓及降低寄生效應的過程中,所面 臨的另一個問題,卻會影響者元件的可靠度,即所謂的基體電流所引 起之基體效應(Substrate-Current-induce Body Effect,SCBE)[7,15,24], 以及突然折回崩潰的問題。

2.2 突然折回崩潰

突然折回崩潰(Snapback Breakdown)主要肇因於撞擊游離(Impact Ionization)所引起之寄生雙極接面電晶體效應,而撞擊游離又為高電場 環境所造成之物理現象。在雙擴散汲極金氧半場效電晶體中,會產生 高電場的情況主要有:(1)當閘極電壓操作在高電壓時,此時電晶體的 閘極氧化層會處在高電場之下(>4×106V/cm),(2)當汲極端操作在高電 壓範圍時,汲極端的空乏區也會處在高電場之下,此時也是熱載子(Hot Carrier)發生的主要原因,以及(3)閘極端和汲極端同時作用在高電壓範 圍,此時除了熱載子的產生之外,更可能因通道熱電子的注入(Channel18 Hot-Electron Injection,CHEI),致使閘極氧化層因注入的電子陷入 (Electron Trapped),而使電晶體的特性退化。在雙擴散汲極金氧半場效 電晶體中,會產生寄生雙極接面電晶體效應的操作條件,主要發生在 高汲極電壓及低閘極電壓之下(參考圖 2-11),對於高壓電晶體而言,最 主要的可靠性考量在於雙極接面電晶體的突然折回致使元件崩潰 (Snapback Breadown)。 圖2-12 可發現,對短通道元件而言,當操作電壓逐漸增加時,突 然折回崩潰會先在累增崩潰之前發生。誠如先前所言,突然折回崩潰 的發生在於熱載子所引起,而欲降低此效應的方式,依據文獻所探討 [16-21],降低雙擴散汲極的濃度,以趨緩汲極端空乏區的電場強度, 如此可使突然折回發生的操作條件提高,在圖 2-13(b)中,Vg=1.5V ~ 7.5V 即出現突然折回的 C 型曲線,與圖 2-13(a)相較之下,即可發現濃 度的增加,將使突然折回的現象提早發生。此外,降低漂移區的濃度, 亦可改善元件的關閉崩潰電壓(Turn-off Breakdown Voltage,如圖 2-6), 但如前一節所探討,此方式將使汲極端電阻增加,進而影響元件飽合

電流的大小,甚至使得元件的關閉電流(Ioff,Turn-off Current)增加(圖

2-14)。除此之外,我們亦從圖 2-15 中可發現,降低植入劑量的方式會 使元件操作在高閘極電壓時,其基體電流將明顯增加,而導致其基體 電流所引起之基體效應將更趨嚴重。若漂移區濃度較淡的元件,操作 在高電壓之下的偏壓時,由於其空乏區的寬度將較高濃度的漂移區來 得寬,因此將使得電位差主要集中在 N+與漂移區的接面,而使得其最 大電場強度高於漂移區濃度較高者[26]。在高電場條件之下,撞擊游離 將因此而漸增,導致基體電流(Isub)增加,並且提高基體的電位能 (Potential),使得導通電流亦相對增加。另外從圖 2-16 基體電流對閘極 電壓的特性(Isub-Vg Curve)上,會觀察到有所謂雙峰(Double-hump)的平

19 衡(Trade-off)問題,即降低雙擴散汲極區的濃度,欲改善其高閘極偏壓 時的基體效應時,卻會導致在低閘極偏壓時,其基體電流嚴重增加。 此亦說明基體電流所引起之基體效應將明顯影響雙擴散汲極金氧半電 晶體的操作特性及其可靠度。表2-2 為總結前述之離子植入條件,對於 元件特性影響之比較表,由表中可發現,植入能量與植入劑量的趨勢, 成為影響元件特性的蹺蹺板。 突然折回崩潰的問題亦可藉元件佈局(Layout)來改善,將基極端的 接點儘可能接近源極端(Source)的接點,以降低基體與源極間的電阻 值,避免基極端與源極端之間的電位大於 P-N 接面的導通電壓,甚而 有將基極和源極直接聯接在一起的方法。關於在元件佈局的方式,本 論文將不詳述其對元件的影響。由於突然折回崩潰與基體電流所引起 之基體效應,成為改善元件特性的蹺蹺板,如何從製程上去解決此一 問題,為本論文主要探討的重點,因此會將探討的重心放在離子佈植 的條件,對於雙擴散汲極電晶體的影響做詳細討論。在下一章節,將 針對雙擴散區域的不同離子植入條件,利用製程及元件模擬軟體,來 觀察元件在操作電壓下的物理機制,並比較不同條件下的差異,以作 為實際製作元件時之參考依據。

20

BVdd_off BVdd_on Idsat size

Concentration (D) Offset (S) Channel Length (L)

21

BVdd_off Idsat Ioff Isub

Energy Dosage

22 圖2-1 DDDMOS 之類型:(a)非對稱型,(b)對稱型其重要參數 (a) (b) L:通道長度 (μm) S:閘極端至汲極端接點之距離 (μm) N+ Gate N+ NDDD L S Gate N+ NDDD S L N+ NDDD S

23 圖2-2 DDDMOS 在操作電壓下,近似飽合現象之解釋 V g V d Channel N+ Depletion Separation

24

圖2-3 提高漂移區之濃度以改善近似飽合之現象:

(a) 130KeV,6.5×1012 cm-2,(b)130KeV,8.5×1012 cm-2 (a) (b) 0 1 2 3 4 5 6 7 8 9 10 0 2 4 6 8 10 12 14 16 18 Vd (V) Id (mA) Vg : 1.5V ~ 15V Step : 1.5V W/L/S=20um/3um/2um 0 1 2 3 4 5 6 7 8 9 10 0 2 4 6 8 10 12 14 16 18 Vd (V) Id (mA) Vg : 1.5V ~ 15V Step : 1.5V W/L/S=20um/3um/2um

25 圖2-4 提高漂移區之濃度對其片電阻之影響 (元件:W/L/S=20μm/3μm/1μm) 0 1 2 3 4 5 6 0 5 10 15 20 25 Dosage (×1012cm-2) Rs_NDDD (K Ω/□ ) 170 KeV 160 KeV

26 圖2-5 提高漂移區之濃度對汲極飽合電流之影響 (元件:W/L/S=20μm/3μm/1μm) (a) (b) 0 1 2 3 4 5 6 7 8 9 10 100 120 140 160 180 200 Energy (KeV) Idsat (mA) 6.5×10^12 8.5×10^12 0 2 4 6 8 10 12 14 0 5 10 15 20 25 Dosage (×1012 cm-2) Id s a t (m A ) 170 KeV 160 KeV 180 KeV 150 KeV

27 圖2-6 提高漂移區之濃度對元件崩潰電壓之影響 (元件:W/L/S=20μm/3μm/1μm) 0 5 10 15 20 25 30 0 5 10 15 20 25 Dosage (×1012cm-2) BVdd (V) 170 KeV 160 KeV 150 KeV 180 KeV (a) 0.0 0.5 1.0 1.5 2.0 0 5 10 15 20 25 30 35 Vd (V) Id ( μA) 6.5×10^12 8.5×10^12 1×10^13 (b) Energy : 170 KeV Dosage : cm-2

28 圖2-7 閘極至汲極端接點距離(S)之影響: (a)S=2μm,(b)S=1μm (a) (b) 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd(V) Id(mA) Vg : 1V ~ 14V Step : 1V W/L/S=20um/3um/1um Vg = 8V 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd(V) Id(mA) Vg : 1V ~ 14V Step : 1V W/L/S=20um/3um/1um Vg = 9V

29 圖2-8 漂移區之閘極至汲極端接點距離(S)對導通崩潰電壓之 影響 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 Vd(V) Id(mA) S=2μm S=1.5μm S=1μm Energy : 120 KeV Dosage : 6.5×1012cm-2 W/L=20um/3um

30 圖2-9 非對稱元件寬度為 20μm,通道長度(L)之影響: (a)L=20μm,(b)L=3μm (a) (b) 0 1 2 3 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd(V) Id(mA) Vg : 1V ~ 14V Step : 1V S=1um 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd(V) Id(mA) Vg : 1V ~ 14V Step : 1V S=1um

31

圖2-10 (a)傳統 MOS 元件與(b)DDDMOS 元件之互導比較 (a) (b) 0 2 4 6 8 10 0 1 Vg (V) 2 3 Id (mA) 0 1 2 3 4 gm (mA/V) Vd=3.3V 0 1 2 3 4 5 0 7.2 14.4 Vg (V) Id (mA ) 0 1 2 3 4 gm (mA/V) Vd=18V

32 圖2-11 寄生雙接面電晶體所引起之突然折回現象 0 5 10 15 0 5 10 15 Vd (V) Id (mA)

33 圖2-12 元件尺寸 W/L/S=20μm/1.2μm/1μm 之 DDDMOS, 突然折回崩潰發生於累增崩潰之前 0 5 10 15 0 5 10 15 20 Vd (V) Id (mA) Vg=3 Vg=9

34

圖2-13 雙擴散汲極區的濃度對寄生雙接面電晶體的影響:

(a) 170 KeV, 6.5×1012 cm-2,(b) 170 KeV, 1×1013 cm-2

(b) (a) 0 2 4 6 8 10 12 0 6 12 18 Vd (V) Id (mA) Vg : 1.5V ~ 13.5V Step : 1.5V W/L/S=20um/3um/2um 0 2 4 6 8 10 12 0 6 Vd (V) 12 18 Id (mA) Vg : 1.5V ~ 13.5V Step : 1.5V W/L/S=20um/3um/2um

35 圖2-14 不同劑量濃度對關閉電流之影響 0 10 20 30 0 5 10 15 20 25 Dosage (×1012cm-2) Ioff (pA) 170 KeV 160 KeV 180 KeV

36 圖2-15 不同劑量濃度對導通崩潰電壓之影響 0 1 2 3 4 5 6 7 8 9 10 11 12 0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 Vd(V) Id(mA) Nd=6.5×10^12 Nd=8.5×10^12 Nd=1×10^13 Energy : 170KeV W/L/S=20um/3um/2um

37 圖2-16 植入劑量對改善寄生雙接面電晶體效應之影響 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 0 5 10 15 Vg (V) Isub (mA) 6.5×10^12 8.5×10^12 1.0×10^13 Energy : 140 KeV Dosage : cm-2 Vd = 15V

38

第三章

製程模擬與元件實作

3.1 前言

本章將利用製程和元件模擬軟體TSUPREM4[22]及 MEDICI[23]來 探討在不同的離子植入條件下,其物理上和電性上的關聯性,並藉此 來決定下一步的實驗條件,以期得到更完整的資料。模擬之元件結構 將以第二章的圖 2-1 所示之非對稱元件為基礎,其模擬的幾個重要參 數,如表3-1 所示。在製程模擬過程中,由於其模擬參數並未經過實驗 晶片校準,因此我們將根據現有已知之離子植入條件及其電性上的量 測數據與元件模擬出之電性結果做比對,以確認模擬結果與實際數據 之趨勢是相近的。 根據第二章的敘述及先前的經驗,植入劑量的增加,可以增加汲 極飽合電流,降低關閉漏電流,並使元件在高閘極電壓下不致產生近 似飽合的現象。但在高劑量(>1×1013cm-2)時,汲極飽合電流及關閉漏電 流的特性似乎有趨於飽合的現象,亦即高劑量對於提升元件的效能上 並無太大的幫助,但若搭配者高植入能量(>180KeV),卻可以使得元件 的崩潰電壓略微提升。因此,在本章節的模擬中,將朝向高植入劑量 及能量的探討,以期能在其他特性不被影響之下,提升元件的崩潰電 壓。除了前述的目的,我們亦期望在高植入劑量及高植入能量的條件 之下,可以緩和閘極在高電壓時,趨近飽合的特殊性質,以提高元件 的可設計性。39

3.2 製程模擬結果之探討

首先,圖3-1、圖 3-2 分別為模擬元件特性的結果及趨勢圖。從圖 3-3 模擬植入條件與元件汲極飽合電流的趨勢圖中,可觀察到當植入劑 量增加時,可以提高元件的汲極飽合電流;但當植入能量提高時,低 劑量元件的汲極電流有下降的趨勢,高劑量元件的汲極電流則小幅增 加。我們可藉圖3-4 的模擬的濃度分佈(Doping Profile)觀察出,植入能 量的提高會使濃度分佈的峰值(Peak)較深,使表面濃度降低,漂移區的 表面電阻升高,甚至發生表面濃度不足而維持 P-型的現象。此時,通 道電流進入漂移區後,被迫繞行漂移區的下方,總電阻增加,因此汲 極端飽合電流會下降。但有趣的是,植入劑量的條件為 1.4×1013 cm-2 的趨勢與劑量1.0×1013 cm-2及6.5×1012 cm-2的趨勢是相反的。可能是因 為高劑量的時候,整體片電阻降低,但表面電阻降低得不多,電流不 需繞行漂移區下方所造成。由圖 3-5 及 3-6 觀察元件的剖面圖結構 (Cross-section)及在操作電壓下的電場分佈,當植入能量從 150KeV 提 高到 240KeV,漂移區表面出現 P-型區域,提高劑量可以使此 P-型區 域減少。雖然能量的增加將使漂移區的表面濃度降低,但同時也將使 元件的有效通道長度變短,而降低通道的導通電阻,因此當植入高劑 量時,元件的有效通道長度及漂移區的阻抗將左右整個元件的導通阻 抗,因而有不同趨勢變化之情況發生。 圖3-7 為模擬的崩潰電壓趨勢圖,可發現元件崩潰電壓會隨著植入 的能量增加而提高。我們可由圖3-8 及圖 3-9 的模擬電場分佈圖及空乏 區域圖,可比較出當植入劑量減少時,空乏區的寬度會較寬,電場降 低,故崩潰電壓增加;當植入能量提高時,漂移區靠近表面的濃度降 低,空乏區域較寬,電場強度降低,故崩潰電壓增加。40

3.3 元件實作

依據3.2 模擬之結果,我們決定之實驗條件如表 3-2 所示,關於元 件的基本結構,則仍依據表 3-1 之條件,不作結構或圖形上特別的實 驗。至於製程程序,則表示於圖 3-10 元件之簡易製程流程圖之中。其 中有關傳統互補式金氧半場效電晶體的製程部分,我們不多加描述, 但若與雙擴散汲極金氧半場效電晶體有關之部分,則會加註說明於圖 示中。由圖中顯示,雙擴散汲極金氧半場效電晶體與傳統的互補式金 氧半場效電晶體,在製程條件及程序上幾乎沒有太大差異,這也正如 之前我們所說的,雙擴散汲極金氧半場效電晶體極易整合於傳統的互 補式金氧半場效電晶體中的原因。41 項 目 參 數 值 元件通道長度 (μm) 1.2 元件閘極至汲極端接點距離 (μm) 1 元件操作電壓範圍 (V) 0 〜 15 元件閘極氧化層厚度 (Å) 310 離子佈植能量 (KeV) 120 〜 240 離子佈植劑量 (cm-2) 6.5×1012 〜 2×1013 表3-1 雙擴散汲極金氧半場效電晶體模擬參數值

42 離子植入劑量 (cm-2) 1.0×1013 1.4×1013 120 V 150 V 180 V V 離子 植入 能量 (KeV) 240 V V 表3-2 元件製作之離子植入條件分佈表

43 圖3-1 模擬 DDDMOS 元件(L/S=3μm/1μm)之電性特性 0 2 4 6 8 10 12 0 5 10 15 Vd (V) Id ( m A ) Vg : 1.5V ~ 13.5V Step : 1.5V Energy : 120 KeV Dosage : 6.5×1012cm-2

44 圖3-2 模擬元件(L/S=3μm/1μm)電性結果之趨勢圖 (a) 劑量:6.5×1012cm-2;(b) 能量:170KeV (a) (b) 0 2 4 6 8 10 12 100 120 140 160 180 200 Energy (KeV) Idsat (mA) Dosage : 6.5×1012 cm-2 0 5 10 15 20 25 0 5 10 15 20 25 Dosage (×1012 cm-2) Idsat (mA) Energy : 170 KeV

45 圖3-3 不同植入條件對汲極飽合電流之趨勢圖, 電壓操作條件:Vg=13.5V,Vd=15V 6 8 10 12 14 16 18 20 0 50 100 150 200 250 300 Energy (KeV) Idsat(mA) 6.5×10^12 1×10^13 1.4×10^13 Dosage : cm-2

46

圖3-4 雙擴散汲極區(漂移區)之濃度分佈圖:

(a) 150KeV, 1×1013cm-2;(b) 240KeV, 1×1013 cm-2 (a)

47

圖3-5 在 Vg = 13.5V, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1×1013 cm-2;(b) 240KeV, 1×1013 cm-2 (元件:L/S=3μm/1μm)

(a)

48

圖3-6 在 Vg = 13.5, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1.4×1013 cm-2;(b) 240KeV, 1.4×1013 cm-2 (元件:L/S=3μm/1μm)

(b) (a)

49 圖 3-7 不同植入條件對關閉崩潰電壓之趨勢圖, 電壓操作條件:Vg=0V,Vd=15V (元件:L/S=3μm/1μm) 10 15 20 25 0 50 100 150 200 250 300 Energy (KeV) BV dd (V) 6.5×10^12 1×10^13 1.4×10^13 Dosage : cm -2

50

圖3-8 在 Vg = 0, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1×1013 cm-2;(b) 240KeV, 1×1013 cm-2 (元件:L/S=3μm/1μm)

(a)

51 (a)

(b)

圖3-9 在 Vg = 0, Vd = 15V 條件下,電場分佈及空乏區圖:

(a) 150KeV, 1.4×1013cm-2;(b) 240KeV, 1.4×1013 cm-2 (元件:L/S=3μm/1μm)

52 P-Well Implant Field Oxidation Gate Oxide-2 Poly Gate NDDD Implant LDDN Implant S/D Implant Contact Implant DDD_NMOS NMOS V V V V V V V V V V V Gate Oxide-1 V V V V DDD VtN Implant V V V 圖3-10 DDD_NMOS 之簡易製程流程圖

53

第四章

元件電性量測結果與討論

在本章中,我們除了依據第三章模擬結果,藉由實際的元件製作, 以驗證之前的推論外,我們還將從實際量測中去觀察及探討,在模擬 中較不易推論的部分,以補在模擬探討中不足之處。4.1 汲極飽合電流(I

dsat)之探討

依據第三章模擬結果所擬定之實驗,其電性測量結果及統計值如 表4-1 所示。圖 4-1 為離子植入條件與汲極飽合電流之關係圖,由圖中 可觀察出其趨勢與第三章所模擬之趨勢(參考圖 3-2)是一致的,另外可 從圖 4-2 漂移區片電阻與植入條件的關係中,可看出植入劑量為 1× 1013cm-2的條件其片電阻高於 1.4×1013cm-2之條件,但與植入的能量似 乎並無明顯趨勢,再根據第三章我們所模擬的結果,可判斷當植入條 件為240 KeV,1×1013cm-2時,雖然其有效通道變短可降低通道電阻, 但電流流入漂移區之後的路徑所造成之整體阻抗,仍舊高於通道電阻 許多,以致其汲極飽合電流不升反降。 另外從圖 4-3(b)元件的電流-電壓特性中可看出,不僅提升了元件 的汲極飽合電流,先前我們所提及高壓元件在高閘極電壓時,會出現 近似飽合的現象亦有明顯的改善。雖然在低閘極電壓時,汲極電壓增 加仍有汲極電流些微上升的趨勢,但已不致於在操作電壓範圍之內, 即發生折回現象。54

4.2 崩潰電壓(BV

dd)之探討

圖4-4 為離子植入條件與崩潰電壓之關係圖,從圖中之趨勢我們並 無太大的意外,基本上與濃度的關係有著很明顯的趨勢,即提高植入 的能量或降低植入的劑量,皆可提升元件的崩潰電壓。另外在表 4-2 為根據模擬的崩潰電壓位置所作的統計,發現崩潰發生之位置有二: 一為汲極端漂移區的表面;另一則為汲極端的 P-N 接面的接面底部(圖 4-5),而決定發生方式的主因仍與漂移區的濃度有關。從表中可發現, 如前所述崩潰電壓將隨著植入能量的增加或者劑量的減少而提高,此 時,發生崩潰之處以 P-N 接面崩潰為主,原因在於植入的離子濃度高 峰(Peak)將因此較深(參考圖 3-4),亦將使得漂移區表面承受電壓的能力 提升,因此 P-N 接面崩潰將先於表面崩潰而發生。反之,高劑量或低 能量造成較高的表面濃度,使得最大電場位置移到表面而發生表面崩 潰。圖4-6、圖 4-7 顯示模擬的二維電場分佈,藉此了解不同植入能量 及劑量對電場強度的影響。從趨勢上可觀察到,接面的最大電場將會 隨著植入能量的提高或植入劑量的降低而減弱,崩潰電壓因此而提 升。表面電場則會隨著植入能量的增加而略為降低,從圖 3-9 中可發 現,此時電力線的分布主要集中在閘極邊緣的氧化層中,雖然最大的 電場強度發生於閘極邊緣,但水平方向電力線的密集程度,不如接面 的電力線來得高,所以電子雖然在如此強大的電場之下,但並未得到 足夠能量使元件產生崩潰,崩潰電壓未因此而下降。另外,我們亦可 觀察到,植入條件對於汲極端的 P-N 接面的電場強度,似乎影響並不 是那麼明顯。 另外有趣的現象是,導通崩潰將隨著植入劑量的增加而提早發生 (如圖 4-8 所示),這與我們在圖 2-15 所看到的趨勢是相反的。其主要因55 素為植入劑量的增加使得表面濃度提高,電場強度因而增加所致。

4.3 關閉電流(I

off)之探討

圖 4-8 離子植入條件與關閉電流的關係圖與先前我們所知的經驗 是相同的,即影響關閉電流的主要因素在於植入劑量的多寡,至於植 入能量的大小,影響不是很明顯,特別是在較高劑量的時候,影響程 度會更為趨緩,這是一個好現象。在圖 4-10 中我們可以觀察到,元件 在關閉(Vg<Vt)時漏電流的現象會隨著閘極電壓降低與汲極電壓的增加 而增加,造成此現象的主要因素是由所謂的閘極所致汲極端漏電流 (Gate-Induced Drain Leakage,GIDL)所引起。此現象的發生機制,是因 閘極氧化層之下與漂移區的重疊部分,因閘極端與汲極端的電壓差(VDG>0V),使得漂移區靠近表面的區域被空乏(參考圖 3-8 及圖 3-9)。

當汲極-閘極之電位差持續增加,使得電場增強,使得空乏區產生電子 -電洞對。在靠近氧化層之處由於電洞的聚集形成反轉層(Inversion Layer),而電子則由價電帶(Valence Band)直接穿透(Tunneling)位障到達 傳 導 帶(Conduction Band) , 而 形 成 所 謂 的 能 帶 穿 透 (Band-to-Band Tunneling)的現象。此時,在反轉層的電洞則會因水平方向的電場,流 至基體而形成漏電流。 傳統的金氧半場效電晶體的 GIDL 效應會隨閘極/汲極重疊區的濃 度增加而增加,這是因為較高的濃度產生較強的電場。但是對於本論 文的雙擴散汲極金氧半場效電晶體,圖 4-11 及圖 4-12 均顯示植入劑量 增加,關閉電流反而降低,這個現象和傳統的GIDL 效應相反。在 Vg<Vt 之後,關閉電流隨 Vg 降低而增加的斜率和植入劑量無關,這也表示關 閉電流和植入劑量的關係不是 GIDL 造成的。我們猜測是因為劑量低 的時候,漂移區很快就完全空乏,空乏區的電荷不多,漂移區電位降

56 不大,汲極電場較高。劑量增加之後,漂移區的空乏電荷較多,承受 較大的電位降,使得汲極電場反而較低。因此在本論文使用的劑量範 圍內,增加劑量反而造成較低的汲極漏電流。 另外我們從樣本晶片中各取四點位置,並量測其關閉電流與汲極 飽合電流的關係,得到圖 4-13 之結果,可看出植入劑量在 1×1013cm-2 時,其植入的能量將會影響漏電流與飽合電流之間的關係,但主要的 因素在於植入能量影響了汲極飽合電流的大小,換句話說,在這樣的 植入劑量條件之下,想要得到較高的汲極飽合電流有一種選擇,就是 降低植入能量。在1.4×1013cm-2這一組中,其關閉電流之所以趨近於定 值(~20pA)的原因,是因為自動量測系統對於電流量測能力的極限所導 致,從圖4-10 中不難看出,實際漏電流將比 20pA 更低。但若從圖 4-14 關閉電流與崩潰電壓之關係圖中,可看出這樣將會使得崩潰電壓降 低。所幸,在 1.4×1013cm-2這個條件之下,植入能量對於漏電流幾乎沒 有影響,但卻可提升元件的汲極飽合電流及崩潰電壓。雖然高植入劑 量的條件,在提升汲極飽合電流及崩潰電壓的特性上並不如低劑量那 麼顯著,但對於元件整體而言,卻可降低許多的寄生效應,不失是解 決雙擴散汲極金氧半場效電晶體的方法之一。

57 Wafer No. Energy (KeV) Dosage (cm-2) #1 #2 #3 #4 #5 #6 120 1.4×1013 V 150 1.4×1013 V 180 1.0×1013 V 180 1.4×1013 V 240 1.0×1013 V 240 1.4×1013 V

Vt

(V) 1.1595 1.1245 1.1218 1.1341 1.1365 1.1541 Idsat (mA) 10.710 11.223 10.691 11.291 10.235 11.714 BVdd (V) @ Vg=0 Id=1uA 16.93 16.02 18.87 17.32 19.99 18.24 Ioff (pA) @ Vd=13.5V Vg=0V 52.96 17.61 85.01 22.58 82.39 26.58 表4-1 實驗結果統計值58 表4-2 模擬關閉崩潰電壓及崩潰發生型式: (1)表面崩潰,及(2)接面崩潰 能量 (KeV) 關閉崩潰電壓(V) 120 150 180 240 6.5×1012 19.00 20.00 22.00 24.00 1×1013 15.00 16.00 18.00 21.00 劑量 (cm-2) 1.4×1013 14.00 16.00 17.00 19.00 陰影部分代表崩潰電壓為表面崩潰 其他部分則為接面崩潰

59 圖 4-1 離子植入條件與汲極飽合電流之關係圖 8 9 10 11 12 0 50 100 150 200 250 300 Energy (KeV) Idsat (mA) 1×10^13 1.4×10^13 Dosage : cm -2

60 圖 4-2 離子植入條件與漂移區片電阻之關係圖 0 1 2 3 0 50 100 150 200 250 300 Energy (KeV) Rs_NDD ( K Ω/□ ) 1×10^13 1.4×10^13 Dosage : cm -2

61 圖4-3 離子植入能量為 240KeV 之電性比較 劑量:(a) 1×1013cm-2,(b) 1.4×1013 cm-2 (a) (b) 0 4 8 12 16 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd (V) Id (mA) Vg : 0V ~ 15V Step : 1.5V W/L/S=20um/3um/1um 0 4 8 12 16 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Vd (V) Id (mA) Vg : 0V ~ 15V Step : 1.5V W/L/S=20um/3um/1um

62 圖4-4 離子植入條件與崩潰電壓之關係圖 15 16 17 18 19 20 21 0 50 100 150 200 250 300 Energy (KeV) BV dd (V) 1×10^13 1.4×10^13 Dosage : cm -2

63 圖 4-5 崩潰電壓發生及最大電場分布示意圖

E

SurfE

JunGate

NDDD

64

圖 4-6 模擬電場強度圖:Vg=0V,Vd=15V

(a) 240KeV, 1.4×1013cm-2,(b) 240KeV, 1×1013cm-2

(a) (b) Source Drain ESurf =7.03×105 V/cm EJun=4.80×105 V/cm ESurf =6.80×105 V/cm EJun=4.36×105 V/cm

65

圖4-7 模擬電場強度圖:Vg=0V,Vd=15V

(a) 120KeV, 1.4×1013cm-2,(b) 120KeV, 1×1013cm-2

(b) ESurf =6.13×105 V/cm EJun=5.32×105 V/cm (a) ESurf =6.21×105 V/cm EJun=5.57×105 V/cm

66 圖 4-8 離子植入條件對導通崩潰電壓之關係圖 0 5 10 15 0 5 10 15 20 25 Vd (V) Id (mA) 1.4×10^13 1×10^13 Energy : 240 Kev Dosage : cm-2 Vg = 15V

67 圖4-9 離子植入條件與關閉電流之關係圖 0 10 20 30 40 50 60 70 80 90 0 50 100 150 200 250 300 Energy (KeV) Ioff (pA) 1×10^13 1.4×10^13

68

圖4-10 植入劑量對 DDDMOS 之關閉電流的影響:

(a) 240KeV, 1×1013cm-2,(b) 240KeV, 1.4×1013cm-2

(a) (b) 1E-14 1E-13 1E-12 1E-11 1E-10 1E-09 1E-08 1E-07 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 -10 -5 0 5 10 15 Vg (V) ID (A) VD=2V VD=4V VD=6V 1E-14 1E-13 1E-12 1E-11 1E-10 1E-09 1E-08 1E-07 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 -10 -5 0 5 10 15 Vg (V) ID (A ) VD=2V VD=4V VD=6V

69 圖 4-11 漂移區植入劑量對關閉電流之影響 1E-14 1E-13 1E-12 1E-11 1E-10 1E-09 1E-08 1E-07 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 -10 -5 0 5 10 15 Vg (V) ID (A) 1.4×10^13 cm-2 1×10^13 cm-2 Dosage : cm -2 Vd=6V

70 圖4-12 漂移區植入劑量對基體漏電流之影響 0 10 20 30 40 50 0 5 10 15 20 25 Vdg (V) Isu b (p A ) 1×10^13 cm-2 1.4×10^13 cm-2

71 圖4-13 汲極飽合電流與關閉電流之關係圖 0 20 40 60 80 100 10.0 10.5 11.0 11.5 12.0 12.5 Idsat (mA) Ioff (pA) 180KeV 240KeV 120KeV 150 KeV Dosage : 1.4×1013 cm-2 Dosage : 1×1013 cm-2

72 圖4-14 關閉電流與崩潰電壓之關係圖 0 20 40 60 80 100 14 16 18 20 22 BVdd (V) Ioff (pA) 180KeV 240KeV 120KeV 150 KeV Dosage : 1.4×1013 cm-2 Dosage : 1×1013 cm-2

73

第五章

結論與展望

5.1 結論

雙擴散汲極金氧半場效電晶體早已被廣泛運用,由於元件結構簡 單,極易與互補式金氧半場效電晶體製程技術整合在一起,因此,如 何就既有之製程程序,小幅度變更製程上的條件(Condition),而不直接 更改製程配方(Recipe),但又能改善元件的特性,將是此類元件比其他 高壓元件較具競爭力之處。 本論文即依據此精神,從離子的植入條件上去著手探討其對元件 的影響程度及可行性。就觀察整個結果及趨勢,我們可以得到下列幾 個結論: (1) 若寄生雙接面電晶體及基極電流引起之基體效應在可靠度允 許之下被接受時,若欲提升元件的效能(performance),可將植 入劑量提高,但必須在1×1013cm-2以下,否則崩潰電壓將嚴重 偏低。 (2) 若欲改善元件的整體特性,最佳的條件是將植入的劑量及能量 調整在約 1.2×1013cm-2及 200KeV 以上,並搭配著能量的提高 而增加劑量,如此對於元件的崩潰電壓將有所幫助,亦可避免 因植入劑量的提高,而使漂移區表面所形成的反形態(type convert)成為阻礙電流行進的因素。不僅如此而已,對於飽合 電流可提升約70%,及降低關閉電流約 75%。 (3) 就離子植入條件對元件整體特性來看,崩潰電壓與關閉電流的74 趨勢是相反的;而飽合電流與關閉電流就植入劑量的趨勢來看 是一致的。所以想要提升崩潰電壓,則關閉電流及飽合電流就 須有部分程度的犧牲,意謂著在崩潰電壓與關閉電流或飽合電 流之間必須依據需求來取得一個平衡點。 (4) 依據實驗所得的結果及第二章的討論,我們在元件的尺寸上, 將有機會使通道長度(L)及閘極至汲極端接點的距離(S)再做適 度的縮小,不僅可以提高電晶體的驅動能力,亦可增加晶粒中 的電晶體密度,對於雙擴散汲極電晶體在尺寸縮小化(Scaling) 上而言,可謂是一重大突破。 正如之前我們所提,雙擴散汲極金氧半場效電晶體主要是被運用 於操作電壓在20V 以下之元件,就上述(3)結論所述,如欲將本論文所 討論的離子植入條件實現於更高操作電壓之元件時,首要任務必須使 元件至少可以耐壓至1.1 倍的操作電壓,再依據需求作適度的調整。

5.2 後續工作

截至目前為止,關於基體電流與植入條件之間的關係,以及環境 溫度對元件的影響,在本論文中我們尚未釐清及探討,但基本上與熱 載子有著很密切的關係,是未來對於元件特性上的探討可以繼續深入 的部分。另外針對更高植入劑量或能量的探究,亦是可以持續研究的 課題。 雙擴散汲極金氧半場效電晶體,由於應用於高電壓的條件,其閘 極端及汲極端對於元件而言都是很大的偏壓,將使得元件處在很強大 的電場之下,對於元件的使用有著很大的影響。因此,在可靠度方面 的測試,仍可繼續執行及探究,包括熱載子對閘極氧化層的影響、安 全操作面(Safe Operating Area,SOA)、栓鎖效應(Latch-up)測試及環境75 溫度測試等。 此外,我們可以藉由植入高劑量、高能量的物理機制,去思索如 何在低劑量、低能量下可以達到相似的效果,即在漂移區可多加植入 一較淺的p-區域。如同植入能量 240KeV 之下的條件,在漂移區表面所 形成接近反型態之區域,用以降低漂移區空乏之後的電場強度,是可 以考慮的方式。唯此 p-區域要如何控制其深度,是要面臨的挑戰,一 旦太深,不但無法改善元件的特性,根據本論文所得之趨勢,反而會 使元件的飽合電流降低,這部分是在探究 p-植入條件時,必需小心謹 慎的部分。 最後,正如一開始曾經探討過的元件尺寸,若能配合本論文所論 述的植入條件,去設法縮小尺寸,在電性上仍能保持相同特性,將使 得設計者在電路設計時能夠縮減晶粒大小,節省開發時間,如此必能 節省製造上的有形及無形的成本。對於雙擴散汲極金氧半場效電晶體 而言,其在高壓製程中將占有更重要的地位,並更具競爭力。

76

參考文獻

[1] F.E. Holmes and C.A.T. Salama, “VMOS-A New MOS Technology,”

Solid-State Electron., vol. 17, pp. 1147-1154, 1974.

[2] D. Ueda,H. Takagi, and G. Kono, “A New Vertical Power MOSFET Structure with Extremely Reduced On-resistance,” IEEE Trans. On

electron Device, vol. ED-32, pp. 2, 1985

[3] V.A.K. Temple and P.V. Gray, “Theoretical Comparison of DMOS and VMOS Structures for Voltage and On-resistance,” in IEDM Tech. Dig., 1979, Abstr. 4.5, pp. 88-92.

[4] S.C. Sun and J.D. Plummer, “Modeling the On-resistance of LDMOS, VDMOS and VMOS Power Transistor,” IEEE Trans. On electron

Device, vol. ED-27, pp. 356-367, 1980.

[5] T. Syau, P. Venkatramam, and B.J. Baliga, “Comparison of Ultralow Specific On-resistnce UMOSFET Structure,” IEEE Trans. On electron

Device, vol. ED-41, pp. 800-808, 1994.

[6] B.J. Baliga, “Trends in Power Discrete Device,” in Proc. ISPSD’98, 1998, pp. 5.

[7] B.J. Baliga, “Power Semiconductor Device,” 2nd Edition, PWS Press, 2000.

[8] V. Benda et al, “Power Semiconductor Device : Theory and Application,” JWS Press, 1999.

[9] M.D. Pocha and R.W. Dutton, “A Computer-Aided Design Model for High-Voltage Double Diffused MOS (DMOS) Transistors,” IEEE J.

77

Solid-State Circuit, vol. SC-11, pp. 718-726, 1976.

[10] T.J. Rodgers et al., “An Experimental and Theoretical Analysis of Double-Diffused MOS Transistors,” IEEE J. Solid-State Circuit, vol. SC-10, pp. 322-330, 1975.

[11] C. Bassin et al., “High-Voltage Device for 0.5μm Standard CMOS Technology,” IEEE Trans. On electron Device Letters, vol. 21, pp. 40-42, 2000.

[12] J. Jang et al., “RF LDMOS Characterization and Compact Modeling,” IEEE MTT-S Digest 2001.

[13] T. Myono et al., “High-Voltage MOS Device Modeling with BSIM3v3 SPICE Model,” IEICE Trans. Electron., vol. E-82C, No.4 April 1999, pp. 630-637.

[14] A.W. Ludikhuize, “Kirk Effect Limitations in High Voltage IC’s,”

Symposium on Semiconductor Device & IC’s, pp. 249-252, 1994. [15] C.Y. Chang and S.M. Sze, “ULSI Device,” JWS Press, 2000.

[16] Eiji Takeda et al., “Hot-Carrier Effects in MOS Device,” Academic Press, 1995.

[17] Hussein Ballan and Michel Declercq, “High Voltage Device and Circuits in Standard CMOS Technologies,” Academic Press, 1998. [18] Y. Taur and T.H. Ning, “Fundamentals of Modern VLSI Device,”

Cambridge University Press, 1997.

[19] S.M. Sze, “Physics of Semiconductor device,” JWS Press, 1983.

[20] S. Wolf and R.N. Tauber, “Silicon Processing for the VLSI era volumn 3 : The Submicron MOSFET,” California Lattice Press, 1995.

78 JWS Press, 1967.

[22] “User Manual of TSUPREM-4 Version 2003,” Synopsys, 2003. [23] “User Manual of MEDICI Version 2003,” Synopsys, 2003.

[24] J.H. Huang et al., “A Physical Model For MOSFET Output Resistance,” in IEDM Tech. Dig., 1992, pp. 569-572.

[25] M.K. Orlowski and C. Werner, “Model for the Electric Fields in LDD MOSFET’s - Part II : Field Distribution on the Drain Side,” IEEE

Trans. On electron Device, vol. ED-36, pp. 382-391, 1989.

[26] K.W. Terrill et al., “An Analytical for the Channel Electric Field in MOSFET’s with Graded-Drain Structure,” IEEE Trans. On electron