國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

應

應

應用

用

用於

於

於兆

兆

兆級

級

級序

序

序列

列

列傳

傳

傳輸

輸

輸系

系

系統

統

統之

之

之等

等

等化

化

化器

器

器技

技

技術

術

術

Multi-Gbps Equalizer Technology for Serial

Link System

研 究 生 : 黃喻暄

指導教授: 周世傑 博士

應用於兆級序列傳輸系統之等化器技術

Multi-Gbps Equalizer Technology for Serial Link System

研 究 生 : 黃喻暄

Student: Yu-Sam, Huang

指 導 教 授 : 周世傑 博士

Advisor: Dr. Shyh-Jye Jou

國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

A Thesis

Submitted to Department of Electronics Engineering & Institute

of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Department of Electronics Engineering

October 2008

HsinChu, Taiwan, Republic of China

應用於兆級序列傳輸系統之等化器技術

學生: 黃喻暄

指 導 教 授 : 周世傑 博士

國立交通大學

電子工程學系 電子研究所碩士班

摘

要

在多媒體時代的今天,各種高速串列傳輸技術廣泛的使用在許多高效能的電子產品 中。為了讓訊號經過各種傳輸通道破壞後可以保持一定的品質,等化器在高速串列傳 輸的系統中扮演了重要的角色。根據信號處理的方式我們可以將等化器分成連續時間 領域等化器跟離散時間領域等化器。 在本論文中,首先我們提出了一個操作在 6 Gbps 的連續時間領域等化器。在等 化電路的輸入端我們使用了一個準位平移電路來減少通道輸出端直流電壓準位漂移對 等化器造成的影響。準位平移電路同時也提供低頻訊號的放大功能。為了減少在增加 高頻放大率的同時對低頻訊號的抑制量,我們將等化電路設計成兩級串接的模式。我 們提出的連續時間領域等化器在時脈訊號頻率 3 GHz 可以提供 13.87 dB 的補償。 實做晶片使用聯電標準臨界電壓 90 耐米互補式金氧半導體製程來製造。佈局之後的 模擬結果,位於等化器輸出端的信號眼圖可以開至正負 250 mV,而緩衝器的輸出端 可以將信號眼圖張開到規格所定的正負 300mV。電路總面積為0.49 × 0.49 mm2。在 1.0 V 的操作電壓下,電路總功率為 78.83 mW。 接著,我們對一個半速率的決策回授等化器電路架構 [8]提出跳躍式係數更新 方案以及乒乓係數更新方案。該電路結構擁有5筆過去的資料消除符號間干擾並且 使用一個位元的猜測方法來紓解時間上得限制。係數更新的演算法是使用sign-sign LMS演算法。在跳躍式係數更新方案中,係數計算電路的操作頻率將會降低而且功率消耗也會減少。乒乓係數更新方案則是在每個資料路徑上省下一個用來計算錯誤量正 負號的比較器。針對這兩個係數更新方案,我們執行許多不同條件的模擬並且整理決 策回授等化器係數收斂時間的表現。希望能夠藉此得到設計電路時在規格的規範下選 擇相關參數的方針,尤其是決策回授等化器係數收練的速度。

Multi-Gbps Equalizer Technology for Serial Link System

Student: Yu-Sam, Huang

Advisor: Dr. Shyh-Jye Jou

Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

ABSTRACT

In the multi-media era, many high-speed serial link trarnsmission technologies are developed and are widely used for high performance modern electronic product.

In order to maintain the data quality that will be attenuated by communication channel, the equalizer becomes an important component in the high-speed serial

link system. Based on the type of data processing, the equalizer can be categoried into continuous-time equalizer and discrete-time equalizer.

In this thesis, we first propose a continuous-time equalizer that operates at

6 Gbps. We take a level-shifter stage in the front of our proposed equalizer for minimizing the DC voltage level variation in the equalizer input and for providing

the low-frequency gain in the proposed circuit. In the equalization block, we use two serial cascade stages to minimize the gain suppression at low frequency while

to boost the gain in high frequency. The proposed equalizer can compensate 13.87 dB channel loss at clock frequency of 3 GHz. The test chip is fabricated

in UMC 90 nm CMOS regular-Vt process. The post-layout simulation results show that the data eye in the output of equazlier stage is about ±250 mV, and the data eye in the output of buffer stage can reach ±300 mV that meets our specification. Total area of our proposed equalizer including pads is 0.49× 0.49 mm2 and power consumption is 78.83 mW under 1.0 V supply voltage.

Secondly, we propose a hopping coefficients update and ping-pong coeffi-cients update schemes for a discrete-time half-rate DFE (Decision-feedback

(intersymbol-interference) effects and uses the speculation method to relax the timing

con-strain. The algorithm used for coefficients update is the sign-sign LMS (least-mean-square) algorithm. For the hopping update scheme, the operation frequency

of coefficients update block can be reduced and the power can be saved. For ping-pong update scheme, we calculate the sign of error under different conditions in

these two data paths. The ping-pong update scheme saves one comparator for calculating the sign of error in each data path. For these two update schemes, we

run different conditions and summary the convergent performance. We get the guideline of choosing parameters in the proposed equalizer under some system

誌

誌

誌

謝

謝

謝

首先我要感謝指導教授周世傑老師在我兩年又1個半月的碩士生涯中細心的指 導。不論是在研究內容上的指導以及每次meeting報告時所給予的糾正以及建議,都 讓我在這短段時間獲益良多,同時也要謝謝老師這段時間對我犯錯時的包容,耐心並 且孜孜不倦的叮嚀我們要努力從事研究。在此祝福老師家庭和樂融融,老師與師母身 體健康笑口常開,老師的三位小朋友們在未來求學的路上一路順風。另外,也要感謝 蘇朝琴教授、陳巍仁教授與蔡嘉明教授撥冗參加口試,給予珍貴的經驗讓我的論文能 更加完整。 接著,我要特別謝謝林志憲博士在整個研究的過程中不厭其煩的解答我各式各樣 的問題。整本論文能夠完成,他的幫忙一直是很關鍵的一個因素。謝謝他提供我許多 研究的方向以及許多小細節上得幫忙。祝福他接下來的從軍生活一切順利,家庭生活 圓滿。 這一路上,還要謝謝許多朋友陪伴我走過一段又一段的難關。除了常常聽我滿滿 的抱怨還有我接納陷入低潮時負面的情緒,每當想到大家對我這段時間的支持與鼓 勵,再多的謝謝也無法道盡我心中的感恩之情,很高興這段時間能有你們這群朋友的 陪伴。祝福大家在各自的跑道上一切順利,不論是找工作或者出國深造都能有佳音。 最後,要謝謝我的父母的照顧與支持。在我走入低潮的時候幫我鼓勵打氣,甚至 還要每天聽我發牢騷,真的辛苦你們了。Content

摘要 . . . ii Abstract . . . iv 誌謝 . . . vi Content . . . vii List of Tables . . . x List of Figures . . . xi 1 Introduction . . . 11.1 Challenges in High-Speed Applications . . . 1

1.2 Motivation . . . 3

1.3 Thesis Organization . . . 3

2 Theory of Equalizer . . . 5

2.1 Equalizers in High-Speed Application . . . 5

2.1.1 Physical Limitation of High-Speed Transmission . . . 5

2.1.2 Equalizer and Compensation . . . 8

2.2 Concepts of Equalizers . . . 10

2.2.1 Continuous-Time Equalizers . . . 10

2.2.2 Discrete-Time Equalizers . . . 12

2.3 Traditional algorithm of discrete-time Equalizer . . . 15

2.3.2 Mean-Square Error Algorithm . . . 17

2.4 General Topology of Equalization . . . 18

2.4.1 Linear Equalization . . . 18

2.4.2 Decision Feedback Equalization . . . 19

3 Continuous-Time Equalizer . . . 21

3.1 Overview . . . 21

3.2 Motivation and the proposed architecture . . . 22

3.3 Circuit design and simulation results . . . 24

3.3.1 Level-Shifter . . . 24

3.3.2 Equalizer stage . . . 27

3.4 Implementation and layout . . . 39

3.5 Measurement environment setup . . . 47

4 Discrete-Time equalizer . . . 48

4.1 Overview . . . 48

4.2 Techniques and architectures for discrete-time DFE . . . 49

4.3 Sign-sign least-mean-square algorithm . . . 52

4.3.1 Method of steepest descent . . . 52

4.3.2 Sign-sign LMS algorithm . . . 54

4.4 Design parameters selection based on power and area consideration 55 4.4.1 Architecture in our model . . . 56

4.4.3 Ping-pong coefficients update scheme . . . 63

5 Conclusions and Future Works . . . 77

5.1 Conclusions . . . 77

5.2 Future Works . . . 78

List of Tables

1.1 Industrial standards of high-speed serial link . . . 1

2.1 Skin depth of several material at various frequencies . . . 7

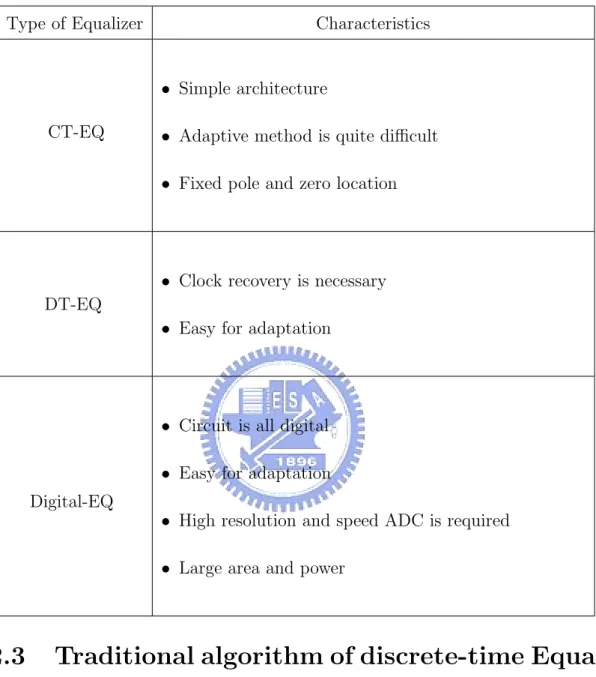

2.2 Characteristics of CT-EQ, DT-EQ and Digital-EQ . . . 15

3.1 Specification of proposed equalizer . . . 23

3.2 Pad assignment . . . 44

3.3 Summary of proposed test chip . . . 46

3.4 Comparison with other works . . . 46

4.1 Eave and Tcon for hopping update scheme under three different data rate . . . 62

4.2 Eave and Tcon for hopping update scheme with/without ping-pong update scheme under five different data rate . . . 72

4.3 Eave and Tcon for hopping update scheme under three different data rate with ping-pong update scheme. . . 74

4.4 Eave and Tcon for hopping update scheme under three different data rate with ping-pong update scheme and 8b/10b input data. . 76

List of Figures

1.1 An ISI phenomenon and error introduced by wire. (a) An impulse

and its response. (b) A series of impulse and their response. . . . 2

2.1 Channel response and equalizer response . . . 9

2.2 Typical system view with equalizer . . . 10

2.3 Frequency Response of continuous-time equalizers . . . 11

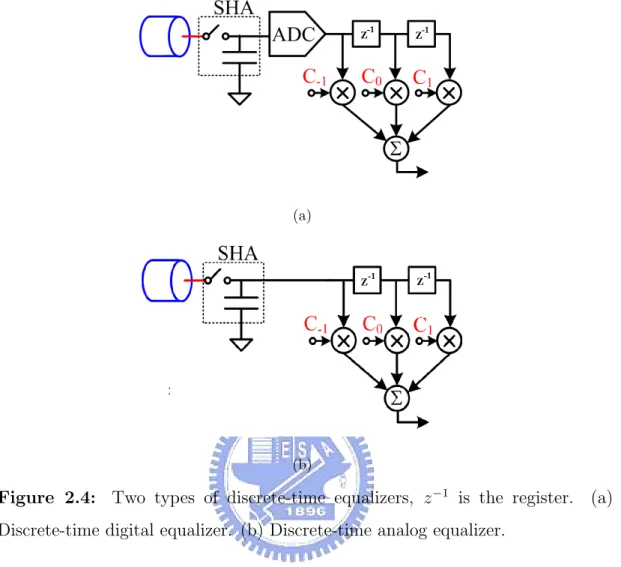

2.4 Two types of discrete-time equalizers, z−1 is the register. (a) Discrete-time digital equalizer. (b) Discrete-time analog equalizer. 14 2.5 Noise enhancement in zero forcing equalizer . . . 16

2.6 Noise enhancement is reduced by MSE . . . 18

2.7 (a) Basic block diagram of a linear equalizer. (b) Equivalent block diagram of linear equalizer [16]. . . 19

2.8 (a) Equivalent block diagram of DFE. (b) Basic block diagram of a DFE [16]. . . 20

3.1 Equivalent model of continuous-time equalizer . . . 21

3.2 Equalizer model of our proposed equalizer . . . 22

3.3 Block diagram of our proposed equalizer . . . 23

3.4 Circuit diagram of level-shifter . . . 25

3.5 Relationship between output and input DC voltage of the level-shifter. . . 26

3.7 Circuit diagram of one equalizer stage . . . 28

3.8 Small signal circuit of equalizer. (a) Simplified equivalent

small-signal model. (b) Further simplified equivalent small-small-signal model. (c) Virtual ground in equivalent small-signal model. . . 30

3.9 Half circuit of equalizers. . . 31

3.10 Final circuit of equalization stage . . . 31

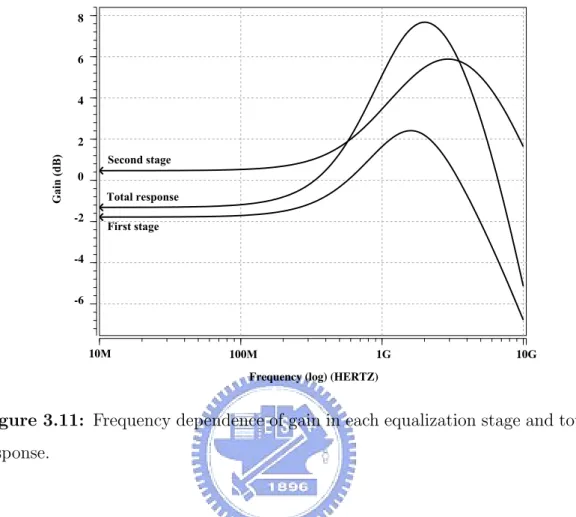

3.11 Frequency dependence of gain in each equalization stage and total

response. . . 32

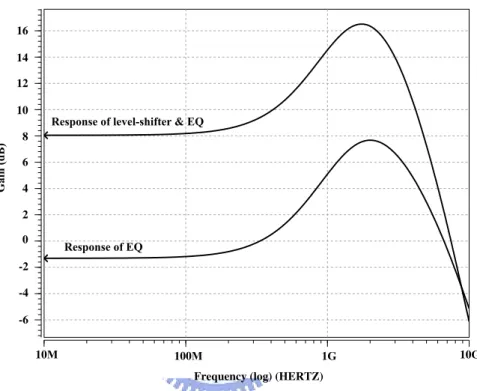

3.12 Response of equalizer stage and combination of level-shifter and equalizer. . . 33

3.13 Frequency response of channel output and equalizer output. . . . 34

3.14 Group delay in the equalizer output . . . 35

3.15 Eye diagram of pre-layout simulation: (a) channel output. (b) equalizer output. (c) buffer output . . . 37

3.16 Jitter histogram of pre-layout simulation: (a) equalizer output. (b)

buffer output . . . 38

3.17 Eye diagram of post-layout simulation under TT corner condition: (a) channel output. (b) equalizer output. (c) buffer output . . . . 40

3.18 Jitter histogram of post-layout simulation under TT corner

condi-tion: (a) equalizer output. (b) buffer output . . . 41

3.19 Eye diagram of post-layout simulation under FF corner condition: (a) channel output. (b) equalizer output. (c) buffer output . . . . 42

3.20 Eye diagram of post-layout simulation under SS corner condition:

3.21 Layout view of the proposed equalizer. (a) Total view. (b) zoom-in

on level-shifer and equlizer block. . . 45

3.22 Test environment setup . . . 47

4.1 Typical block diagram of DFE with one tap . . . 50

4.2 Block diagram of speculation for one bit . . . 51

4.3 Half-rate DFE block diagram with speculation . . . 51

4.4 N-tap FIR Wiener filter . . . 53

4.5 The architecture of analog discrete-time DFE in our model . . . . 56

4.6 Data arrangement of (a)half-rate architecture, (b)quarter-rate ar-chitecture . . . 59

4.7 Hopping update scheme under data-rate. (a) DFE Coefficients, (b) error. . . 61

4.8 Hopping update scheme under 1/4 data-rate. (a) DFE Coefficients, (b) error. . . 61

4.9 Hopping update scheme under 1/16 data-rate. (a) DFE Coeffi-cients, (b) error. . . 62

4.10 Illustration of calculating sign of error speculatively. . . 64

4.11 Hopping update scheme under data rate without ping-pong update scheme. (a) DFE coefficients. (b) error . . . 67

4.12 Hopping update scheme under data rate with ping-pong update scheme. (a) DFE coefficients. (b) error . . . 67

4.13 Hopping update scheme under 1/2 data rate without ping-pong update scheme. (a) DFE coefficients. (b) error . . . 68

4.14 Hopping update scheme under 1/2 data rate with ping-pong

up-date scheme. (a) DFE coefficients. (b) error . . . 68

4.15 Hopping update scheme under 1/4 data rate without ping-pong update scheme. (a) DFE coefficients. (b) error . . . 69

4.16 Hopping update scheme under 1/4 data rate with ping-pong

up-date scheme. (a) DFE coefficients. (b) error . . . 69

4.17 Hopping update scheme under 1/8 data rate without ping-pong update scheme. (a) DFE coefficients. (b) error . . . 70

4.18 Hopping update scheme under 1/8 data rate with ping-pong

up-date scheme. (a) DFE coefficients. (b) error . . . 70

4.19 Hopping update scheme under 1/16 data rate without ping-pong update scheme. (a) DFE coefficients. (b) error . . . 71

4.20 Hopping update scheme under 1/16 data rate with ping-pong up-date scheme. (a) DFE coefficients. (b) error . . . 71

4.21 Hopping update scheme under data rate with ping-pong update

scheme. (a) DFE coefficients. (b) error . . . 73

4.22 Hopping update scheme under 1/4 data rate with ping-pong up-date scheme. (a) DFE coefficients. (b) error . . . 73

4.23 Hopping update scheme under 1/16 data rate with ping-pong

up-date scheme. (a) DFE coefficients. (b) error . . . 74

4.24 Hopping update scheme under data rate with ping-pong update scheme and 8b/10b input. (a) DFE coefficients. (b) error . . . 75

4.25 Hopping update scheme under 1/4 data rate with ping-pong

4.26 Hopping update scheme under 1/16 data rate with ping-pong

up-date scheme and 8b/10b input data. (a) DFE coefficients. (b) error . . . 76

Chapter 1

Introduction

1.1

Challenges in High-Speed Applications

Following the trend of serial link transmission applications, we can observe that data-rate is increasing dramatically in the resent years as shown in

Ta-ble 1.11. In these high data-rate communications, transmitted data will suffer severe frequency-dependent loss. Skin effect, for example, will attenuate the high

frequency signal in wire transmission. The loss limits the transmission speed and length of cable. The negative effect gives an upper bound when systems demand

higher speed and wider range in the area of transmission technology.

Table 1.1: Industrial standards of high-speed serial link

USB 2.0 (High Speed) 400 Mb/s

PCI-Express 2.5 Gb/s

Serial ATA 1.5/3/6 Gb/s

IEEE 802.3ae 10 Gb/s

Moreover, the transmitted data will be distorted when it passes the low pass frequency response channel and the distorted date will cause

intersymbol-interference (ISI). Fig. 1.1(a) illustrates phenomenon of ISI. When a nice short pulse is fed into a low pass frequency response channel the input pulse gets spread

out. If we change the input wave to two consecutive nice short pulses as in

1Reference: ”Universal Serial Bus Specification Revision 2.0, Mar. 2000.”, ”PCI Express

Base Specification Revision 10.a, 15 April 2003.”, ”Serial ATA II Electrical Specification Revi-sion 1.0, 26 May 2004.”, ”IEEE Std. 802.3ae: IEEE standard for 10Gbps Ethernet.”

Fig. 1.1(b), the final output wave is summation of the two spread out waveforms

as in Fig. 1.1(a). The waveform is not the same as input anymore and an error may occur.

(a)

(b)

Figure 1.1: An ISI phenomenon and error introduced by ISIa.(a) An impulse

and its response. (b) A series of impulse and their response.

aThis figure is imaged from the tutorial “Lecture #4 Communication Techniques:

Equal-ization & Modulation in Advanced Topics in Circiut Design: High-Speed Electrical Interface,” 2004 by Jared Zerbe.

1.2

Motivation

To compensate for the signal loss, some methods have been proposed in high

speed serial link. Either pre-emphasis in a transmitter [1], equalization in the receiver [2–7], or a combination of the two [8–10] is employed. The pre-emphasis

method solve the problem in transmitter side, the method has no information about the channel in the unidirectional system. Doing equalization in the receiver

side becomes the main solution to guarantee the correctness of the data in whole system.

In this thesis, the proposed equalizer based on continuous-time domain signal process can compensate severe channel loss at data rate of 6-Gb/s. The proposed

equalizer has a level-shifter in front of the equalization stage that is composed of two cascade stages. In time domain, the target of the proposed equalizer is to

open the amplitude of the data eye to±300 mV. The test chip was fabricated in UMC 1P9M 90nm 1.0V CMOS technology.

An analysis of equalizer based on discrete-time domain signal process is

also carried out. Based on proposed architectures [8], impact of several design parameters is analyzed and simulated by MATLAB.

1.3

Thesis Organization

The thesis is organized as follows:

Chapter 2 introduces the operation of equalizer in high-speed serial link ap-plication. After giving a brief overview, two categories of equalizer depending

on the domain of signal process will be introduced. The concepts of equaliza-tion operaequaliza-tion, advantages, challenge in design, and some previous arts for both

categories will be covered.

implementation details and simulation results are presented. Measurement and

equipment consideration for test chip are also discussed.

Chapter 4 shows the discrete-time domain equalizer. Algorithm and some previous arts will be introduced. Based on an existing architecture, analysis and

comparison about design scheme and parameters will be carried out in MATLAB simulations.

Chapter 2

Theory of Equalizer

2.1

Equalizers in High-Speed Application

In the multimedia era, size of source data is increasing dramatically to get high definition video or better audio quality. At the same time, high-speed

trans-mission for related application becomes more and more important to provide sufficient hardware ability. However, the physics characteristics of channels such

as wire between TV and DVD player, wire of earphone, introduce several negative impacts on the correctness of data. Therefore, we will give a brief introduction

about the factors that cause these negative impacts from physics point of view.

2.1.1

Physical Limitation of High-Speed Transmission

There are two main phenomena that will alter the characteristic of current

or voltage on conductors when we take frequency of current or voltage into con-sideration. One of the phenomena is skin effect that is mentioned in chapter 1,

the other phenomenon is dielectric loss. We will give a short introduction and explanation about these two roles and will get a whole picture of the relationship

between signal frequency and characteristics of channel.

The skin effect is the tendency of alternating electric current (AC current) to distribute itself within a conductor so that the current density near the surface of

the conductor is greater than that at its core. That is, the electric current tends to flow at the skin of the conductor. The way to measure the depth current flows

measure of the distance over which the current density falls to 1/e of its original

value.

Skin depth is a property of the material that varies with the frequency.

Skin depth is affected by the material relative permittivity, conductivity of the

material and frequency of the wave. First, we let the complex permittivity εc of

an material is

ε

c= ε(1

− j

σ

ωε

)

(2.1)

where:

ε: permittivity of the material of propagation

σ: electrical conductivity of the material of propagation ω: angular frequency of the wave

j: the imaginary unit

Thus, the propagation constant kcof the signal propagating on the conductor

will also be a complex number

k

c= ω

√

µε

c= ω

r

µε(1

−

jσ

ωε

)

(2.2)

where:

µ: permeability of the material

Before we get the final equation of skin depth, there is one more

simplifica-tion. For a good conductor, we can say that 1¿ εωσ . Therefore, the propagation constant in equation (2.2) can be simplified as

k

c=

p

jµωσ =

1 + j

√

2

p

2πf µσ = (1 + j)

p

πf µσ

(2.3)

then the above equation can be separated into real part, α, and imaginary part,

β,

k

c= α + jβ =

p

Now, assume a uniform wave, that can be voltage or current, propagating in

the +z-direction,

E

z= E

0e

jkcz= E

0e

jαze

−βz(2.5)

then β gives an exponential decay as z increases. For this reason β is also calledattenuation constant of a propagating wave. By the definition of skin depth, it

is the distance over which the current density decays to 1/e of its original value,

that is βz = 1. Therefore, the skin depth δ is

δ =

1

β

=

1

√

πf µσ

(2.6)

From equation (2.6) we can find that the skin depth decreases while the

signal frequency increases. That means the high frequency signal has less effective

cross area than the low frequency signal. Moreover, the effective resistance is

inverse proportion to effective area. So that high frequency signal will suffer more

effective resistance and will get more loss than low frequency signal will. Table

2.1 lists the skin depths of several types of materials at various frequencies [11]

Table 2.1: Skin depth of several material at various frequencies

Material f =60(Hz) 1(MHz) 1(GHz)

Silver 8.27(mm) 0.064(mm) 0.0020(mm)

Copper 8.53 0.066 0.0021

Gold 10.14 0.079 0.0025

Aluminum 10.92 0.084 0.0027

the wire. When an time-varying electric field passes to a material, the particles

in the material will be polarized. The polarization vector will change with the

varying of electric field. With the input field frequency increases, the internal

polarized charge cannot follow the varying of field in time and the polarized charge

becomes out of phase. This phenomenon leads to a frictional damping mechanism

that causes power loss and generates heat. We can model the phenomenon in the

imaginary part in a complex permittivity εc

ε

c= ε

0

− jε

00(F/m)

(2.7)

where both ε0 and ε00 can be functions of frequency. Here, we also define an

equivalent conductivity σ representing all loss

σ = ωε

00(S/m)

(2.8)

The ratio ε00/ε0 is called a loss tangent because it is a measure of the power loss in the medium:

tan δ

c=

ε

00ε

0∼

=

σ

ωε

(2.9)

The quantity δc in equation (2.9) is called the loss angle. We know that a medium

is say to be a good conductor if σÀ ωε, and a good insulator if ωε À σ. For an fix medium, ω and σ are almost constants. When the frequency of signal increases, the medium tends to be like an insulator. That means the signal suffers more

resistant force to pass the medium.

2.1.2

Equalizer and Compensation

An ideal channel should have uniform gain for any band of frequency. How-ever, from the previous introduction of physical characteristics of a channel we

The behavior of having much loss at high frequency than at low frequency is just

like a low pass filter. Therefore, we often model the channel frequency response as a low pass filter.

Equalization is a process to compensate or to make equal the frequency

response of the channel. This technique was first used by the Bell Labs for correcting audio transmission losses on the telephone system [12]. The block to

complete the equalization process is called equalizer.

An equalizer can be understood as an high pass filter. This filter has a trend of increasing gain in high frequency to compensate gain decreasing of the channel.

After adding equalizer between the channel and receiver, we hope the high pass response can just compensate the losses of channel at high frequency to flat or to

equal the total effective response. If we can not flat the response, at least we can make the band nearly flatten. Fig. 2.1 roughly illustrates the goal of equalizer.

Figure 2.1: Channel response and equalizer response

Fig. 2.2 shows the location of equalizers in a system. As mentioned in

chap-ter 1, we can put the compensation block in the transmitchap-ter side also called pre-emphasis or do the mechanism in the receiver side. No matter in transmitter

side or in receiver side, the goal is that the channel response plus the responses of the two compensation blocks can be almost flat at the target frequency.

Figure 2.2: Typical system view with equalizer

2.2

Concepts of Equalizers

Equalization is a kind of signal processing. The equalizer deals with the data received from the channel output and then transfers the equalized data to

the circuit after it. A common classification of equalizer are continuous-time equalizers [2,3] and discrete-time equalizers [8,13]. The basis of the classification

is the method of handling the received data. They do the equalization from different point of view. In this section, we will give a brief introduction of these

two categories.

2.2.1

Continuous-Time Equalizers

The continuous-time equalizers (CT-EQ) do equalization without the timing

information. The signal dealt with by continuous-time equalizer is not digitized. Therefore, the circuit belongs to analog domain. Due to the input data is

con-tinuous, we can understand the continuous-time equalizer from compensation in frequency domain just like the explanation in the previous section.

However, any circuit has poles and zeros itself. That means to reach infinite

high gain at the infinite high frequency is impossible. The frequency response of equalizer is never like what we plot in Fig. 2.1. Gain amount of frequency

response will fall after an limited frequency range.

frequency response to reach the equalization function. Fig. 2.3 illustrates the idea

of band-pass like frequency response. In this figure, we use piece-wise to sketch a roughly Bode plot.

Figure 2.3: Frequency Response of continuous-time equalizers

First, we assume that there is a zero at a relative low frequency in the equalizer circuit. By the rule of plotting Bode plot, we know that the frequency

response will increase in 20dB/dec when there is a zero. The value of gain starts to rise with the frequency increases until reaching frequency of the first pole.

Because a pole will let frequency response decrease in 20dB/dec, the effect of zero is canceled by the lowest frequency pole. As the frequency keep increasing,

the frequency will decrease dramatically due to dominate pole which is introduced by the circuit itself.

By such arrangement of poles and zeros, we can get a gain pulse in frequency

response. Therefore, to allocate the first pole and first zero at proper frequency can move the gain pulse to the band we focus on. Although the effective response

is not flat through the whole frequency, but the equalizer extends the flat part toward system data transmission frequency. In any data transmission system, the

we do not need to compensate the response at the frequency that exceeds the

frequency defined in the specification.

If the channel loss is severe, the response of equalizer will need a high gain pulse. One way is to suppress the low frequency gain while keeping the peak gain

value. This strategy do not make sense because the low frequency signal suffers too many attenuation. The other way is to push up the peak gain value while

keeping the low frequency gain. From Fig. 2.3 we can know that slope of rising response is a constant, +20dB/dec, if there is only one zero. Assume that the

numbers of pole and zero do not change. If we push the first pole toward high frequency, the rising trend will stop later. And the response of equalizer will get

a high gain pulse.

In summary, the advantage of continuous-time equalizers is having relative simple architecture. Therefore, they have small area and own a good equalization

ability. For a well-known and time-invariant channel, the architecture of fixed fre-quency of poles and zeros can provide a stable performance. On the contrary,

because continuous-time equalizers handle the equalization function in frequency domain, the adaptive solution is more difficult than discrete-time equalizer.

More-over, a little change in the location of poles and zeros due to process variation will affect total response dramatically.

2.2.2

Discrete-Time Equalizers

Discrete-time signal processing is for signals that are defined only at discrete points in time. The processing includes concept of timing index and the order

of data becomes a key parameter in operation. Discrete-time equalizer has the same idea of equalizing signal in discrete data points. This category of equalizers

handle their operation from the view of cancelling intersymbol-interference (ISI).

signal sequence is x(t), and the signal in the channel output, y(t), is y(t) =

x(t)∗ h(t). The data received at timing index n can be written as

y(n) = x(n)h(n) +

∞X

m=−∞ m6=0x(m)h(n

− m) = x(n)h(n) + ISI (2.10)

the ISI term is the sum of all the ISI contributed by past and future bits. Although an ideal pulse will be spread out causing ISI to the neighbor bits, the value of

spread out ISI data is not obvious for the timing index far from it. The equalizer just needs to cancel the ISI terms that are close to the current timing index.

A finite impulse response (FIR) filter can accomplish this operation. To cover the finite length of past data and future data, the dominate effect of ISI can be

removed. The equalizer output can get the data that is near equal to the original data in the transmitter side.

The discrete-time equalizer has a sampler to get discrete time data per

sam-ple period. After the samsam-pler samsam-ples the data from the channel output, the discrete data will be passed to the later stage of circuit. Due to the data is

discrete, the implementation of the later stage of circuit can be implemented in digital or in analog. Fig. 2.4 shows the circuit architecture of two types of circuit.

The discrete-time digital equalizer (Digital-EQ) shown in Fig. 2.4(a) is also

called the digital equalizer. It owns a analog-to-digital converter (ADC) to digitize the analog signal. But when a transmission system needs high resolution and

operates at high frequency, the design of ADC will face a huge challenge. On the other hands, the discrete-time analog equalizer [13,14] (DT-EQ) shown in

Fig. 2.4(b) will be a proper solution in the high speed application.

To make the sampler work properly, discrete-time equalizer needs an accurate clock to provide correct sampling. The clock source will need the cooperation

of clock and data recovery (CDR) circuit. In the total system consideration, the CDR circuit must operate on the raw data first. Another issue about the

(a)

(b)

Figure 2.4: Two types of discrete-time equalizers, z−1 is the register. (a)

Discrete-time digital equalizer. (b) Discrete-time analog equalizer.

of equalization will be reduced. Because discrete-time signal processing is for

signals that are defined only at discrete points in time, we can arrange these data to separated data paths without losing any information. By paralleling several

data path, the circuit can slow down its operation frequency. With the increase of data rate, this is really a good news for equalizer design.

Table 2.2: Characteristics of CT-EQ, DT-EQ and Digital-EQ

Type of Equalizer Characteristics

CT-EQ

• Simple architecture

• Adaptive method is quite difficult • Fixed pole and zero location

DT-EQ

• Clock recovery is necessary • Easy for adaptation

Digital-EQ

• Circuit is all digital • Easy for adaptation

• High resolution and speed ADC is required • Large area and power

2.3

Traditional algorithm of discrete-time

Equal-izer

In this section, we introduce two traditional equalization algorithms, zero

forcing algorithm and minimum mean-square error (MMSE) algorithm. The zero forcing algorithm is a straight forward method. However there is usually some

drawback for straight forward strategy. We will give a precise introduction about a solution that can improve the equalization performance.

2.3.1

Zero Forcing Algorithm

The zero forcing algorithm is to remove ISI completely, that is to force the

ISI to zero. In the frequency domain, the meaning is to allocate an equalizer that

has the response that is the reciprocal of channel response. We can write the

equation as

E(z) =

1

H(z)

(2.11)

where E(z) is the frequency of equalizer, H(z) is the frequency response of chan-nel.

The zero forcing equalizer inverse the channel response to remove all ISI,

and is ideal when the channel is noiseless. However, when the channel is noisy, the zero forcing equalizer may amplify the noise greatly. Fig. 2.51 illustrates the

idea of amplifying the noise.

Figure 2.5: Noise enhancement in zero forcing equalizer

The figure shows a situation that channel response has a deep notch at a

frequency. By the zero forcing algorithm, the equalizer response is reciprocal of the channel response. Therefore, the deep notch in the channel response becomes

a sharp pulse in the equalizer response. The noise in the channel is usually model as a noise source introduced in the output of channel and as white response. The

noise which is not filtered by the channel will be amplified greatly by the pulse of

the equalizer response, and is not white anymore. The noise is colored, and we

call this phenomenon as noise enhancement.

The main reason of noise enhancement is we only inverse the channel response without considering the situation that the channel has large gain difference in the

response. If we want to improve the drawback of noise enhancement, we need to get the other criterion to measure the performance of equalization.

2.3.2

Mean-Square Error Algorithm

The purpose of equalizer in a transmission system is to minimize the

differ-ence between the received data and the original data. The minimum mean-square

error equalizer does not usually eliminate ISI completely but instead minimizes

the following criterion

E(

|c

k− ˆc

k|)

(2.12)

where ckis the data in front of the decision, ˆckis the data in the output of decision

block, E() means expectation. This idea is from statistics. If we treat the data in the equalizer output, ˆck, as an estimator of original data, ck, the mean square

error (MSE) of the estimator is a way to quantify the amount of differs from original data and estimator as defined in equation (2.12).

By the criterion, we can derive the equalizer response as [15]

E(z) =

H

∗

(z

−1)

H(z)H

∗(z

−1) + N

0(2.13)

where E(z) is the equalizer response, H(z) is the channel response, H∗(z−1) is conjugate of channel response, and N0is the channel noise. Fig. 2.62 gives a simple

example of MSE equalizer. When channel also has a deep notch in response, the

MSE equalizer gives up removing the loss completely. It responds to the deep

notch and takes the effect of noise at the same time. In sum, the MSE equalizer

tries to the balance between noise enhancement and ISI cancellation.

Figure 2.6: Noise enhancement is reduced by MSE

2.4

General Topology of Equalization

In this section, we will introduce two common topologies of equalization,

lin-ear equalization (LE) and decision feedback equalization (DFE). The first topol-ogy equalizes the data in the channel output and feeds the equalized data to later

stage directly. The second topology, however, will feedback the equalized data as

an information for equalization of later data.

2.4.1

Linear Equalization

In Fig. 2.7(a) the basic structure of a linear equalizer is shown. The received data sequence rk is the original data sequence ck filtered by the channel H(z)

and adding noise nk. Then the received data sequence is applied to the equalizer

input. The amount of error ek is defined as the difference between the output

of the equalizer and output of the decision block. If the equalizer can recover the distorted data, the data in the decision block output should equal with the

original data sequence ck. The definition of error is the same as what mentioned

(a)

(b)

Figure 2.7: (a) Basic block diagram of a linear equalizer. (b) Equivalent block

diagram of linear equalizer [16].

The structure in Fig. 2.7(a) is equivalent to the structure in Fig. 2.7(b) under

the assumption that the equalizer recover the data completely and the data in

the decision block output is equal to the original data sequence. The equivalent

relationship can be derived as follows:

e

k= E(z)[c

kH(z) + n

k]

− ˆc

k= c

kH(z)E(z)

− ˆc

k+ n

kE(z) (2.14)

Assume, the decision is correct ˆck = ck, then we will get

e

k= c

k[H(Z)E(Z)

− 1] + n

kE(z)

(2.15)

The structure in Fig. 2.7(b) emphasis the contribution to the error signal. One is the ISI contributed by other bits and the filtered noise.

2.4.2

Decision Feedback Equalization

The decision feedback equalization (DFE) [17] makes use of the regenerative

the LE basically, and we use Fig. 2.8(a) to explain the scheme. If we add an

additional linear prediction block after the output of Fig. 2.7(b) to filter the correlated error ek. We get a new error ˜ek that has always a lower variance

compared to ek due to the properties of a linear predictor [16]. In other words,

the linear predictor remove all predictable information resulting in white output

noise.

(a)

(b)

Figure 2.8: (a) Equivalent block diagram of DFE. (b) Basic block diagram of a

DFE [16].

An equivalent structure is shown in Fig. 2.8(b), we can also prove the two

structures are equivalent. From Fig. 2.8(a), we can write the new error ˜ek as

˜

e

k= e

kC(z) = E(z)C(z)[c

kH(z) + n

k]

− ˆc

kC(z)

(2.16)

if we add ˆck− ˆck in the right side of the above equation, we will get ˜ek as

˜

e

k= E(z)C(z)[c

kH(z) + n

k]

− ˆc

k[C(z)

− 1] − ˆc

k(2.17)

The block diagram in Fig. 2.8(b) equals to what equation (2.17) describes. There-fore, we can say that the DFE is an enhancement of LE under the assumption of

Chapter 3

Continuous-Time Equalizer

In this chapter, we will put emphasis on the linear continuous-time analog

equalizer. In Section 3.1 we will give an overview of several previous works of continuous-time equalizer [2,3,10]. The proposed architecture is shown in Section

3.2. The detail of circuit implementation and simulation results are given in Sec-tion 3.3. Finally, SecSec-tion 3.5 will show the plan of measurement and verificaSec-tion

of our test chip.

3.1

Overview

We can model the equalizer stage as shown in Fig. 3.1 [2,10]. The

equiv-alent model has two signal paths: one is the unity-gain path with gain, α, and high-frequency-boosting path with gain, β. The high-frequency loss of the

chan-nels compensated by the high-frequency-boosting path, while the unity-gain path guarantees the low-frequency gain. So that the overall loss becomes the same for

all frequencies.

Figure 3.1: Equivalent model of continuous-time equalizer

However, when we design the gain for unity-gain path, the gain value will

dependence of the two paths to relax the design consideration or to provide more

flexibility for adaptation design is an issue that we shall deal with.

With the data rate increases, the operation frequency of equalizer also needs to push up. In this chapter, we will try to propose an equalizer system that can

compensate severe channel loss.

3.2

Motivation and the proposed architecture

In the model shown in Fig. 3.1, there is a high pass filter in the

high-pass-boosting path while the unity-gain path has gain block only. The gain block in the unity-gain path will also affect the high-frequency gain. In an analog design,

all the design factors in one block will affect each other. That means there are at least two parameters that can decide the high-frequency gain at the same time.

In other words, the low-frequency gain controlled by unity-gain path will affect with high-frequency gain.

A way to minimize the dependence is to move the gain block of unity-gain

path out of the equalizer as shown in Fig. 3.2. The moved out block is series connection with the equalizer. In this way, the two kinds of gain are covered by

two different blocks. The gain block in front of the equalizer determines the low-frequency gain, and the equalization stage boosts high-low-frequency gain. Although

the response of any gain stage may cover a wide frequency range, a gain stage only owns good performance at a particular frequency band. By using two gain

blocks, we can take the amplification consideration separately.

On the other hands, the characteristics of equalizer such as frequencies of

poles and zeros will be influenced by DC voltage level variation at the channel output if the equalizer stage is connected to the channel directly. By allocating a

level-adjusting block between the equalizer stage and channel output, the effect may be eased, even be released.

Fig. 3.3 shows the block diagram of our proposed equalizer. The differential

incoming signals attenuated through the wire are terminated using 50-Ω on-chip resisters. The received signal is amplified and shifted to a DC signal level by the

level-shifter. Two cascade equalization stages are in the same common-source like topology. Then the buffer amplifies the equalized signal amplitude to the

standard defined in the specification. All the blocks are fully-differential to reject common-mode noise.

Figure 3.3: Block diagram of our proposed equalizer

Finally, the specification of the proposed equalizer is listed in Table 3.1

Table 3.1: Specification of proposed equalizer

Data Rate 6 GHz

Amplitude of transmitted signal

±300 mV

3.3

Circuit design and simulation results

This section includes the details of circuit implementation and shows the

simulation results of each block and total system. The test chip is fabricated with UMC 90 nm 1P9M 1V regular-Vt technology.

3.3.1

Level-Shifter

As mentioned in Section 3.2, the equalizer stage will suffer a great effect when

the DC voltage level in the equalizer input is not stable. Therefore, the proposed design adds a level-shifter between the equalization stage and channel output.

Moreover, the supply voltage of our used technology is 1 V, and the margin for signal swing is limited. Therefore, we need a circiut confine the DC voltage level

at equalizer input to a proper region. And the signal can have enough room to swing.

Fig. 3.4 shows the circuit diagram of level-shifter. In order to guarantee the

level-shifter can ease the DC voltage level variation in equalizer input, we use poly resister that has more stable impedance characteristics than active load. If we do

not add this level-shifter stage in front of equalizer stage, the ratio of DC voltage level variation in the equalizer stage input to the one in the channel output is

one. The design goal of level-shifter is to reduce the ratio as small as possible. The ideal value is zero, of course, because that means the DC level variation in

the channel output has no effect on the DC voltage level anymore.

The level-shifter circuit use fully-differentail architecture to reject the common-mode noise. M3 and M4 work as the current source. The widths of these two

current source MOS are designed large enough to decrease the effective resis-tance and increase the stability of the current. The bias voltage Vbn is supplied

by off-chip voltage source, and we choose the bias voltage as 0.3 mV. By the specification of our proposed design, the amplitude of the transmitted signal is

±300 mV in differential. That is ±150 mV swing in single end signal. Therefore,

we will bias the output higher than 0.5 V to provide larger swing margin. The resistance of two load resisters are chosen by biasing the DC output voltage of

level-shifter at 0.6 V. This level can provide some voltage margin for the later two equalization stage.

Typically, the DC voltage level for a signal that has ±150 mV is chosen at 0.85 V. So that the voltage range of the signal is from 0.7 V to 1 V. After attenuation of channel, the DC voltage level in the channel output will be different

with the DC voltage level in the channel input. Therefore, the level-shifter needs to have a flat curve for the relationship of output DC voltage level and input DC

voltage level when the input DC voltage is greater than 0.5 V or 0.6 V. In this way, the level-shifter can work properly for a certain range of DC voltage level of

channel output.

Figure 3.4: Circuit diagram of level-shifter

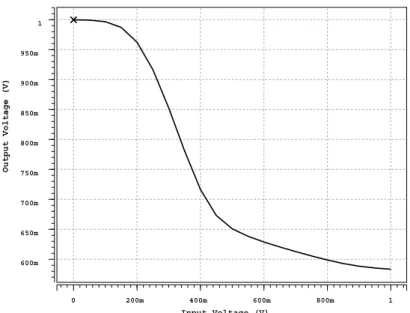

Now, we sweep the DC voltage level in the level-shifter input, plot the curve of DC voltage level in level-shifter output versus DC voltage level in level-shifter

in-put DC voltage is greater than about 500mV, the slope the curve is decreasing

dramatically. To estimate the slope of the segment:

slope ∼= 583.3(mV )− 650.8(mV )

1(V )− 500(mV ) =−0.135

We reduce the output variation to ten percent of the input variation. From the results, the uncertain variable of DC voltage level variation in the channel output

is almost removed by the block of level-shifter.

O u t p u t V o l t a g e ( V ) 600m 650m 700m 750m 800m 850m 900m 950m 1 Input Voltage (V) 0 200m 400m 600m 800m 1

Figure 3.5: Relationship between output and input DC voltage of the

level-shifter.

Beside easing the DC voltage variation, the level-shifter also has the function to guarantee a basic low-frequency gain in total system. In the introduction of

the proposed architecture in Section 3.2, we move the function of low-frequency amplification to the front of equalizer stage. We merge the amplification function

into the level-shifter. Fig. 3.6 shows the frequency reponse in the channel output and in the level-shifter output. After the amplification of level-shifter, the

low-frequency gain at level-sifter output is about 10 dB. The channel bandwidth (the -3 dB frequency) is at about 300 MHz. In the output of level-shifter, the

G ai n (d B) -60 -40 -20 0 10M 100M 1G 10G

Frequency (log) (HERTZ) Response after level-shifter

Channel Response

Figure 3.6: Channel response and response after level-shifter

The level-shifter does not extends the bandwidth to the clock frequency

3GHz, but the level-shifter also provides some gain at 3GHz. The level-shifter almost lifts all the response up under about 7GHz. That means the level-shifter

somehow provides some gain to help the equalizer minimizing the gain loss in the response.

3.3.2

Equalizer stage

Analog equalizers as introduction in 2.2.1, they do equalization operation by

allocating a zero in the low frequency to produce a gain pulse in the frequency response. The equalization filter in our equalizer stage use the topology that

introduces a zero in the source terminal of common-source amplifier as shown in Fig. 3.7 [3].

M1 and M2 are as the active load in the circuit. M3 and M4 play the main

roles for the function of amplification. M5 and M6 are the current source part. The resister Rm and capacitor C are the key elements to introduce the zero.

Figure 3.7: Circuit diagram of one equalizer stage

We will derive the transfer function of this equalizer stage by using the half circuit scheme. The first part is to find the effective ground point in the circuit.

We assume the characteristics of M1, M3, and M5 are the same with M2, M4, and M6. We model the current source as two resistors with ro of the two transistors,

and model the active load, M1 and M2 as two simple resistor load, Rp. The

circuit diagram is shown in Fig. 3.8(a).

Under the assumption of previous paragraph, the resistance of ro5 and ro6

should be the same. This means the source voltage of M3 and M4 are the same,

too. Then, the circuit can be further simplified as shown Fig. 3.8(b). We let the

current in the differential small-signal equivalent circuit is i, the following can be

derived

i = (v

in− v

s3)

· gm

3=

−(v

in#− v

s4)

· gm

4⇒ (v

in+ v

in#) = (v

s3+ v

s4)

∵ gm

3= gm

4The equation vs3 =−vs4 says that the voltage in the two sides of the resistor and

capacitor is sysmetric to zero as shown in Fig. 3.8(b). If we split the resister into two serial segments which have the same resistance, the voltage in the middle

point, G, of the two segments is equivalent ground point. The same manner can also be applied to the capacitor as shown in Fig. 3.8(c).

Finally, we can get the half circuit of the equalizer stage as shown in Fig. 3.9.

Based on the half circuit, the transfer function is derived as follow:

v

out#v

in=

−gm

3·

R

p Rm 2//

1 s·2C=

−gm

3·

2R

pR

m· (1 + sCR

m)

(3.1)

where Rp is the effective resistance of M1. From the tranfer equation, we can find

there is a zero that is used to produce the gain pulse in the frequency response.

The final version of the equalization stage is shown in Fig. 3.10. We replace the resistor, Rm, with a NMOS which gate is connected to VDD. Moreover, in

order to improve the PMOS ability of pulling the output voltage up, each PMOS for active load is shunt with another PMOS which gate is connected to the input

respectively as a negative resistor. The bias voltage of current source part uses the same source as the level-shifter uses.

The equalizer block is composed of two cascade stages. The margin of

in-creasing frequency between the first zero and the first pole is limited. So, we usually surpress a little low-frequency gain to get a sharp gain pulse in the

fre-quency response. If there is only one stage, the low-frefre-quency gain will be surpress too low while pushing the gain pulse. If we use two cascade stages, we can get a

sharp gain pulse in the final output while surpressing the low-frequency gain as less as possible.

Fig. 3.11 shows the frequency response of the two equalization stages and

the total frequency response. Because the two stages suffer different input and output loading, the two stage will have different zeros and poles frequency. In

(a) (b)

(c)

Figure 3.8: Small signal circuit of equalizer. (a) Simplified equivalent

small-signal model. (b) Further simplified equivalent small-small-signal model. (c) Virtual

ground in equivalent small-signal model.

the stage has a real zero at about 1.95 GHz and a pair of complex zero at about

2.6 GHz. On the other hand, the first stage has two pair of complex poles at about 1.41 GHz and 2.96 GHz. There is also a real pole at 2.39 GHz. Therefore,

we can observe that the frequency response of first equalization stage decreases dramatically after the gain peak frequency.

In the second equalization stage, the frequencies of first two zeros are at

about 790 MHz and 3.89 GHz. While the frequencies of first two poles are at about 2 GHz and 3.9 GHz. The second stage owns the first pole and the first

Figure 3.9: Half circuit of equalizers.

Figure 3.10: Final circuit of equalization stage

zero at the frequency higher than the first stage owns. We push the gain pulse

of the second stage to higher frequency than the gain pulse of the first stage. Moreover, by minimizing the gate capacitance of the first buffer stage, loading

in the output of the second equalization stage is dominated by the stage itself. We can push the frequency of poles to higher frequency. So that the trend of

G ai n (d B) -6 -4 -2 0 2 4 6 8

Frequency (log) (HERTZ)

10M 100M 1G 10G

Second stage

Total response First stage

Figure 3.11: Frequency dependence of gain in each equalization stage and total

response.

stage. These two methods let the second stage provide more compensation ability

at high frequency than the first stage provides as shown in Fig. 3.11.

In Fig. 3.11 we can also find that the equalizer contributes nagative gain value under the frequency about 400 MHz. As our architecture decribed in Section 3.2,

the low-frequency gain is dominated by the level-shifter stage. The equalizer introduces the gain boosting in high frequency, and the low-frequency gain will

be provided by the level-shifter. Fig. 3.12 shows the response of the equalizer stage and the total response of level-shifter and equalizer stage. The level-shifter

amplifies the low-frequency gain about 9.5 dB, and the effect of amplification also extend to the frequency of gain pulse. On the other words, the level-shifter not

only provides the gain in low frequency but also contributes amplification in high frequency. However, the difference between equalizers and amplifiers is that the

signal without any correction mechanism. The level-shifter just lifts the response

up through a limited frequency, it can not extend the flatten response towards high frequency. The gain pulse used to flat the response is still provieded by the

equalizer stage. G ai n (d B) -6 -4 -2 0 2 4 6 8 10 12 14 16

Frequency (log) (HERTZ)

10M 100M 1G 10G

Response of level-shifter & EQ

Response of EQ

Figure 3.12: Response of equalizer stage and combination of level-shifter and

equalizer.

The final frequency response in the equalizer output is shown in Fig. 3.13.

Our proposed equalizer is under the 6GHz system. The clock rate is 3GHz. In Fig. 3.13, the channel response is -25.35dB at 3GHz. After compensation by

our equalizer, the response at 3GHz is -11.48dB. The proposed equalizer recovers 13.87dB channel loss.

In Fig. 3.14, we show the group delay in the equalizer output. We know

that the group delay is the differential of the phase response. Therefore, for a linear phase response system, the group delay should be a constant. In Fig. 3.14

G ai n (d B) -80 -70 -60 -50 -40 -30 -20 -10 0 10

Frequency (log) (HERTZ)

10M 100M 1G 10G

Response at EQ output Channel response

Figure 3.13: Frequency response of channel output and equalizer output.

is almost a constant. That means the proposed equalizer does not introduce too much phase distortion.

However, the signal is used in time domain for system application. The effect

of equalization can not be measured just in the frequency domain. Therefore, the performance in the time domain is most important because the meaning of

equalizer is to corrent the signal distorted in the channel. The goal of our equalizer in time domain is to open the data amplitude to±300mV. The specification of the proposed system is to transmit data with±300mV, so that we need to recover the received data amplitude amplitude as much as possible. If the signal amplitude

can not reach ±300mV, the buffer stage will amplify the signal to the goal.The signal in the output of equalizer stage is been equalized, even if the amplitude do

not reach the specification. The buffer stage just amplifies the equalized signal amplitude to meet the requirment in specification.

G rou p D el ay (S ec ) -100n -80n -60n -40n -20n 0 20n 40n

Frequency (log) (HERTZ)

10x 100x 1g 10g

Figure 3.14: Group delay in the equalizer output

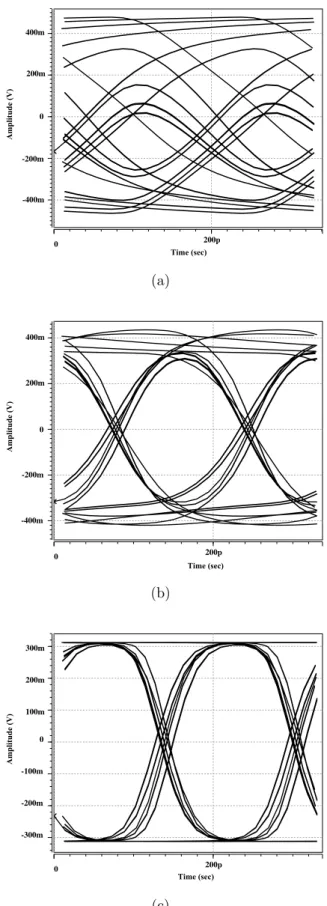

We change the length of the channel model to get about the -25dB channel loss at the clock frequency 3GHz under 6GHz data rate. Base on this channel model,

we apply psuedorandom bit sequence (PRBS) pattern to the channel input and observe the eye diagram of three points: channel output, equalizer output, and

buffer output. The PRBS pattern is set to have ±300 mV swing with 6 Gbps and the length of the PRBS pattern is 1000 bits. Fig. 3.15 shows the eye diagram

of pre-layout simulation. Fig. 3.15(a) shows the diagram of channel output. Due to the channel loss, the signal is hard to be distinguished. Fig. 3.15(b) shows

that the equalizer opens the data eye to about ±280 mV. The peak-to-peak jitter of the eye at the equalizer output is 22.85 ps and the RMS jitter is 7.47

ps, and the jitter histogram is shown in Fig. 3.16(a). The equalized signal is further amplified by buffer stage to±300 mV swing, as shown in Fig. 3.15(c). At buffer output, the data eye has peak-to-peak jitter of 22.96 ps and RMS jitter is 7.51 ps, and the jitter histogram is shown in Fig. 3.16(b). The buffer stage

buffer is also to push the loadings including bounding line and connectors in the

measurement environment. If we just need to amplify and shape the output eye to the specification, we do not need to design such a buffer stage that with large

A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (a) A mp li tu d e (V ) -400m -200m 0 400m Time (sec) 0 200p 200m (b) A mp li tu d e (V ) -300m -200m -100m 0 100m 200m 300m Time (sec) 0 200p (c)

Figure 3.15: Eye diagram of pre-layout simulation: (a) channel output. (b)

(a)

(b)

Figure 3.16: Jitter histogram of pre-layout simulation: (a) equalizer output.

3.4

Implementation and layout

The layout of proposed design is based on UMC 90 nm 1P9M 1 V

techonol-ogy. In order to minimize the the parasitical effect, we try to reduce the distance betweeen level-shifter block and equalizer block. Therefore, the interconnection

between these two blocks can be minimized. On the other hands, the routing of differential signal line takes the length of line into consideration. We try to

minimize the difference between two line length in a pair of differential signal line. So that the time of differential signal traveling on the line can be almost the same

to minimize the time skew issue. In each block, the circuit is fully differential. We also use parallel MOS to minimize the effect of process variation.

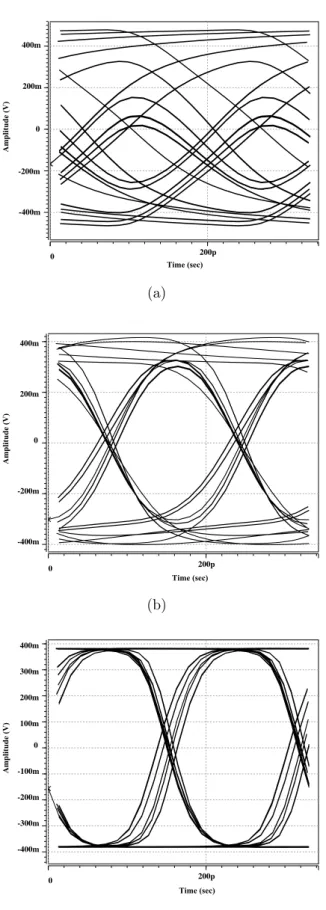

Fig. 3.17 shows the eye diagram of the post-layout simulation in three points: channel output, equalizer output, and buffer output. Comparing with the

pre-layout simulation, the eye diagram in the equalizer output is small in the post layout simulation. The eye open is about±250 mV in the post-layout simulation as shown in Fig. 3.17(b). The peak-to-peak jitter of data eye is 25.53 ps, the RMS jitter is 8.89 ps and the jitter histogram is shown in Fig. 3.18(a). We can

not avoiding the effect of parasitical elements although we try to minimize these in the layout. Fig. 3.17(c) shows the post-layout eye diagram of buffer output.

In the buffer output, the data eye can open to ±300 mV with peak-to-peak jitter of 26.71 ps, the RMS jitter is 8.94 ps, and the jitter histogram is shown in Fig. 3.18(b).

All the simulation results above is based on the TT corner condition. The simulation based on FF and SS corn conditions are shown in Fig. 3.19 and

Fig. 3.20. We can find that the eye diagram in the equalizer output still can open the data eye to at least ±200 mV, but the buffer stage that drives the output loading perform not well in FF and SS corner conditions.

A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (a) A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (b) A mp li tu d e (V ) -400m -300m -200m -100m 0 100m 200m 300m 400m Time (sec) 0 200p (c)

Figure 3.17: Eye diagram of post-layout simulation under TT corner condition:

(a)

(b)

Figure 3.18: Jitter histogram of post-layout simulation under TT corner

A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (a) A mp li tu d e (V ) -300m -200m -100m 0 100m 200m 300m Time (sec) 0 200p (b) A mp li tu d e (V ) -600m -400m -200m 0 200m 400m Time (sec) 0 200p (c)

Figure 3.19: Eye diagram of post-layout simulation under FF corner condition:

A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (a) A mp li tu d e (V ) -400m -200m 0 200m 400m Time (sec) 0 200p (b) A mp li tu d e (V ) -250m -200m -150m -100m -50m 0 50m 100m 150m 200m 250m Time (sec) 0 200p (c)

Figure 3.20: Eye diagram of post-layout simulation under SS corner condition: