國

立

交

通

大

學

電機學院 電子與光電學程

碩

士

論

文

9−25GHz 寬頻 COMS LNA 設計

9−25GHz Wideband CMOS LNA Design

研 究 生:洪祺源

指導教授:胡樹一 教授

9−25GHz 寬頻 COMS LNA

9−25GHz Wideband CMOS LNA Design

研 究 生:洪祺源 Student:Darren (Qi-Yuan) Horng 指導教授:胡樹一 Advisor:Robert (Shu-I) Hu

國 立 交 通 大 學

電機學院 電子與光電學程

碩 士 論 文

A Thesis

Submitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in

Electronics and Electro-Optical Engineering August 2008

Hsinchu, Taiwan, Republic of China

9−25GHz 寬頻 CMOS LNA 設計 學生:洪祺源 指導教授:胡樹一 國 立 交 通 大 學 電 機 學 院 電 子 與 光 電 學 程 碩 士 班 摘 要 本論文研製之主要目的是想要利用 0.18um RF-CMOS 製程,來達成 9− 25GHz 寬頻 LNA 的應用,因為目前 0.18um CMOS 製程的寬頻 LNA,大都 為 3− 10GHz 的設計,相對於目前所發表的論文,0.18um 製程的窄頻 LNA 操作 頻率已能達到 24GHz。所以本專題目的就是使用便宜的 0.18um CMOS 製程去 設計一個能操作在 Ka 頻段的寬頻 LNA。

此電路設計是期望能利用 L 和 R-C 匹配方式,來達到寛頻及相對低的雜訊 指數,並把它實現應用在 nMOS 0.18um 的製程上,在 CIC 量測的結果顯示, S21 可以達到 10-16dB 的增益,在9GHz 的雜訊指數約為 4.5dB。當操作的 Vdd 範圍在 1.2− 2.0 伏特時,功率消耗為 58−111mW。此晶片的大小為 0.945 x 1.295 mm²。

9−25GHz Wideband CMOS LNA Design

Student:Qi-Yuan Horng Advisors:Dr. Shu-I Hu

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

ABSTRACT

A procedure is to introduce a 9−25GHz wide band LAN design which uses 0.18um RF-CMOS technology. In general, the 0.18um CMOS LNA usually be designed for 3−10GHz operating range. Otherwise, the narrowband LNA design already is proved that it could work at 24GHz. So, we would like to design a LNA and it can work at Ka band.

The CIC measured result shows LNA S21 has 10-16dB gain and it has 4.5dB noise figure when operate at 9GHz, with 58−111mW power consumption for Vdd ranging from 1.2−2.0V. The chip size is 0.945 x 1.295mm².

誌

謝

學生首先要謝謝家人的支持,讓學生能夠在工作和學業上同時兼顧。對 於胡教授的耐心指導和幫助,學生一直感激在心,感謝教授讓學生在 LNA 和積體電路設計等多方面,得到許多的啓蒙,亦讓學生能夠對微波領域有 著更進一步的了解。除此之外,學生也要向羅斯允同學說聲謝謝,他在電 路設計及程式應用方面,給予學生極大的幫助。還有林麗卿同學,提供我 許多研究所相關的經驗。最後還要感謝我的母校-交通大學,提供我們如此 完善的學習空間及環境。

目

錄

中文提要 9−25GHz 寬頻 CMOS LNA 設計 i

英文提要 9−25GHz Wideband CMOS LNA Design ii

誌謝 ……… iii 目錄 論文結構 iv 表目錄 表 1~表 12 v 圖目錄 圖 1~圖 80 vi 一、 緒論 1 二、 工作原理 8 三、 實驗結果 52 四、 結論 55 參考文獻 ……… 57 自傳 ……… 59

表目錄 表 1 通訊應用頻段………6 表 2 模擬結果………17 表 3 模擬結果………31 表 4 製程飄移之模擬結果………41 表 5 製程飄移之模擬結果………43 表 6 電容製程變異之模擬結果………45 表 7 電容製程變異之模擬結果………47 表 8 溫度變異之模擬結果………48 表 9 相關研究結果比較………49 表 10 不同 VDD 偏壓點之性能比較………49 表 11 預計規格表 (1.4V)……… ………50 表 12 預計規格表 (2.0V)……… ………51

圖目錄

圖 1 Arecibo radio telescope ………1

圖 2 Arecibo radio telescope ………1

圖 3 SKA 示意圖………2

圖 4 未 來 太 空 通 訊 架 構 ………6

圖 5 利 用 LFB, RFB 和 CFB 達 到 匹 配 ………8

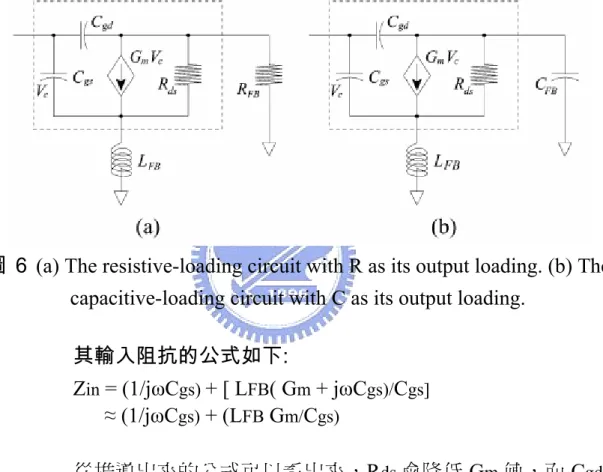

圖 6 Output loading circuit………9

圖 7 The circuit’s input impedance………10

圖 8 First stage circuit………11

圖 9 原始電路……….11 圖 10 設計流程圖………12 圖 11 信號反饋考量………14 圖 12 穩定參數………..………14 圖 13 第 一 版 電 路 ………15 圖 14 S11 參數……….…15 圖 15 S22 參數………16 圖 16 S21 參數………16 圖 17 S12 參數………16 圖 18 Smith chart………17 圖 19 Noise Figure 模擬………17 圖 20 第一版 Layout 的完成圖………18 圖 21 Momentum 模擬電感 S 參數………19 圖 22 Y 參數 Deembedding………19 圖 23 Deembedding 示意圖………20 圖 24 考量 layout 線段之電路圖………20 圖 25 S 參數模擬結果………21 圖 26 Layout 的 grounding 層………22 圖 27 Vd power trace ………23 圖 28 第二版電路………23 圖 29 S11 參數………24 圖 30 S22 參數………24 圖 31 S21 參數………25 圖 32 S12 參數………25 圖 33 Smith chart ………25 圖 34 Noise Figure 模擬………26 圖 35 S11 參數………26

圖 36 S22 參數………26 圖 37 S21 參數………27 圖 38 S12 參數………27 圖 39 Smith chart ………27 圖 40 Noise Figure 模擬………28 圖 41 穩定參數………28

圖 42 第一級 Inter-stage stability analysis ………29

圖 43 第二級 Inter-stage stability analysis ………29

圖 44 第三級 Inter-stage stability analysis ………30

圖 45 第四級 Inter-stage stability analysis ………30

圖 46 第五級 Inter-stage stability analysis ………30

圖 47 考量 layout 線段之電路圖………31 圖 48 S11 參數………32 圖 49 S22 參數………32 圖 50 S21 參數………33 圖 51 S12 參數………33 圖 52 Smith chart ………34 圖 53 Noise Figure 模擬………34 圖 54 S11 參數………35 圖 55 S22 參數………35 圖 56 S21 參數………36 圖 57 S12 參數………36 圖 58 Smith chart ………37 圖 59 Noise Figure 模擬………37 圖 60 製程飄移之模擬結果 F/F………38 圖 61 製程飄移之模擬結果 S/S………39 圖 62 製程飄移之模擬結果 F/S………39 圖 63 製程飄移之模擬結果 S/F………40 圖 64 製程飄移之模擬結果 F/F………41 圖 65 製程飄移之模擬結果 S/S………42 圖 66 製程飄移之模擬結果 F/S………42 圖 67 製程飄移之模擬結果 S/F………43 圖 68 電容製程變異的影響 F/F ………44 圖 69 電容製程變異的影響 S/S ………45 圖 70 電容製程變異的影響 F/F ………46 圖 71 電容製程變異的影響 S/F ………46 圖 72 溫度變異的影響………47 圖 73 溫度變異的影響………48

圖 74 探針示意圖………52

圖 75 Circuit Layout and Photo………53

圖 76 S 參數量測結果………53

圖 77 IP1dB 量測結果………54

圖 78 Noise Figure 量測結果………54

圖 79 Revision on Drain Bias Isolation ………55

一、緒 論 在我們日常生活中,我們雖然看不見微波,但它卻影響我們十分 深遠,它的應用廣泛,而且無所不在。 在天文方面, 像是天文望遠鏡中,也是不乏微波上的應用。 許 多好萊塢電影,像是「接觸未來(Contact)」、「黃金眼(Goldeneye)」 等膾炙人口的電影,其取景的地點就是位在中美洲波多黎各的阿雷西 波電波望遠鏡(Arecibo radio telescope),如圖 1 及圖 2。它是全世 界最大的單一碟面望遠鏡,其直徑高達 305 公尺,涵蓋的面積更是高 達 7 萬平方公尺,在在波霎(pulsar,中子星)和外星生命搜尋方面 等研究有著卓越的貢獻。 然而,單一碟面式的望遠鏡在直徑涵蓋面積及建造成本上,有著 相對的限制,故在美國的地面天文學計畫中,新望遠鏡所需的經費逐 漸佔去舊望遠鏡的預算,像是設立於智利的 ALMA 毫米波陣列計畫 (Atacama Large Millimeter Array)就耗資 NSF 約 5 億美金的預算, 而另一個跨國合作的平方公里陣列(Square Kilometre Array,SKA) 經費,更是多達 10 億美金以上。

圖 1 Arecibo radio telescope 圖 2 Arecibo radio telescope

(The Canberra Time)刋載,未來 SKA 將由近兩百個無線電台共同建 構,其涵蓋範圍可以超過三千公里,若此天文望遠鏡一旦完成,將有 助於天文學家尋找類地行星(Earth-like planets)與成千上萬的脈衝星 (pulsars)、磁場形成研究、探究宇宙自大爆炸以來的歷史及黑洞的秘 密。 另 一 方 面,歐 洲 航 太 總 署( ESA)已 經 決 定 資 助 全 世 界 最

大 的 望 遠 鏡 --平 方 公 里 陣 列( Square Kilometer Array,SKA) 的 設 計 與 建 造 ,參考圖 3 (SKA 示意圖)。 其 涵 蓋 了 一 百 萬 平 方 公 尺 的 面 積,相 當 於 200 座 足 球 場 , 成 為 全 世 界 最 大 的 電 波 望 遠 鏡。 圖 3 SKA 示意圖 SKA 的 設 計 概 念,主 要 是 用 來 觀 測 氫 氣 所 發 射 出 的 電 波 輻 射 ; 藉 由 這 些 氫 原 子 的 電 波 輻 射 , 天 文 學 家 可 以 測 定 10 億 個 以 上 星 系 的 位 置 和 質 量 。 另 一 個 SKA 的 目 標 是 波 霎 ( pulsars) --大 質 量 恆 星 演 化 末 期 爆 炸 之 後 的 核 心 殘 骸 , 質 量 高 達 地 球 的 100 萬 倍 以 上 ,直 徑 卻 僅 有 一 個 城 市 大 小 ,因 此 密 度 相 當 高;波 霎 自 轉 速 度 超 快,每 秒 可 自 轉 數 百 圈 以 上,

但 自 轉 速 度 相 當 穩 定 , 是 宇 宙 中 最 精 確 的 時 鐘 。 天 文 學 家 可 經 由 觀 察 波 霎 自 轉 的 改 變 , 來 測 試 愛 因 斯 坦 對 於 重 力 的 想 法 究 竟 是 對 是 錯 。 而 SKA 其 觀 測 運 作 的 波 段 , 即 是 100 MHz ~ 25 GHz。 在 日 常 生 活 方 面,微波最廣為人知的除了使用於微波爐外,就 是無線區域網路的應用了。由 於 寬 頻 的 普 及 和 無 線 的 需 求,無線 區域網路已是大家耳熟能詳的用語了。 早 在 1997 年, 無線區域網 路的第一個版本就已經被發表出來, 其中定義了 MAC 層和實體層, 工作頻率定在 2.4GHz 的 ISM 頻段上,並 且 擁 有 兩種無線調頻方式 和一種紅外傳輸的方式,總數據傳輸速率設計為 2Mbit/s。 在 1999 年, 又 加上了兩個補充版本: 802.11a 及 802.11b, 分 別 定義在 5GHz 頻段上可達 54Mbit/s 的數據傳輸速率及在 2.4GHz 頻段上有 11Mbit/s 的數據傳輸速率。 在 2003 年進而推出 802.11g, 其 允 許 實 體 工 作 在 2.4GHz 時,擁有 54Mbit/s 的數據傳輸速率。在 2004 年 1 月,IEEE 宣佈組成一個新的單位來發展新的 802.11 標準, 預 估 資料傳輸速度估計將達 540Mbit/s, 此項新標準預計要比 802.11b 快上 50 倍,而比 802.11g 快上 10 倍左右。802.11n 也將會 比目前的無線網路傳送到更遠的距離。 802.11n 在 2006 已有初版推 出, 並 且 有 相 關 產 品 在 市 面 上 銷 售 。 為了追求更高的頻寬,在 2002 年二月,美國的 Federal Communications Commission (FCC)公佈超寬頻技術能在 3.1 GHz 到 10.6 GHz 之間的頻率範圍使用,而不用申請執照, 這 對 無 線 寬 頻 的 愛 用 者 更 是 一 大 福 音 。 在高速網路頻寬需求的時代下,像是有線網路已從早期的

10Mbps 提昇到目前的 1Gbps,甚 至 是 10Gbps 的 數據傳輸速率, 其 速 度 的 提 昇 是 如 此 之 強 悍 , 相 較 於 無 線 網 路 , 若 無 線 網 路 在 速度上要有更卓越的提昇, 除 了 在 加 強 資 料 壓 縮 的 技 術 外 , 勢 必 在 使 用 的 頻 段 上 要 有 所 提 昇 , 像 是 利 用 較 高 的 頻 率 來 達 到 更 高 的 傳輸速率,所 以 開 放 更 高 頻 段 給 大 眾 使 用,將 是 一 個 不 變 的 趨 勢 。 在通訊方面, 衛 星 通 訊 的 應 用 範 圍 越 來 越 廣 , 尤 其 是 寬 頻 帶 通 信 衛 星 技 術 的 不 斷 提 昇 , 在 加 上 衛 星 通 信 有 著 不 少 獨 特 的 優 點,像 是 接 入 方 式 靈 活,而 且 能 進 行 廣 播 式 傳 送 等 特 性, 所 以 使 它 有 著 不 可 動 搖 的 地 位 。 就多媒体傳輸對頻寬 的 要 求 , 光 纖 的 確 是 能 滿 足 大 部 分 的 需 求 , 只 不 過 , 就 算 是 在 先 進 的 開 發 國 家 , 仍 然 無 法 克 服 ” 最 後 一 英 里 ” 的 障 礙 , 因 為 若 要 把 光 纖 拉 到 每 個 月 戶 家 中 或 是 辦 公 室 , 除 了 工 程 量 龐 大 , 費 用 過 高 外 , 施 工 期 也 很 長 , 這 情 形 在 偏 遠 地 區 就 更 顯 困 難 了。所以就目前的技術水平跟可預 見的未來來看, 發 展 寬 頻 帶 衛 星 通 信 系 統 是 最 佳 的 選 擇 。目前 來看,已 有 些 先 進 國 家,正 在 積 極 開 發 Ka 頻 段 (18GHz)衛 星 通 信 技 術 , 並 取 得 預 期 的 效 果 。 Ka 頻段的下行頻率範圍為 17.7G~21.2GHz,亦 即 它 可 以 提 供 3G~4GHz 的 工 作 頻 寬,所 以 遠 遠 大 於 C 頻 段 和 Ku 頻 段。另 外,使 用 Ka 頻 段 還 可 以 減 少 對 地 面 系 統 的 干 擾,在 人 口 稠 密 地 區 , 對 地 面 干 擾 的 減 少 也 意 味 著 對 發 射 現 埸 選 位 變 的 較 為 容 易 和 相 對 的 降 低 成 本 。 Ka 頻段衛星通信將用在長途通話, 高 容 量 數 據 服 務 , VSAT

業 務 服 務 和 電 視 會 議 服 務 等 方 面 , 受 到 Ka 頻 段 開 發 成 功 的 鼓 舞 , 有 些 國 家 更 是 進 一 步 地 開 始 向 更 高 的 頻 段 挑 戰 , 像 是 Q,V 頻 段 等 等,如 此 看 來,衛 星 通 信 仍 然 會 持 續 火 熱 下 去 。

在太空通訊方面, 在 Space Communication Architecture Working Group (SCAWG) 的 NASA Space Communication and Navigation Architecture Recommendations for

2005-2030 中 , 對 未 來 太 空 通 訊 架 構 有 著 十 分 清 楚 的 示 意 圖 , 參 考 圖 4。參考文獻[1] 。

它 把 SCA 大 致 分 成 4 個 區 域 - 1). Earth, 2). Moon, 3). Mars vicinity and 4). Deep Space。 其 中 所 使 用 的 頻 率 有 UHF、S、L、K、Ku 和 Ka 等 頻 段,像 是 Ground-based Earth Element 對 Near-Earth Relay Element 就 是 使 用 13GHz ~ 15GHz 頻 率 , Ground-based Earth Element 對 Launch Vehicles、Earth Orbital User、Lunar Surface 和 Orbital User 即 是 使 用 22GHz ~ 27GHz,這 些 頻 段 均 落 在 本 專 題 的 使 用 範 圍 , 也 是 為 什 麼 要 選 擇 9G-25GHz 的 原 因 之 一 。

圖 4 未 來 太 空 通 訊 架 構 表 1 通訊應用頻段 研究動機 1). 在科技日新月異的時代中,通訊技術不斷進步下,操作頻率 也不斷在向上推昇,直接影響到的就是高速元件對材料方面的要求及 改良。現今商業中利用 MOS 來製做的積體電路,其頻段大都落在 3G~10GHz,此專題除了做為未來頻段擴展應用的前導,亦可以驗證 MOS 在 Ka 頻 段 操 作 的可行性。 應用 頻段 天文 SKA 100 MHz~ 25 GHz 軍 事 EW/ECM 9G~26GHz 衛 星 通 訊 Ka 頻 下行傳輸 17.7G~21.2GHz 太空通訊 地 面 對 衛 星 傳 輸 13G ~ 15GHz 太空通訊 星 際 對 星 際 傳 輸 22G ~ 27GHz

2). 微波在天文及衛星通訊的應用上,其成本一直居高不下,尤

其像SKA 是由上百個無線電台所組成,其架設成本定會讓許多國家

望而止步, 若要普遍應用,勢必要使用 IC 來降低成本,而 MOS 的 製造成本相對低廉,若能成功使用 MOS 來量產,定可以為天文及衛 星通訊等發展帶來福音。

3). 現階段研究的 Ultra Wideband LNA,在輸入端及輸出端的匹 配電路,大都相對複雜,也往往是造成 Noise Figure 上昇的原因之 一,尤其頻率越高,Noise Figure 更是急速增加。所以在超寛頻的應 用上,如何同時保有好的增益及低的雜訊指數,是一門值的深入探討 的課程。 本專題期望能利用 L-C 匹配方式,來達到超寛頻及相對低的雜訊 指數,並把它實現應用在 nMOS 0.18um 的製程上,讓頻寬能夠操作 在 9G~25GHz 的頻率範圍。

二、工 作 原 理 此電路架構共有五級: 1). 第一級 nMOS 電路中,主要原理是調整輸出的 RC 負載阻抗 及 nMOS 的源極電感,來達到超寬頻的目的[2]。如下圖 5 中,我們 可以看到曲線 1 是模擬輸出負載端,串 50 歐姆所得到的結果,可以 明顯看出來其 Sin並不理想。而曲線 2 則是模擬利用 LFB,RFB及 CFB 來做阻抗匹配及達成寬頻的應用。 圖 5 利 用 LFB, RFB 和 CFB 達 到 匹 配 圖 5(a)的輸入轉導 Yin(=1/Zin)可以用下列公式表示。 Yin = jω Cgs + jω Cgd { 1 – [(jω Cgd – Gm)/jω (Cgd + CFB)]} ≈ jω (Cgs + Cgd) + [Cgd Gm/(Cgd + CFB)] (1) 這時等同一個電容並聯一個電阻,所以使用一個外部的源極電 感將可以移除 Yin的虛部。可以達到寛頻的阻抗匹配。 有些電路的作法,是利用較複雜的 LC 匹配電路,像是高階的 帶通濾波器來做最前端的匹配電路,故用了至少兩個電感來作為匹 配,但往往會因為電感的品質因數不夠高,而導致雜訊上昇,以及 輸入信號的損失,故在本電路上,每級只應用一個電感及電容做匹

配,以降低前端匹配電路所貢獻的雜訊。參考文獻[3]~[10]。 在輸入阻抗匹配的分析中,寬頻電路可以把它解析成兩個部

分,一個是輸出負載為電阻性 RFB,如圖6(a),其主要負責較高頻

段的匹配。而另一部分則是電容性的輸出負載 CFB,如圖6(a)。而

LFB均呈現在這兩部分的電路之中。

圖 6 (a) The resistive-loading circuit with R as its output loading. (b) The capacitive-loading circuit with C as its output loading.

其輸入阻抗的公式如下: Zin = (1/jωCgs) + [ LFB( Gm + jωCgs)/Cgs] ≈ (1/jωCgs) + (LFB Gm/Cgs) (2) 從推導出來的公式可以看出來,Rds會降低Gm值,而Cgd亦 會使輸入容抗變大,所以減少LFB的電抗性。 較完整的輸入阻抗公式如下: Zin ≈ (1/jωCgs) + (LFB γ Gm/Cgs) [ 1 + Cgd ( 1 + γ Gm RFB )/Cgs]-1 (3) γ = Rds/(Rds + RFB + jω LFB) (4) 假設 ω LFB << 1/ωCgs,ω LFB << RFB

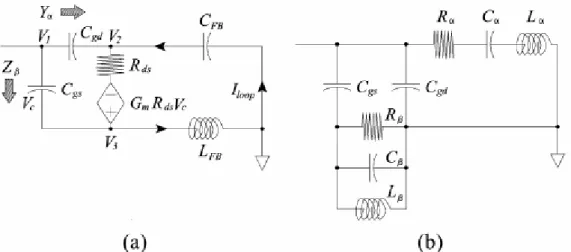

圖 7 (a) To find out the circuit’s input impedance, values of Yα and Zβ , which are indicated by the arrows, need to be derived first. (b) The equivalent circuit

from the input impedance’s point-of-view where Rα , Cα , Lα come from Yα ,

while Rβ , Cβ , Lβ are from Zβ .

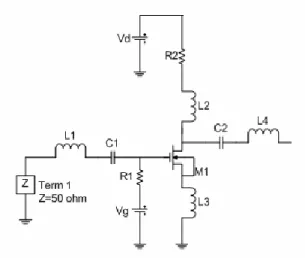

整個輸入阻抗 Zin等於 Yα 和Zβ互相並聯,其公式如下: Zin = ( Yα + 1/Zβ )-1 (5) Yα = jωCgd + ( Rα + 1/jωCα + jωLα )-1 (6) With Rα = CFB/GmCgd (7) Cα = GmRdsCgd (8) Lα = ( LFBCFB/Gm Rds Cgd ) ( 1 + Gm Rds) (9) Zβ = 1/jωCgs + ( 1/Rβ + jωCβ + 1/jωLβ )-1 (10) With Rβ = GmLFB/Cgs (11) Cβ = Cgs/GmRds (12) Lβ = ( LFBGm Rds CFB )/Cgs (13) 2). 同樣地,在每一級的輸出端,也一樣採用一組電感及電容來 做匹配。電容除了做 DC 隔離外,亦作為輸出電路的匹配。而每級間 的交連電感主要是用來提昇增益及電路匹配之用。參 考 圖 8。

圖 8 First stage circuit

3). 第二級到第五級: 其每一級均用一組 L-C 來做阻抗匹配,而 M2~M5 的 nMOS,主要是用來放大 S21 的增益。參 考 圖 8。 原始電路:

設計流程圖如圖 10,步驟流程如下。 (1) 首先依照應用層面來訂定LNA操作的頻率範圍,並決定相關的規格。 (2) 確立LNA之基礎電路及構思。 (3) 利用ADS完成整個電路的設計。 (4) 先完成前3級之電路架構,待性能達到規格後,做inter-stage stability 和全級之穩 定性分析。 (5) 增加級數至5級,在性能達到規格後,完成inter-stage stability和全級 之穩定性分 析。 (6) 考量製程飄移及溫度變異所造成的影響。 (7) 使用Cadence 進行電路的佈局,包含DRC、LVS。 (8) 把Layout的線段和電感滙出,並利用Momentum粹取出S參數,再放回 ADS做模擬 並驗證結果。 (9) 完成設計,IC下線生產。 圖 10 設計流程圖

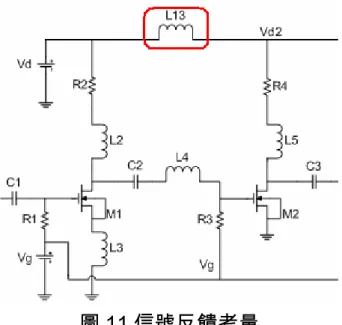

設計概要: 1). 改變 nMOS 的 nr- 為了使 S22 達到較好的效能,故把 nMOS 的 nr 從 M1 的 32,依 序降成 M2=M3=16,M4=M5=8。 2). 減少製程上的變動- 為了減少因製程上的影響,所以在汲極端的小電阻,均採用並聯 方式,以期望可以降低電阻的偏移。 3). 考量 Current Density 及溫度的效應- 為了怕溫度變動及電流過大造成電路燒毀,我加入 Current Density 的效應考量。設計讓 M1 容許的電流量至少為 23mA,而 M2 跟 M3 則約為 13mA,M4 跟 M5 則為 8mA 左右。 故在 M1 使用 3 顆 電阻並聯, 其電阻寛度皆保持為 3um,而汲極跟源極電感亦採用 9um, 讓整體線寬均為 9um,使得 M1 電路在 70 度時,依然可以承受至少 31mA 的電流量。 而在 M2 到 M5 則各使用 2 顆電阻並聯,並考量全部線寬,使電路 即使操作在 70 度時,仍可避免因為 Current Density 的效應而使電路 無法正常工作。 4). 考量信號反饋的效應- 在高頻時,為了怕後級的信號透過電源反饋到M1 來,所以在 M1 跟 M2 的電源中間,特地加了一個大電感來隔離訊號。同時考慮 Current Density 的效應,故電感 L13 及電源走線線寬均使用 15um 寬度,來做 為 M2~M5 的電源供給。參 考 圖 11。

圖 11 信號反饋考量 5). 檢測電路是否振盪- 為了考量輸入電源線的電感所造成的影響,所以在 Vd 電源供應端 串接一個 CHOKE 來模擬電源電感的效應,並加入適當的電容來減低 電路振盪的可能性。下圖為 ADS 模擬的穩定因素。 我們可以看見,在 0~40GHz 的頻率中,Mu 均大於 1,而穩定因 素 K 亦大於 1,B>0,故我們可以確保此電路達到無條件穩定。參 考 圖 12。 圖 12 穩定參數

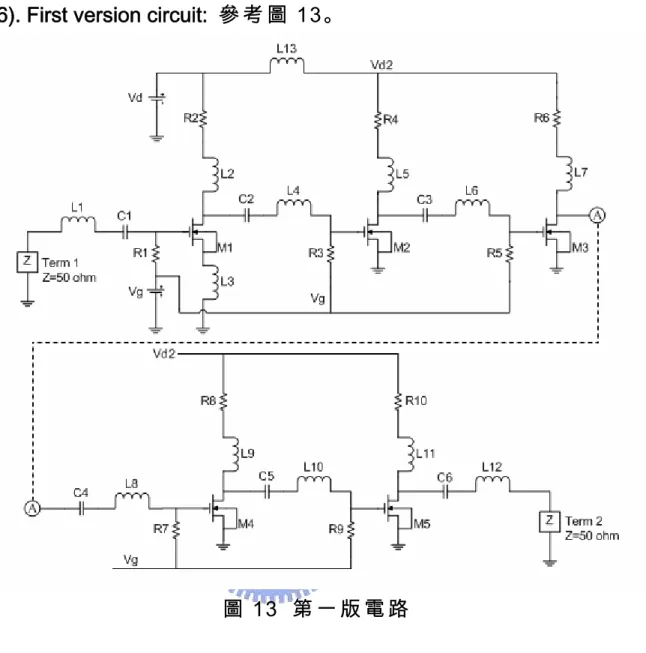

6). First version circuit: 參 考 圖 13。

圖 13 第 一 版 電 路 7). 下面為電路模擬的結果:

a) S11:在工作頻率內,皆 under -11dB 以下。參 考 圖 14。

b) S22:在工作頻率內,皆 under -11dB 以下。參 考 圖 15。 圖 15 S22 參數 c) S21:在工作頻率內,Gain 均保持在 21dB 正負 0.7dB 右左。 可見在寛頻應用上,其增益及變動量,均能達到很好的效能。 參 考 圖 16。 圖 16 S21 參數 d) S12:在工作頻率內,皆 under -60dB 以下。參 考 圖 17。 圖 17 S12 參數

e) S11 和 S22 的 smith chart:參 考 圖 18。 圖 18 Smith chart f) NF:從曲線上可以得知,Noise Figure 在操作頻率中,其值為 2.747~5.679. 在寛頻應用上,算是相當好的效能。參 考 圖 19。 圖 19 Noise Figure 模擬 Tech. BW (GHz) S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) Simulate Result 0.18μ mCMOS 9-25 < -11 < -11 21±0.7 < -60 2.84-5.4 3 表 2 模擬結果

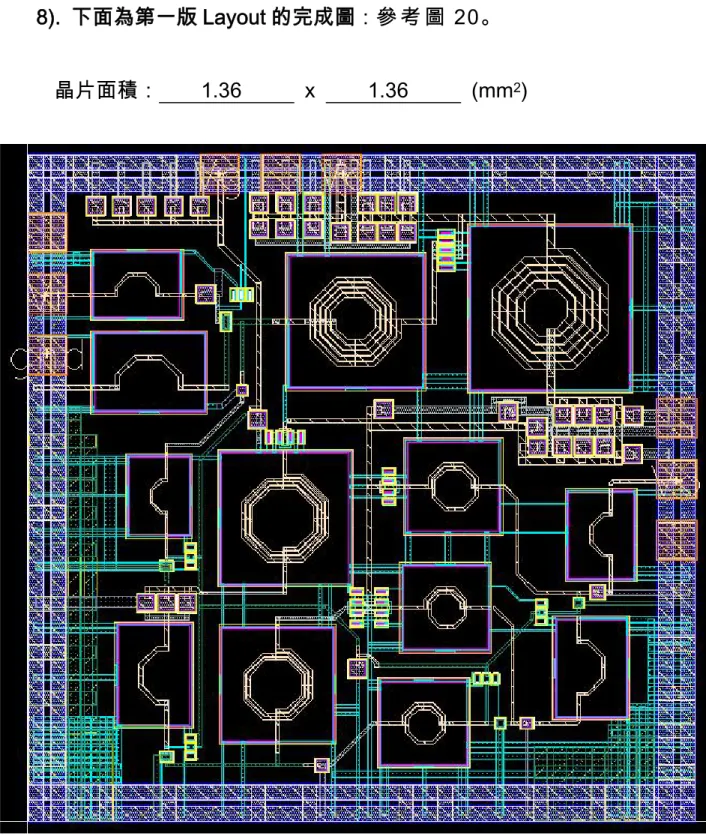

8). 下面為第一版 Layout 的完成圖:參 考 圖 20。

晶片面積: 1.36 x 1.36 (mm2)

9). 粹取出每個電感,並放入 Momentum 模擬它們的 S 參數: 在 layout 完成後,我首先把每個電感放入 Momentum 去模擬,這樣 可以模擬出實體 layout 的電感 S參數,並把粹取出來的參數重新放入 ADS 電路中,再次模擬。這樣一來,不僅可以增加電感元件的正確性,並降低 因 ADS 電感等效電路的偏移誤差,所造成的設計失誤。參 考 圖 21。 圖 21 Momentum 模擬電感 S 參數 • 利用下面的方法取得電感的 S 參數。參 考 圖 22,圖 23。 參考文獻[11][12]。 圖 22 Y 參數 Deembedding

圖 23 Deembedding 示意圖 10). 取出每一個 layout 的線段,並放入 Momentum 模擬以粹取出 S 參 數。 我分別把對電路較為敏感的每條 Layout 走線,分別利用 Momentum 模擬求得 S 參數,再套入 ADS 的電路中模擬,以防止因 Layout 線段所 造成的寄生電感,而造成的設計錯誤。 11). 把每一個電感跟 Layout 線段所粹取出來的 S 參數,重新放入 ADS 電路中,再次模擬,(如圖 24): 圖 24 考量 layout 線段之電路圖

模擬結果: 參 考 圖 25,我們可以看到 S21 及 S11 已經不符合當初所設計的 效能,其起因於 M1 到 L3,L3 到 GND,以及 M3 到 C4 之間的連接線 過長,導致寄生電感過大,而使電路匹配產生偏移。故學生對 Layout 元件的配置、整體走線以及電路設計均會再做適當的修改及調整。 圖 25 S 參數模擬結果 12). 參考以上的模擬結果,以及 CIC 評審委員所給予的建議,我做了 下列的改善:

a). 在第一版的 layout 中,Pad 的 size 是使用 75mm X 75mm,因 為 Pad 的尺寸越大,其寄生電容越大,故將其改成 50mm X 50 mm, 以降低寄生電容對電路所產生的影響。 b). 重新配置元件位置,考量介於 M3 源極到 L3 和 GND,還有各級 間的交連電容及電感其 layout 的線段長度,使其越短越好,以減低寄生 電感所帶來的效應。 c). 因為使用許多電感,所以晶片面積達到 1.36 X 1.36 (mm2) ,為

率。

在新的 layout 中,所使用到的晶片面積只有 0.945 X 1.295 (mm2) ,比

原來所使用到的面積還要小 33%左右。

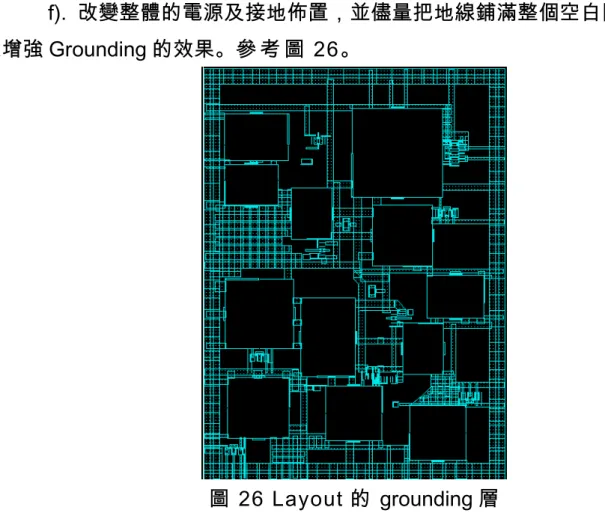

d). 在閘極電源間,加入信號隔離電阻,以降低信號反饋的可能性。 e). 增加 inter-stage stability analysis,製程飄移及溫度變異等模擬。 f). 改變整體的電源及接地佈置,並儘量把地線鋪滿整個空白區域, 以增強 Grounding 的效果。參 考 圖 26。

圖 26 Layout 的 grounding 層

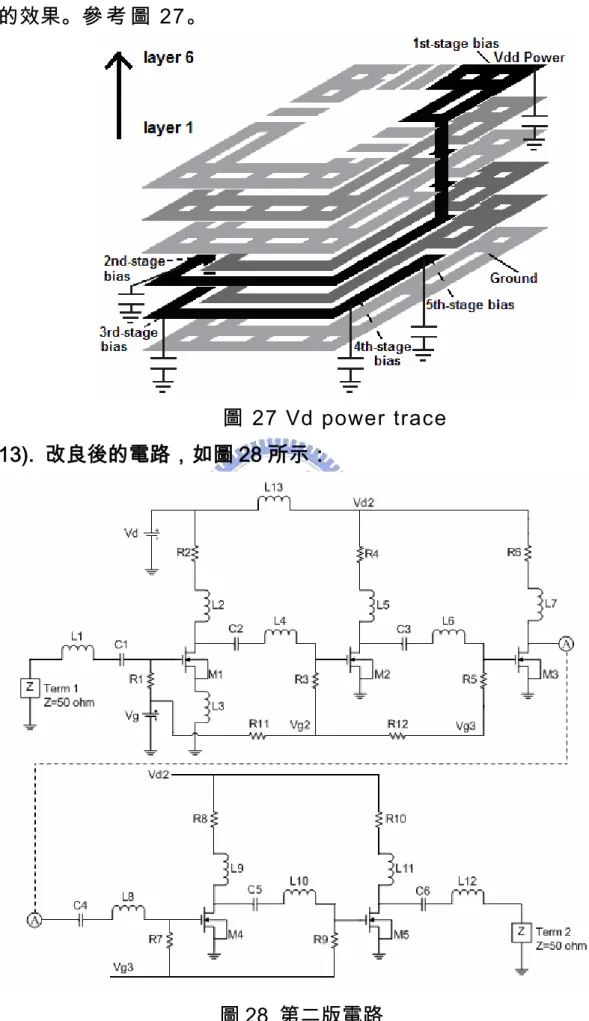

g). 為了考量信號反饋的效應,所以在第一版電路中添加了一個 L13 大電感,並利用它來防止後級的信號透過電源反饋到前級去。因為現在 為了減少 die size,所以移除 L13,並改而使用 layout 的技巧來處理信 號的反饋。我把 layer2 跟 layer3 的一部分 ground 拿來當做 Vd power 的走線,使其等同連接一個大電感一般,達到防止信號反饋跟節省面積

的效果。參 考 圖 27。

圖 27 Vd power trace 13). 改良後的電路,如圖 28 所示:

我把完成的電路,放到再次使用 ADS2005 模擬,工作電壓 Vg 為 0.8V 電壓,而 Vd 分別使用不同的電壓 1.4V 和 2.0V 來模擬,其結果如下: 一). 工作電壓: Vg = 0.8V and Vd = 1.4V a) S11:在工作頻率內,皆低於-11dB 以下,符合設計規格。請參 考 圖 29。 圖 29 S11 參數 b) S22:在工作頻率內,皆 under -12dB 以下。參 考 圖 30。 圖 30 S22 參數 c) S21:在工作頻率內,Gain 均保持在 19.5dB 正負 1 dB 右左。 在寛頻應用上,其增益及變動量,仍然能達到很好的效能。 參 考 圖 31。

圖 31 S21 參數 d) S12:在工作頻率內,皆 under -62dB 以下。參 考 圖 32。 圖 32 S12 參數 e) S11 和 S22 的 smith chart:我們可以看到,S11 和 S22 均圍繞在 史密斯圖的中心點,請參 考 圖 33。

f) NF:我們可以從曲線上得知,Noise Figure 在操作頻率中,其值為 3.337~5.843. 在寛頻應用上,算是相當不錯的效能。參 考 圖 34。 圖 34 Noise Figure 模擬 從上面的模擬結果來看,可以清楚的得知此 LNA 設計,即使工作在 Vd 為 1.4V 的低電壓,仍然可以符合設計的規格,尤其在如此高頻及寛頻 的應用上,算是相當不錯的效能。 二). 工作電壓: Vg = 0.8V and Vd = 2V a) S11:在工作頻率內,皆低於-11dB 以下。參 考 圖 35。 圖 35 S11 參數 b) S22:在工作頻率內,皆 under -11dB 以下。參 考 圖 36。

圖 36 S22 參數 c) S21:在工作頻率內,Gain 均保持在 22dB 正負 1 dB 右左。 在寛頻應用上,其增益及變動量,仍然能達到很好的效能。 參 考 圖 37。 圖 37 S21 參數 d) S12:在工作頻率內,工作頻段皆 under 在-60dB 以下。請參 考 圖 38。 圖 38 S12 參數

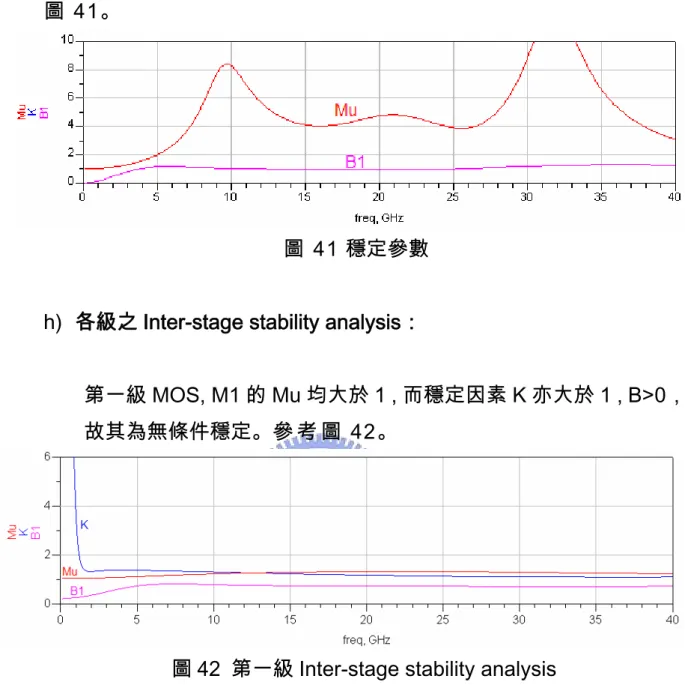

e) S11 和 S22 的 smith chart:參 考 圖 39。 圖 39 Smith chart f) NF:我們可以從曲線上得知,Noise Figure 在操作頻率中,其值為 2.897~5.454. 在寛頻應用上,算是相當不錯的效能。參 考 圖 40。 圖 40 Noise Figure 模擬 g) 檢測電路是否振盪- 我們可以看見,在 0~40GHz 的頻率中,Mu 均大於 1,而穩定因 素 K 亦大於 1,B>0,故我們可以確保此電路達到無條件穩定。參 考

圖 41。

圖 41 穩定參數 h) 各級之 Inter-stage stability analysis:

第一級 MOS, M1 的 Mu 均大於 1,而穩定因素 K 亦大於 1,B>0, 故其為無條件穩定。參 考 圖 42。

圖 42 第一級 Inter-stage stability analysis

第二級 MOS, M2 的 Mu 均大於 1,而穩定因素 K 亦大於 1,B>0, 故其為無條件穩定。參 考 圖 43。

第三級 MOS, M3 的 Mu 均大於 1,而穩定因素 K 亦大於 1,B>0, 故其為無條件穩定。參 考 圖 44。

圖 44 第三級 Inter-stage stability analysis

第四級 MOS, M4 的 Mu 均大於 1,而穩定因素 K 亦大於 1,B>0, 故其為無條件穩定。參 考 圖 45。

圖 45 第四級 Inter-stage stability analysis

第五級 MOS, M5 的 Mu 均大於 1,而穩定因素 K 亦大於 1,B>0, 故其為無條件穩定。參 考 圖 46。

從圖 42~圖 46 可以清楚看到各級的 Inter-stage stability analysis 均是 無條件穩定的,如此一來,可以避免因為每級之間的不穩定參數,而造成 電路振盪,而影響到整體的效能。 整個模擬結果如下表3,在頻率 9~25GHz 的操作頻段,S11 均小於 -11dB,而 S22 參數一樣小於-11dB,增益更是高達 19.5 dB 以上。相對於 其它的寬頻 LNA 設計,NF 效能更是十分優異。 Tech. BW (GHz) S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Simulate Result 0.18μ mCMOS 9-25 < -11 < -12 19.5±1 < -62 3.33-5.8 4 1.4 Simulate Result 0.18μ mCMOS 9-25 < -11 < -11 22±1 < -60 2.89-5.4 5 2.0 表 3 模擬結果 14). 同樣的,在 layout 完成後,把粹取出來的電感跟 Layout 線段的 S 參數,全部再次放到 ADS 電路中 (如圖 47),並進行模擬。 圖 47 考量 layout 線段之電路圖

[8]模擬結果: 我把更改過後的電路,再利用 Momentum 求得每個電感的 S 參數,最 後再加上每個 Layout 線段的模擬,把整體的模擬結果展示在下列資料中, 同樣地,工作偏壓 Vd 一樣使用 1.4V 和 2.0V 的電壓準位來進行模擬,以確 保此電路可以操作在較寛的電壓變動。 操作頻率: 9G ~ 25GHz 工作電壓: Vg = 0.8V and Vd = 1.4V 1. S11:如下圖所示,在 9G ~ 25GHz 的工作頻率內,皆其 S11 參數全部皆 under -10dB 以下。參 考 圖 48。 圖 48 S11 參數 2. S22:圖 49 顯示出此 LNA 在工作頻率內,每個頻率點皆 under -14dB 以下,最大值也有-14.264dB,顯示出本 LNA 在 S22 參數有著 十分優異的效能。參 考 圖 49。 圖 49 S22 參數

3. S21:在工作頻率內,S21 的 Gain 均可以保持在 20.5 dB 正負 1 dB 右左的效能。所以證明其增益平坦性及整體變動量,在寛頻應用 上,是十分良好的效能,尤其是工作在如此高的頻率中,依舊能保持 很好的效能。請參 考 圖 50。 圖 50 S21 參數 4. S12:從先前的模擬到現在S12 模擬,其工作頻率內的任一點 S12 參數,均在-60dB 左右,此電路模擬結果顯示 S12 最大點落在 27.2GHz 上,但仍能保持在 under -58dB 以下。S12 參數請參 考 下 圖 51。 圖 51 S12 參數

5. 下圖 52 為 S11 和 S22 的 smith chart,我們可以看到因為加入 每條連接線段的電感模擬,所以在 MOS 源極的電感性會隨之增加, 故 S11 匹配的曲線圍繞在中心點的圓圈會變的較大,但操作頻率仍然 是圍繞在中心點的的位置,沒有太大的偏移。 圖 52 Smith chart 6. NF: 從曲線上可以得知,Noise Figure 在操作頻率中,其值為 2.840~5.431。在寛頻應用上,是非常不錯的效能。參 考 圖 53。 圖 53 Noise Figure 模擬 綜合上面的模擬結果,可以得知此電路一樣可以操作在 Vd = 1.4V 的電壓。

操作頻率: 9G ~ 25GHz 工作電壓: Vg = 0.8V and Vd = 2V 7. S11:現在把 Vd 電壓調成 2V,再利用模擬軟體模擬,我們可 以從圖 55 的曲線得知,在 9G ~ 25GHz 工作頻率內,均 under -10dB 以下,故符合設計規格。 圖 54 S11 參數 8. S22:在 Vd 電壓為 2V 的條件下,操作的工作頻率內,皆能夠 under -13dB 以下,其最大值落在 15.8GHz 上,值為-13.497dB,請 參 考 圖 55。 圖 55 S22 參數

9. S21:在工作頻率內,Gain 均保持在 20.5 dB 正負 1 dB 右左。 所以其增益及變動量,在寛頻應用上一樣能達到很好的效能。 參 考 圖 56。 圖 56 S21 參數 10. S12:在工作頻率內,皆 under -60dB 以下。參 考 圖 57。 圖 57 S12 參數 從上面的 S 參數模擬報告得知,本寬頻 LNA 電路在經過嚴謹 的設計考量下,即使加上每級的 layout 線段和電壓變動的環境模 擬,一樣能夠保有十分優異的效能。

11. 下圖為 S11 和 S22 的 smith chart。請參 考 圖 58。我們可以從 此圖看出,S22 一樣圍繞在 smith chart 中心點,而 S11 雖然中心點 有些微的往下偏一點點,但大致上仍是繞著中心點而轉動,所以確保 S11 和 S22 沒有太大的偏移。 圖 58 Smith chart 12. NF: 從曲線上可以得知,Noise Figure 在操作頻率中,其值 為 2.840~5.431. 在高頻及寛頻應用上,是非常不錯的效能。 參 考 圖 59。 圖 59 Noise Figure 模擬

13. 製程飄移之模擬:

接 下 來 , 為 了 確 保 本 電 路 不 會 因 為 MOS 製 程 上 的 變 異 , 而 造 成 整 體 效 能 的 下 降 , 甚 至 輸 入 阻 抗 匹 配 的 偏 移 ,所 以 必 須 驗 證 MOS 在 Fast/Fast,Slow/Slow,Fast/Slow,Slow/Fast 各個條件下的模擬,而 Resistance 設為 Worst case,相同的一樣 針對 Vd = 1.4V 和 Vd = 2.0V 來做模擬,整體模擬結果如圖 60~圖 67。 MOS 製程變異的影響 工作電壓: Vg = 0.8V and Vd = 1.4V a. Fast/Fast,Resistance=Worst,參考圖 60。 圖 60 製程飄移之模擬結果 F/F S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-15.535 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 的增益亦 保持在 19.6 dB 以上。

b. Slow/Slow,Resistance=Worst,參考圖 61。 圖 61 製程飄移之模擬結果 S/S S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-13.253 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 的增益雖 然有所下降,但仍能保持在 12.204 dB 以上。 c. Fast/Slow,Resistance=Worst,參考圖 62。 圖 62 製程飄移之模擬結果 F/S

S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-15.047 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 的增益保 持在 18.9 dB 以上。 d. Slow/Fast,Resistance=Worst,參考圖 63。 圖 63 製程飄移之模擬結果 S/F S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-13.635 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 的增益雖 然有所衰減,但仍能保持在 13.638 dB 以上。

下表 4 為 MOS 製程變異在 Vdd 為 1.4V 的模擬結果總表,雖然在 Slow/Slow 的 S21 增益有所下降,但整體的S參數仍是在預期的操作 範圍內。 製程飄移 S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Stable Fast/Fast < -9.5 < -15 20.6±1 < -60 3.27-5.6 9 1.4 無條件穩定 Slow/Slow < -10 < -13 13.1± 0.9 < -57 3.62-6.2 2 1.4 無條件穩定 Fast/Slow < -9.8 < -15 19.7±1 < -59 3.32-5.8 2 1.4 無條件穩定 Slow/Fast < -10 < -13 14.6±1 < -57 3.44-5.9 3 1.4 無條件穩定 表 4 製程飄移之模擬結果 工作電壓: Vg = 0.8V and Vd = 2V e. Fast/Fast,Resistance=Worst,參考圖 64。 圖 64 製程飄移之模擬結果 F/F S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-14.459 dB 以下,而 S12 在操作頻率內,依然小於-61 dB,S21 的增益更 是保持在 22.3 dB 以上。

f. Slow/Slow,Resistance=Worst,參考圖 65。 圖 65 製程飄移之模擬結果 S/S S11 在 9GHz~25GHz 均小於-11dB,而 S22 也均小於-14.459 dB 以下,而 S12 在操作頻率內,依然小於-61 dB,S21 的增益更 是保持在 22.3 dB 以上。 g. Fast/Slow,Resistance=Worst,參考圖 66。 圖 66 製程飄移之模擬結果 F/S S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-14.087 dB 以下,而 S12 在操作頻率內,依然小於-61 dB,S21 有 21.5 dB 以上的增益。

h. Slow/Fast,Resistance=Worst,參考圖 67。 圖 67 製程飄移之模擬結果 S/F S11 在 9GHz~25GHz 均小於-11dB,而 S22 也均小於-13.031 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 雖有所下 降,但仍保有 16.5 dB 以上的增益。 下表為 MOS 製程變異在 Vdd 為 2.0V 的模擬結果總表,雖然在 Slow/Slow 的 S21 增益有所下降,但整體的S參數仍是落在預期的操 作範圍內。 製程飄移 S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Stable Fast/Fast < -10 < -14 23.3±1 < -61 2.81-5.3 6 2.0 無條件穩定 Slow/Slow < -11 < -12 15.1± 0.8 < -59 3.12-5.8 1 2.0 無條件穩定 Fast/Slow < -10 < -14 22.3±1 < -61 2.86-5.5 0 2.0 無條件穩定 Slow/Fast < -11 < -13 17.4± 0.8 < -59 2.96-5.5 4 2.0 無條件穩定 表 5 製程飄移之模擬結果

接 著 為 了 確 保 電 路 不 會 因 為 電 容 在 製 程 上 的 變 異 而 造 成 整 體 效 能 的 偏 差 , 甚 至 輸 入 或 是 輸 出 阻 抗 匹 配 的 偏 移 ,所 以 必 須 驗 證 電 容 在 Fast/Fast,Slow/Slow 條件下的模擬,而 Resistance 一樣設為 Worst case,相同的,一樣針對 Vd = 1.4V 和 Vd = 2.0V 來做模擬,整體模擬結果如圖 68~圖 71。 電容製程變異的影響 工作電壓: Vg = 0.8V and Vd = 1.4V i. RFCAP=Fast/Fast,Resistance=Worst,參考圖 68。 圖 68 電容製程變異的影響 F/F S11 在 9GHz~25GHz 均小於-9.65dB,而 S22 也均小於-15.213 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 在操作頻 率上有 15.4 dB 以上的增益。

j. RFCAP= Slow/Slow,Resistance=Worst,參考圖 69。 圖 69 電容製程變異的影響 S/S S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-13.725 dB 以下,而 S12 在操作頻率內,依然小於-58 dB,S21 在操作頻率上 有 17.5 dB 以上的增益。 表 6 為電容製程變異在 Vdd 為 1.4V 的模擬結果總表,雖然 S21 增益有所下降,但整體的S參數仍是符合設計規格。 製程飄移 S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Stable Fast/Fast < -10 < -15 16.5±1.1 < -59 3.49-5.8 8 1.4 無條件穩定 Slow/Slow < -10 < -13.7 18.1±1 < -58.7 3.16-5.7 1 1.4 無條件穩定 表 6 電容製程變異之模擬結果

工作電壓: Vg = 0.8V and Vd = 2.0V k. RFCAP=Fast/Fast,Resistance=Worst,參考圖 70。 圖 70 電容製程變異的影響 F/F S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-14.3 dB 以 下,而 S12 在操作頻率內,依然小於-60 dB,S21 在操作頻率上有 18.5 dB 以上的增益。 l. RFCAP= Slow/Slow,Resistance=Worst,參考圖 71。 圖 71 電容製程變異的影響 S/S

S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-12.993 dB 以下,而 S12 在操作頻率內,依然小於-60 dB,S21 在操作頻率上 有 19.5 dB 以上的增益。 表 7 為電容製程變異在 Vdd 為 2.0V 的模擬結果總表,我們可以看 到整體的S參數符合設計規格。 製程飄移 S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Stable Fast/Fast < -10.2 < -13.9 19.5±1 < -60.8 2.98-5.5 3 2.0 無條件穩定 Slow/Slow < -10 < -12.9 20.6±1.1 < -60.5 2.74-5.3 7 2.0 無條件穩定 表 7 電容製程變異之模擬結果 最 後 驗 証 溫 度 變 異 對 電 路 造 成 的 影 響 , 把 操 作 溫 度 昇 高 為 70.0 C,並針對 Vd = 1.4V 和 Vd = 2.0V 來做模擬,整體模擬 結果如圖 72~圖 73。 溫度變異的影響 工作電壓: Vg = 0.8V and Vd = 1.4V m. Temperature=70.0 C,參考圖 72。 圖 72 溫度變異的影響

S11 在 9GHz~25GHz 均小於-10dB,而 S22 也均小於-15.1 dB 以 下,而 S12 在操作頻率內,依然小於-59 dB,S21 在操作頻率上有 13.8 dB 以上的增益。 工作電壓: Vg = 0.8V and Vd = 2.0V n. Temperature=70.0 C,參考圖 73。 圖 73 溫度變異的影響 S11 在 9GHz~25GHz 均小於-11dB,而 S22 也均小於-14.2 dB 以 下,而 S12 在操作頻率內,依然小於-60 dB,S21 在操作頻率上有 16.8 dB 以上的增益。 製程飄移 S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) Stable Fast/Fast < -10 < -15.1 14.6±0.8 < -59 3.96-6.5 7 1.4 無條件穩定 Slow/Slow < -11 < -14.2 17.5±0.8 < -60 3.35-6.1 4 2.0 無條件穩定 表 8 溫度變異之模擬結果 從模擬結果可以看到,即使在不同高溫的考量下,此寛頻放大器的S 參數依然保有優異的效能。

14. 相關研究結果比較: 比較同樣為 0.18um 製程的寬頻放大器效能,我們可以從模擬結果看 到,此放大器所操作的頻率更高,而且頻寬更為寬廣,操作的電壓範圍也 十分的大,就雜訊指數方面,更是有著優異的效能,在S21 的增益上,更 是有明顯的優勢。請參照表 9。 Tech. BW (GHz) S11 (dB) S22 (dB) S21 (dB) NF (dB) VDD (V)

This work 0.18μ mCMO

S 9-25 <-10 <-14 <-13 17.6±0.7 20.3±1.0 3.2-5.7 2.8-5.4 1.4 2.0 *[1] 0.18μ m CMOS 2.4-9.4 <-10 <-10 10.9 4.1 1.8 *[2] 0.18μ m CMOS 3-6 <-12 <-10 13.53- 15.91 4.7-6.7 1.8 表 9 相關研究結果比較 不同 VDD 偏壓點之性能比較 BW (GHz) S11 (dB) S22 (dB) S21 (dB) S12 (dB) NF (dB) VDD (V) <-10 <-15 14.8 -56 3.7-6.2 1.0 <-10 <-14 16.4 -57 3.5-5.9 1.2 <-10 <-14 17.8 -58 3.2-5.7 1.4 <-10 <-13 18.9 -59 3.0-5.6 1.6 <-10 <-13 19.7 -60 2.9-5.5 1.8 This work 9-25 <-10 <-13 20.3 -63 2.8-5.4 2.0 表 10 不同 VDD 偏壓點之性能比較

根據上面表格的資料,我們可以看到本專題在操作頻寬範 圍,除了有更為寬廣的操作頻率外,所容許的 VDD 操作範圍亦 十分大,在整體的增益及 NF 特性,亦有優異的改進。為了有 更高的增益,雖然使用 5 級來放大,但在 die size 方面,仍然 是相對的小很多。 * 專題[1]及[2]請參閱-參考文獻[13]、[14] 。 規格 結果 S11 [dB]. < -10 S22 [dB]. < -14 S21 [dB]. 17.6 ± 0.7 S12 [dB]. < -58 BW [GHz]. 9 ~ 25 NF [dB @9GHz]. 3.2 NF [dB @26GHz]. 5.7 Power Consumption Vd = 1.4V, 80 mW 表 11 預計規格表 (1.4V) 規格 結果 S11 [dB]. < -10 S22 [dB]. < -13 S21 [dB]. 22.5 ± 1.0 S12 [dB]. < -60 BW [GHz]. 9 ~ 25 NF [dB @9GHz]. 2.8

NF [dB @25GHz]. 5.4

Power Consumption Vd = 2.0V, 130 mW

三、實 驗 結 果 測試考量: 此電路將申請 CIC 量測機會,進行 On Wafer 量測,欲量測項目 主要為:S 參數及 N.F 等電路特性。 把 Vg 接上 0.8V 直流電壓,而 Vd 使用 1.4V~2V 直流電壓. 並 利用網路分析儀,量得 S11、S22、S21、S12 等參數。

再使用 Noise Figure Analyzer 去量測 Noise Figure。

下針圖,如圖 74 所示:(欲使用 pitch 100um 的 3 Pin RF 探針, 與 pitch 100um 的 3 Pin DC 探針)

Circuit Layout and Photo

圖 75 Circuit Layout and Photo

S− Parameter Measured Results

IP1dB Measured Results

圖 77 IP1dB 量測結果

Noise Figure Measured Results

圖 78 Noise Figure 量測結果

量測結果顯示 S11 在 9GHz~20.5GHz 時均小於-10dB,20.5GHz~ 25GHz 則小於-7dB 以下。S22 在操作頻率範圍內均小於-10dB 以下, 而當 Vd=2.0V 時,S21 在 2.0V 操作頻率內均有 10 dB 以上的增益。

四、結 論

我們可以看到雖然 S11 在高頻時有些偏移,但基本性能仍然十分良 好,所以可以證明即使是使用使用 TSMC 0.18um RF-CMOS technology , 仍然還是可以成功設計出操作在 Ka 頻的寛頻 LNA。而 S21 有高頻的增益 上有所下降,其主因大致有幾點, 第一: tsmc 所提供的 model 準確性不 夠,只保證操作頻率在 20GHz 內。第二:因為電源走線所帶來的寄生電阻 效應,而導致後級 MOS 的電源衰減,造成增益的下降。第三:Pad 的電容 效應比預期的大,所以造成匹配有些偏移。 再者,因為後極電壓下降和電源走線的關係,所以有機會造成雜訊之 間的互相耦合,而造成 Noise Figure 上昇,所以改進方式可以電源線分開, 插入一層 Ground 分隔開來,相信可以大大的降低整體的雜訊指數。

圖 80 Revision on Circuit Layout

Add more GND

Pads

Add more by-pass

capacitors on

參 考 文 獻

[1] NASA Space Communication and Navigation Architecture Recommendations for 2005-2030

Space Communication Architecture Working Group (SCAWG)

[2] Wide-Band Matched LNA Design Using Transistor’ s Intrinsic Gate-Drain Capacitor

Robert Hu

[3] A GaAs monolithic 6 GHz low-noise amplifier for satellite receivers R. C. Mott,

IEEE Trans. Microw. Theory Tech., vol. 37, no. 3, pp. 565– 570, Mar. 1989. [4] A CMOS Low-Noise Amplifier for UltraWidebandWireless Applications M.F. CHOU, W.S. WUEN, C.C. WU, K.A. WEN, and C.Y. CHANG,

Nonmembers IEICE TRANS. FUNDAMENTALS, VOL.E88– A, NO.11 NOVEMBER 2005

[5] A gain-controllable wide-band low-noise amplifier in low-cost 0.8-_m Si BiCMOS technology

F. Seguin, B. Godara, F. Alicalapa, and A. Fabre,

IEEE Trans. Microw. Theory Tech., vol. 52, no. 1, pp. 154– 160, Jan. 2004. [6] A low supply voltage SiGe LNA for ultra-wideband front ends

D. Barras, F. Ellinger, H. Jackel, and W. Hirt

IEEE Microw. WirelessCompon. Lett., vol. 14, no. 10, pp. 469– 471, Oct. 2004. [7] Ultra-low-noise 1.2– 1.7-GHz cooled GaAsFET amplifiers

S. Weinreb, D. L. Fenstermacher, and R. W. Harris,

IEEE Trans. Microw. Theory Tech., vol. MTT-82, no. 6, pp. 849– 853, Jun. 1982. [8] Cryogenic wide-band ultra-lownoise IF amplifiers operating at ultra-low DC power

N.Wadefalk, A. Melberg, I. Angelov, M. E. Barsky, S. Bui, E. Choumas, R. W. Grundbacher, E. L. Kollberg, R. Lai, N. Rorsman, P. Starski, J. Stenarson, D. C. Streit, and H. Zirath

IEEE Trans. Microw.Theory Tech., vol. 51, no. 6, pp. 1705– 1711, Jun. 2003. [9] G. Gonzalez, Microwave Transistor Amplifiers Analysis and Design

Englewood Cliffs, NJ: Prentice-Hall, 1984.

[10] R. Goyal, High-Frequency Analog Integrated Circuit Design

New York: Wiley, 1995.

[11] Modeling toolkits 0_DEEMB.WPS | 18.03.02, De-embedding

Agilent Technologies, dept.: EEsof, D-82024 Taufkirchen (Munich), Germany

[12] 電感嗀型建立與電磁模擬驗證

國家晶矱系統設計中心 許源佳

IC Application & Design magazine 2005 May

[13] A 3– 10-GHz low-noise amplifier with LC-ladder matching network A. Ismail and A.A. Abidi,

” IEEE J. Solid-State Circuits, vol.39, no.12, pp.2269– 2277, 2004.

[14] 0.18 um 3– 6 GHz CMOS broad-band LNA for UWB radio C. P. Chang and H. R. Chuang,

自 傳 南部有個名叫 Takau(打狗)的可愛城市,也就是現今的南方港都- 高雄,是學生從小成長及學習的地方。我的名字叫洪祺源, 出生於 1976 年, 從小居住在高雄,所以有著南部純樸的個性,對工作或是學業上都十分努 力,有良好的責任感及學習態度。 學生父親服務於台灣電力公司,是個務實且具責任感的公務人員,母 親從事家管,負責照料我們的生活起居,尚有兄弟二人,生活十分樸實簡 單。從小父母親不但給予我們十分自由的學習環境,讓學生可以盡情的發 揮想像及創造力,同時也特別要求我們處事須努力踏實,要不斷學習上進, 以及常保一顆善良仁慈的心。這對我的人生態度及處事原則有著深切的影 響,也塑造了學生獨立自主、積極進取的個性。 德智體群美五育並重,一直是學生努力的方向。深信除了健全的智力 發展外,亦需具備良好的品德,並鍛練強健的體魄,從中學習運動家的精 神及努力不懈的態度;注重團隊合作及溝通協調,以發揮一加一大於二的 力量;培養美學鑑賞能力,以期望能夠達到實用與美感兼具,及不斷創新 的品質。因為這樣的人格特質,學生總是一直秉持積極樂觀,不怕失敗與 挫折,勇於接受各項挑戰的精神,再加上強烈的責任心及高度熱忱的態度, 努力認真的學習與生活,以期能取之於社會、用之於社會。