一個可做動態電壓/頻率調整且使用中繼器的匯流排電路設計

全文

(2) 一個可做動態電壓/頻率調整且使用中繼器 的匯流排電路設計 A Bus Circuit Design with Dynamic Voltage/Frequency Scaling and Repeater Insertion Student : Ya Ting Chen. 研 究 生:陳雅婷 指導教授:蘇朝琴 教授. Advisor : Chau Chin Su. 國 立 交 通 大 學 電機與控制工程研究所 碩士論文. A Thesis Submitted to Department of Electrical and Control Engineering College of Electrical Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Master in Electrical and Control Engineering October 2008 Hsinchu, Taiwan, Republic of China. 中 華 民 國 九 十 七 年 十 月.

(3) 一個可做動態電壓/頻率調整且使用中繼器 的匯流排電路設計. 研究生 : 陳雅婷. 指導教授 : 蘇朝琴 教授. 國立交通大學電機與控制工程研究所. 摘. 要. 本論文提出一使用嵌入式中繼器的匯流排電路,來降低全區域連接線時間延遲、功 率及面積消耗,並且利用一個時脈檢測電路來觀察訊號雜訊的大小,依照檢測訊號的不 同,我們可以分析出訊號是否適合在此電壓此頻率下工作。若不適合工作在此電壓或頻 率之下,再決定是要調整電壓,或調整資料傳送的頻率,來使得資料能夠正確的傳輸。. 在資料產生方面,使用偽隨機資料產生器來產生 8 筆並聯的偽隨機資料,並且同時 產生一時脈訊號 (用來做時脈檢測),觸發位置剛好切在資料的中間點,資料和時脈訊號 同時經過傳輸距離為 10mm 的匯流排電路,再由時脈檢測電路來檢測訊號的雜訊大小。 此晶片使用台積電 0.13 μ m RF CMOS 製程來實現。在 1.2V 的電源供應下,偽隨機資 料產生器的功率損耗約 1.36mW,傳輸線消耗功率約 22.18mW (每條消耗功率約 2.77mW),檢測電路的功率消耗約 9.75mW。. 關鍵字: 晶片內建匯流排,嵌入式緩衝器,動態電壓,動態頻率,時脈量測,抖動量測. iii.

(4) A Bus Circuit Design with Dynamic Voltage/Frequency Scaling and Repeater Insertion Student: Ya Ting Chen. Advisor: ChauChin Su. Department of Electrical and Control Engineering National Chiao Tung University. Abstract This thesis proposes a bus circuit using repeater insertion to reduce its power consumption and area. Moreover, we use a timing measurement circuit to estimate eye opening and jitter. According to the eye opening, we can determine if the supply voltage or the frequency is adequate for the task. If the supply voltage or the frequency disagrees with the task, we can dynamically change the supply voltage or the frequency to make the signal correctly transferred. For the data generation, a pseudorandom binary sequence generator has been used to generate eight parallel outputs and a divider to generate a clock signal. The clock’s trigger location is at the middle of pseudorandom data. The data and the clock have been transferred to the bus circuit which is 10mm in length. Finally, we use a timing measurement circuit to estimate the jitter. This chip is implemented in TSMC 0.13um RF CMOS process. On a 1.2V power supply, the PRBS generator consumes 1.36mW, the global interconnects consume 22.18mW (each interconnect consumes 2.77mW), and the timing measurement circuit consumes 9.75mW.. Keyword: on-chip bus, buffer insertion, dynamic voltage scaling, dynamic frequency scaling, timing measurement, jitter measurement.. iv.

(5) 誌. 謝. 首先要感謝的是我的指導教授 蘇朝琴教授,這兩年的辛勤教導,無論是在專業領 域的知識與技術,抑或是生活上為人處世的道理,都讓我獲益良多。 接下來要感謝的是博士班學長們:丸子學長、盈杰學長、鴻文學長、仁乾學長、煜 輝學長在我遇到研究上的困難時,給予我熱心的指導。還有實驗室碩士班學長姊們:小 馬、方董、議賢、村鑫、小潘潘、存遠、教主、snoopy,解決我在課業與研究上的疑惑。 實驗室的同學們與學弟們:子俞、碩廷、孔哥、挺毅、洲銘、于昇、家齊,在課業上互 相討論,生活上互相照顧與幫助。還要感謝助理雅雯和上容,對我的照顧及幫忙。 最後要感謝我的父親、母親、哥哥、妹妹們、以及男朋友玩具,感謝你們的鼓勵與 陪伴,讓我能夠順利的度過這兩年的碩士生涯。. 雅婷 2008/10/01. v.

(6) 目錄. 目錄 中文摘要 .................................................................................................................................. iii 英文摘要 .................................................................................................................................. iv 誌謝 ............................................................................................................................................v 目錄 .......................................................................................................................................... vi 表目錄 ........................................................................................................................................x 圖目錄 ...................................................................................................................................... xi. 第一章 ........................................................................................................................................1 緒論 ............................................................................................................................................1 1.1 簡介.................................................................................................................................1 1.2 研究動機.........................................................................................................................1 1.3 論文結構.........................................................................................................................2 第二章 ........................................................................................................................................4 背景回顧 ....................................................................................................................................4 2.1 艾莫爾延遲.....................................................................................................................4 2.2 切換活動因子.................................................................................................................5 2.3 延遲時間的最佳化.........................................................................................................5 2.4 功率消耗的最佳化.........................................................................................................7 2.5 功率消耗、延遲、傳輸速率的最佳化.........................................................................8 vi.

(7) 目錄 2.5.1 最佳傳輸線線寬...................................................................................................9 2.5.2 最佳傳輸線線寬和線距.....................................................................................10 2.6 總結...............................................................................................................................10 第三章 ......................................................................................................................................11 全區域連接線電路設計 ..........................................................................................................11 3.1 全區域連接線............................................................................................................... 11 3.2 模組參數....................................................................................................................... 11 3.3 全區域連接線的模組...................................................................................................12 3.3.1 中繼器模組.........................................................................................................12 3.3.2 晶片上連接線模組.............................................................................................15 3.4 全區域連接線的效能...................................................................................................16 3.4.1 時間常數.............................................................................................................16 3.4.2 上升時間.............................................................................................................17 3.4.3 傳輸速率.............................................................................................................17 3.4.4 功率消耗.............................................................................................................18 3.4.5 面積.....................................................................................................................21 3.4.6 總傳輸速率與總功率消耗的方程式.................................................................22 3.5 效能指數的最佳化.......................................................................................................22 3.5.1 最佳傳輸線寬度.................................................................................................22 3.5.2 最佳傳輸線線距.................................................................................................23 3.5.3 最佳的中繼器並聯個數.....................................................................................24 vii.

(8) 目錄 3.5.4 選擇中繼器的尺寸與傳輸線線距.....................................................................26 3.6 設計流程.......................................................................................................................27 3.7 設計參數值...................................................................................................................28 3.8 總結...............................................................................................................................28 第四章 ......................................................................................................................................29 時脈量測電路 ..........................................................................................................................29 4.1 前言...............................................................................................................................29 4.2 時脈量測電路...............................................................................................................30 4.2.1 邊緣偵測器.........................................................................................................30 4.2.2 延遲串列電路.....................................................................................................31 4.2.3 取樣電路.............................................................................................................31 4.2.4 時脈檢測器.........................................................................................................32 4.2.5 消除突波的取樣電路.........................................................................................33 4.3 時脈量測電路的操作...................................................................................................33 4.3.1 檢測訊號量測說明.............................................................................................34 4.3.2 檢測訊號的分析.................................................................................................35 4.4 總結...............................................................................................................................37 第五章 ......................................................................................................................................39 匯流排電路之實現 ..................................................................................................................39 5.1 偽隨機位元序列產生器...............................................................................................39 5.2 匯流排電路...................................................................................................................41 viii.

(9) 目錄 5.3 時脈量測電路...............................................................................................................42 5.4 輸出緩衝器與開汲極輸出...........................................................................................42 5.5 佈局圖和模擬結果.......................................................................................................44 5.5.1 晶片佈局圖.........................................................................................................44 5.5.2 佈局後模擬.........................................................................................................45 5.6 性能比較.......................................................................................................................51 5.7 量測考量.......................................................................................................................52 5.8 總結...............................................................................................................................53 第六章 ......................................................................................................................................54 結論 ..........................................................................................................................................54 6.1 結論...............................................................................................................................54 6.2 未來發展.......................................................................................................................54 參考文獻 ..................................................................................................................................55. ix.

(10) 表目錄. 表目錄 表格 3. 1 製程參數值..............................................................................................................12 表格 3. 2 設計參數值..............................................................................................................28 表格 4. 1 反相器的平均閘延遲..............................................................................................34 表格 4. 2 可量測傳輸速率的下限..........................................................................................34 表格 4. 3 檢測訊號 比對 取樣輸出訊號...............................................................................35 表格 4. 4 檢測訊號 比對 取樣位置點...................................................................................37 表格 5. 1 匯流排的各項參數值..............................................................................................42 表格 5. 2 供電源大小對應外部示波器振幅大小..................................................................43 表格 5. 3 各個腳位的屬性......................................................................................................45 表格 5. 4 不同供電源在不同 CORNER 下的抖動大小 ...........................................................46 表格 5. 5 各個電路的功率消耗與總功率消耗......................................................................47 表格 5. 6 電路規格表..............................................................................................................51 表格 5. 7 電路規格..................................................................................................................51 表格 5. 8 比較表......................................................................................................................52. x.

(11) 圖目錄. 圖目錄 圖 1. 1 晶片內部的模組互連線................................................................................................2 圖 1. 2 動態電壓/頻率調整電路...............................................................................................2 圖 2. 1 RC 階梯網路 ..................................................................................................................4 圖 2. 2 轉態關係圖....................................................................................................................5 圖 2. 3 以中繼器尺寸與分段連接線長度為函數之單位長度的時間常數............................6 圖 2. 4 以中繼器尺寸與分段連接線長度為函數之單位長度的功率消耗............................8 圖 2. 5 傳輸線線距對應單位線電容值....................................................................................9 圖 3. 1 使用中繼器的全區域連接線......................................................................................12 圖 3. 2 等效 RC 模組 ..............................................................................................................13 圖 3. 3 CMOS 反相器 和 MOS 的佈局圖 .............................................................................14 圖 3. 4 輸入輸出電容 c gs c db 與 輸出電阻 rs ....................................................................15 圖 3. 5 全區域連接線的切面圖..............................................................................................15 圖 3. 6 連接線的單位線電阻 rw 與 連接線的單位線電容 c w .............................................16 圖 3. 7 上升時間和資料週期..................................................................................................18 圖 3. 8 反相器的短路電流......................................................................................................19 圖 3. 9 傳輸線和中繼器的佈局擺放方式..............................................................................22 圖 3. 10 和傳輸線線寬與線距有關的效能............................................................................23 圖 3. 11 決定好傳輸線線寬的情況之下,與傳輸線線距有關的效能 ................................24 圖 3. 12 選擇中繼器的 MOS 並聯個數 .................................................................................25 xi.

(12) 圖目錄 圖 3. 13 選擇中繼器並聯個數................................................................................................25 圖 3. 14 不同中繼器尺寸,得到的傳輸線線距與傳輸速率的關係圖................................26 圖 3. 15 傳輸線各項參數的設計流程....................................................................................27 圖 4. 1 電路整體架構圖..........................................................................................................29 圖 4. 2 邊緣偵測器..................................................................................................................30 圖 4. 3 邊緣偵測器的輸出時序圖..........................................................................................31 圖 4. 4 延遲串列電路..............................................................................................................31 圖 4. 5 取樣電路......................................................................................................................32 圖 4. 6 時脈檢測器..................................................................................................................33 圖 4. 7 消除突波的取樣電路..................................................................................................33 圖 4. 8 取樣位置關係圖..........................................................................................................34 圖 4. 9 檢測訊號 OS1=0 ..........................................................................................................35 圖 4. 10 檢測訊號 OS1, OS2=0.................................................................................................36 圖 4. 11 檢測訊號 OS1, OS2, OS3=0 .........................................................................................36 圖 4. 12 檢測訊號 OS1, OS2, OS3, OS4=0 .................................................................................36 圖 4. 13 檢測訊號 OS1, OS2, OS3, OS4, OS5=0 .........................................................................37 圖 5. 1 PRBS 電路....................................................................................................................39 圖 5. 2 除頻器..........................................................................................................................40 圖 5. 3 PRBS 與除頻器的輸出訊號時序圖............................................................................40 圖 5. 4 PRBS 電路的輸出時脈波形圖....................................................................................41 圖 5. 5 PRBS 電路的輸出眼圖................................................................................................41 xii.

(13) 圖目錄 圖 5. 6 簡易的匯流排電路......................................................................................................42 圖 5. 7 簡易的時脈量測電路..................................................................................................42 圖 5. 8 輸出緩衝器..................................................................................................................43 圖 5. 9 使用輸出緩衝器及開汲極輸出,在外部示波器觀察波形......................................43 圖 5. 10 電路佈局圖................................................................................................................44 圖 5. 11 匯流排輸出模擬圖(VDD=1.2V, DATA RATE=2GBPS) ................................................45 圖 5. 12 匯流排輸出模擬圖(VDD=1.0V, DATA RATE=1.5GBPS) .............................................46 圖 5. 13 匯流排輸出模擬圖(VDD=0.8V, DATA RATE=1GBPS) ................................................46 圖 5. 14 匯流排輸出波形圖(VDD=1.0V, DATA RATE=2GBPS) ................................................47 圖 5. 15 時脈量測輸出結果(VDD=1.0V, DATA RATE=2GBPS) ................................................48 圖 5. 16 匯流排輸出波形圖(VDD=1.2V, DATA RATE=2GBPS) ................................................49 圖 5. 17 時脈量測輸出結果(VDD=1.2V, DATA RATE=2GBPS) ................................................49 圖 5. 18 匯流排輸出波形圖(VDD=1.0V, DATA RATE=1.5GBPS) .............................................50 圖 5. 19 時脈量測輸出結果(VDD=1.0V, DATA RATE=1.5GBPS) .............................................50 圖 5. 20 晶片量測架構圖........................................................................................................53. xiii.

(14) 第一章 緒論. 第一章 緒論. 1.1 簡介 由於電腦科技的蓬勃發展,資料的處理更加快速,以至於晶片上所要處理的資料越 來越多,速度也越快,在需求增加的情況下,有限的通道上要傳輸的資料也越多,所以 需要的資料傳輸速度相對來說會越來越大。 隨著製程技術不斷地演進,所有複雜的功能全部都整合在一個小晶片上。再加上現 在的製程尺寸越做越小,使得晶片內的通道距離更小,連接情況更複雜。衍生出的問題 主要可分為以下兩項: (1) 因為製程尺寸的縮小,雖然閘延遲 (Gate delay) 和區域連接 線延遲 (Local interconnect delay) 都變得比較小,但是全區域連接線延遲 (Global interconnect delay) 佔的比例卻越來越大,所以降低此延遲時間為首要問題。(2) 製程尺 寸縮小,連接線之間的距離變小,傳輸線之間的訊號發生耦合效應 (Coupling effect), 資料會互相影響,而降低此效應,使得訊號能正確的傳輸也是一個重要的難題。. 1.2 研究動機 雖然晶片面積會隨著製程縮小而變小,但隨著晶片內模組數目的增加,模組和模組 之間的互連線長度變長,見圖 1.1。為了推動全區域連接線,使訊號能夠順利傳送,必 須使用驅動電路來做驅動。於是我們選擇中繼器 (Repeater insertion) 來做為驅動電路。 1.

(15) 第一章 緒論 利用反相器 (Inverter) 電路將傳輸線 (Interconnect) 切成很多小段,來使整體的延遲變 小。. TX. SOC. RX. 圖 1. 1 晶片內部的模組互連線. 當需要資料傳輸的速度下降時,如果可以隨著資料傳輸的快慢,來調整供電源電壓 值的大小,就可藉此達到最佳功率消耗 (Optimal power consumption) 的效果。所以我們 在電路的後端,設計了一個時脈量測電路 (Timing measurement circuit),來檢測資料, 藉由輸出檢測訊號來估算抖動 (Jitter) 大小,並且依照目前工作的狀況,來決定要如何 調整電壓或傳輸速率 (增減電壓或是增減傳輸頻率),使電路達到最佳的耗電狀態 (低功 率消耗),見圖 1.2。. Supply. Clock. Voltage. Frequency. Circuit. Analysis. 圖 1. 2 動態電壓/頻率調整電路. 1.3 論文結構 本論文內容分成以下六個章節。第一章為緒論,說明傳輸線的發展現況,研究動機, 以及論文結構。第二章為背景回顧,探討一般 RC 傳輸線選擇參數值的方法。第三章介 紹選擇匯流排之各項參數的方法。我們使用最佳化的方式來求出傳輸線的寬度以及中繼 2.

(16) 第一章 緒論 器的並聯個數。並且在選擇傳輸速率的同時,決定了中繼器的尺寸和傳輸線的線距。這 個章節中還介紹了各個基本性能的計算方式:包含了時間常數、上升時間、傳輸速率、 功率消耗,和傳輸線面積。最後,依照設計流程圖來決定如何選擇傳輸線的寬度、傳輸 線的線距、中繼器的並聯個數、傳輸速率,以及中繼器的尺寸。第四章介紹了一個時脈 量測電路。這個電路包含了邊緣檢測器、延遲串列電路、取樣電路、時脈檢測器,和消 除突波的取樣電路。我們使用時脈量測電路的輸出檢測訊號,來估算出眼圖張口 (Eye opening) 的大小。依照這個眼圖張口的大小,再決定要如何調整供電壓或是傳輸速率, 來使電路工作在最適當的情況之下。第五章為匯流排電路設計的實現。整體電路架構包 含了偽隨機位元序列產生器 (PRBS),長度為 10mm 的全域傳輸線電路,以及用來做動 態電壓頻率調整的時脈量測電路。章節中還包括了晶片佈局圖、佈局後模擬、規格表、 比較表,以及量測考量。第六章為結論,討論電路設計結果,以及未來發展的方向。. 3.

(17) 第二章 背景回顧. 第二章 背景回顧. 2.1 艾莫爾延遲 使用艾莫爾延遲 (Elmore delay),我們可得到電路的一階時間常數 (First-order time constant) [1]。雖然這個數值只是一個從輸入點到輸出點之訊號傳輸延遲的近似值,但由 於容易求得且簡單易懂,所以一般都使用這個方法來求電路的時間常數。 在滿足以下三點的情形之下,我們可以使用艾莫爾延遲來算出 RC 樹狀網路 (RC tree network) 的時間常數。(1) 沒有電阻形成迴路,(2) 所有的電容都有一端接到地,(3) 電路中只有一個輸入點。 圖 2.1 為一 RC 樹狀網路的特例,是一個簡單的 RC 階梯網路 (RC ladder network), 使用艾莫爾延遲來算出它從輸入點到輸出點 (N) 的時間常數,如下列方程式所示 N. j. j =1. k =1. τ N = ∑ C j ⋅ ∑ Rk. Vin. R1. R2 C1. (2.1). RN. R3 C3. C2. 圖 2. 1 RC 階梯網路. 4. Vout CN.

(18) 第二章 背景回顧. 2.2 切換活動因子 CMOS 電路的切換功率消耗和切換活動因子 (Switching activity factor, α ) 有關 [1],而 α 代表的是輸出電容造成功率消耗的電壓轉態有效個數,我們可以由電路的邏輯 閘和輸入訊號來推算出轉態機率 (Transition probability)。 轉態機率可以用轉態關係圖來表示,我們可由圖 2.2 中看出輸出訊號 0 和 1 的轉換 關係。以一個反相器為例,輸出為 0 的機率為 P0 =. 1 1 ,輸出為 1 的機率為 P1 = ,則輸 2 2. 出端由訊號 0 變成 1 所產生之功率消耗的轉態機率為 P0→1 = P0 ⋅ P1 =. 1 1 1 ⋅ = 。 2 2 4. P0 × P1 P0 × P0. 0. 1. P1 × P1. P1 × P0 圖 2. 2 轉態關係圖. 2.3 延遲時間的最佳化 一般使用中繼器的 RC 連接線,通常都取延遲的最小極值來做最佳化,求出中繼器 尺寸和分段連接線的長度 [2]。只要已知傳輸線的單位線電容與單位線電阻,就可以得 到兩者的數值。 首先,使用艾莫爾延遲來估算出每一分段連接線 l 的時間常數,如下所示. τ=. (. ). rs r 1 c gs m+ c db m + s c w l + rw lm c gs + rw c w l 2 m m 2. (2.2). 所以單位長度的時間常數可以表示為. τ. (. ). r 1 1 = rs c gs + c db + s c w + rw m c gs + rw c w l 2 2 l l m 5. (2.3).

(19) 第二章 背景回顧 用圖形來表示,可以得到圖 2.3 的 3D 圖形。為了要求它的最小極值,所以對單位長度. ⎛τ ⎞ ⎛τ ⎞ ∂⎜ ⎟ ∂⎜ ⎟ l l 的時間常數做最佳化動作,令 ⎝ ⎠ = 0 和 ⎝ ⎠ = 0 ,最後得到最佳的中繼器尺寸與 ∂l ∂m 連接線的分段長度,如下所示. mopt =. rs c w rw c gs. lopt =. 2 ⋅ rs c gs + c db rw c w. (. (2.4). ). (2.5). 將 (2.4) 和 (2.5) 代入 (2.3) 中,可以得到最小單位長度的時間常數 ⎛τ ⎜ ⎝l. ⎛ c 1 ⎛⎜ ⎞ ⎜ 2 r c r c 1 + db = ⎟ s gs w w ⎜ 1 + 2 ⎜⎝ c gs ⎜ ⎠ opt ⎝. ⎞ ⎞⎟ ⎟ ⎟ ⎟⎟ ⎠⎠. (2.6). 由於分段連接線長度所造成的延遲時間,和時間常數有一乘數關係,所以可以得到 最小之單位長度的延遲時間為. (2.7). time constant (τ/ τopt ). ⎛ c db ⎞⎟ ⎞⎟ 1 ⎛⎜ ⎛τ ⎞ ⎜ log e 2 ⋅ ⎜ ⎟ 1+ = 2 ⋅ log e 2 rs c gs rw c w ⎜ 1 + 2 ⎜⎝ c gs ⎟⎠ ⎟⎟ ⎜ ⎝ l ⎠ opt ⎝ ⎠. (. segment length l l opt. ). (. repeater size m mopt. ). 圖 2. 3 以中繼器尺寸與分段連接線長度為函數之單位長度的時間常數 若將參數的電容電阻值代入 (2.4) 和 (2.5) 中,得到的中繼器尺寸很大,而分段長 6.

(20) 第二章 背景回顧 度也很長,造成總功率消耗大,所以在選擇中繼器尺寸和分段連接線長度時,除了延遲 時間的大小之外,還必須要考量到功率消耗的問題。. 2.4 功率消耗的最佳化 對功率消耗做最佳化動作,希望使功率消耗接近最小的狀態,進而求出中繼器的尺 寸和分段連接線的長度 [2]。此時的延遲並非最小值,而是取最小延遲的 (1 + f ) 倍。 只要知道連接線的單位線電容與單位線電阻的大小,就可以立刻得到兩者的數值。 功率消耗的方程式可以寫成 Prepeater = Pswitching + Pshort -circuit + Pleakage. (2.8). 其中. ((. ). ). Pswitching = α ⋅ m c db + c gs + c w l ⋅ V DD 2 f clk Pshort - circuit = α ⋅ V DD ⋅ Wn m⋅ I short - circuit ⋅ τ log e 3 Pleakage = V DD ⋅. (. (2.9). ). 1 I off nWn + I off pW p ⋅ m 2. 假設單位長度的時間常數的誤差值為 f ,所以單位長度的時間常數為. τ. ⎛τ = (1 + f ) ⋅ ⎜ l ⎝l. ⎞ ⎟ ⎠ opt. (2.10). 得到單位長度的功率消耗為. Prepeater l. (. ). m ⎞ ⎛m = k1 ⎜ cdb + c gs + c w ⎟ + k 2τ m+ k 3 l ⎠ ⎝l. (2.11). 用圖形來表示,可以得到圖 2.4 的 2D 圖形。 為了要求它的最小極值,所以對單位長度的功率消耗做最佳化動作,令. ⎛ Prepeater ∂⎜⎜ l ⎝ ∂l. ⎛ Prepeater ⎞ ⎜ ⎟ ∂ ⎜ ⎟ l ⎠ =0 和 ⎝ ∂m. ⎞ ⎟ ⎟ ⎠ = 0 ,並且使用牛頓法 (Newton-Raphson’s method) 來. 求得最佳的中繼器尺寸與連接線的分段長度的近似值。 7.

(21) power (P/l)/ (P/l) opt. 第二章 背景回顧. l/l. (. segment length l l opt. S/S. ). (. repeater size m mopt. ). 圖 2. 4 以中繼器尺寸與分段連接線長度為函數之單位長度的功率消耗. 2.5 功率消耗、延遲、傳輸速率的最佳化 除了延遲時間與功率消耗之外,傳輸速率的大小也是我們在設計傳輸線時的必須考 量的效能 (Performance) 之一。先假設延遲時間為最小極值,得到中繼器尺寸與分段連 接線長度的公式,見 (2.4) 和 (2.5),由於它們都是傳輸線的線電容與線電阻組成的方 程式,所以最後得到的各項效能都與連接線的線寬、線距有直接相關性。於是我們定義 了效能指數 (Figure-of-merit, FOM),找出在效能指數最大時的傳輸線線寬和線距,同時 得到低功率消耗、低延遲時間、和高傳輸速率。由於傳輸速率 B 和單位時間的延遲時間 成反比,可以定義為. B = n⋅. 1 D. (2.12). 其中,n 為傳輸線的數目,而功率消耗和延遲時間的大小,見 (2.6) 和 (2.11)。最後, 定義效能指數為. F=. B D. (2.13). 使用兩種方式,來求傳輸線的最佳參數值。其中一種假設傳輸線線距為定值,來. 8.

(22) 第二章 背景回顧 求傳輸線的最佳線寬;另外一種方式,則是同時求傳輸線的線寬和線距。. 2.5.1 最佳傳輸線線寬 假設傳輸線之線距為一定值,求最佳傳輸線線寬,來達到最大效能指數[3][4]。 (1) 最小線距 ( S = S min )。目的是為了觀察在固定的耦合效應 (Cross-talk effect) 之下, 變化傳輸線的線寬大小,對各項性能所造成的影響。傳輸線的線寬增大時,單位線 電容成正增加,見圖 2.5(a)。 (2) 線距等於線寬 ( S = W )。傳輸線線寬在增大過程中,有單位線電容的最小極值出現, 見圖 2.5(b)。 在兩種不同傳輸線線距之下,取效能指數的最大值,求出最佳傳輸線線寬。傳輸速率和 延遲時間都與線寬 (W) 和線距 (S) 有關,所以令. c a S + cc cb. (2.14). cw (fF/um). cw (fF/um). Wopt =. ∂F = 0 ,來得到最佳傳輸線線距為 ∂W. W (um). W (um). (a)當 S = S min 時的單位線電容. (b)當 S = W 時的單位線電容. 圖 2. 5 傳輸線線距對應單位線電容值. 9.

(23) 第二章 背景回顧. 2.5.2 最佳傳輸線線寬和線距 因為線距的大小,和單位線電容有很大的關係,只要線距有所變化,即使只有一點 點,都會造成各項效能的變化,所以我們同時來求最佳傳輸線線寬和線距 [5]。取效能 指數的最大極值,令. ∂F ∂F =0 與 = 0 ,來得到最佳的線寬和線距為 ∂W ∂S. Wopt =. S opt =. ca S opt + cc cb ccWopt c a + cbWopt. (2.15). (2.16). 求得的最佳傳輸線線寬和線距,必須滿足 Wopt ≥ Wmin 和 S opt ≥ S min 。. 2.6 總結 本章節中,回顧了全區域傳輸線歷年來的文獻,除了介紹了一般 RC 連接線之時間 常數的求法,與 CMOS 電路中切換活動因子的估算方式,還回顧了一般選擇連接線參 數值的各項方法。主要是利用最佳化的方式來選擇中繼器尺寸、連接線的分段長度、傳 輸線線寬與傳輸線線距。可以自己設定效能指數來決定要對哪些效能做最佳化的動作, 進而得到最佳的參數值。. 10.

(24) 第三章 全區域連接線電路設計. 第三章 全區域連接線電路設計. 3.1 全區域連接線 本章節主要決定全區域連接線的各項參數值。在 3.2 節可看到不同製程下的模組參 數值。而 3.3 節介紹了中繼器模組和晶片上連接線模組。3.4 節分析了全區域連接線的效 能。在 3.5 節中,我們用最佳化的方法,讓效能指數 (FOM) 為最大值,來得到最佳的 傳輸線寬度,並且在選擇傳輸速率時,決定傳輸線的線距。在此章節中,介紹了一個對 於傳輸速率、功率消耗、以及傳輸線面積做最佳化的方法,來決定連接線的各項參數值, 以及中繼器電路的尺寸。. 3.2 模組參數 製程 350nm 到 90nm 的技術參數以及等效電路參數,如表格 3.1 所示。這些模組參 數 (Model parameter) 是 由 台 積 電 (Taiwan Semiconductor Manufacturing Company,. TSMC) 的資料庫,以及國際半導體技術藍圖 (International Technology Roadmap for Semiconductors, ITRS) 的資料庫所獲得。其中,T 為傳輸線厚度 (Metal thickness),Wmin 為最小傳輸線寬度 (Minimal metal width), S min 為最小傳輸線線距 (Minimal metal spacing), ρ 為傳輸線的電阻率 (Metal resistivity), ca 、 cb 、 cc 分別為傳輸線的側面電 容與邊緣電容、傳輸線與基板間的平行板電容、傳輸線之間的耦合電容, V DD 為供電 源電壓值 (Power supply voltage)。 11.

(25) 第三章 全區域連接線電路設計 表格3. 1 製程參數值 Tech. Node. 350. 180. 130. 90. T (nm). 6400. 5300. 3700. 2250. Wmin (um). 0.6. 0.28. 0.2. 0.14. Smin (um). 0.5. 0.28. 0.21. 0.14. ρ (10-8Ω‧m). 2.2. 2.2. 2.2. 2.2. cb (fF/um2). 0.0124. 0.039. 0.053. 0.065. ca (fF/um). 0.0112. 0.05. 0.07095. 0.05824. cc (fF). 0.162. 0.09. 0.046. 0.029. VDD (V). 3.3. 1.8. 1.2. 1. (nm). 3.3 全區域連接線的模組 我們可以將全區域連接線的模組可以分成兩個部份,包含了中繼器模組,以及晶片 上連接線模組,將在以下章節介紹。. 3.3.1 中繼器模組 使用中繼器的全區域連接線,如圖 3.1 所示 [5]。其中, L 為傳輸線的總長度, l 為 分段傳輸線長度, W 為傳輸線的寬度, S 為傳輸線之間的距離。每一個中繼器模組 (Repeater model),都是由分段傳輸線,與連接在它前後的兩個反相器所構成的。 L l l. l. S. W. l l. l. 圖 3. 1 使用中繼器的全區域連接線 中繼器模組,可以等效成一個 RC 模組,如圖 3.2 所示。反相器在並聯個數為 m = 1 12.

(26) 第三章 全區域連接線電路設計 時,等效的參數值: c gs 為輸入電容, c db 為輸出電容,而 rs 為輸出阻抗。當中繼器的 並聯個數為 m 時,則它的總輸入電容為 C gs = c gs ⋅ m ,總輸出電容為 C db = c db ⋅ m ,總 輸出阻抗為 Rs = rs m 。. inv output Rs = rs / m V DD. inv input rw ⋅ l. C db = c db ⋅ m. VO. cw ⋅ l. C gs = c gs ⋅ m. 圖 3. 2 等效 RC 模組. 反相器的輸入電容與輸出電容 [1],以及輸出阻抗的方程式可以寫成. c gs = ⎛⎜ c gs + c gs ⎞⎟ + ⎛⎜ c gd + c gd ⎞⎟ + ⎛⎜ c gb + c gb ⎞⎟ ,n ,p ⎠ ⎝ ,n ,p ⎠ ⎝ ,n ,p ⎠ ⎝ ≅ C ox ⋅ W n ⋅ Ln + C ox ⋅ W p ⋅ L p. c db = c db ,n + c db , p. ( (. ). = An ⋅ C j ,n ⋅ K eq ,n + Pn ⋅ C jsw ,n ⋅ K eqsw ,n + A p ⋅ C j , p ⋅ K eq , p + Pp ⋅ C jsw , p ⋅ K eqsw , p. rs =. (3.1). (3.2). ). rs ,n + rs , p 2. (3.3). 其中. (. An( p ) = Wn( p ) ⋅ Yn( p ) + Wn( p ) ⋅ X j ,n( p ). K eq ,n ( p ) = −. K eqsw,n( p ) = − rs ,n =. Pn( p ) = 2 ⋅ Yn( p ) + Wn( p ). (. 2 φ0 ,n( p ) φ0 ,n( p ) + V DD − φ0 ,n( p ) + VSS − V DD − (− VSS ). ). ). 2 φ0 SW ,n( p ) φ0 SW ,n( p ) + V DD − φ0 SW ,n( p ) + VSS − V DD − (− VSS ). (. 2 ⋅ V DD. rs , p =. β n ⋅ (V DD − Vt ,n ). 2. 13. (. 2 ⋅ V DD. β p ⋅ V DD − Vt , p. )2. ).

(27) 第三章 全區域連接線電路設計 如圖 3.3 所示, Wn( p ) 為反相器的通道寬度 (Channel width), L n( p ) 為反相器的通道 長度 (Channel length), X j ,n( p ) 為反相器的接面深度 (Junction depth), Yn( p ) 為擴散區域 的長度 (Typical diffusion region length), C ox 為單位面積的閘氧化層電容 (Gate oxide capacitance per unit area), An( p ) 為接面面積 (Junction area), Pn( p ) 為 MOS 的汲極或源 極周長 (Perimeter), C j ,n( p ) 為單位面積的接面電容 (Junction capacitance per unit area), C jsw ,n( p ) 單位長度的側面接面電容 (Sidewall junction capacitance per unit length), K eq ,n( p ) 為電壓等效因子 (Voltage equivalence factor), K eqsw,n( p ) 為側面電壓等效因子. (Sidewall voltage equivalence factor), φ0 ,n( p ) 為內建接面電壓 (Built-in junction potential), φ0 sw ,n( p ) 為側面內建接面電壓 (Sidewall built-in junction potential), rs ,n( p ) 為 輸出阻抗。. C gs,n Yn( p ) Ln( p ). Vin. C gd, p. C gd,n. C db, p. Vout. Wn ( p ). C db,n. ro C gs, p. Xj ,n ( p ). 圖 3. 3 CMOS 反相器 和 MOS 的佈局圖. 我們可以用 MATLAB 畫出反相器的輸入輸出電容 c gs c db 與輸出電阻 rs 的 2D 圖 形,如圖 3.4 所示。隨著電壓大小的不同,可得到不同的 c gs 、 c db 、 rs (此時使用最小 尺寸的中繼器)。當 V DD 越大時, rs 會越小。 連接線的單位線電阻 (Resistance per unit length, rw ) 和單位線電容 (Capacitance per unit length, c w ) 兩項參數值,都可以由計算來得到。假使每一小段的長度為 l ,則它傳 輸線的電容為 C w = c w ⋅ l ,傳輸線的電阻為 Rw = rw ⋅ l 。 14.

(28) Capacitance (fF). Resistance (ohm). 第三章 全區域連接線電路設計. VDD (V). VDD (V). 圖 3. 4 輸入輸出電容 c gs c db 與 輸出電阻 rs. 3.3.2 晶片上連接線模組 晶片上連接線模組 (On-chip interconnect model) 如圖 3.5 所示,其中, W 為傳輸線 寬度 (Interconnect width), S 為傳輸線之間的距離 (Interconnect spacing), T 為傳輸線的 厚度 (Interconnect thickness),而 H 為傳輸線和基板之間的距離 (Dielectric height),c a 為 側邊電容 (Fringing-field capacitance), cb 為傳輸線和基板之間的平行板電容 (Parallel plate capacitance),而 cc 為傳輸線之間的耦合電容 (Coupling capacitance)。. W S. Tox. Ca Cc Ca. T. Cb Cb. Ca Cc Ca. 圖 3. 5 全區域連接線的切面圖. 我們可以將傳輸線的單位線電阻表示為. rw =. ρ W ⋅T. (3.4). 其中, ρ 為傳輸線的電阻率。用 MATLAB 畫出 rw 的 2D 圖,如圖 3.6 所示。當 W 上升 時, rw 會下降。 15.

(29) 第三章 全區域連接線電路設計 根據表格 3.1 的 0.13um 製程,可以得到 ca 、 cb 、 cc 的數值。而傳輸線的單位線電 容,可以表示為 c c w = c a + cb ⋅ W + c S. (3.5). cw (fF/um). r w (ohm/um). 用 MATLAB 畫出 c w 的 3D 圖,如圖 3.6 所示。當 W 上升或 S 下降時, c w 會持續上升。. S (um) W (um). W (um). 圖 3. 6 連接線的單位線電阻 rw 與 連接線的單位線電容 c w 對於 0.13um 製程,Metal2~Metal6 的最小線寬為 0.2um,最小的線距為 0.21um。分 析傳輸線的各項效能,如傳輸頻率、功率消耗,以及傳輸線面積。取效能指數的最大值 來做最佳化動作,即可決定最佳的連接線寬度和連接線的線距。. 3.4 全區域連接線的效能 在本節中,分析全區域連接線的各項效能,包含時間常數、上升時間、傳輸速率、 功率消耗,以及傳輸線面積。. 3.4.1 時間常數 根據圖 3.2,我們使用艾莫爾延遲模組來估算時間常數 (Time constant),表示式為. τ = Rs ⋅ (C gs + C db + c w ⋅ l ) + rw ⋅ l ⋅ C gs + rw ⋅ l ⋅ c w ⋅ l 1 2. (. ). 1 ⎛ r ⋅c ⎞ = rs c gs + cdb + ⎜ s w + rw c gs ⋅ m ⎟ ⋅ l + rw ⋅ c w ⋅ l 2 2 ⎝ m ⎠ 16. (3.6).

(30) 第三章 全區域連接線電路設計. 3.4.2 上升時間 因為中繼器模組可以等效成一個 RC 模組 ( τ = R ⋅ C ),我們使用簡單的 RC 電路來 得到上升時間 (Rise time)。假設電容一開始已放電到低電位,且輸入訊號為一個在 t = 0 的上升步階脈衝 (Rising step pulse),則此 RC 電路的輸出電壓波形可以表示為. (. V p = V DD ⋅ 1 - e -tp/RC. ). (3.7). 當 t = t p 的時候,上升輸出電壓充電到 V p ,而上升時間 t p 可以寫成. ⎛ V DD t p = ln⎜ ⎜ V DD − V p ⎝. ⎞ ⎟ ⋅ RC ⎟ ⎠. (3.8). tr (20% ~ 80% ) 定義為輸出電壓從 V20% 充電到 V80% 所需要的時間,而電壓位準 V20% 和. V80% 可以寫成. (. ). (3.9). (. ). (3.10). V20% = V DD ⋅ 1 − e −t1 RC V80% = V DD ⋅ 1 − e −t2 RC. 於是我們可以得到輸出的上升時間 tr (20% ~ 80% ) ,如下面的方程式所示. ⎡ ⎛ 1 ⎞ ⎛ 1 ⎞⎤ t r (20% ~ 80% ) = t 2 − t1 = ⎢ln⎜ ⎟ − ln⎜ ⎟⎥ ⋅ τ ≅ 1.386τ ⎝ 1 − 0.2 ⎠⎦ ⎣ ⎝ 1 − 0.8 ⎠. (3.11). 由 (3.11) 可以發現,上升時間和時間常數有一個常數乘積的關係。. 3.4.3 傳輸速率 假 設 上 升 時 間 tr (20% ~ 80% ) 佔一個資料週期的 0.15UI,如圖 3.7 所示。我們可以將 此關係寫成. t r (UI ) ≤ 0.15. 17. (3.12).

(31) 第三章 全區域連接線電路設計 接著,我們得到傳輸速率 (Data rate) 和上升時間的關係. Data Rate ≤. 0.15 tr. (3.13). 1UI. 0.15UI. 圖 3. 7 上升時間和資料週期. 因為我們在前面已求出上升時間,將上升時間和時間常數的關係式 (3.11) 代入 (3.13) 中,所以最後可以將傳輸速率寫成. Data Rate ≤. 0.15 0.108225 = τ 1.386 ⋅ τ. (3.14). 3.4.4 功率消耗 當製程尺寸持續下降,總功率消耗不能只估算切換功率消耗,漏電流造成的功率消 耗急速增加,以及短電路功率消耗佔據整個總功率消耗的大小也會變得顯著。總功率消 耗包含的三項功率消耗如下所示 [1] [6]。 (1) 切換功率消耗 (Switching power dissipation) 切換功率消耗, Psw ,因 CMOS 電路的輸出電容充放電所造成。輸出電容為 C load , 是由中繼器的輸出寄生電容、連接線的電容、以及中繼器的輸入電容所組成。 當輸入訊號在下降轉態時 (Falling transition),PMOS 電晶體導通 (Turn-on) 而 NMOS 電晶體關閉 (Turn-off),有一電流路徑從供電電壓對 C load 充電到高電位 V DD 。 在對輸出電容充電的期間,供電源所消耗的能量為 C load ⋅ V DD 2 。其中一半的能量儲存 到電容 C load 中,另外一半的能量被 PMOS 電晶體的寄生電容和連接線的電容消耗掉。 當輸入訊號在上升轉態時 (Rising transition),NMOS 電晶體導通而 PMOS 電晶體關 18.

(32) 第三章 全區域連接線電路設計 閉,在輸出電容到地之間有一電流路徑產生。原本在輸出電容上的能量 21 ⋅ C load ⋅ V DD 2 從 NMOS 電晶體放電到地。當輸入訊號在上升轉態的時候,供電源沒有能量被消耗掉。而 切換功率消耗可以被寫成. Psw = α 0→1 ⋅ V DD 2 ⋅ Cload ⋅ f clk. (. (3.15). ). = α ⋅ V DD 2 c gs + c db + l⋅ c w ⋅ m⋅ f clk. 其中, α 為切換活動因子,在章節 2.2 中介紹,代表在一時間週期裡,在輸出電容上造 成功率消耗的電壓轉態次數。 f clk 為時脈頻率 (Clock frequency)。 (2) 短路電流功率消耗 (Short-circuit power dissipation) 短路電流功率消耗, Psc ,當輸入訊號轉態時,由於供電源和地之間有一直接電流 路徑產生,所造成的功率消耗。這個電流路徑發生在 PMOS 和 NMOS 都導通的情況之 下。 圖 3.8 為反相器的輸入訊號轉態所造成的電流圖。輸入訊號在上升轉態,當輸入電 壓上升至 Vin = Vt,n ( t = t1 ) 時,NMOS 導通,產生一直接電流路徑從供電源到地;而 PMOS 在輸入電壓上升至 Vin = V DD - Vt, p. ( t = t 3 ) 時會關閉,此電流路徑消失。. Vin. T. V DD V DD − Vtp Vin. Vout I sc. Vtn. Time. I sc I max I mean tr. tf. Time. 圖 3. 8 反相器的短路電流. 假使反相器電路為一對稱反相器,則它的上升時間和下降時間相等 ( t r = t f ), PMOS 和 NMOS 的門檻電流相同 ( Vt = Vt,n = Vt, p ),以及 β = β n = β p 。當 Vin = V DD 2 19.

(33) 第三章 全區域連接線電路設計 ( t = t 2 ) 時,電流大小為 I max 。電流的方程式可以寫成. I (t ) =. β 2. (vin (t ) - vt )2. for 0 < I < I max. (3.16). 平均短路電流可以被算出,如下所示. I mean = α ⋅. β 12 ⋅ V DD. (V DD - 2Vt )3 τ. Tclk. (3.17). 我們可以得到短路電流功率消耗. Psc = V DD ⋅ I mean = α ⋅. β 12. (V DD - 2Vt )3 ⋅ τ ⋅ f clk. (3.18). 其中. ⎛W ⎝L. β = μcox ⎜. ⎞ ⎟⋅m ⎠. β 為一個和電晶體尺寸成比例的常數, Vt 為 NMOS 和 PMOS 的門檻電壓, τ 為輸入訊 號的上升時間與下降時間, α 為反相器輸出的平均轉態次數,而 f clk 為時脈頻率。 (3) 漏電流功率消耗 (Leakage power dissipation) 漏電流功率消耗, Pleakage ,由兩種漏電流所造成的功率消耗。其中一種是二極體 逆偏漏電流 (Reverse-bias diode leakage current),透過電晶體的汲極 (Drain) 漏電;而另 一種為次門檻電流 (Sub-threshold current),在電晶體關閉時,透過電晶體通道漏電。 二極體逆偏漏電流發生的主要成因:由於電晶體的汲極和基底 (Bulk) 之間形成一 逆偏壓的 pn 接面,如同一個二極體,產生一漏電流從電源由汲極流到基底。這個逆偏 漏電流的大小可以用方程式寫成. ⎛ Vbias ⎞ ⎜ V ⎟ I reverse = A ⋅ J s ⋅ ⎜ e T − 1⎟ ⎜ ⎟ ⎝ ⎠. (3.19). 其中, Vbias 為接面上的逆偏電壓 (Reverse-bias voltage), J s 為逆偏飽和電流密度 (Reverse saturation current density), A 為接面面積,而 VT = kT q 為熱電壓 (Thermal voltage)。 20.

(34) 第三章 全區域連接線電路設計. 次門檻電流的發生主因:電晶體在弱反轉 (Weak insertion) 時,載子由源極 (Source) 流到汲極的擴散電流。此時的 MOSFET 的工作特性與一個雙載子電晶體 (Bipolar transistor,BJT) 電路非常相似,次門檻電流和閘極門檻呈指數關係。當閘極對源極電壓 比門檻電壓低的時候,此電流將會變得很明顯。次門檻電流可以表示為. I sub = K. Vgs −Vt ⋅ e nVT. Vds ⎛ − ⎜ ⋅ ⎜ 1 − e Vt ⎜ ⎝. ⎛ W = ⎜⎜ μ n c ox ⋅ m⋅ n ⋅ vt Ln ⎝. ⎞ ⎟ ⎟ ⎟ ⎠. Vgs −Vt 2 ⎞⎟ ⋅ e nVT. ⎟ ⎠. Vds ⎛ − ⎜ ⋅ ⎜ 1 − e Vt ⎜ ⎝. ⎞ ⎟ ⎟ ⎟ ⎠. (3.20). 其中, K 為一個和製程有關的方程式,Vt 為門檻電壓,而 n = 1 + Ω ⋅ t ox D ,其中, t ox 為 閘氧化層厚度 (Gate oxide thickness), D 為通道深度寬 (Channel depletion width),而. (. ). Ω = ε si ε ox 。當 Vds >> VT 時, 1 - e -Vds VT ≅ 1,此時汲極到源極的漏電流與汲極對源極 電壓無關。最後,漏電流功率消耗可以被寫成 Pleakage = V DD ⋅ (I reverse + I sub ). (3.21). Prepeater = Psw + Psc + Pleakage. (3.22). 每一中繼器的總功率消耗為. 切換功率消耗大約佔了總功率消耗的 84%,而短路電流功率消耗大約佔總功率的 15%,漏電流大小大約佔總功率的 1%。. 3.4.5 面積 傳輸線和中繼器的佈局擺放方式如圖 3.9 所示。我們在畫佈局圖時,將傳輸線放置 在中繼器的上方,目的是為了降低整體的面積大小。所以在估算面積的時候,只需要考 慮傳輸線的面積。面積的大小可以表示為. Ach = (n × W + (n − 1) × S ) × L. 21. (3.23).

(35) 第三章 全區域連接線電路設計. L W S n inverters. interconnect. 圖 3. 9 傳輸線和中繼器的佈局擺放方式. 3.4.6 總傳輸速率與總功率消耗的方程式 因為匯流排總共包含了 n 條並聯的傳輸線,每一條傳輸線的傳輸速率大小如 (3.14) 所示,所以總傳輸頻率 (Total bandwidth) 可以被寫成. BW = n × (Data Rate ) = n ×. 0.108225. τ. (3.24). 每一傳輸線分成 L l 段,n 條傳輸線的總功率消耗 (Total power consumption) 為. (. ⎛L⎞ P = n ⋅ ⎜ ⎟ ⋅ Psw + Psc + Pleakage ⎝l⎠. ). (3.25). 3.5 效能指數的最佳化 在設計全區域連接線時,我們希望能夠同時得到高傳輸頻率、小面積、低功率消耗, 所以使用效能指數 (FOM) 來求極值做最佳化的動作。. 3.5.1 最佳傳輸線寬度 由於傳輸線的單位線電容電阻是由它的寬度與線距的方程式所得到,而各項效能 (如傳輸頻率、功率消耗) 都與傳輸線單位線電容電阻有關,所以可得知這些效能都是由 傳輸線寬度與線距的方程式所構成,相關計算請參照第三章第四節。因為在傳輸速率、 功率消耗、以及面積之間,有折衷 (Trade-off) 的關係,所以定義一 FOM 方程式,希望 22.

(36) 第三章 全區域連接線電路設計 能同時達到高傳輸速率、低功率消耗、與小面積消耗。 FOM 的方程式可以表示成. FOM =. Data Rate Pch ⋅ Ach. (3.26). 假設供電源為 VDD = 1.2V ,分段長度 l = 100um ,使用最小尺寸的中繼器。傳輸速率和 傳輸線線寬與線距的關係圖,如圖 3.10 (a) 所示,在 W = 0.2um 且 S = 1um 時有最大的 傳輸頻率,但傳輸線的面積此時有點大,如圖 3.10 (b) 所示。每一條傳輸線的功率消耗 如圖 3.10 (c) 所示,它的功率消耗會隨著傳輸線線寬增加而上升。 FOM 值如圖 3.10 (d). Area (channel). Data Rate (Gbps). 所示,在線寬 Wopt = 0.2um 時,可以得到最大的 FOM 值。. S (um). W (um). S (um). (b)總傳輸線面積. FOM. Power (mW). (a)每一條傳輸線的傳輸速率. W (um). S (um). S (um). W (um). (c)每一條傳輸線的功率消耗. W (um). (d) FOM. 圖 3. 10 和傳輸線線寬與線距有關的效能. 3.5.2 最佳傳輸線線距 我們將前面所得到的最佳傳輸線線寬帶入 (3.26) 中,可以得到傳輸線線寬和各項 效能的關係圖,如圖 3.11 (a)~(d) 所示。當傳輸線線距為 S = 0.26um 時,可以得到最大 23.

(37) 第三章 全區域連接線電路設計 的 FOM 值。傳輸線的線距越大,得到的傳輸速率會越大。由於我們必須考量到傳輸速. Area (channel). Data Rate (Gbps). 率的大小,所以我們稍後在選擇中繼器尺寸時,才來選擇傳輸線的線距。. S (um). S (um). (b)總傳輸線面積. FOM. Power (mW). (a)每一條傳輸線的傳輸速率. S (um). S (um). (c)每一條傳輸線的功率消耗. (d) FOM. 圖 3. 11 決定好傳輸線線寬的情況之下,與傳輸線線距有關的效能. 3.5.3 最佳的中繼器並聯個數 現在,我們要決定每個中繼器所並聯的 MOS 個數 (The number of MOS finger)。如 圖 3.12 所示,我們假設每一分段長度 l = m × h , h = 50um ,而傳輸線線寬為 0.2um, 傳輸線線距為 0.26um,傳輸速率為 2Gbps,且使用最小的中繼器尺寸 ( L n = L p = 0.13um , Wn = 0.4um , Wp = 1.7um ),則 MOS 並聯個數多大的時候,可以同時得到低功率消耗. 與低上升時間。我們定義 FOM1 方程式為. FOM 1 =. 1 Pch × t r (20% ~ 80% ). 24. (3.27).

(38) 第三章 全區域連接線電路設計 1cm m=1. m=1. In. h. m=1 100f. m=2. m=2. In. m=2. 2h. 2h. m=2 100f. m=a In. m=1. h. m=a. m=a. a*h. a*h. m=a 100f. 圖 3. 12 選擇中繼器的 MOS 並聯個數. 我們模擬 MOS 並聯個數由 1 到 4,得到圖 3.13 (a)~(c)。在並聯個數上升時,功率. Power (mW). tr (20%~80%) (ps). 消耗有非常微幅的上升,上升時間也會變大,所以最後在 m = 1 時,得到最大的 FOM1 值。. MOS finger (m=?). MOS finger (m=?). (b)傳輸線的上升時間(20%~80%). FOM. (a)每一條傳輸線的功率消耗. MOS finger (m=?). (c) 傳輸線的 FOM1 值 圖 3. 13 選擇中繼器並聯個數. 25.

(39) 第三章 全區域連接線電路設計. 3.5.4 選擇中繼器的尺寸與傳輸線線距 假設總全區域連接線長度 L = 10000um ,每一分段長度 l = 100um ,使用的傳輸線線 寬為 W = 0.2um ,MOS 電晶體的通道長度 L n = L p = 0.13um ,中繼器並聯個數 m = 1 。 我們將如何選擇中繼器的尺寸和傳輸線的線距,來達到所需要的傳輸速率大小? 我們模擬了三種中繼器尺寸來做傳輸速率的比較 (a) Wn = 0.4um, Wp = 1.7um. (b) Wn = 0.6um, Wp = 2.6um (c) Wn = 0.8um, Wp = 3.4um ,模擬圖如圖 3.14 (a)~(c) 所 示。我們發現在 NMOS 的通道寬度 Wn = 0.8um 且 PMOS 通道寬度 Wp = 3.4um 時,若 傳輸線線距為 S = 0.4um ,在供電電壓為 1.2V 的情況之下,可以得到 2.5Gbps 的傳輸速. Data Rate (Gbps). Data Rate (Gbps). 率。. S (um). S (um). (b) Wn=0.6um, Wp=2.6um. Data Rate (Gbps). (a) Wn=0.4um, Wp=1.7um. S (um). (c) Wn=0.8um, Wp=3.4um 圖 3. 14 不同中繼器尺寸,得到的傳輸線線距與傳輸速率的關係圖 26.

(40) 第三章 全區域連接線電路設計. 3.6 設計流程 全區域連接線之各參數值的設計流程 (Design flow) 如下圖 3.15 所示。. Starting the bus circuit design. To choose process technology (obtain ca , cb , cc ). Choose the optimal interconnect width for the maximal FOM (obtain rw ). Choose the MOS finger of the repeater for the maximal FOM1. Choose the repeater size and the interconnect spacing when the data rate has be selected (obtain c gs , c db , rs , c w ). Ending the bus circuit design. 圖 3. 15 傳輸線各項參數的設計流程. 27.

(41) 第三章 全區域連接線電路設計. 3.7 設計參數值 根據傳輸線的設計流程圖,可以得到傳輸線電路的各項參數值,如表格 3.2 的設計 參數值 (Design parameter) 所示。. 表格 3. 2 設計參數值. Parameter. Value. Number of interconnects. 9 (Data:8 , Clock:1). Global interconnect length. 10000um. Each segment length. 100um. Number of repeaters. 100. Interconnect width/spacing. 0.2um / 0.4um. PMOS. Lp=0.13um , Wp=3.4um. NMOS. Ln=0.13um , Wn=0.8um. 3.8 總結 在本章節中,我們利用一最佳化的動作,來求出全區域傳輸線的參數值,並且列出 了整個設計的流程圖。我們對傳輸線線寬以及中繼器並聯個數做最佳化的動作,來求出 最佳線寬與並聯個數。最後,在選擇傳輸速率大小的同時,決定中繼器的尺寸以及傳輸 線的線距。. 28.

(42) 第四章 時脈量測電路. 第四章 時脈量測電路. 4.1 前言 我們的整體電路架構圖如圖 4.1 所示,先用偽隨機位元序列產生器 (Pseudo random. binary sequence generator, PRBS) 產生 8 筆並聯的偽隨機訊號 (Parallel pseudorandom data) 為 d0~d7,在產生偽隨機訊號的同時,我們用除頻器 (Divider) 產生了一個在偽隨 機資料中間點轉態的時脈訊號 ick。. CLK Freq.. VDD1. VDD2. VDD3. BUS (On-chip global interconnect). d0~d7 …. …. ick. o6 …. PRBS & Divider. ock. Timing Meas. Circuit. os1~os5. Logic Analysis. L=10000um. Inside. Outside. 圖 4. 1 電路整體架構圖. 將偽隨機訊號與時脈訊號輸入匯流排 (BUS) 中傳輸,取出其中一筆輸出訊號 o6 和 輸出時脈訊號 ock,傳到時脈量測電路中做檢測。得到的檢測訊號 os1~os5 可以用來估 算出眼圖張口 (Eye opening),進而估算出抖動 (Jitter) 的大小。根據眼圖張口的大小, 29.

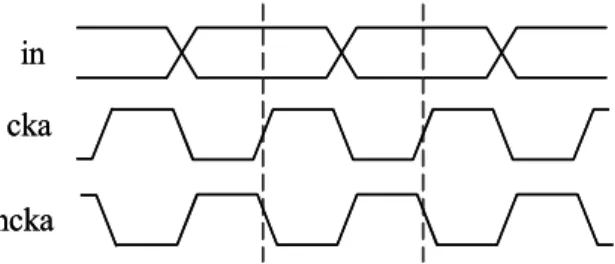

(43) 第四章 時脈量測電路 來決定要如何調整供電壓或是時脈頻率,來改善眼圖張口。. 4.2 時脈量測電路 PRBS 的輸出訊號 d0~d7 和時脈訊號 ick 經過 10mm 的匯流排傳輸通道之後,取出 輸出訊號 o6 和輸出時脈訊號 ock,傳到時脈量測電路中做檢測。而時脈量測電路中包含 了邊緣偵測器、延遲串列電路、取樣電路、時脈檢測器,以及消除突波的取樣電路。. 4.2.1 邊緣偵測器 圖 4.2 中,先將訊號經過緩衝器 (Buffer),得到時脈訊號 ck0 和訊號 in0。為了使時 脈在正負轉態的時候都可以對訊號做取樣的動作,將時脈經過一邊緣偵測器 (Edge. detector)。將時脈 ck0 經過反相器產生閘延遲 (Gate delay),再經互斥閘 (XOR),產生時 脈 ckb,使得原本的時脈無論在正邊緣或是負邊緣都可以對資料作取樣動作。. ck0 ck0 (Δt) ckb ock. Buffer. ckb. ck0. ncka. o_data. Buffer. in0. o_data in. ock. 圖 4. 2 邊緣偵測器. 為了讓時脈訊號 ckb 正緣仍對準資料的中間點,我們也同時將訊號 in0 經過一互斥 閘 (XOR)。最後得到訊號 in,cka,ncka,輸出的時序圖如圖 4.3 所示,時脈訊號 cka, 30.

(44) 第四章 時脈量測電路. ncka 仍然對準了訊號 in 的中間點。. in cka ncka. 圖 4. 3 邊緣偵測器的輸出時序圖. 4.2.2 延遲串列電路 將時脈訊號 cka,ncka 和訊號 in 傳入延遲串列電路 (Delay chain circuit),見圖 4.4, 由於經過相同數目的反相器,所以 Node F 和 Node 6 經過的閘延遲數相同,Node F 的時 脈訊號仍然對準 Node 6 訊號的中間點。由於我們希望可以找出資料訊號轉態的位置點 和中間點的距離,以便求出眼圖張口的大小,所以用 Node F 時脈來對 Node 1~11 訊號 作取樣的動作。其中,Node 5、Node 7 與 Node 6 相差了一個閘延遲,Node 4、Node 8 與 Node 6 相差兩個閘延遲,Node3、Node 9 與 Node 6 相差三個閘延遲,Node2、Node 10 與 Node 6 相差四個閘延遲,Node 1、Node 11 與 Node 6 相差五個閘延遲。如此一來, 我們可以以閘延遲來作為時間的基準,找出資料的轉態位置。. 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. in F cka ncka. 圖 4. 4 延遲串列電路. 4.2.3 取樣電路 圖 4.5,我們用時脈 Node F 對訊號 Node1~11 作取樣,因為 Node 1~Node 11,中間 相隔的是反相器,所以使用的正邊緣觸發 D 正反器 (Postivie edge-triggered D-type flip 31.

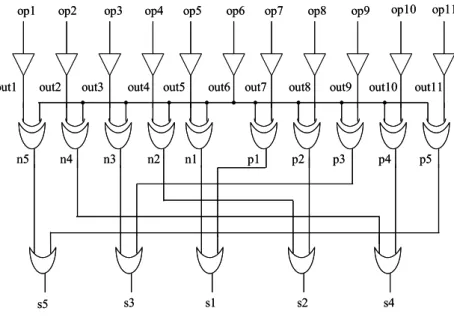

(45) 第四章 時脈量測電路. flop, DFF) 的輸出訊號有 Q、Qb 兩種,且 Q 和 Qb 會間隔出現。因 Node F 要同時對 Node 1~11 作取樣的動作,要驅動的負載 (Loading) 很大,所以加入了緩衝器,以便可以推十 一個 DFF,輸出的訊號為 op1~op11。. 1. 2. 3. 5. 4. 6. D Q. D Q. D Q. D Q. D Q. D Q. Qb. Qb. Qb. Qb. Qb. Qb. F op1. op2. op4. 8. 9. 10. 11. op3. op5 7. D Q. D Q. D Q. D Q. D Q. Qb. Qb. Qb. Qb. Qb. op11. op10. op6. op9. op8. op7. 圖 4. 5 取樣電路. 4.2.4 時脈檢測器 為了找出資料轉態的位置,將訊號 op1~op11 經過一時脈檢測器 (Timing detector), 如圖 4.6 所示。讓 op6 和其他 op 做互斥的動作,若和 op6 相同,則互斥閘的輸出為低電 位;若和 op6 不同,則互斥閘的輸出會有高電位出現。經過互斥之後,得到訊號為 n5~n1、. p1~p5。接下來,我們將與中間點相距同樣閘延遲數所取樣檢測得到的訊號經過 OR 閘, 最後得到檢測訊號 s1~s5,其中 s1=(n1.p1),s2=(n2.p2),s3=(n3.P3),s4=(n4.p4),. s5=(n5.p5),它們分別顯示資料相較於時脈所產生的時間餘式(Timing margin)。. 32.

(46) 第四章 時脈量測電路 op1. out1. op2. out2. n5. op3. out3. n4. op4. out4. n3. op5. out5. n2. out6. op8. op7. op10. op9. op11. out7. out8. out9. out10. out11. p1. p2. p3. p4. p5. n1. s3. s5. op6. s1. s4. s2. 圖 4. 6 時脈檢測器. 4.2.5 消除突波的取樣電路 由於經過時脈檢測器的邏輯電路,會有突波 (Glitch) 產生,所以我們將檢測訊號再 做一次取樣的動作。如圖 4.7 所示,使用的取樣時脈為 Node F 經過延遲 Δt 之後的訊號, 由於這個延遲不超過半個資料訊號週期,所以我們可以順利的對檢測訊號 s1~s5 做取樣。 s1. s2. s3. D Q. D Q. s4. D Q. s5. D Q. D Q. F(Δt) os1. os2. os3. os4. os5. 圖 4. 7 消除突波的取樣電路. 4.3 時脈量測電路的操作 介紹完時脈量測電路之後,接下來要說明如何得到檢測訊號,以及如何利用檢測訊 號來估算出眼圖張口和時脈抖動的大小。 33.

(47) 第四章 時脈量測電路. 4.3.1 檢測訊號量測說明 訊號經過延遲串列電路之後,再做取樣所得到的取樣位置關係圖,如圖 4.8 所示。 我們將這個取樣位置關係圖,看成一把量尺,尺的中間點對應到資料的中間點。. 1.2V 1.1V 1.0V 0.9V 0.8V 11 10 9. 8. 7. 6. 5. 4. 3. 2. 1. 圖 4. 8 取樣位置關係圖 在不同的供電壓之下,它們的刻度大小不同,而刻度的大小,如同表格 4.1 的平均 閘延遲所示。當供電壓越大,刻度越小;供電壓越小,刻度越大。 表格 4. 1 反相器的平均閘延遲. Unit: ps. 0.8V. 0.9V. 1.0V. 1.1V. 1.2V. SS. 105. 84. 70. 60. 55. TT. 80. 68. 58. 49. 44. FF. 58. 53. 47. 41. 37. 由於取樣的位置與中間點最大相距 5 個閘延遲,所以當我們假設時脈抖動的大小為. 0.4UI 時,估算出在不同的供電壓之下可量測的最小傳輸速率,如表格 4.2 所示。若供 電壓為 1.2V @ TT,傳輸速率不可以小於 1.36Gbps,太小的傳輸速率無法被量測。 表格 4. 2 可量測傳輸速率的下限. Unit: Gbps. 0.8V. 0.9V. 1.0V. 1.1V. 1.2V. SS. 0.57. 0.71. 0.86. 1.00. 1.09. TT. 0.75. 0.88. 1.03. 1.22. 1.36. FF. 1.03. 1.13. 1.28. 1.46. 1.62. 34.

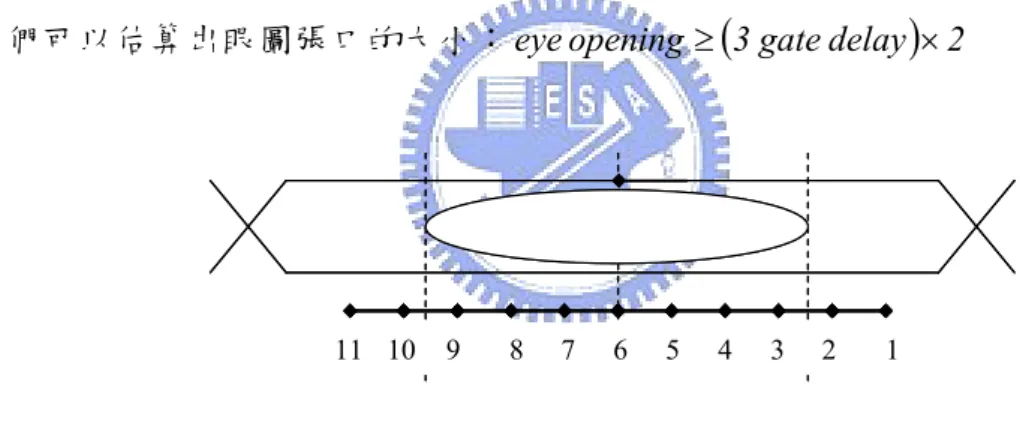

(48) 第四章 時脈量測電路 取樣過後的訊號 op1~op11,經過了時脈檢測器,得到檢測訊號 s1~s5,而檢測訊號 比對取樣訊號如同表格 4.3 所示。取樣輸出 op5、op7 與中間點取樣輸出 op6 相差一個閘 延遲,得到的檢測訊號為 s1,依此類推。 表格 4. 3 檢測訊號 比對 取樣輸出訊號. Detector signal. diff. with Node 6. Use Node. s1. 1 gate delay. op5, op7. s2. 2 gate delay. op4, op8. s3. 3 gate delay. op3, op9. s4. 4 gate delay. op2, op10. s5. 5 gate delay. op1, op11. 舉例說明:(1) 當 op5、op7 和 op6 訊號相同時,得到的檢測訊號 s1=0。(2) 當 op4、. op5、op7、op8 和 op6 訊號相同時,得到檢測訊號 s1=0、s2=0。我們將接著說明如何用 檢測訊號來估算出眼圖張口的大小。. 4.3.2 檢測訊號的分析 分析不同的檢測訊號結果,來估算出眼圖張口的大小,可分成以下五種情況。. (1) os1=0 代表和中間點相距一個閘延遲的取樣輸出訊號,和中間點取樣輸出訊號相同,所以 我們可以估算出眼圖張口的大小: eye opening ≥ (1 gate delay ) × 2 。由於閘延遲是由中間 點向兩旁張開,所以要乘以 2。. 11 10. 9. 8. 7. 6. 5. 4. 3. 圖 4. 9 檢測訊號 os1=0 35. 2. 1.

(49) 第四章 時脈量測電路. (2) os1, os2=0 代表和中間點相距兩個閘延遲的取樣輸出訊號,都和中間點取樣輸出訊號相同,所 以我們可以估算出眼圖張口的大小: eye opening ≥ (2 gate delay ) × 2. 11 10. 9. 8. 7. 6. 5. 4. 3. 2. 1. 圖 4. 10 檢測訊號 os1, os2=0. (3) os1, os2, os3 =0 代表和中間點相距三個閘延遲的取樣輸出訊號,都和中間點取樣輸出訊號相同,所 以我們可以估算出眼圖張口的大小: eye opening ≥ (3 gate delay ) × 2. 11 10. 9. 8. 7. 6. 5. 4. 3. 2. 1. 圖 4. 11 檢測訊號 os1, os2, os3=0. (4) os1, os2, os3, os4=0 代表和中間點相距四個閘延遲的取樣輸出訊號,都和中間點取樣輸出訊號相同,所 以我們可以估算出眼圖張口的大小: eye opening ≥ (4 gate delay ) × 2. 11 10. 9. 8. 7. 6. 5. 4. 3. 2. 1. 圖 4. 12 檢測訊號 os1, os2, os3, os4=0 36.

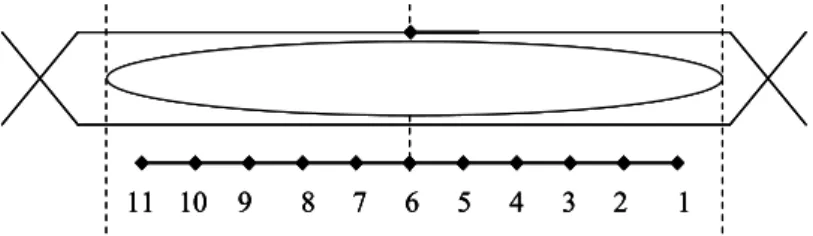

(50) 第四章 時脈量測電路. (5) os1, os2, os3, os4, os5=0 代表和中間點相距五個閘延遲的取樣輸出訊號,都和中間點取樣輸出訊號相同,所 以我們可以估算出眼圖張口的大小: eye opening ≥ (5 gate delay ) × 2. 11 10. 9. 8. 7. 6. 5. 4. 3. 2. 1. 圖 4. 13 檢測訊號 os1, os2, os3, os4, os5=0. 估算出眼圖張口的大小,可進而估算出時脈抖動的大小:. jitter (UI ) ≤. (Data Period - eye opening ). (4.1). Data Period. 觀察眼圖張口的大小,以及時脈抖動的大小,來決定要如何調整供電壓或是傳輸頻 率大小。當眼圖張口太小時,我們可以將供電壓調升,或是將傳輸速率降低,來使得眼 圖張口大小獲得改善。而檢測訊號比對取樣位置點,如表格 4.4 所示。 表格 4. 4 檢測訊號 比對 取樣位置點. Detector signal. diff. with Node 6. Sample Node. os1. 1 gate delay. 5, 7. os2. 2 gate delay. 4, 8. os3. 3 gate delay. 3, 9. os4. 4 gate delay. 2,10. os5. 5 gate delay. 1,11. 4.4 總結 本章節介紹了時脈量測電路的電路架構,以及如何用時脈量測電路所輸出的訊號, 估算出眼圖張口的大小,並且藉由此眼圖張口,決定要如何調整供電壓或是傳輸速率, 37.

(51) 第四章 時脈量測電路 來達到最佳的工作情況。當眼圖張口太小時,可以將供電源電壓調升,或是將傳輸速率 調降,來改善目前的情況。. 38.

(52) 第五章 匯流排電路之實現. 第五章 匯流排電路之實現. 5.1 偽隨機位元序列產生器 利用 PRBS 電路產生訊號輸入匯流排中傳輸,PRBS 電路如圖 5.1 所示。此電路是 由十一個 D 型正反器和兩個互斥閘所構成。. d0 D Q D Q. d1 D D Q Q. d2 D D Q Q. d3 D Q. d4 D Q. d5 D Q. d6 D D Q Q. d7 D Q D Q. ck. Q D D Q. Q D D Q. Q D D Q. set. 圖 5. 1 PRBS 電路. 一開始先將所有的 D 型正反器重置 (Reset) 為 0,接著使用 set = VDD 的脈衝波. (Pulse) 訊號來觸發 PRBS 電路,產生並列 (Parallel) 的偽隨機訊號 d0~d7。在第九個和 第十一個 DFF 的輸出做互斥的動作,利用方程式來表示,可以寫成. P( X ) = X 11 + X 9 + 1. 39. (5.1).

(53) 第五章 匯流排電路之實現 我們還另外在 PRBS 電路中,加入了一個除頻器 (Divider),對 ck 時脈訊號做除頻 的動作,如圖 5.2 所示,最後可以產生一個觸發在資料正中間點的時脈訊號,目的是為 了要做電路最後面的時脈量測。而除頻器所產生出來的時脈訊號 ick,頻率為 ck 頻率的 一半。. nck. D D Q Q Qb. ick. 圖 5. 2 除頻器. 若控制 PRBS 的時脈訊號 ck 的頻率為 2GHz,則它可以產生 8 筆偽隨機訊號 d0~d7, 傳輸頻率為 2Gbps,而時脈訊號 ick 的頻率為 1GHz。因為產生的訊號,每經過 (211-1) 筆 資料之後,它會自己再重複產生,所以稱之為偽隨機訊號。最後得到的時序圖,如圖 5.3 所示。. d0~d7 ck nck ick. 圖 5. 3 PRBS 與除頻器的輸出訊號時序圖. 將偽隨機位元序列產生器與除頻器的電路,用 HSPICE 模擬驗證。假設供電源為. 1.2V,ck 時脈訊號的頻率為 2GHz,則我們可以得到傳輸速率為 2Gbps 的偽隨機訊號, 見圖 5.4 的時脈波形圖 (Timing diagram),而它的眼圖 (Eye diagram) 如圖 5.5 所示。. 40.

(54) 第五章 匯流排電路之實現 d0 d1 d2 d3 d4 d5 d6 d7 ick. 圖 5. 4 PRBS 電路的輸出時脈波形圖. d0 d1 d2 d3 d4 d5 d6 d7 ick. 圖 5. 5 PRBS 電路的輸出眼圖. 5.2 匯流排電路 見圖 5.6,將前面所產生的偽隨機訊號 d0~d7 和時脈訊號 ick 輸入匯流排電路,經過 匯流排傳送之後,輸出訊號為 o1~o8 還有 ock。. 41.

(55) 第五章 匯流排電路之實現 o1~o8. d0~d7 BUS ick. ock. 圖 5. 6 簡易的匯流排電路 匯流排電路各項參數值的決定方式,請見第三章,最後可以得到表格 5.1。 表格5. 1 匯流排的各項參數值. Parameter. Value. Number of interconnect. 9 (Data:8 , Clock:1). Global interconnect length. 10000um. Each segment length / Number of repeaters. 100um / 100. Interconnect width / Interconnect spacing. 0.2um / 0.4um. PMOS. Lp=0.13um , Wp=3.4um. NMOS. Ln=0.13um , Wn=0.8um. 5.3 時脈量測電路 經過匯流排的輸出訊號,取出其中輸出 o6 和時脈輸出 ock,來做時脈檢測的動作, 最後可以得到 5 個輸出的檢測訊號,如圖 5.7 所示。我們用這些檢測訊號估算出眼圖張 口的大小,進而決定要如何調整供電壓或傳輸速率的大小。. o6 ock. Timing Meas.. os1 os2 os3 os4 os5. 圖 5. 7 簡易的時脈量測電路. 5.4 輸出緩衝器與開汲極輸出 由於資料輸到外部的過程中,必須經過接合線 (Bonding wire) 和腳位 (Pad),可能 會因為電感和電容使得訊號共振 (Resonance)。所以由外部觀察的訊號,必須先經過輸 42.

(56) 第五章 匯流排電路之實現 出緩衝器 (Output buffer) 之後,再傳到外部。輸出緩衝器如圖 5.8 所示,是由簡單的反 相器電路所組成的。. m=1 m=2. m=4 m=8. 圖 5. 8 輸出緩衝器 見圖 5.9,為了使模擬的輸出訊號可以被外部量測到,我們在輸出訊號之後,加入 輸出緩衝器,確保訊號可以推得動開汲極輸出 (Open drain),並且利用外部流進的大電 流來推動 pad 電容,最後經由接合線連結到示波器 (Oscilloscope)。而在示波器上可以看 到的振幅大小,如表格 5.2 所示。. CS (Open Drain) connect to PAD Node A. Last Repeater. Ics 2nH. PAD v=L. Buf. 1pF. di dt. 50 ohm. PIN. Vpp= Ics x 50. 1pF. 50ohm 100nF. Inside Chip. Node B. Oscilloscope. 圖 5. 9 使用輸出緩衝器及開汲極輸出,在外部示波器觀察波形 表格 5. 2 供電源大小對應外部示波器振幅大小. Swing. Node A. Node B. 1.2V. Full swing. 280mV. 1.1V. Full swing. 240mV. 1.0V. Full swing. 210mV. 0.9V. Full swing. 170mV. 0.8V. Full swing. 130mV. 43.

(57) 第五章 匯流排電路之實現. 5.5 佈局圖和模擬結果 我們利用 Laker 來畫晶片佈局圖,經過 Calibre 驗證之後,粹取出電路的寄生效應, 再用 HSPICE 來做佈局後模擬(Post-simulation)。. 5.5.1 晶片佈局圖 使用了 TSMC 0.13RF 製程來實踐我們的電路,如圖 5.10 所示。晶片佈局圖 (Chip. layout) 的總面積為 0.7639 mm 2 ( 874um × 874um ),總共有 22 個腳位,各個腳位的屬性如 表格 5.3 所示。此晶片包含了偽隨機位元序列產生器、9 條長度各為 10mm 的全區域傳 輸線、時脈量測電路,以及輸出緩衝器。在佈局圖空白面積上,我們放入了去耦電容. (Decoupled capacitors),平均分配給四組供電源使用,目的是為了讓供電源的雜訊能夠 降低。這個晶片將被實現,且於 2008 年 12 月 7 日送回。 874um vdd2. rst. vdd1. nck. gnd3. gnd1. set. ck. gnd2. PRBS. rst1. gndpb. 874um. 10mm on-chip global interconnect. vdd3. o6. with repeater chain gnd4. ock. BUF. Timing Meas.. BUF. vdd4. gndp. os5. os1. os4. os3. 圖 5. 10 電路佈局圖 44. os2.

(58) 第五章 匯流排電路之實現 表格 5. 3 各個腳位的屬性. Attribute. Pin Name. Pads. Power. vdd1, gnd1, vdd2, gnd2, vdd3, gnd3, vdd4, gnd4, gndp, gndpb. 10. Control. ck, nck, rst, set, rst1. 5. Output. o6, ock. 2. Logic Output. os1,os2,so3,os4,os5. 5. 5.5.2 佈局後模擬 我們在供電源為 VDD=1.2V 時,傳輸線可以傳送的最大傳輸速率為 2Gbps,匯流排 的輸出波形圖如圖 5.11 所示,圖中包含了 5 種不同 corner 的模擬結果,jitter 大約為. 0.3~0.4UI。. SS. SF. TT. FS. FF. 圖 5. 11 匯流排輸出模擬圖 (VDD=1.2V, Data Rate=2Gbps). 此外,我們還模擬了 VDD=1.0V 在 Data Rate=1.5Gbps,和 VDD=0.8V 在 Data. Rate=1Gbps 時的情況,見圖 5.12 和圖 5.13。最後我們將模擬得到的 jitter 結果列成一表 45.

數據

相關文件

※步進點主要應用於步進電路中。當不使 用步進指令時,步進點可作為一般的輔助 繼電器使用。 FX2 PLC的步進點可分為初

附表 1-1:高低壓電力設備維護檢查表 附表 1-2:高低壓電力設備維護檢查表 附表 1-3:高低壓電力設備(1/13) 附表 2:發電機檢查紀錄表. 附表

表 6.3.2 為不同電壓下,驅動整個系統運作所需電流。圖 6.3.2 為 測試情形。其中紅燈代表正常工作。結果證明只要太陽能板能夠提供

Based on the forecast of the global total energy supply and the global energy production per capita, the world is probably approaching an energy depletion stage.. Due to the lack

4.手機充電後,立刻拔掉充電器插頭,只要全球 行動電話 使用者做到 省下的能源 相當 10%行動電話

Monopolies in synchronous distributed systems (Peleg 1998; Peleg

Corollary 13.3. For, if C is simple and lies in D, the function f is analytic at each point interior to and on C; so we apply the Cauchy-Goursat theorem directly. On the other hand,

Corollary 13.3. For, if C is simple and lies in D, the function f is analytic at each point interior to and on C; so we apply the Cauchy-Goursat theorem directly. On the other hand,