行政院國家科學委員會電信國家型研究計畫成果報告

總計畫 :多媒體無線接收機系統單晶片設計技術之研究

子計畫二:數位式多媒體無線接收機之中頻與基頻類比前級

超大型積體電路架構設計與晶片製作(III)

VLSI Architecture Design and Implementation of IF and Baseband Analog F ront End

.for

Digital Multimedia Wireless Receiver (III)

計畫編號:NSC 90-2215-E002-044

執行期限:90 年 8 月 1 日至 91 年 7 月 31 日

總計畫 主持人:陳良基教授 台灣大學電子工程研究所

子計畫主持人:汪重光教授 台灣大學電子工程研究所

一、中文摘要

本計劃之類比前級主要應用於無線區域網路, 射 頻 為 2.4GHz, 中 頻 為 280MHz, 基 頻 頻 寬 為 17.6MHz。本報告為子計劃的第三年報告,本年度主要 計畫要項,為混波器,低通濾波器,震盪器之佈局設計, 以及 post-layout 模擬,並完成整個中頻類比前級的晶 片製作,以及測試驗證。最後,將中頻部分與前級射頻 部分加以整合,以模擬此類比前級系統是否可行。電 路採用 TSMC 0.35μm CMOS 標準製程。 中頻/基頻 轉換器晶片面積為 2.4mm 2mm。 關鍵詞:限制放大器, 接收訊號強度指示器, 低通 濾波器, 混波器, 環狀震盪器, 降頻轉換。Abstr act

This report presents an analog front-end VLSI architecture that deals with IF signal in wireless LAN system. The center frequencies of RF and IF chosen are 2.4GHz and 280MHz respectively, and the baseband bandwidth is 17.6MHz. The mixer, low pass filter, and ring oscillator circuits are designed and post-simulated in the third period. The implementation of whole IF portion must be accomplished, and the chip must be tested for verification. The last procedure is the integration of RF and IF portions in this project. All the circuits employ TSMC 0.35μm CMOS standard technology using single power supply 3V. The chip of IF/Baseband downconverter occupied area of 2.4mm 2mm.

Keywor ds: limiting amplifier, received signal strength indicator, wideband amplifier, bandpass filter.

二、計畫緣由與目的

隨著寬頻通信與數位訊號處理技術快速成長,消 費者已能享受到結合聲音、圖形、影像、及大量文字 傳遞的多媒體通訊服務。諸如遠距教學,電子商務 等。為提供更可靠、更便捷、與低成本的多媒體傳輸 服務,發展結合 3C (computer, communication, and

consumer ) 環境之高效能數位式多媒體無線接收機, 將是一重要課題。 對於無線傳輸而言,有下列幾項重要特性需要考 慮: 低功率,少量元件,低成本,且須符合要求標準。本 次計劃除了有效達成降頻轉換外,另一重要目標,為數 位與類比電路之相容性,即以 SOC 為方向。本次報告 為三年計劃之第三年成果報告。 本年度主要目標 ,為混波器、低通濾波器與震盪 器之佈局設計,以及 post-layout 模擬。晶片需完成製 作並測試完成。另外,本中頻部分需與前級的射頻達 成整合,以驗證整體類比前級的可行性。

三、研究方法與成果

圖一為整個接收器中,中頻/基頻類比前端的方塊 圖。 將 280MHz 中頻信號,降頻轉換為相差 90 度之 I-channel 及 Q-channel 之基頻信號。 限制放大器接 收前級(射頻/中頻)輸出之中頻信號,將信號限制在一 固定之大小;接收信號強度指示器則監測出中頻原始 信號的大小,輸出至基頻,指示信號的強度;最後利用 二個相同的混波器,灌入相差 90 度之振盪信號,再透 過低通濾波器,除去高頻諧波與雜訊,達成降頻。本子 計畫中所有線路皆已完成設計,並完成晶片製作,經測 試驗證無誤 LPF LPF RSSI DSP4-Stage Ring Osc. Limiting Amp. I Limiting Amp. II IF Mixer I Q ADC ADC ADC 圖一 系統方塊圖 晶片製作與測試結果 圖二為完整的中頻轉基頻類比前級電路晶片佈 局圖, 電路採用 TSMC 0.35μm CMOS 標準製程,使 用面積為 2.4mm 2mm。左半部份為主要信號路徑,

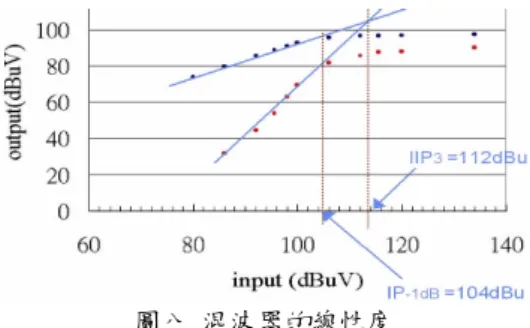

經箝制放大器,再經由九十度相差的混波器,最後經低 通濾波器產生輸出。右半部分為獨立的電路方塊,供 測試用。 圖二 晶片佈局圖 圖三(a)為箝制放大器之震幅頻率響應,3dB 截止 頻率為 300MHz。由於輸出端阻抗與網路分析儀的不 匹配,與單端輸出比差模少了 6dB,差模的 DC 增益實 際上應為 42dB,與模擬值(45dB)相去不遠。圖(b)為相 位的頻率響應,在 3dB 頻率,也就是 300MHz 處,相位移 為 520°。 (a)震幅響應 (b)相位響應 圖三 限制放大器頻率響應 在不同輸入震幅下,箝制放大器應能將其皆放大 至相同的飽和位準,如圖四所示,在 298MHz 頻率,分 別輸入 400mV,10mV,與 5mV,輸出位準皆相同。 圖四 限制放大器飽和輸出波型 圖五為箝制放大器的靈敏度。因為受限於測試環 境與電源供應器的雜訊,當輸入震幅小於 2mV 時,輸 出都會維持在相同位準,此乃因電路被雜訊所主控 了。這也是我們所能量測到最小的正常操作輸入。 圖六為接收訊號強度指示器的偵測範圍,在誤差 正負 3dB 的要求下,其偵測範圍應大於限制放大器的 動態範圍。但是,如同在箝制放大器中的雜訊影響,當 輸入訊號小於 2mV 時, 接收訊號強度指示器的輸出 維持在一固定位準,不再下降。 圖五 限制放大器的靈敏度 圖六 接收訊號強度指示器的偵測範圍 由混波器的時域表現,以及頻譜分析,見圖七,我 們可看出,其將 300mV,290MHz 的弦波信號,與 280 MHz 震盪信號相乘,得到 10MHz 的輸出。混波器的 轉移增益為-6dB,將輸入信號衰減,以避免超過下級低 通濾波器的線性區間。圖八為混波器的線性度量測, 其-1dB 壓縮點為 104dBuV,IIP3 為 112dBuV。 (a)時域輸出 (b)頻譜 圖七 混波器

0.1 1.1 2.1 3.1 4.1 5 Frequency (GHz) G r ap h 4 -30 -20 -10 0 10 20 2.4 GHz -12.7 2.4 GHz -6.25 2.4 GHz 2.15 2.41 GHz 11.2 DB(|S[1,1]|) id_10mA DB(|S[2,1]|) id_10mA NF id_10mA DB(|S[2,2]|) id_10mA 圖八 混波器的線性度 圖九為五階 Butterworth 低通濾波器的頻率響 應。上圖為震幅響應,可看出其 3dB 截止頻率為 18MHz,之後,就以每兩倍頻 30dB 的速度衰減,符合五 階的低通濾波器設計;下圖為相位響應,可看到在 3dB 截止頻率處,相位差為 215 度。因為本系統屬展頻系 統,為了配合其不同的 chip rate 需求,此處的低通濾波 器,需有四種不同的頻寬變化,即 2.2/4.4/8.8 /17.6 MHz, 以適應不同的通道品質使用。這部分功能,主要是由 電容陣列構成,藉由控制電壓,可決定接於各端點的電 容值,即可使濾波器的轉換函數改變,而造成頻寬的改 變。圖十為低通濾波器的另外三種頻寬變化。 圖九 低通濾波器頻率響應 圖十 低通濾波器可變頻寬 圖十一 完整的系統信號路徑:混波器及濾波器輸出 圖十一為完整的信號路徑-箝制放大器,混波器,低通 濾波器-的輸出波型。輸入皆為 10mV 的弦波信號,改 變其輸入頻率,分別為 296MHz,292MHz,及 287MHz, 被箝制放大器放大至相同位準,經過混波器後,仍維持 相同的震幅;再經過低通濾波器,濾出所欲之降頻信號, 此信號依然維持相同強度。由此可知,在系統的要求 範圍(頻率,震幅)下,強度控制能發揮作用。 底下為整個中頻線路的效能列表:

Table 1: Performance Summary

圖十二為射頻前端和中頻/基頻類比前端整合模 擬的架構圖。在射頻前端,包含了 LNA、Image Reject Mixer 的 RF 電路,而中間的外接的 Channel-Select Filter 則是利用被動元件去 modeling 他的特性來模 擬。 圖十二 射頻前端和中頻/基頻類比前端整合的架構圖 圖十三為 LNA 低雜訊放大器的特性圖,圖上可以 得知其電壓增益(S21)為 11.2dB, 且其在 2.4GHz 的操 作 頻 段 下 , 其 NF=2.15dB , S11=-6.25dB , S22=-12.7dB。 I

4- stage Ring Osc. Channel Select Filter

IF out Buffer Buffer Q LNA RF input

Limiting Amp.ILimiting Amp.II

IF Mixer IF Mixer LPF LPF RF Mixer RF Mixer RSSI ADC DSP ADC ADC LPF Bandwidth Select

圖十四則是 Image-Reject Mixer 的特性圖,其 conversion gain=10dB,IRR=30dB,IP3=85dBuV

圖十四,Image-Reject Mixer 的 Transient Response

圖十五則是 modeling 後的 Channel-Select Filter 的 Frequency Response。其操作的頻段在於 278MHz 和 292MHz,增益為 -7.1dB,在士 33MHz 的地方, 其 Attenuation 到 -50dB。

圖十五 Modeling Channel Select Filter ac Response

接下來看到的,則是整個架構結合起來的模擬 圖 , 我 們 可 以 看 到 在 圖 十 六 , 是 變 換 其 Input Amplitude 去 看其 output 輸 出。下 圖,我 們輸入 2410MHz 22Vp-p & 100mVp-p 的訊號進入後所得 到的圖形。我們可以看到其 AM-PM noise 大概是在 5ns 左右。 圖 十 六 中 頻 / 基 頻 類 比 前 端 輸 出 vs. RF 輸 入 振 幅 22uVp-p&100mVp-p@2410MHz I Q 圖十七,我們可以看到在改變成頻率下所得到 的 圖 形 。 此 處 , 我 們 則 是 輸 入 2410MHz 、 2405MHz&2402MHz 2mVp-p 的訊號, 下圖則是其在 中頻濾波器後 Output 所看到的結果。 圖 十七 當 輸 入 2410MHz 、 2405MHz&2402MHz 的 2mVp-p 弦波時,中頻濾波器的輸出 I Q 接下來的圖十八,則是在整個 802.11 操作的頻 帶上,選擇不同的 tone 所呈現的結果。其輸入的信 號分別為 2410MHz、2430MHz、2450MHz、2470MHz 和 2490MHz 2mVp-p 的訊號,我們可以在下圖中,看 到他們之間的變化。在靠近左邊的線段是 2410MHz 而最右邊的則是 2490MHz。 I Q 圖十八為在不同的 tone 輸入其相對應的 2mVp-p 的 10MHz 的訊號產生的暫態輸出圖。

四、計畫成果自評

現在,我們已完成第三年度的工作,即完成整個子 計 畫 。 針 對 降 頻 轉 換 部 分 的 佈 局 設 計 , 和 post-simulation,由模擬結果可知,降頻部分的表現,符 合我們在系統設計時,所訂定的規格。而晶片經測試 後,也再度驗證此設計是良好,且達到要求的。 整體而言,此子計畫最主要目的是要在低電壓低 功率高速度的要求下,發展中頻至基頻類比前級的線 路設計技術,以配合射頻前端與基頻信號處理,達成高 階整合之系統晶片。五、參考資料

1. M. E. Van Valkenburg, Analog Filter Design, Pretice-Hall, 1982

2. B. Gilbert, Monolithic Logarithmic Amplifier, August, 1994

3. Kuang-Hu Huang, “Low-voltage low-power circuit and architecture design for CMOS receiver front-end”

4. Z. H. Wang, “Full-wave precision rectification that is performed in current domain and very suitable for CMOS implementation”, IEEE Trans. Circuits and Systems-I, vol.39, pp.456-462,June 1992.