國

立

交

通

大

學

電機學院 電子與光電學程

碩

士

論

文

多重閘極金氧半場效電晶體的變異特性模擬與分析

Investigation of Variability for Multi-Gate MOSFETs

- A Study Based on Device Simulation

研 究 生:陳燦堂

多重閘極金氧半場效電晶體的變異特性模擬與分析

Investigation of Variability for Multi-Gate MOSFETs

- A Study Based on Device Simulation

研 究 生:陳燦堂 Student:Tsan-Tang Chen 指導教授:蘇 彬 Advisor:Pin Su 國 立 交 通 大 學

電機學院 電子與光電學程

碩 士 論 文 A ThesisSubmitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in

Electronics and Electro-Optical Engineering June 2007

Hsinchu, Taiwan, Republic of China

多重閘極金氧半場效電晶體的變異特性模擬與分析

學生:陳燦堂 指導教授:蘇 彬 國立交通大學 電機學院 電子與光電學程碩士班 摘 要 本論文藉由元件模擬器,對多重閘極金氧半電晶體做三維的元件模 擬,探討製程參數漂移及隨機摻雜變動對多重閘極金氧半電晶體的起始 電壓的影響。 鰭狀電晶體,三閘電晶體及類似平面電晶體分別於三種不同的基 底:厚埋層氧化層(100nm,類型一),矽基底(類型二)及薄埋層氧化 層(10nm,類型三)將被進行模擬、分析與探討。 通道長度、鰭狀通道寬度(fin-width)、鰭狀通道高度(fin-height)、閘 極氧化層厚度、通道摻雜濃度等製程參數的漂移及隨機摻雜變動,對元 件起始電壓所造成的影響,將被逐一探討。此外,埋層氧化層的厚度及 矽基底,對多重閘極電晶體的起始電壓的影響,也將一併探討。 由模擬的結果,我們可以得知:在相同總通道寬度(Wtotal)的情況下, 對低摻雜通道元件,鰭狀電晶體因對製程參數漂移及隨摻雜變動有較高 的忍受度,而具有最小的起始電壓變量;然而對高摻摻雜元件,類似平 面電晶體則因為具有較小的隨機摻雜變動量,具有較小的起始電壓變量。Investigation of Variability for Multi-Gate MOSFETs

- A Study Based on Device Simulation

Student:Tsan-Tang Chen Advisors:Dr. Pin Su

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

ABSTRACT

This study investigates the threshold voltage (Vth) variation of multi-gate

devices using 3-D device simulation. FinFET, Tri-gate and Quasi-planar device structures on thick buried oxide (100nm, scenario 1), bulk (scenario 2) and thin buried oxide (10nm, scenario 3) are examined.

The Vth dispersion caused by variation of the process parameters such as

gate length, gate oxide thickness, channel doping, fin width and fin height have been investigated. In addition, the impact of random dopant fluctuation of channel doping on Vth has also been examined. Besides, the impact of

buried oxide thickness and bulk substrate on the Vth variation of multi-gate

MOSFETs are studied.

Our simulation results indicate that, for lightly doped devices, FinFET structure shows the smallest Vth dispersion because of its better immunity to

process-induced variations and random dopant fluctuation. For heavily doped devices, Quasi-planar structure shows smaller V dispersion because of

誌

謝

在這一段不算短的日子裡,終於完成了個人的碩士學業,一個重要的 人生里程碑。 承蒙蘇彬教授的耐心指導,使得本論文得以順利完成。在與老師討論 的過程中,深深感受到老師做學問的嚴謹及對於研究的熱忱,是學生所應 學習的研究態度。不管是做學問亦或做事,這種熱情的投入與嚴謹的求證, 將是成功的不二法門。 在論文的研究過程中,感謝李維學長帶領入門元件模擬,及王生圳學 長在 RF 領域的指導及經驗分享,並感謝吳育昇同學在最後的論文研究上的 協助及討論,讓論文研究得以順利完成。而與實驗室的俊延、銘隆及昆諺, 在平時的討論,及其所給予的寶貴建議,在此一併感謝。 最後,由衷地感謝我的妻子凈儀,在我這段疏於照顧家庭的日子裡, 對我的包容、支持與鼓勵,及其對家庭及小孩的付出,謹以此論文感謝她 的辛勞及付出。

目 錄

論文摘要 (中文) ………..………..…… i 論文摘要 (英文) ………..……….……….……… ii 誌謝 …..……….……… iv 目錄 …………..……….……… v 表目錄 ………...……… vii 圖目錄 ………..……….……… viii 第一章 緒論 ……… 1 1.1 多重閘極金氧半場效電晶體簡介..……….… 1 1.2 起始電壓漂移……… 2 1.3 研究動機 …..……….… 3 1.4 論文架構 ………. 4 第二章 元件模擬與方法 ……… 8 2.1 前言 ……….. 8 2.2 元件結構 ……….… 8 2.3 方法 ……….…… 10 第三章 元件模擬結果與討論 ……… 16 3.1 類型一 厚絕緣層多重閘極電晶體 ………... 16 3.2 類型二 矽基底多重閘極電晶體 ……… 183.4 總結 ……..……….….. 21 第四章 結論與展望 ……… 55 4.1 結論 ……… 55 4.2 後續工作 …….……… 56 參考文獻 …….………..……… 58 附錄 A ……….… 60

A.1 Input deck of heavily doped FinFET (DEVISE) ………... 60

A.2 Input deck of heavily doped FinFET (DESSIS) ………… 62

表 目 錄

第一章 緒論

第二章 元件模擬與方法

表 2-1 模擬的製程參數漂移項目

圖 目 錄

第一章 緒論 圖 1-1 矽覆蓋絕緣層多重閘極金氧半場效電晶體 圖 1-2 矽基底多重閘極金氧半場效電晶體 圖 1-3 原子數量之 Poisson 分布圖 第二章 元件模擬與方法 圖 2-1 厚絕緣層多重閘極電晶體結構 (a)鰭式場效電晶體;(b)三閘極電晶體;(c)類似平面電晶體 圖 2-2 矽基底多重閘極電晶體結構 (a)鰭式場效電晶體;(b)三閘極電晶體;(c)類似平面電晶體 圖 2-3 薄絕緣層多重閘極電晶體結構 (a)鰭式場效電晶體;(b)三閘極電晶體;(c)類似平面電晶體 第三章 元件模擬結果與討論 圖 3-1 通道長度漂移(±10%)引起之起始電壓變量比較圖 圖 3-2 起始電壓對通道長度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-3 鰭狀通道寬度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量 圖 3-4 起始電壓對鰭狀通道寬度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-5 鰭狀通道高度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量圖 3-6 不同鰭狀通道高度的三閘極電晶體起始電壓對通道長度之關係 圖 圖 3-7 閘極氧化層厚度漂移(±10%)引起之起始電壓變量比較圖 圖 3-8 通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖 圖 3-9 隨機掺雜濃度變動引起之起始電壓變量比較圖 圖 3-10 起始電壓對通道掺雜濃度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-11 厚絕緣層多重閘極電晶體的起始電壓變量總和 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-12 通道長度漂移(±10%)引起之起始電壓變量比較圖 圖 3-13 電流分佈圖 (a)100nm;(b)bulk 圖 3-14 鰭狀通道寬度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量 圖 3-15 鰭狀通道高度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量 圖 3-16 閘極氧化層厚度漂移(±10%)引起之起始電壓變量比較圖 圖 3-17 通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖 圖 3-18 隨機掺雜濃度變動引起之起始電壓變量比較圖 圖 3-19 矽基底掺雜濃度變動引起之起始電壓變量比較圖 圖 3-20 厚絕緣層/矽基底多重閘極電晶體的起始電壓變量總和比較圖 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-21 (a)通道長度漂移(±10%)引起之起始電壓變量比較圖 (b)類型一對類型三的通道長度漂移引起之起始電壓變量差異 (低掺雜)

圖 3-22 類似平面電晶體的電位分布圖 (a) 厚絕緣層(類型一);(b)薄絕緣層(類型三) 圖 3-23 鰭狀通道寬度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量 圖 3-24 鰭狀通道高度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量 圖 3-25 閘極氧化層厚度漂移(±10%)引起之起始電壓變量比較圖 圖 3-26 通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖 圖 3-27 隨機掺雜濃度變動引起之起始電壓變量比較圖 圖 3-28 低摻雜通道元件的起始電壓對通道摻雜濃度關係圖 (a) 厚絕緣層(類型一);(b)薄絕緣層(類型三) 圖 3-29 埋層氧化層厚度變動引起之起始電壓變量比較圖 圖 3-30 矽基底掺雜濃度變動引起之起始電壓變量比較圖 圖 3-31 厚/薄絕緣層多重閘極電晶體的起始電壓變量總和比較圖 (a)低掺雜通道元件;(b)高掺雜通道元件 圖 3-32 三種類型的起始電壓變量總和比較圖 (a)低通道掺雜鰭式場效電晶體;(b)高通道掺雜類似平面電晶體

第 一 章

緒論

1.1 多重閘極金氧半場效電晶體簡介

當 MOSFET 製程不斷的進行元件微縮,傳統的平面矽基底架構電晶

體,對於抑制短通道效應已變的愈來愈困難。

多重閘極金氧半場效電晶體(Multi-Gate Field Effect Transistor),諸如 鰭式場效電晶體(FinFET)和三閘極電晶體(Tri-gate),因其可減少短通道 效應(Short-channel effects),進而具有較佳的通道控制能力[1,2,3]。因此當 互補式金氧半(CMOS)製程技術繼續微縮至 45 奈米(nm)時,多重閘極金 氧半場效電晶體便成為一極具競爭力的元件結構。以下為常見的二種類 型: (1) 矽 覆 蓋 絕 緣 層 多 重 閘 極 金 氧 半 場 效 電 晶 體 (Multi-Gate SOI MOSFET) 如圖 1-1 所示,因具有埋層氧化層,減少了漏電流(Leakage current) 及栓鎖(Latchup)效應。然而,矽覆蓋絕緣層多重閘極金氧半場效電 晶體其中的一個缺點為,埋層氧化層(BOX, Buried Oxide)阻絕了元件 通道對矽基底的散熱路徑,而使此種架構的元件具有很高的熱阻抗 (Thermal resistance),進而降低元件的驅動電流,甚至影響某些類比 (Analog)電路的特性[1]。

對於互補式金氧半(CMOS)製程相容性高、所需的晶圓(wafer)成本較 低及具有較佳的熱散逸等特性,近幾年來開始被人們注意,也逐漸 被採用來製做記憶體產品,如 SRAM 亦或是 DRAM 產品[6,7,8],希 望藉由較佳的互補式金氧半製程相容性,可整合既有的 CMOS 製程 的 IP,提高系統單晶片(System-on-a-chip, SoC)設計的可能性。

1.2 起始電壓漂移

金 氧 半 場 效 電 晶 體 (Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)的起始電壓是影響電晶體性能最重要的參數之一,當 此一參數因製程參數漂移而造成變動時,會伴隨著其它元件參數跟著變 動,如元件的驅動電流(Diving current),進而對電路性能造成影響。 會造成起始電壓變化的兩個主要製程參數為閘極氧化層厚度(Gate oxide thickness)及通道掺雜濃度(Channel dopant concentration)。另外,隨 著元件不斷的微縮,元件通道中的雜質數目跟著減少,而使得隨機掺雜 濃度變動對元件起始電壓影響變的更加嚴重,因其乃為區域性的變化, 是故,兩相鄰的元件的通道掺雜濃度即可能具有很大的差異,進而導致 不同元件間起始電壓的差異。圖 1-3 為原子數量之 Poisson 分布圖,而式 (1-1)為摻雜原子數目標準差公式,式(1-2)為摻雜濃度標準差公式。 (1-1)σ

atom

=

V

×

N

,其中 V 代表元件通道體積, N 代表通道摻雜濃度。 (1-2)V

V

N

atom

N

=

σ

=

σ

由式(1-2)可看出,當元件的通道體積或通道摻雜濃度變化時,將影 響摻雜濃度的偏差量,進而導致不同程度的起始電壓變量。

1.3 論文研究動機

在相關的文獻中[1,6]已提出元件的起始電壓漂移(Threshold voltage variation)對電路特性的重要影響,但大多僅針對通道長度(Lg)因製程漂 移(Process Variation)對元件的起始電壓的改變做探討,而對於其它的製 程(Process Parameter)參數漂移,如鰭狀通道寬度(fin-width)、鰭狀通道高 度(fin-height)、閘極氧化層厚度(TOX)、通道掺雜濃度( Nch)等製程參數漂 移對元件起始電壓的影響則甚少著墨。 隨著元件尺寸微縮,元件通道體積(volume)亦跟隨減縮,於是隨機掺 雜濃度變動(Random Dopant Fluctuation)對元件的起始電壓的影響亦趨嚴 重,低掺雜通道元件(Lightly doped channel device)便被採用,來減小隨機 掺雜濃度變動的影響,並增加載子的漂移速度。

此外,較薄的絕緣層(Thin BOX)及具高掺雜濃度(heavily doped)類接 地 (Ground Plane) 基 底 的 元 件 結 構 , 因 其 對 絕 緣 層 的 邊 緣 效 應 (Field-fringing Effect)的抑制作用[9,10,12],進而降低元件起始電壓因為製 程參數漂移所引起的變異,故也被許多文獻所探討。 本論文欲藉由元件模擬器(Device Simulator),來對前文提到的三種類 型的多重閘極金氧半場效電晶體,對應不同長寬比及通道摻雜條件,在 各種不同製程參數漂移及隨機掺雜濃度變動下,做一完整的模擬、分析 和探討,以瞭解元件的變異特性-起始電壓對製程參數漂移及隨機掺雜 濃度變動的敏感性(sensitivity)變化情形。

1.4 論文架構

第一章首先介紹多重閘極金氧半場效電晶體的結構及其優缺點。進 而對本論文要分析的元件特性參數:起始電壓,做一概略描述,並針對 製程參數的漂移及隨機掺雜濃度變動,對起始電壓的影響做一探討,藉 以決定本論文所欲進行模擬分析的項目。 第二章對本論文將分析、探討的元件類型做一介紹,並描述模擬的 項目、方法及起始電壓萃取的條件。 第三章針對三種元件類型的模擬結果進行分析,討論及比較。藉以 瞭解各種元件的起始電壓對製程參數漂移的忍受度。 第四章則對論文做一總結,並對將來此類元件可繼續深入研究的部 份進行探討。

Lg Tox Wfin S/D Gate S/D Hfin Tbox BOX Substrate

AR (Aspect Ratio) = H

fin/W

finW

total= W

fin+ H

fin×2

S/D Gate S/D BOX Substrate 圖 1-2 矽基底多重閘極金氧半場效電晶體

60 70 80 90 100 110 120 130 0 500 1000 1500 2000 F requenc y Atom number 圖 1-3 原子數量之 Poisson 分布圖

第 二 章

元件模擬與方法

2.1 前言

本章將利用元件模擬軟體 ISE[16],在不同的製程參數漂移條件下, 對各種的元件結構做三維的元件模擬,藉以探討製程參數漂移及隨機掺 雜濃度變動,對元件的起始電壓所造成的影響。另外,也將探討不同基 底類型,對應兩種通道摻雜濃度的元件,在製程參數漂移及隨機掺雜濃 度變動下,元件起始電壓所受到的影響。

2.2 元件結構

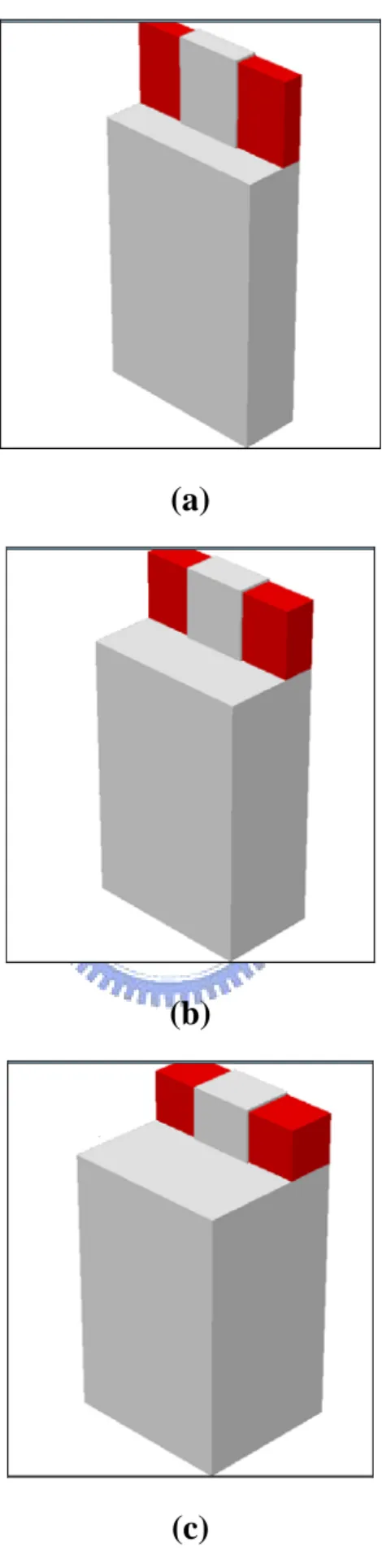

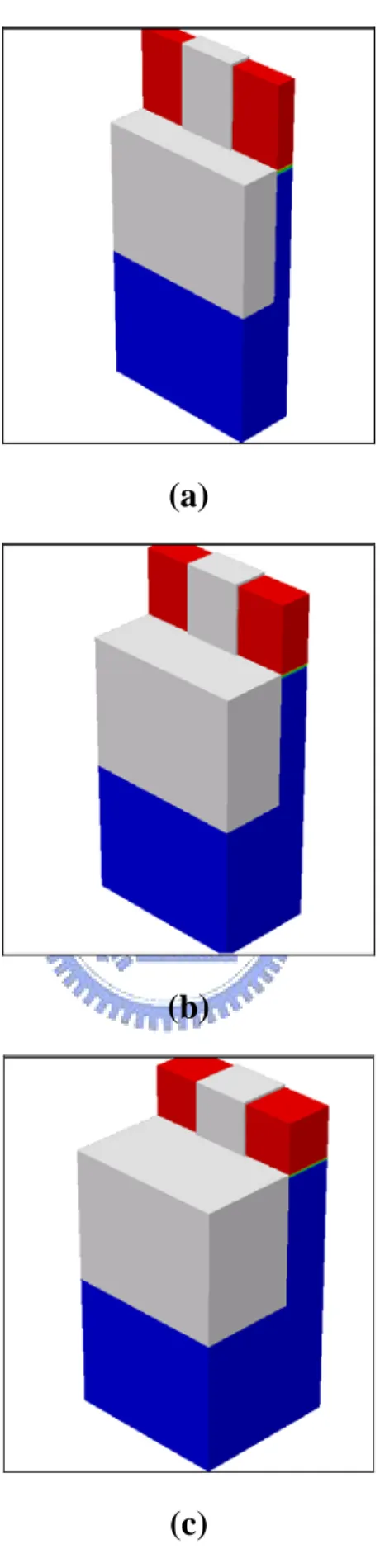

欲進行模擬之元件結構,將在一固定 75nm的總通道寬度(Wtotal)下, 依不同的長寬比,區分為鰭式場效電晶體(FinFET,AR=2)、三閘極電晶 體(Tri-gate,AR=1)及類似平面電晶體(Quasi-Planar,AR=1/2) ,對應三 種不同的基底,如厚絕緣層(Thick BOX)、薄絕緣層(Thin BOX)及矽基底 (Bulk),區分成三種類型如下: 類型一 (scenario 1):鰭式場效電晶體、三閘極電晶體及類似平面電 晶體於厚絕緣層(Tbox=100nm),如圖 2-1 所示。藉以探討傳統的矽覆 蓋絕緣層多重閘極金氧半場效電晶體的起始電壓,因製程參數漂移 及隨機掺雜濃度變動所造成的影響。 類型二 (scenario 2):鰭式場效電晶體、三閘極電晶體及類似平面電 晶體於矽基底(Nsub=1E15cm-3),如圖 2-2 所示。藉以瞭解,當元件沒 有絕緣層與矽基底做隔絕時,元件起始電壓因製程參數漂移及隨機掺雜濃度變動所造成的影響。

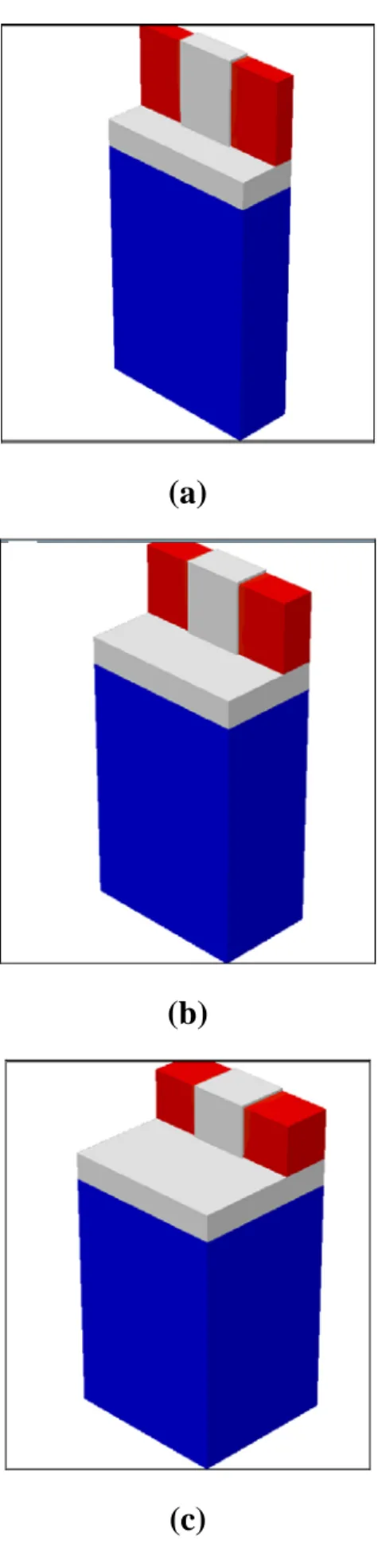

類型三 (scenario 3):鰭式場效電晶體、三閘極電晶體及類似平面電 晶體於薄絕緣層(Tbox=10nm)及類接地基底(Nsub=6E18cm

-3 ),如圖 2-3 所示。藉以瞭解、分析,當絕緣層變薄後,元件起始電壓因製程參 數漂移及隨機掺雜濃度變動所造成的影響。 如第一章中所提及,兩種不同的通道掺雜濃度之元件,因製程參數 漂移對起始電壓所引起的變化,也將一併探討。在此使用 1E17 cm-3為低 掺雜濃度,而高掺雜濃度則設定為 6E18 cm-3 。 使用的詳細製程參數如下: Wtotal = 75nm, Lg = 25nm NS/D = 2E20 cm -3 , 低掺雜通道 Nch = 1E17cm -3,T HfO2 = 2nm (k=25, workfunction=4.7) 在此使用高介電係數之閘極介電層二氧化鉿,以較厚的介電 層,達到高於二氧化矽的閘極電容,以降低薄閘極介電層可能 引起的漏電流,並藉由功函數(workfunction)的調整,以維持元 件的 electrostatic。 高掺雜通道 Nch = 6E18 cm -3,T ox = 1nm (workfunction=4.1) 基於以上幾種元件結構,進行模擬的製程參數漂移項目如表 3-1 所 示。

2.3 方法

首先,在本論文中對元件起始電壓的萃取,乃採取定電流方式:V

D=

0

.

05

V

; g total D g thL

W

I

V

V

=

@

=

3

×

10

−7×

為了減少三維元件模擬所需的時間及電腦資源,所有模擬的元件架 構皆以一半元件來進行,再加倍模擬得到的汲極電流,還原成原有的電 流量,以萃取起始電壓。 其次,對於起始電壓的漂移量則定義如下: 對 10% 製程漂移: ∆Vth=|Vth(+10%) - Vth(-10%)︱/ 2 對固定值製程漂移: ∆Vth=|Vth(+1.5nm) - Vth(-1.5nm)︱/ 2另外,隨機掺雜濃度變動(Random Dopant Fluctuation)在元件模擬上 之實現方法介紹如下:

如第一章中對隨機掺雜濃度變動所做的介紹

Mean no. = V × N, 其中 V 代表元件通道體積, N 代表通道摻雜濃度。

N

V

atom

=

×

σ

則依據正、負三個原子數標準差,所取得的通道摻雜濃度變化範圍 如下:

正三個原子數標準差所決定的通道摻雜濃度變化值: Nch, higher

= (mean no. + 3 σ

atom) / V

負三個原子數標準差所決定的通道摻雜濃度變化值:

N

ch, lower= (mean no. - 3 σ

atom) / V

藉由以上方式,來做為元件模擬之兩組摻雜濃度變化,以觀察元件 的起始電壓,因隨機掺雜濃度變動所造成的影響。模擬時,元件通道摻 雜濃度乃採用固定摻雜濃度(constant doping concentration),以簡化模擬的 複雜度。

量子效應(Quantum effect)模型在模擬時尚未考慮,而在元件模擬中 採用的模型(physical model) 如下:

Intrinsic density model: Band-gap narrowing model

Mobility model: default temperature-dependent constant mobility model.

Recombination model: Shockley–Read–Hall (SRH) recombination with doping dependence lifetime、Auger recombination 及 Avalanche-Generation。 最後,元件模擬所使用之命令檔(input deck),如附錄 A 所示(高掺雜 通道鰭式場效電晶體)。A.1 為用來建立元件架構的 DEVISE 命令檔,而 A.2 為用來進行元件電性模擬的 DESSIS 命令檔。

(a)

(b)

(c)

圖 2-1 厚絕緣層多重閘極電晶體結構

(a)

(b)

(c)

圖 2-2 矽基底多重閘極電晶體結構

(a)

(b)

(c)

(a)鰭式場效電晶體;(b)三閘極電晶體;(c)類似平面電晶體 類型一 類型二 類型三 Lg √ √ √ Wfin √ √ √ Wfin(1.5nm) √ √ √ Hfin √ √ √ Hfin(1.5nm) √ √ √ Tox √ √ √ Nch √ √ √ Nch_RDF √ √ √ Nsub √ √ Tbox √

註: “√” 代表該項參數漂移在該類型元件將進行模擬、探討。 表 2-1 模擬的製程參數漂移項目

第 三 章

元件模擬結果與討論

3.1

類型一 模擬結果 首先,探討通道長度漂移對元件之影響。圖 3-1 為通道長度漂移 (± 10%) 所引起之起始電壓變量比較圖,由圖中可觀察到,對低掺雜濃度的 元件,通道長度漂移對鰭式場效電晶體所引起的起始電壓變量最小,而 對類似平面電晶體則引起較大的起始電壓變量。由圖 3-2(a)及(b)看出,鰭 式場效電晶體對短通道效應有較佳的抑制,特別是對低掺雜通道元件更 為顯著,是故,通道長度漂移對鰭式場效電晶體所引起的起始電壓變量 最小。 其次,探討兩種鰭狀通道寬度漂移情況(±10%及固定 1.5nm偏移量) 對元件的起始電壓所造成的影響。圖 3-3(b)顯示出,對低通道掺雜元件, 三閘極電晶體的起始電壓變量最大。由於鰭狀通道寬度漂移,將影響元 件兩側閘極(Side Gate)的對通道的控制能力。就元件的長寬比而言,鰭式 場效電晶體和三閘極電晶體的兩側閘極為最主要的通道控制來源,是故 受到鰭狀通道寬度漂移影響應最為明顯。由圖 3-4(a)可看到,隨著鰭狀通 道寬度逐漸減小,兩側閘極對通道控制能力漸增,進而更加有效的抑制 短通道效應,於是對於擁有最小鰭狀通道寬度的鰭式場效電晶體,因此 具有很好的electrostatics,當鰭狀通道寬度漂移量不大時(1.5nm),並不會 導致太大的起始電壓變量;反觀類似平面電晶體,其兩側閘極對通道控 制能力非主要項,於是元件的起始電壓受到鰭狀通道寬度漂移影響相對較小。對高通道掺雜元件,則以鰭式場效電晶體的起始電壓變量最大。 由圖 3-4(b),隨著鰭狀通道寬度逐漸減少,起始電壓對鰭狀通道寬度漂移 的敏感度亦跟隨增加,此一現象乃由逆窄通道效應(Reversed Narrow Width Effect) 所導致[13]。是故具有最小鰭狀通道寬度(Wfin)的鰭式場效

電晶體,因鰭狀通道寬度漂移引起的起始電壓變量也將最大。 接著,探討兩種鰭狀通道高度漂移情況(±10%及固定 1.5nm 偏移量) 所引起的效應。由圖 3-5(a)及(b)觀察到,低通道掺雜類似平面電晶體的起 始電壓變量最大。判斷原因為,鰭狀通道高度漂移將對元件上方閘極(Top Gate)的通道控制能力造成衝擊,就元件的長寬比而言,類似平面電晶體 的上方閘極(Top Gate)為最主要的通道控制來源,是故受到鰭狀通道高度 漂移影響最為據烈,而導致最大的起始電壓變量。藉由圖 3-6 可驗證此一 推論,在固定的鰭狀通道寬度下,鰭狀通道高度變化將會改變起始電壓 對通道長度漂移的敏感度,亦即,元件上方閘極(Top Gate)的通道控制能 力會受到鰭狀通道高度漂移的影響。 圖 3-7 及圖 3-8 分別為閘極氧化層厚度漂移(±10%)引起之起始電壓變 量比較圖及通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖。兩圖 皆呈現出一共同的趨勢,對於高通道掺雜元件,起始電壓變量受這兩項 製程參數漂移的影響遠較低通道掺雜元件所受的影響大,原因為,對高 通道掺雜元件而言,閘極氧化層厚度和通道掺雜濃度是決定元件起始電 壓的重要參數。另外,此兩種製程參數漂移對起始電壓變量的影響,並 不會因元件的長寬比不同而有明顯的差異。 而隨機掺雜濃度變動對元件起始電壓之影響,可藉由圖 3-9 來加以討 論。該圖顯示,對高通道掺雜元件,類似平面電晶體受隨機掺雜濃度變

平面電晶體的通道體積最大,使其因隨機掺雜濃度變動而引起的通道掺 雜濃度漂移量最小;另外,由圖 3-10(b)所示,高通道掺雜的三種元件之 起始電壓對通道掺雜濃度的敏感度非常接近,類似平面電晶體於是具有 最小的起始電壓變量。然而,對低通道掺雜元件,類似平面電晶體的起 始電壓變量卻最大。由圖 3-10(a)可看出,雖然類似平面電晶體依然擁有 最大的通道體積,但是由於低通道掺雜類似平面電晶體的起始電壓,對 通道掺雜濃度變化較其它兩者敏感,而導致最大的起始電壓變量。 本節最後對各個製程參數漂移及隨機掺雜濃度變動,所引起之起始 電壓變量做加總並比較,藉以瞭解那一種長寬比元件具有較小的起始電 壓變化。圖 3-11 為不同長寬比的厚絕緣層多重閘極電晶體的起始電壓變 量總和比較圖,由圖中可看出,對低掺雜通道元件而言,鰭式場效電晶 體具有最小的起始電壓變量總和,主要乃因其對製程參數漂移及隨機掺 雜濃度變動的忍受度較高;然而,對高掺雜通道元件而言,類似平面電 晶體則具有較小的起始電壓變量總和,主要原因為在一固定的總通道寬 度下,其隨機掺雜濃度變動較小所致。

3.2

類型二 模擬結果 圖 3-12 為通道長度漂移對起始電壓變量的比較圖,相較於類型一的 該項製程參數漂移之結果,通道長度漂移對矽基底低掺雜通道元件的起 始電壓影響較大。原因如圖 3-13(b)所示,矽基底多重閘極電晶體的矽基 底有漏電流(Leakage),而使元件通道的控制能力變差。 圖 3-14 為鰭狀通道寬度漂移引起之起始電壓變量比較圖,所得結果 與類型一的該項製程參數漂移之結果極為接近。 鰭狀通道高度漂移對起始電壓之影響,可由圖 3-15 來探討。與類型一相較,對於低通道掺雜的類似平面電晶體,因矽基底的漏電流位於通 道下方,較不易受到上方閘極的控制,於是鰭狀通道高度漂移對起始電 壓變量,較類型一的該項製程參數漂移,所引起的起始電壓變量較小些。 圖 3-16 及圖 3-17 分別為閘極氧化層厚度漂移(±10%)引起之起始電壓 變量比較圖及通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖。所 得結果與類型一的該項製程參數漂移之結果極為接近。 圖 3-18 為隨機掺雜濃度變動對元件起始電壓之影響。結果亦與類型 一的該項製程參數漂移之結果極為接近。 圖 3-19 為矽基底掺雜濃度變動引起之起始電壓變量比較圖,對低掺 雜通道元件及高掺雜通道元件,矽基底掺雜濃度變動對各個元件的起始 電壓皆不造成改變。 圖 3-20 為不同長寬比的矽基底多重閘極電晶體的起始電壓變量總和 比較圖,同樣地,對低掺雜通道元件,鰭式場效電晶體具有最小的起始 電壓變量總和,而對高掺雜通道元件,類似平面電晶體則具有較小的起 始電壓變量總和。另外,當矽基底被採用來製作多重閘極金氧半場效電 晶體時,類平面場效電晶體的 electrostatics 將會變差,進而影響短通道控 制能力。

3.3

類型三模擬結果 圖 3-21(a)為通道長度漂移對起始電壓變量的比較圖。對低掺雜通道 元 件 及 低 掺 雜 通 道 元 件 而 言 , 因 鰭 式 場 效 電 晶 體 一 樣 具 有 最 佳 的 electrostatics,導致其起始電壓變量最小。圖 3-22(a)及(b)為厚絕緣層(類distribution)圖。由圖 3-22(b)可觀察到,當採用薄絕緣層及類接地面基底 來製作多重閘極電晶體時,可有效地抑制厚絕緣層中的邊緣效應,進而 改善元件的短通道控制能力;另外,類接地面基底使得電位皆分布於薄 絕緣層之上,而使元件 electrostatics 得到改善,尤其是對上方閘極為主要 通道控制的類似平面電晶體的得到的改善最大。圖 3-21(b),則呈現出兩 種類型,對應不同長寬比元件間的起始電壓變量差異。低掺雜通道元件 類似平面電晶體及三閘極電晶體的 electrostatics 因薄絕緣層及類接地面 基底得到很大的改善,使其具有較好的短通道控制能力,進而大幅減少 了起始電壓變量。 圖 3-23(a)、(b)及圖 3-24(a)、(b)分別為鰭狀通道寬度漂移(±10%、1.5nm) 引起之起始電壓變量比較圖及鰭狀通道高度漂移(±10%、1.5nm)引起之起 始電壓變量比較圖。所得結果與類型一的該項製程參數漂移之結果相比 較,在低掺雜通道元件可看到較大的差異,類似平面電晶體 electrostatics 得到的改善最大,而得到較類型一小的起始電壓變量。 圖 3-25 及圖 3-26 分別為閘極氧化層厚度漂移(±10%)引起之起始電壓 變量比較圖及通道掺雜濃度漂移(±10%)引起之起始電壓變量比較圖。所 得結果與類型一的該項製程參數漂移之結果極為接近。 圖 3-27 為隨機掺雜濃度變動對元件起始電壓之影響。類型一的該項 製程參數漂移之結果相比較,發現對於低通道掺雜類似平面電晶體有較 大的差異。原因可由圖 3-28(a) 及(b)中看出,本類型的類似平面電晶體之 electrostatic 得到很好的改善,進而降低元件起始電壓對通道摻雜變化的 敏感度,於是具有較高的隨機掺雜濃度變動抗擾性。 圖 3-29 為埋層氧化層厚度變動引起之起始電壓變量比較圖。低通道 掺雜類似平面電晶體的起始電壓受到埋層氧化層厚度變動引起的變量最

大。原因為薄埋層氧化層與高濃度掺雜(6E18 cm-3)的類接地面(Ground Plane)基底對通道的垂直電場對通道控制能力的加強作用,使原本上方閘 極為主要通道控制來源的類似平面電晶體,所受到的影響較其它兩者來 得大。 圖 3-30 為矽基底掺雜濃度變動引起之起始電壓變量比較圖,對低掺 雜通道元件及高掺雜通道元件,矽基底掺雜濃度變動對兩種類型中各個 元件的起始電壓皆不造成改變,乃因矽基底掺雜濃度±10% 的變動,對原 本即為高濃度掺雜(6E18 cm-3 )的類接地面(Ground Plane)基底,所造成的 影響很小所致。 圖 3-31 為不同長寬比的厚/薄絕緣層多重閘極電晶體的起始電壓變 量總和比較圖,和類型一所得到的結果一樣,對低掺雜通道元件,鰭式 場效電晶體具有最小的起始電壓變量總和,而對高掺雜通道元件,類似 平面電晶體具有較小的起始電壓變量總和。相較於類型一的電壓變量總 和,不論對低掺雜通道元件或高掺雜通道元件,薄埋層氧化層與高濃度 掺雜的類接地面基底的搭配,可有效加強元件對通道的控制能力,尤其 是對低掺雜通道元件的改善最為明顯。

3.4 總結

模擬的結果顯示,三種類型的元件中,對低掺雜通道的多重閘極金 氧半場效電晶體元件,因鰭式場效電晶體對製程參數變異及隨機掺雜濃 度變動具有較佳的抗擾性,皆可得到最小的起始電壓漂移量。而對高掺 雜通道的多重閘極金氧半場效電晶體元件,因類平面場效電晶體具有較 小的隨機掺雜濃度變動,故可得到較小的起始電壓漂移量。圖 3-32(a)及

對三種類型的起始電壓變量總和比較圖。由圖 3-32(a),對於低掺雜通道 鰭式場效電晶體無採用薄絕緣層的需要;而由圖 3-32(b),高掺雜通道類 平 面 場 效 電 晶 體 採 用 薄 絕 緣 層 及 類 接 地 面 基 底 可 得 到 較 佳 的 electrostatics。

0

10

20

30

40

50

60

70

80

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 20 22.5 25 27.5 30 32.5 35 37.5 40 Vth (V ) Lg(nm) FinFET Tri-gate Q.Planar (a) -0.07 -0.06 -0.05 -0.04 -0.03 -0.02 -0.01 0 0.01 0.02 0.03 20 22.5 25 27.5 30 32.5 35 37.5 40 Vth (V ) Lg(nm) FinFET Tri-gate Q.Planar Doping=1E17 cm-3 Wtotal=75nm tHfO2=2nm, VDS=0.05V Doping=6E18cm-3 Wtotal=75nm tOX=1nm, VDS=0.05V (b) 圖 3-2 起始電壓對通道長度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件

0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration(cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 10 15 20 25 30 35 40 45 Vth (V) Wfin(nm) FinFET Tri-gate Q.Planar Doping=1E17cm-3 Lg=25nm tHfO2=2nm, VDS=0.05V (a) -0.08 -0.07 -0.06 -0.05 -0.04 -0.03 -0.02 -0.01 0 10 15 20 25 30 35 40 45 Vth (V) Wfin(nm) FinFET Tri-gate Q.Planar Doping=6E18cm-3 Lg=25nm tOX=1nm, VDS=0.05V (b) 圖 3-4 起始電壓對鰭狀通道寬度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件

0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 20 22.5 25 27.5 30 32.5 35 37.5 40

V

th(V)

L

g(nm)

Hfin_15nm

Hfin_25nm

Doping=1E17 cm-3 tHfO2=2nm, VDS=0.05V 圖 3-6 不同鰭狀通道高度的三閘極電晶體起始電壓對通道長度之關係圖0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Conerntration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

10

20

30

40

50

60

70

80

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0.25 0.3 0.35 0.4 0.45 0.5 0.55

1.5E+10 5.0E+17 1.0E+18 1.5E+18 2.0E+18

Vth (V) NCH(cm-3) FinFET Trigate Q.Planar (a) -0.1 -0.09 -0.08 -0.07 -0.06 -0.05 -0.04 -0.03 -0.02 -0.01 0

4.0E+18 5.0E+18 6.0E+18 7.0E+18

Vth (V) NCH(cm-3) FinFET Trigate Q.Planar Doping=6E18 cm-3 Wtotal=75nm, Lg=25nm tOX=1nm, VDS=0.05V Doping=1E17 cm-3 Wtotal=75nm, Lg=25nm tHfO2=2nm, VDS=0.05V (b) 圖 3-10 起始電壓對通道掺雜濃度之關係圖 (a)低掺雜通道元件;(b)高掺雜通道元件

74 44 16 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2 ∆ Vth ,t o ta l (m V ) Aspect Ratio (a) 45 47 52 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2 ∆ Vth ,to ta l (m V ) Aspect Ratio (b) 圖 3-11 厚絕緣層多重閘極電晶體的起始電壓變量總和

0

10

20

30

40

50

60

70

80

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(a)

(b)

0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm -3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

10

20

30

40

50

60

70

80

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

78 44 17 74 44 16 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2 ∆ Vth,t ota l (m V) Aspect Ratio scenario #2 (bulk) scenario #1 (100nm-box) (a) 46 48 53 45 47 52 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2

∆

V

th ,t o ta l(m

V)

Aspect Ratio

scenario #2 (bulk) scenario #1 (100nm-box) (b) 圖 3-20 厚絕緣層/矽基底多重閘極電晶體的起始電壓變量總和比較圖 (a)低掺雜通道元件;(b)高掺雜通道元件0 10 20 30 40 50 60 70 80 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 10 20 30 40 50 60 70 80 0.5 1 2 ∆ Vth (m V ) Aspect Ratio 10nm-BOX 100nm-BOX (b) 圖 3-21 (a)通道長度漂移(±10%)引起之起始電壓變量比較圖

D

S

(a)S

D

(b) 圖 3-22 類似平面電晶體的電位分布圖 (a) 厚絕緣層(類型一);(b)薄絕緣層(類型三)0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm-3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar) (a) 0 5 10 15 20 25 30 35 40 1.0E+17 6.0E+18 ∆ Vth (m V ) Doping Concentration (cm -3)

Hfin= 2Wfin (FinFET) Hfin= Wfin (Tri-gate) Hfin=1/2Wfin (Q.Planar)

(b)

圖 3-24 鰭狀通道高度漂移引起之起始電壓變量比較圖 (a)±10%漂移量;(b)1.5nm 固定漂移量

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration(cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration(cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

10

20

30

40

50

60

70

80

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0.25 0.3 0.35 0.4 0.45 0.5 0.55

1.5E+10 5.0E+17 1.0E+18 1.5E+18 2.0E+18

Vth (V) NCH(cm-3) FinFET Trigate Q.Planar (a) 0.25 0.3 0.35 0.4 0.45 0.5 0.55

1.5E+10 5.0E+17 1.0E+18 1.5E+18 2.0E+18

Vth (V) NCH(cm-3) FinFET Trigate Q.Planar Doping=1E17 cm-3 Wtotal=75nm, Lg=25nm tHfO2=2nm, VDS=0.05V Doping=1E17 cm-3 Wtotal=75nm, Lg=25nm tHfO2=2nm, VDS=0.05V (b) 圖 3-28 低摻雜通道元件的起始電壓對通道摻雜濃度關係圖 (a) 厚絕緣層(類型一);(b)薄絕緣層(類型三)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

0

5

10

15

20

25

30

35

40

1.0E+17

6.0E+18

∆

V

th(m

V

)

Doping Concentration (cm

-3)

Hfin= 2Wfin (FinFET)

Hfin= Wfin (Tri-gate)

Hfin=1/2Wfin (Q.Planar)

74 44 16 35 30 14 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2 ∆ Vth ,to ta l (m V ) Aspect Ratio scenario #1 (100nm-box) scenario #3 (10nm-box) (a) 45 47 52 41 44 48 0 10 20 30 40 50 60 70 80 90 100 0.5 1 2 ∆ Vth ,to ta l (m V ) Aspect Ratio scenario #1 (100nm-box) scenario #3 (10nm-box) (b) 圖 3-31 厚/薄絕緣層多重閘極電晶體的起始電壓變量總和比較圖

16 17 14 0 10 20 30 40 50 60 70 80

scenario 1 scenario 2 scenario 3

∆ Vth ,t o tal (m V ) (a) 45 46 41 0 10 20 30 40 50 60 70 80

scenario 1 scenario 2 scenario 3

∆ Vth ,to ta l (m V ) (b) 圖 3-32 三種類型的起始電壓變量總和比較圖 (a)低通道掺雜鰭式場效電晶體;(b)高通道掺雜類似平面電晶體

第 四 章

結論與展望

4.1 結論

在本論文中探討了三種基底類型對應不同長寬比的多重閘極電晶 體,因製程參數漂移及隨機掺雜濃度變動,對元件的起始電壓所造成之 影響。由模擬的結果中,我們觀察到製程漂移引起的鰭狀通道高度 (fin-height)及鰭狀通道寬度(fin-width)變化,對不同長寬比的低掺雜通道 元件之起始電壓的影響不盡相同。低掺雜通道元件對元件的長寬比具有 相依性,亦即對不同長寬比的元件,在一固定的總通道寬度(Wtotal)下,製 程參數漂移會引起不同的起始電壓變異。相反的,高掺雜通道元件對元 件的長寬比則幾近乎不具有相依性。 由三種類型(厚絕緣層、矽基底及薄絕緣層)多重閘極金氧半場效電 晶體的模擬結果及所呈現的趨勢來觀察,我們可以得到如下幾個結論: (1) 對低掺雜通道的多重閘極金氧半場效電晶體元件,因鰭式場效電 晶體(AR=2)具有較佳的 electrostatics,是故由製程參數漂移所引 起的起始電壓變量較小。 (2) 對低掺雜通道的多重閘極金氧半場效電晶體元件,因鰭式場效電 晶體(AR=2)對通道摻雜的敏感度較低,使其對隨機掺雜濃度變動 的抗擾性較高。 (3) 對高掺雜通道的多重閘極金氧半場效電晶體元件,因類平面場效 電晶體(AR=1/2)對隨機掺雜濃度變動的抗擾性較高,使其具有較(4) 當矽基底被採用來製作多重閘極金氧半場效電晶體時,類平面場 效電晶體(AR=1/2)的 electrostatics 將會變差。 (5) 當薄絕緣層與高摻雜的接地平面基底被採用來製作多重閘極金 氧半場效電晶體時,將可改善低掺雜通道的類平面場效電晶體 (AR=1/2)及三閘極場效電晶體(AR=1)的 electrostatics。但對於鰭 式場效電晶體(AR=2)則無採用薄絕緣層的需要。 (6) 採用薄絕緣層與高摻雜的類接地平面基底來製作多重閘極金氧 半場效電晶體,可增強元件對隨機掺雜濃度變動的抗擾性,尤其 是對低掺雜通道類平面場效電晶體(AR=1/2)的改善最為明顯。 由於厚絕緣層及矽基底兩種類型元件對起始電壓的抗擾度非常接 近,因矽基底多重閘極金氧半場效電晶體因具有較低的晶圓成本,對金 氧半製程相容性高及具有較佳的熱散逸等特性,如採用的為高掺雜通道 元件時,不失為一良好選擇。而薄絕緣層多重閘極金氧半場效電晶體, 因絕緣層的邊緣效應(Electric-field fringing)得到抑制,及類接地面基底可 得到較好元件起始電壓的抗擾度,對低掺雜通道類似平面電晶體及三閘 極電晶體,薄絕緣層與高摻雜的接地平面基底應為最佳選擇,但較薄厚 度的埋層氧化層在製程上的挑戰,是採用此種基底所需面臨的問題。

4.2 後續工作

本論文已針對各種製程參數漂移及隨機掺雜濃度變動,在低汲極電壓(Low drain bias)下,對各元件起始電壓的影響做一全面性探討,但對於 元件在高汲極電壓(High drain bias)下,製程參數漂移及隨機掺雜濃度變動 對元件起始電壓特性的影響則尚未探討,是未來可以繼續研究的部份。

而對於矽基底多重閘極金氧半場效電晶體(類型二),貫穿阻止植入 (punch through stopper implantation)對元件特性的影響亦未被探討。藉由 增加此一製程手續,應可降低漏電流,進而減小元件的短通道效應,得 到較佳的起始電壓抗擾度,是此類型元件可繼續深入探討的部分。 另外,隨著元件的尺寸微縮持續進行,量子效應(Quantum effect)對 元件特性所產生的影響,則需加以考量。

參考文獻

[1] G. Knoblinger et al., “Multi-Gate MOSFET Design,” ESSDRC, pp.65-68, Sept. 2006.

[2] O. Faynot et al., “Advanced SOI technologies: advantages and drawbacks,” International Workshop on Junction Technology, pp.200-203, May 2006.

[3] Nagumo, T and Hiramoto, T, “Design Guideline of Multi-Gate MOSFETs

with Substrate-Bias Control,” IEEE Transactions on Electron Device, Vol.53, Issue 12, pp.3025-3031, Dec. 2006.

[4] A. V-Y Thean et al., “Performance and Variability Comparisons between Multi-Gate FETs and Planar SOI Transistors,” EDM, pp.1-4, Dec.2006. [5] Aniket Breed and Kenneth P. Roenker, “Comparison of the scaling

characteristics of nanoscale silicon N-channel multiple-gate MOSFETs,”

Circuit and System, Vol. 1, pp.603-606, Aug. 2005.

[6] S. Inaba et al., “FinFET: the prospective multi-gate device for future SoC applications,” ESSDRC, pp.49-52, Sept. 2006.

[7] Jong-Ho Lee et al., “Device Design Consideration for 50nm Dynamic Random Access Memory Using Bulk FinFET,” Japan Journal of Applied

Physics, Vol. 44, No. 4B, pp.2176-2179, 2005.

[8] Hey Jin Cho et al., “’The Vth Controllability of 5nm Body-Tied CMOS FinFET,” VLSI Technology, pp.116-117, April 2005.

[9] Lisa T. Su et al., “Deep-Submicrometer Channel Design in Silicon-on-Insulator (SOI) MOSFET’s,” IEEE Electron Device Letter, Vol.15, Issue 5, pp.183-185, May 1994.

[10] Jyi-Tsong Lin et al., “Recessed Multi-Gate SOI MOSFET in deep deca-nanometer regime,” IEEE International SOI Conference, pp.47-48,

Oct. 20001.

[11] Seung-Hwan Kim et al., “Bulk inversion in FinFETs and implied insights on effective gate width,” IEEE Transactions on Electron

Device, Vol.52, Issue 9, pp.1993-1997, Sept. 2005.

[12] V.P. Trivedi and J.G. Fossum, “Nanoscale FD/SOI CMOS: Thick or Thin BOX?,” IEEE Electron Device Letters Vol.26, No. 1, pp.26-28, Jan. 2005.

[13] Yu-Sheng Wu and Pin Su, “Investigation of Variability for Multi-Gate MOSFETs Using Analytical Solution of 3-D Poisson’s Equation” Silicon

Nanoelectronics Workshop, pp.87-88, June. 2007.

[14] Y. Taur and T.H. Ning, “Fundamentals of Modern VLSI Device,” Cambridge University Press, 1997.

[15] James B. Kuo and Shih-Chia Lin, “LOW-VOLTAGE SOI CMOS VLSI DEVICES AND CIRCUIT,” WILEY Press, 2001.

[16] ISE TCAD Release 10.0 Manual.

A.1 Input deck of heavily doped FinFET (DEVISE) (define Xcha (* 0.5 0.015)) (define Ycha (* 0.5 0.025)) (define Zcha 0.03) (define Tgox 0.001) (define Tbox 0.1) (define bodydoping 6e18) (define Xgox (+ Xcha Tgox)) (define Ygox Ycha) (define Zgox (+ Zcha Tgox)) (define Xsd Xcha) (define Ysd (+ Ycha 0.02)) (define Zsd Zcha) (define Xbox (* 3 Xcha)) (define Ybox Ysd) (define Zbox (* -1 Tbox))

;---; ;--- Channel

(isegeo:create-cuboid (position 0 (* -1 Ycha) 0) (position Xcha Ycha Zcha) "Silicon" "channel" ) ;--- Gate Oxide

(isegeo:set-default-boolean "BAB")

(isegeo:create-cuboid (position 0 (* -1 Ygox) 0) (position Xgox Ygox Zgox) "Oxide" "gate_oxide" ) ;--- Poly Gate

(isegeo:create-cuboid (position 0 (* -1 Ygox) 0) (position (+ 0.001 Xgox) Ygox (+ 0.001 Zgox)) "PolySi" "Gate") ;--- contact gate

(define GateID (find-body-id (position 0 Ygox (* 0.5 (+ Zgox (+ 0.001 Zgox))) ) )) (isegeo:define-contact-set "gate" 4 (color:rgb 1 0 0 ) "##" )

(isegeo:set-current-contact-set "gate") (isegeo:set-contact-boundary-faces GateID) (isegeo:delete-region GateID )

;--- contact Source/Drain

(isegeo:create-cuboid (position 0 Ycha 0) (position Xsd Ysd Zsd) "Silicon" "drain_region" )

(isegeo:create-cuboid (position 0 (* -1 Ycha) 0) (position Xsd (* -1 Ysd) Zsd) "Silicon" "source_region" ) ;--- BOX

(isegeo:create-cuboid (position 0 (* -1 Ybox) 0) (position Xbox Ybox Zbox) "Oxide" "BOX" ) ;--- contact substrate

(isegeo:define-contact-set "substrate" 4 (color:rgb 1 0 0 ) "##" ) (isegeo:set-current-contact-set "substrate")

(isegeo:set-contact-faces (find-face-id (position (* 0.5 Xbox) 0 Zbox))) ;---; ;--- imprint for S/D

(isegeo:imprint-rectangular-wire (position 0 (+ 0.005 Ycha) Zcha) (position Xsd Ysd Zcha))

(isegeo:imprint-rectangular-wire (position 0 (* -1 (+ 0.005 Ycha)) Zcha) (position Xsd (* -1 Ysd) Zcha)) ;---;

;--- contact drain

(isegeo:define-contact-set "drain" 4 (color:rgb 1 0 0 ) "##" ) (isegeo:set-current-contact-set "drain")

(isegeo:set-contact-faces (find-face-id (position (* 0.5 Xsd) (* 0.5 (+ Ysd (+ 0.005 Ycha))) Zsd))) ;--- contact source

(isegeo:define-contact-set "source" 4 (color:rgb 1 0 0 ) "##" ) (isegeo:set-current-contact-set "source")

(isegeo:set-contact-faces (find-face-id (position (* 0.5 Xsd) (* -1 (* 0.5 (+ Ysd (+ 0.005 Ycha)))) Zsd))) ;---;

;--- doping Si

(isedr:define-constant-profile "body_doping" "BoronActiveConcentration" bodydoping) (isedr:define-constant-profile-material "body_doping" "body_doping" "Silicon")

(isedr:define-refinement-window "drain_doping" "Cuboid" (position (* -1 Xsd) Ycha 0) (position Xsd Ysd Zsd)) (isedr:define-constant-profile "drain_doping" "ArsenicActiveConcentration" 2e20)

(isedr:define-constant-profile-placement "drain_doping" "drain_doping" "drain_doping") ;--- doping source

(isedr:define-refinement-window "source_doping" "Cuboid" (position (* -1 Xsd) (* -1 Ycha) 0) (position Xsd (* -1 Ysd) Zsd)) (isedr:define-constant-profile "source_doping" "ArsenicActiveConcentration" 2e20)

(isedr:define-constant-profile-placement "source_doping" "source_doping" "source_doping") ;--- mesh Si

(isedr:define-refinement-size "Si_Mesh" (/ Xsd 2.5) (/ Ysd 2.5) (/ Zsd 2.5) (/ Xsd 5) (/ Ysd 5) (/ Zsd 5)) (isedr:define-refinement-material "Si_Mesh" "Si_Mesh" "Silicon" )

(isedr:define-refinement-function "Si_Mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh main

(isedr:define-refinement-window "main_mesh" "Cuboid" (position 0 (* -1 (+ Ycha Tgox)) 0) (position Xcha (+ Ycha Tgox) Zgox)) (isedr:define-refinement-size "main_mesh" (/ Xsd 8) (/ Ysd 10) (/ Zsd 8) (/ Xsd 20) (/ Ysd 100) (/ Zsd 20) )

(isedr:define-refinement-placement "main_mesh" "main_mesh" "main_mesh" )

(isedr:define-refinement-function "main_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh BOX

(isedr:define-refinement-window "BOX_mesh" "Cuboid" (position 0 (* -1 Ybox) 0) (position Xbox Ybox (* -1 Zcha))) (isedr:define-refinement-size "BOX_mesh" (/ Xbox 4) (/ Ybox 4) (/ Zcha 3) (/ Xbox 8) (/ Ybox 8) (/ Zcha 8) ) (isedr:define-refinement-placement "BOX_mesh" "BOX_mesh" "BOX_mesh" )

(isedr:define-refinement-function "BOX_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh total

(isedr:define-refinement-window "total_mesh" "Cuboid" (position 0 (* -1 Ybox) 0) (position Xbox Ybox Zbox)) (isedr:define-refinement-size "total_mesh" (/ Xbox 3) (/ Ybox 3) (/ (* -1 Zbox) 3) (/ Xbox 5) (/ Ybox 5) (/ (* -1 Zbox) 5) ) (isedr:define-refinement-placement "total_mesh" "total_mesh" "total_mesh" )

(isedr:define-refinement-function "total_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh topoxide

(isedr:define-refinement-window "topoxide_mesh" "Cuboid" (position 0 (* -1 Ygox) (- Zcha Tgox)) (position Xgox Ygox (+ Zcha Tgox)))

(isedr:define-refinement-size "topoxide_mesh" (/ Xsd 5) (/ Ysd 5) (/ Tgox 3) (/ Xsd 20) (/ Ysd 20) (/ Tgox 6) ) (isedr:define-refinement-placement "topoxide_mesh" "topoxide_mesh" "topoxide_mesh" )

(isedr:define-refinement-function "topoxide_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh buriedoxide

(isedr:define-refinement-window "buriedoxide_mesh" "Cuboid" (position 0 (* -1 Ygox) (* -1 Tgox)) (position Xgox Ygox Tgox)) (isedr:define-refinement-size "buriedoxide_mesh" (/ Xsd 5) (/ Ysd 5) (/ Tgox 3) (/ Xsd 20) (/ Ysd 20) (/ Tgox 6) )

(isedr:define-refinement-placement "buriedoxide_mesh" "buriedoxide_mesh" "buriedoxide_mesh" ) (isedr:define-refinement-function "buriedoxide_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- mesh frontoxide

(isedr:define-refinement-window "frontoxide_mesh" "Cuboid" (position (- Xcha Tgox) (* -1 Ygox) 0) (position Xgox Ycha Zgox)) (isedr:define-refinement-size "frontoxide_mesh" (/ Tgox 3) (/ Ysd 5) (/ Zsd 5) (/ Tgox 6) (/ Ysd 20) (/ Zsd 20) )

(isedr:define-refinement-placement "frontoxide_mesh" "frontoxide_mesh" "frontoxide_mesh" ) (isedr:define-refinement-function "frontoxide_mesh" "DopingConcentration" "MaxTransDiff" 1) ;--- save BND and CMD

(ise:assign-material-and-region-names (part:entities (filter:type "solid?"))) (iseio:save-dfise-bnd (part:entities (filter:t pe "solid?")) "@boundary/o@") y (isedr:write-cmd-file "@commands/o@")

A.2 Input deck of heavily doped FinFET (DESSIS) File { * input files: Grid="@grid@" Doping="@doping@" * output files: Plot="@dat@" Current="@plot@" Output="@log@" } Electrode {

{ Name="gate" Voltage=-0.3 barrier=-0.55} { Name="substrate" Voltage=0} { Name="drain" Voltage=0.0} { Name="source" Voltage=0} } Physics { EffectiveIntrinsicDensity(OldSlotboom)

Recombination(SRH(DopingDependence) Auger Avalanche(Eparallel)) }

Plot {

eDensity hDensity eCurrent hCurrent DisplacementCurrent

Potential SpaceCharge ElectricField hMobility eVelocity hVelocity

Doping DonorConcentration AcceptorConcentration } Math { Extrapolate Derivatives RelErrControl Digits=5 ErRef(electron)=1.e10 ErRef(hole)=1.e10 Notdamped=50 Iterations=30 Newdiscretization Directcurrent Method=ParDiSo -VoronoiFaceBoxMethod NaturalBoxMethod } Solve { Coupled(iterations=150) { Poisson } Coupled { Poisson Electron } NewCurrentFile="n@node@_init" Quasistationary(

InitialStep=1e-1 Increment=5 Minstep=1e-2 MaxStep=0.5 Goal{ name="drain" voltage=0.05 } ){

Coupled { Poisson Electron } }

Quasistationary ( DoZero

InitialStep=1e-1 Increment=5 Minstep=1e-2 MaxStep=0.5 Goal { Name="gate" Voltage=-0.3 } ) { Coupled { Poisson Electron} } #-ramp gate:

NewCurrentFile="" Quasistationary ( DoZero

InitialStep=1e-2 Increment=1.5 Minstep=1e-5 MaxStep=0.01 Goal { Name="gate" Voltage=0.4 } )