國

立

交

通

大

學

電機學院 IC 設計產業研發碩士班

碩

士

論

文

無外部電容的 CMOS 低壓差線性穩壓器

A Capacitor-Free CMOS Low Dropout Linear Voltage Regulator

研 究 生:曾南雄

指導教授:陳科宏 教授

無外部電容的 CMOS 低壓差線性穩壓器

A Capacitor-Free CMOS Low Dropout Linear Voltage Regulator

研 究 生:曾南雄 Student:Nan-Hsiung Tseng

指導教授:陳科宏 Advisor:Ke-Horng Chen

國 立 交 通 大 學

電機學院

IC 設計產業研發碩士班

碩 士 論 文

A ThesisSubmitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master

in

Industrial Technology R & D Master Program on IC Design

Jan 2007

中華民國九十六年一月

無外部電容的 CMOS 低壓差線性穩壓器

學生:曾南雄 指導教授:陳科宏博士

國立交通大學電機學院 IC 設計產業研發碩士班

摘 要

近年來,由於可攜式電子產品的快速發展,開發低功耗的電路來延長電池壽命己成為 主要的研究主題。同時為了達到產品的輕薄、短小,將電路積體化及減少外部元件的使 用已經是必要的趨勢。 一般的電源管理系統通常會包含幾組低壓差線性穩壓器及交換式的直流轉換器。傳統 的低壓差線性穩壓器需要一個很大的輸出電容大約幾微法拉,如此大的電容並不容易作 在IC 內部,並且需要佔據較大的電路板面積及成本。本論文的目標是設計一個無需外部 電容的低壓差線性穩壓器,此低壓差線性穩壓器是架構在三級的放大器設計,能同時兼 顧穩定度、精準度、暫態響應及其它各項效能。所設計的規格是最大負載電流 100mA,輸 入電壓在 1.5V~4.5V,輸出電壓在 1.3V, ,Dropout Voltage 在 200mV,使用 TSMC 0.35 μm 2P4M CMOS 製程,包含參考電壓源僅消耗 46μA 的靜態電流。 實驗的結果証明所實作的低壓差線性穩壓器在穩定度及暫態響應都符合所預期的規 格。因此,此低壓差線性穩壓器適合於SOC 的環境使用。A Capacitor-Free CMOS Low Dropout Linear Voltage Regulator

Student: Nan-Hsiung Tseng Advisor: Dr. Ke-Horng Chen

Industrial Technology R & D Master Program of

Electrical and Computer Engineering College

National Chiao Tung University

Abstract

In the recent years, developing of low power circuits to extend battery life has become a critical research topic due to explosion growing of portable electric devices. In order to make products smaller and thinner, this is a necessary trend to integrate the circuit and reduce the external component.

A power management system usually contains serval LDO regulators and switching regulators.The conventional LDO voltage regulator requires a very large output capacitor in the single microfarad range.Large microfarad capacitors can not easy integrated in IC, and take over a large area of PCB, consuming cost.

The target of this paper is to design a low dropout linear voltage regulator without external capcitor. This LDO is based on three stage amplifiers design, and also consider the stability, resolution, transient response and other performances. The design of specification is shown is the following: The maxmium load current is 100mA. The input voltage is ranged from1.5V to 4.5V. The output voltage is 1.3V. The dropout voltage is 200mV. The quiescent current is consuming only 46uA containing the bandgap reference. This LDO is fabricated by TSMC 0.35um 2P4M process.

Experimental results show that the proposed capacitor-free LDO voltage regulator is achieved the expected specification of stability and transient response.Thus, the proposed capacitor-free LDO voltage regulator is suitable for SoC solution.

誌 謝

能夠順利完成論文,首先要由衷地感謝我的指導教授陳科宏博士。在研究所兩年 來,老師提供我一個良好的學習環境,並且在學習和研究上適時的給予我指導和啟發, 使我在課業及處世上受益良多。同時要感謝論文口試的評審委員,王清松教授和黃立仁 博士的寶貴意見,使本論文內容能更加完整。 再來我要感謝 802 及 703 實驗室的同學們在實驗上的協助與指導。也特別感謝小柯、 國林及柏逢在佈局上給予的指導及幫助。 最後, 謹以此篇論文獻給所有關心我的人。

目 錄 中文摘要 i 英文摘要 ii 誌謝 iii 目錄 iv 圖示 vii 表示

x 第一章...1 概論...1 1.1 研究背景... 1 1.2 研究動機及目的... 2 1.3 內容大綱 3 第二章...4 低壓差(LDO)線性穩壓器介紹...4 2.1 基本的低壓差(LDO)線性穩壓器... 4 2.2 LDO線性穩壓器的規格及專有名詞定義... 5 2.2.1 壓降電壓(Dropout Voltage)... 5

2.2.2 靜態電流或接地電流(Quiescent Current or Ground Current)... 6

2.2.3 功率效率(Power efficiency)... 7

2.2.4 線上穩壓(Line Regulation) ... 7

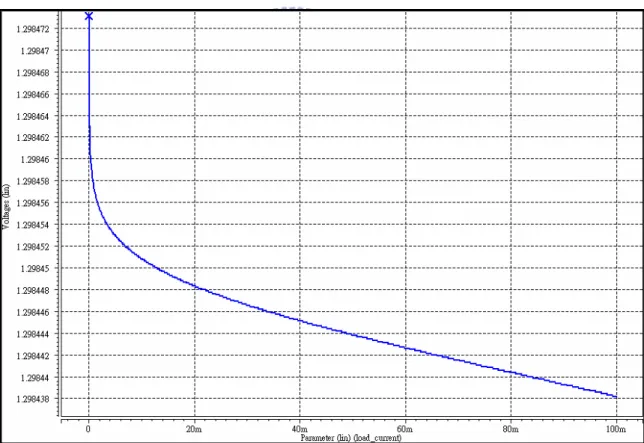

2.2.5 負載穩壓(Load Regulation) ... 9

2.2.6 電源拒斥比(Power Supply Rejection Ratio) ... 9

2.2.7 輸出雜訊(Output Noise) ... 10

2.2.8 精確度(Accuracy)... 11

2.2.9 暫態響應(Transient Response) ... 12

2.3LDO線性穩壓器的設計考量 ... 12

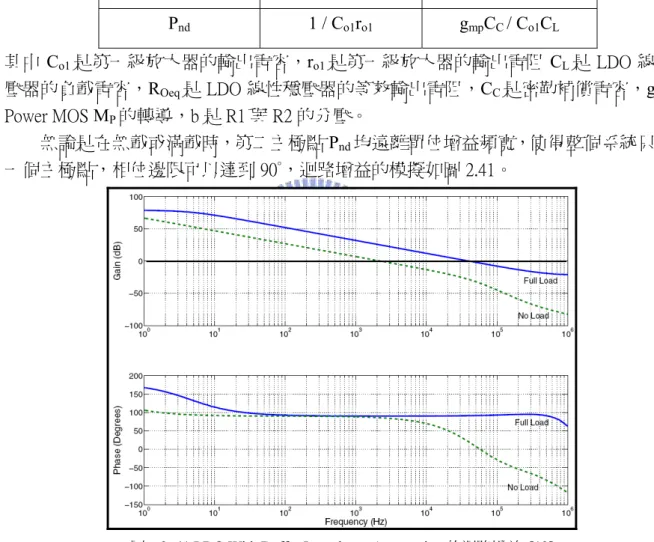

2.3.2 傳統LDO線性穩壓器的穩定度分析 ... 15 2.3.3 暫態響應分析... 20 2.3.4 參考電壓的設計考量... 23 2.3.5 誤差放大器的設計考量... 31 2.3.6 改良傳統LDO線性穩壓器的新架構 ... 35 第三章...39 無外部電容的低壓差(LDO)線性穩壓器...39 3.1 電路架構 39 3.2 實際電路設計... 47 3.2.1 無外部電容的低壓差線性穩壓器電路設計... 47 3.2.2 帶差參考電壓源(BG)及偏壓電路(Biasing Circuit)電路設計 ... 49 起動電路(Start-Up Circuit)... 50 電流源電路... 51 3.3 模擬結果 56 3.3.1 帶差參考電路模擬... 56 3.3.2 低壓差線性穩壓器的模擬... 59 第四章 實體佈局、量測方法及量測結果...76 4.1 實體佈局 76 4.2 量測方法 85 4.2.1 基本的負載暫態產生器... 85 4.2.2 閉迴路的負載暫態產生器... 86 4.3 量測結果 87 4.3.1 無外部電容時的量測結果... 87 4.3.2 有外部電容及ESR電阻時的量測結果 ... 90 第五章 結論及未來研究方向...93 5.1 結論 93 5.2 未來研究方向... 93 參考文獻...94

圖示

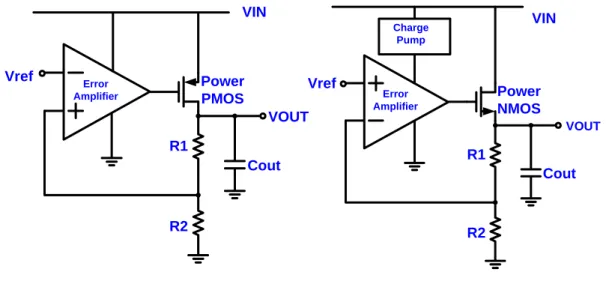

圖 1.1 基本可攜式電子產品的DC-DC電源管理IC架構 ... 2 圖 2.1 基本的LDO線性穩壓器架構[1]... 4 圖 2.2 Vin與Vout的關係圖 ... 6 圖 2.3 LDO線性穩壓器的靜態電流 ... 6 圖 2.4 PMOS的LDO線性穩壓器 ... 8 圖 2.5 LDO線性穩壓器的PSRR [2]... 10 圖 2.6 LDO線性穩壓器的輸出雜訊[10]... 10 圖 2.7 LDO線性穩壓器的暫態響應[2]... 12 圖 2. 8 傳輸電晶體的種類... 13 圖 2.9 PMOS傳輸電晶體LDO 圖 2.10 NMOS傳輸電晶體LDO... 15 圖 2. 11 傳統PMOS LDO線性穩壓器的架構... 15 圖 2. 12 傳統PMOS LDO線性穩壓器的小信號模型 [3]... 16 圖 2. 13 傳統PMOS LDO線性穩壓器的頻率響應 ... 17 圖 2. 14 太大的負載電流將造成系統不穩定... 18 圖 2. 15 太大的ESR造成系統不穩定 ... 19 圖 2. 16 太小的ESR造成系統不穩定 ... 19 圖 2. 17 ESR的穩定範圍 [2]... 19圖 2. 18 AC Open- Loop Gain的Simulation Circuit [5] ... 20

圖 2. 19 量測負載暫態響應的測試電路 [5]... 22 圖 2. 20 LDO線性穩壓器的負載暫態響應 [4]... 22 圖 2. 21 能隙參考電壓電路的基本原理 [6]... 23 圖 2. 22 在CMOS製程技術中垂直的PNP BJT電晶體結構 [7]... 24 圖 2. 23 實際的基本能隙參考電壓電路 [7]... 25 圖 2. 24 與溫度相依的NMOS及PMOS臨限電壓 [8] ... 25 圖 2. 25 一個完全使用MOS電晶體的參考電壓源 [8] ... 26 圖 2. 26 簡單的能隙參考電壓電路 [8]... 27 圖 2. 27 (a)BJT電晶體及(b)電阻的同心軸佈局 [8]. ... 27 圖2.28 (a)使用誤差放大器為基礎的能隙參考電壓電路. (b)簡單的差動對放大器 [9]. ... 29 圖2. 29 一個改善電源拒斥比的能隙參考電壓電路[9]... 29 圖2. 30 PN接面所形成的寄生電容及電阻[9]... 30 圖2. 31 輸入側的PSRR[9]. ... 30 圖2. 32 輸出側的PSRR[9]. ... 30 圖2. 33 長通道及短通道PMOS電流鏡的PSRR[9]. ... 31 圖2. 34 使用電壓緩衝器的LDO線性穩壓器[11]... 32

圖 2. 35 使用電壓緩衝器的LDO線性穩壓器Loop Gain[11]... 33

圖 2. 36 使用電壓緩衝器所造成的VSG電壓差... 33

圖 2. 37 Current efficient-transient boost LDO線性穩壓器[10] ... 34

圖 2. 38 Current efficient-transient boost LDO線性穩壓器的頻率響應[10] ... 34

圖 2. 39 Current efficient-transient boost LDO線性穩壓器的暫態響應[10] ... 35

圖 2. 40 Low-Dropout Regulator With Buffer Impedance Attenuation [12]... 36

圖 2. 41 LDO With Buffer Impedance Attenuation的迴路增益 [12] ... 37

圖 2. 42 LDO With Buffer Impedance Attenuation的負載暫態響應 [12] ... 38

圖 3. 1 無外部電容的低壓差線性穩壓器架構 [13]... 39 圖 3. 2 含有一階高通特性的回授網路... 40 圖 3. 3 無外部電容的低壓差線性穩壓器的小訊號模型... 41 圖 3. 4 在IOUT=0,COUT≠0 時的迴路增益... 43 圖 3. 5 在IOUT≠0,COUT≠0 時的迴路增益 ... 44 圖 3. 6 在IOUT≠0,COUT=0 時的迴路增益 ... 44 圖 3. 7 在COUT≠0 時的迴路增益模擬... 45 圖 3. 8 在COUT=0 時的迴路增益模擬... 46 圖 3. 9 無外部電容的低壓差線性穩壓器的實際電路方塊圖... 47 圖 3. 10 無外部電容的低壓差線性穩壓器實際電路... 47 圖 3. 11 Gm-boosting電路說明... 48 圖 3. 12 帶差參考電路 [14]... 49 圖 3. 13 起動電路的模擬... 51 圖 3. 14 帶差參考電路的電流源... 52 圖 3. 15 IOUT與隨電源VDD變動的模擬 ... 52 圖 3. 16 操作在次臨界區的兩級放大器... 53 圖3. 17 兩級放大器的頻率響應... 54 圖 3. 18 兩級放大器的共模輸入範圍的模擬... 55 圖 3. 19 偏壓電路... 55 圖 3. 20 帶差參考電路的溫度係數模擬... 57 圖 3.21 電源起動的模擬... 57 圖 3. 22 電源拒斥比的模擬... 58 圖 3. 23 負載穩壓的模擬示意圖... 60 圖 3. 24 負載穩壓的模擬結果(有輸出電容及ESR電阻)... 60 圖 3. 25 負載穩壓的模擬結果(無輸出電容)... 61 圖 3. 26 線上穩壓的模擬示意圖... 62 圖 3. 27 線上穩壓的模擬結果(有輸出電容及ESR電阻)... 62 圖 3. 28 線上穩壓的模擬結果(無輸出電容)... 63 圖 3. 29 有輸出電容及ESR電阻的負載暫態響應的模擬示意圖 ... 64

圖 3. 30 含有 10μF的輸出電容及 10Ω的ESR電阻時負載暫態響應的模擬... 64 圖 3. 31 在有輸出電容時,負載從 0mA到 100mA的暫態響應模擬... 65 圖 3. 32 在有輸出電容時,負載從 100mA到 0mA的暫態響應模擬... 66 圖 3. 33 無輸出電容的負載暫態響應的模擬示意圖... 66 圖 3. 34 在無輸出電容時的負載暫態響應模擬... 67 圖 3. 35 在無輸出電容時,負載從 10mA到 100mA的暫態響應模擬... 68 圖 3. 36 在無輸出電容時,負載從 100mA到 10mA的暫態響應模擬... 68 圖 3. 37 線上暫態響應的模擬示意圖... 69 圖 3. 38 VIN由 1.5V變動到 4.5V時的線上暫態響應模擬... 69 圖 3.39VIN由 4.5V變動到 1.5V時的線上暫態響應模擬... 70 圖3.40 電源拒斥比的模擬示意圖... 71 圖 3. 41 含有輸出電容及ESR電阻時的電源拒斥比模擬 ... 72 圖 3. 42 無輸出電容時的電源拒斥比模擬... 72 圖 3.43 靜態電流的模擬示意圖... 73 圖 3. 44 溫度係數的模擬示意圖... 74 圖 3. 45 溫度係數的模擬... 75 圖 4. 1 整體晶片的佈局... 76 圖4.2 低壓差線性穩壓器的佈局... 77 圖4.3 低壓差線性穩壓器的電晶體的詳細佈局... 78 圖4.4 帶差參考電路的Trimming電阻 ... 79 圖 4.5 帶差參考電路的佈局... 80 圖4.6 帶差參考電路的兩級放大器的佈局... 81 圖4.7 帶差參考電路的電流源的Trimming電阻 ... 82 圖 4.8 帶差參考電路的電流源的佈局... 83 圖 4.9 帶差參考電路的緩衝器的佈局... 84 圖 4.10 基本負載暫態產生器的示意圖………..85 圖 4. 11 基本負載暫態產生器的測試平台...85 圖 4. 12 閉迴路的負載暫態產生器的示意圖...86

圖 4. 13 ILOAD=0mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...87

圖 4. 14 ILOAD=48mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...88

圖 4. 15 ILOAD=100mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...88

圖 4. 16 VIN=1.5V 時, ILOAD從 50mA 到 100mA 的 VOUT變動...89

圖 4. 17 VIN=1.5V 時, ILOAD從 75mA 到 105mA 的 VOUT變動...89

圖 4. 18 ILOAD=0mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...90

圖 4. 19 ILOAD=48mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...90

圖 4. 20 ILOAD=100mA,VIN=1.5V 時的 VOUT及 Bandgap 輸出電壓...91

表示

表 2.1 傳輸電晶體的比較... 13

表 2. 2 NMOS與PMOS傳輸電晶體LDO線性穩壓器的比較... 14

表 2. 3 穩定度及其它規格之間的衝突 [4]... 35

表 2. 4 LDO With Buffer Impedance Attenuation的第一及第二主極點... 37

表 3. 1 迴路增益的模擬數據... 46 表 3. 2 所設計的低壓差線性穩壓器元件尺寸... 49 表 3. 3 兩級放大器頻率響應的數據... 54 表 3. 4 帶差參考電路的元件尺寸... 56 表 3. 5 偏壓電路的元件尺寸... 56 表 3. 6 靜態電流的模擬... 58 表 3. 7 帶差參考電路的效能模擬表... 59 表 3. 8 含有 10μF的輸出電容及 10Ω的ESR電阻時的負載暫態響應數據表... 65 表 3. 9 無輸出電容時的負載暫態響應數據表... 67 表 3. 10 線上暫態響應的數據表... 70 表 3. 11 電源拒斥比的模擬數據表... 73 表 3. 12 靜態電流的模擬數據表... 73 表 3. 13 低壓差線性穩壓器的效能... 75

第一章

概論

1.1 研究背景

在可攜式電子產品中,待機電源的節省是很重要的,所以必須利用有效的電源管理。由 於電路中不同模組會需要不同的電壓及電流規格,因此必須使用到許多電源管理 IC。低 壓差(LDO)線性穩壓器是最基本的 DC-DC 電源管理 IC,如圖 1.1 的基本可攜式電子產品, 一共有用到 3 個 LDO 線性穩壓器,及一個 Buck Converter。由於低電壓及高電流效率的需 求,LDO 線性穩壓器已被廣泛用在可攜式的電子產品上,如手機,PDA,筆記型電腦等,以延長 電池壽命。一般的可攜式電子產品大部份時間是處在待機狀態,而低的靜態電流,正是 LDO 特點之一。一般的直流轉直流的穩壓器(DC-DC Regulator)大概分成三種:交換式穩壓器(Switching Regulator),電荷幫浦穩壓器(Charge-Pump Regulator)及 LDO 線性穩壓器。在三種當中,LDO 線性穩壓器具有很快的 Load transient response,較少的 Output Ripple, 較小的靜態電流及較 小的 PCB Layout 面積等特點,因此適合於應用在射頻電路及類比電路。

Li-Ion Battery 2.97V to 4.2V Buck Converter LDO1 LDO2 LDO3 Low Voltaeg Analog Circuit High Voltaeg Analog Circuit 2.8V 1.8V 1.2V Microprocessor and Digital Core Power Management IC 圖 1.1 基本可攜式電子產品的 DC-DC 電源管理 IC 架構

傳統的 LDO 線性穩壓器需要一個大約幾 microfarad 到十幾 microfarad 等級的輸出電容, 做為頻率補償,因此會比較佔 PCB 的面積及成本。在 System on Chip(SoC)的環境中,也不允 許使用外部元件,因此這篇論文題出一個不需輸出電容做頻率補償的 LDO 線性穩壓器架 構,而且在穩定度及各項效能上都能兼顧。

1.2 研究動機及目的

在設計低壓差(LDO)線性穩壓器時,穩定度及其它效能之間一般都是互相權衡,像是暫 態響應,電流效率,線上穩壓,負載穩壓, PSRR 等,為了改善 LDO 線性穩壓器的效能,已經有 許多文獻被提出,這些架構都需要使用到外部電容,來做穩定度的補償,然而外部電容不容 易實現在 SOC 環境下,所以需要開發無外部電容的 LDO 線性穩壓器,無外部電容的 LDO 線 性穩壓器由於缺乏外部電容,所以在負載暫態響應時,會有較大的電壓下降。本篇論文的 LDO 線性穩壓器架構在三級的放大器設計,由於在輕載及重載下,Loop Gain 都很高,在加上 第二級的 push-pull stage,因此具有 fast load transient response 及 high power-supply rejection ratio (PSRR)的特色。本篇論文所設計的 LDO 線性穩壓器是一個最大負載電流 100mA,輸入電壓在 1.5V~4.5V,輸出電壓在 1.3V, ,Dropout Voltage 在 200mV,可以無外部電容,使用 TSMC 0.35μm 2P4M CMOS 製程,包含參考電壓源僅消耗 46μA 的靜態電流。

1.3 內容大綱

本論文共分五個章節說明,各章節的標題與內容簡述如下: 第一章 概論 :旨在說明本論文之研究背景、動機及目的。 第二章 低壓差(LDO)線性穩壓器的介紹 :探討與分析基本低壓差線性穩壓器及專有名詞 的定義以及 LDO 線性穩壓器的設計考量,以及新的低壓差線性穩壓器的架構。 第三章 無外部電容的低壓差(LDO)線性穩壓器 : 對整體電路架構分析及實際電路設 計、模擬結果。 第四章 實體佈局,量測方法及量測結果: 對電路實體佈局,量測方法及結果作說明。 第五章 結論及未來方向: 對整體的研究做總結並討論未來可能的研究方向。第二章

低壓差(LDO)線性穩壓器介紹

2.1 基本的低壓差(LDO)線性穩壓器

圖 2.1 說明了基本的 LDO 線性穩壓器架構,包含有一個精準的參考電壓(Reference Voltage)以及它的起動電路(Start-Up Circuit),一個傳輸電晶體(Pass Transistor),一個誤差放大 器(Error Amplifier),一個回授網路(Feedback Network)和一些限制溫度,電流及防電池逆向的 保護電路(Protection Circuit) 。 Start-up Circuit Reference Voltage Error Amp. Pass Transistor Current Sense Element Feedback Network Protection Circuits Vout Vin Vfb Vref 圖 2.1 基本的 LDO 線性穩壓器架構[1]

整個 LDO 線性穩壓器可看成一個串聯輸入,並聯輸出的負回授系統,輸出電壓經由負 回授系統的調節下,可以保持在一個穩定的電位。理想上,參考電壓(Reference Voltage)是一 個不受溫度及輸入電源影响的電壓源(Vref),提供給 Error Amplifier 當作參考。當負載電流 突然變大時,輸出電壓會瞬間下降,經由回授網路產生回授電壓(Vfb),再由誤差放大器(Error Amplifier)根據參考電壓(Reference Voltage)來比較,進而控制傳輸電晶體(Pass Transistor)供 給更多的電流給負載, 而當負載電流突然變小時,則相反。 LDO 線性穩壓器的輸出電壓可由以下公式決定: 1 2 1 F F OUT ref F

R

R

V

V

R

+

=

×

(2.1)Vref是參考電壓(Reference Voltage),RF1及 RF2是回授網路的分壓電阻。

為了確保 LDO 線性穩壓器能在安全的條件下工作,因此需要一些保護電路,而這些額外的 保護電路在正常工作下,並不會影响 LDO 線性穩壓器的輸出電壓穩定。

2.2 LDO 線性穩壓器的規格及專有名詞定義

在討論 LDO 線性穩壓器的架構之前,必須對 LDO 線性穩壓器的規格及專有名詞定 義做說明,包含有:低壓降(Dropout Voltage),靜態電流或接地電流(Quiescent Current or Ground Current),功率效率(Power efficiency),線上穩壓(Line Regulation),負載穩壓(Load Regulator),電 源拒斥比(Power Supply Rejection Ratio),輸出雜訊(Output Noise), 精確度(Accuracy),暫態響 應(Transient Response)[1][2][3]。分別敘述如下:

2.2.1 壓降電壓(Dropout Voltage)

壓降電壓(Dropout Voltage)定義成:當 LDO 線性穩壓器輸入電壓降到某個程度時,其輸 出電壓將不再穩壓在預計的輸出電壓,而在臨介點(輸出偏移 2%)時的輸入電壓與輸出電壓 的差值,如圖 2.2 所示,當輸入電壓 Vin 大於 Vy 時,LDO 線性穩壓器的傳輸電晶體(Pass Transistor)是工作在飽和區,因此,整個 LDO 線性穩壓器的 Loop Gain 維持在很高,使得 LDO 線性穩壓器處於穩壓區(Regulation Region)。當輸入電壓 Vin 小於 Vy 時, LDO 線性穩壓器 的傳輸電晶體(Pass Transistor)是工作在線性區, 整個 LDO 的 Loop Gain 變的很低,使得 LDO 線性穩壓器的輸出電壓不在穩定在固定值,此時 LDO 線性穩壓器進入 Dropout Region,而此 時傳輸電晶體(Pass Transistor)可當做一個電阻, 壓降電壓(Dropout Voltage)被定義成:

drop out load on

V

−=

I

×

R

(2.2)Ron 是傳輸電晶體(Pass Transistor)的導通電阻, ILoad 是負載電流

由於 LDO 線性穩壓器的功率損耗是正比於電壓差(Dropout Voltage),所以愈小的電壓 差(Dropout Voltage)將有較小的功率損耗在傳輸電晶體(Pass Transistor)上,功率效率比較高。

Cut-Off Region

Dropout

Region Regulation Region

Vout

Vin

Vx Vy

圖 2.2 Vin 與 Vout 的關係圖

2.2.2 靜態電流或接地電流(Quiescent Current or Ground

Current)

IN OUT GND Vi Ii Iq Io Vo ESR Cout + _ 圖 2.3 LDO 線性穩壓器的靜態電流靜態電流或接地電流(Quiescent Current or Ground Current)定義成 LDO 線性穩壓器的輸 入電流減去輸出電流 Iq=Ii-Io,靜態電流包含有系統的偏壓電流(如誤差放大器,回授電阻,參 考電壓及保護電路)及驅動傳輸電晶體(Pass Transistor)所消耗的電流,靜態電流並不會提供 輸出功率,所以低的靜態電流是必要的對於增加電池效率而言,然而在效能與靜態電流之 間有許多 Trade Off,如 LDO 線性穩壓器的暫態响應及穩定度。

靜態電流在 Bipolar 與 MOS 電晶體是有所不同,在 Bipolar 電晶體中,負載電流是由基極 電流所驅動,所以靜態電流是會隨負載增加而增加,但在 MOS 電晶體中,由於 Ig~0,所以

2.2.3 功率效率(Power efficiency)

LDO 線性穩壓器的功率效率(Power efficiency)定義成輸出功率除以輸入功率,主要限 制在靜態電流(Quiescent Current)及輸出與輸入的電壓比值,公式如下:

(

)

out out out q inI

V

Efficiency

I

I

V

×

=

+

×

(2.3) 在輕載時,由於輸出與輸入的電壓差接近零,所以電流的效率決定了功率效率(Power efficiency), 公式如下: Load q LoadI

Efficiency

I

I

≈

+

(2.4)在輕載時,為了改善功率效率(Power efficiency),必須降低靜態電流(Quiescent Current),在 重載時,因為 ILoad很大,所以電流的效率接近 1, 功率效率(Power efficiency)可改寫成

out in

V

Efficiency

V

≈

(2.5) 由 此 可 知 , 為 了 增 加 功 率 效 率 , 降 低 靜 態 電 流 (Quiescent Current) 及 減 少 壓 降 電 壓 (Dropout Voltage)是必要的。2.2.4 線上穩壓(Line Regulation)

線上穩壓(Line Regulation)是用來量測當輸入電壓變動時,輸出電壓能夠保持固定的穩 定度,定義如下: out inV

Line Regulation=

V

Δ

Δ

(2.6)Voltage Reference Vfb EA R1 R2 RL Vout Mp Rpass Vin 圖 2.4 PMOS 的 LDO 線性穩壓器

根據圖 2.4,當Vin變動時,Vout也會跟著變動,而 Error Amplifir 會根據回授電壓去 驅動傳輸電晶體(Pass Transistor)來抑制輸出電壓的變動。線上穩壓(Line Regulation)的分析 如下: L out in fb EA mp L L pass

R

V

V

V

A g

R

R

R

Δ

=

× Δ

− Δ

×

×

+

(2.7) 2 1 2 fb outR

V

V

R

R

Δ

=

× Δ

+

(2.8) 最後可得到新的線上穩壓(Line Regulation)表示:(

)

1 2 2 1 OUT in EA mp L pass V R R V R A g R R Δ = + × Δ × + (2.9) 其中 Rpass 是傳輸電晶體(Pass Transistor)的等效電阻,RL 是負載電阻,AEA 是 Error Amplifier 的 Gain, gmp是傳輸電晶體(Pass Transistor)的轉導。由(2.9)式可知,增加 Error Amplifier 的 Gain 或傳輸電晶體(Pass Transistor)的轉導可以改 善線上穩壓(Line Regulation)。線上穩壓(Line Regulation)是一個穩態(Steady-State)的規格,所 以只考慮輸入電壓的直流變動情形。事實上,參考電壓及 Error Amplifier 的 Offset Voltage 也會受到輸入電壓的影響,必須列入考量。

2.2.5 負載穩壓(Load Regulation)

負載穩壓(Load Regulation)是用來量測當負載電流變動時,輸出電壓能夠保持固定的穩 定度,定義如下: out Load ΔV Load Regulation= ΔI (2.10) 根據圖 2.4,當負載電流變動時,LDO 線性穩壓器的輸出電壓及回授電壓也會跟著變動,經由 Error Amplifier 偵測到回授電壓的變動進而驅動傳輸電晶體(Pass Transistor)去抑制輸出電 壓的變動。負載穩壓(Load Regulation)的分析如下:(

Δ

I

Load-

Δ

V

fb×

A

EA×

g

mp)

×

R

pass= Δ

V

out (2.11)2 1 2 fb out

R

V

V

R

R

Δ

=

× Δ

+

(2.12) 2 2 1 2 1 21

1

pass out Load EA mp pass EA mpR

V

R

R

I

A g

R

A g

R

R

R

R

Δ

=

≅

Δ

+

×

×

×

+

+

(2.13)由上面分析可知,藉由增加 Error Amplifier 的 Gain 或傳輸電晶體(Pass Transistor)的轉導可以 改善負載穩壓(Load Regulation)。

2.2.6 電源拒斥比(Power Supply Rejection Ratio)

電源拒斥比(Power Supply Rejection Ratio)是量測當輸入電壓變化,輸出電壓能夠抑制 變化的能力, 定義如下 : , , o ripple in ripple

V

PSRR

V

Δ

=

Δ

at all frequencies (2.14),跟線上穩壓(Line Regulation)不同的是電源拒斥比(Power Supply Rejection Ratio)與 LDO 線性 穩壓器閉迴路的頻率相關,所以是屬於高頻規格。例如:如果 LDO 線性穩壓器是應用於直 流/直流切換式轉換器(DC/DC switching Converter)之後穩壓時(Post Regulation),則在切換頻 率 100kHz 到 1MHz 的頻寬就比較重要,如圖 2.5, 100kHz 到 1MHz 的頻寬,PSRR 最差。

圖 2.5 LDO 線性穩壓器的 PSRR [2]

PSRR 與迴路增益頻寬(loop-gain bandwidth)及等效串聯電阻(ESR)非常相關。

,比較大的迴路增益頻寬(loop-gain bandwidth),使用低阻值的等效串聯電阻(ESR),一個較 大的輸出電容,及額外的旁路電容(Bypass Capacitor),都可以改善 LDO 線性穩壓器的 PSRR。 此外,參考電壓也會受到輸入電源的漣波影響,所以在設計參考電壓時必須考慮 PSRR 問題。

2.2.7 輸出雜訊(Output Noise)

輸出雜訊(Output Noise)是在指定的頻率內(eg: 10Hz to 100kHz)的輸出雜訊的 RMS 電壓, 所以也是屬於高頻規格。量測的條件必須在固定負載及無漣波的輸入電壓下,以確保雜訊 來源是來自 LDO 線性穩壓器本身產生。典型的輸出雜訊電壓在 100 到 500μV,大部份的 輸出雜訊來自於內部參考電壓及誤差放大器。LDO 線性穩壓器的輸出雜訊分析如下圖 [10]: VREF Feedback NetwotkError Amp Power PMOS +

_

Von_vref Vin_ea Vin_pt

Von_ldo

∑

2 2 2 2 2 2 _ _ _ _ _ 2 _ 2 2

/

on vref in ea in pt EA on vref in ea on ldoV

V

V

A

V

V

V

f

f

+

+

+

=

≈

(2.15)其中Von_vref是參考電壓的輸出雜訊, Vin_ea 是誤差放大器的輸入雜訊, Vin_pt是傳輸電 晶體(Pass Transistor)的輸入雜訊, Von_ldo 是 LDO 線性穩壓器的輸出雜訊。

電晶體使用較大的 Size,及較大的偏壓電流可降低 Flicker Noise, 誤差放大器的差動對 使用 PMOS 輸入電晶體比使用 NMOS 輸入電晶體有比較低的 Flicker Noise。

2.2.8 精確度(Accuracy)

LDO 線性穩壓器的精確度(Accuracy)定義成所有可能造成輸出電壓變動的因素。這些 因素包括有限的線上穩壓(Line Regulation)、有限的負載穩壓(Load Regulation)、參考電壓的 漂移、誤差放大器的漂移、回授電阻的誤差、及電阻的溫度係數變化。 精確度(Accuracy)的計算如下: 2 2 2 2 , , , | | | | 100% LR LDR o ref o EA o res TC O V V V V V V Accuarcy V Δ + Δ + Δ + Δ + Δ + Δ ≈ × (2.16) 2 1 , 2 o ref ref

R

R

V

V

R

+

Δ

=

× Δ

(2.17) 2 1 , 2 o EA EAR

R

V

V

R

+

Δ

=

× Δ

(2.18) 2 1 , 2 2 o res refR

R

V

V

R

R

Δ + Δ

Δ

=

×

+ Δ

(2.19)其中 ΔVLR 是線上穩壓(Line Regulation)的漂移, ΔVLDR 是負載穩壓(Load Regulation)的漂 移,ΔVo,ref是參考電壓的漂移, ΔVo,EA是誤差放大器的漂移,

ΔVo,res 是回授電阻的誤差,ΔVTC是溫度係數變化。一般正常的精確度(Accuracy)誤差在

1~3%內。

另一種精確度的定義是將造成誤差的因素分成兩類:系統誤差(System Error) ΔVo(SYS)及隨機誤差(Random Error) ΔVo(RAN)。表示如下 [4]:

(

2)

( ) ( )100%

o SYS o RAN oV

V

Accuracy

V

Δ

+

Δ

=

∑

∑

×

(2.20) 系 統 誤 差 (System Error)ΔVo(SYS)是 由 於 設 計 造 成 的 輸 出 電 壓 變 動 包 含 線 上 穩 壓 (LineRegulation),負載穩壓(Load Regulation),溫度係數變化,有限增益誤差及參考電壓誤差。 隨機誤差(Random Error) ΔVo(RAN) 是由於製程的漂移及實體佈局的誤差。

2.2.9 暫態響應(Transient Response)

暫 態 響 應 (Transient Response) 是 當 負 載 電 流 突 然 由 輕 載 變 成 重 載 (Load Current StepChange)時或是由重載變成輕載(Load Current StepChange)時, LDO 線性穩壓器的輸出電 壓可以允許的最大變化量。暫態響應(Transient Response)與輸出電容(CO),等效串聯電阻 (ESR),及旁路電容(Bypass Capacitor)有關。 最大的輸出暫態電壓變動定義如下[2]: 1 .max ,max o tr ESR o b

I

V

t

V

C

C

Δ

=

× Δ + Δ

+

(2.21) 如圖 2.7,其中Δt1是與 LDO 線性穩壓器的閉回路頻寬有關,ΔVESR是瞬間負載電流通過 輸出電容(CO)及等效串聯電阻(ESR)所造成的壓降。為了改善 LDO 線性穩壓器的暫態響應 (Transient Response),可以增加 LDO 線性穩壓器的閉回路頻寬,增加輸出電容(CO),及減少 等效串聯電阻(ESR)。 圖 2.7 LDO 線性穩壓器的暫態響應[2]2.3 LDO 線性穩壓器的設計考量

LDO 線性穩壓器常用在可攜式電子產品,主要電力來源是各式電池。電池的電壓會隨 時間慢慢降低。為了延長電池壽命, 低功耗的 LDO 線性穩壓器必須被採用。根據半導體 發展的準則, 由於製程的進步,低電壓源(VIN 小於 1V)的電路將在未來幾年被使用,在如此 要求低的電源電壓,低的靜態電流以及不穩定的電池電壓的環境下,要設計一個精準且穩 定輸出的 LDO 線性穩壓器,是一大挑戰。在這一節將介紹傳統 LDO 線性穩壓器設計有 關的分析及設計考量,包括:傳輸電晶體(Pass Transistor)的討論,穩定度分析,暫態響應的分 析,然後討論參考電壓及誤差放大器的設計考量,最後將討論幾種不同改良傳統 LDO 線性穩壓器的新架構。

2.3.1 傳輸電晶體(Pass Transistor) 的討論

LDO 線性穩壓器的傳輸電晶體(Pass Transistor)一般分為兩大類(如圖 2.8)BJT 電晶體及 MOS 電晶體。而 BJT 電晶體又分為達靈頓(Darlington),NPN 及 PNP 三種,MOS 電晶體分 成 NMOS 及 PMOS 兩種。它們的比較如下表: 表 2.1 傳輸電晶體的比較 BJT 電晶體 MOS 電晶體 特性 達靈頓 (Darlington) 圖 2.8(a) NPN 圖 2.8 (b) PNP 圖 2.8 (c) NMOS 圖 2.8 (d) PMOS 圖 2.8 (e) 最大輸出電流,Iomax 高 高 高 適中 適中 靜態電流 (Quiescent Current) 適中 適中 大 低 低 壓降電壓 (Dropout Voltage)

VCE(Sat)+2VBE VCE(Sat)+VBEVCE(Sat) VDS(Sat)+VGS VSD(sat)

導通速度 (Turn ON Speed) 快 快 慢 適中 適中 (a)Darlington (b)NPN (c)PNP (d)NMOS (e)PMOS Charge Pump C B E E C B C B E S G D D S G 圖 2. 8 傳輸電晶體的種類

BJT 電晶體本身因為是電流驅動裝置,它的基極電流與負載電流成正比,因此在重載時 需要消耗較多的靜態電流(IB=IC/β),因此將浪費許多功率。相對於 MOS 電晶體而言,閘極 端的阻抗很大,流進閘級的電流很小,因此以電壓驅動的 MOS 裝置消耗最小的靜態電流。 傳輸電晶體(Pass Transistor)的大小主要由最大輸出電流及壓降電壓(Dropout Voltage) 來決定。

對於 NMOS 電晶體來說,它的壓降電壓(Dropout Voltage)為

Vdrop = VGS+VDS(SAT),為了減少壓降電壓(Dropout Voltage),它必須外加 Charge Pump 電

路,將傳輸電晶體的 Gate 端電壓拉高,此時的 Vdrop = VDS(SAT)減少了大約一個 VGS的電壓。

而使用 NMOS 電晶體的 LDO 線性穩壓器有一個優點就是它的低輸出阻抗,因此,比較沒有 穩定度的問題。

對於 PMOS 電晶體來說,它的壓降電壓(Dropout Voltage)為:

drop out load on

V

−=

I

×

R

(2.22)

比起 NMOS 電晶體,它有比較低的壓降電壓(Dropout Voltage),壓降電壓(Dropout Voltage)與傳輸電晶體(Pass Transistor)的大小及閘極電壓相關。在輕載時,只有幾 mVoltage, 在重載時,大約幾百 mVoltage。

採用NMOS 傳輸電晶體與 PMOS 傳輸電晶體的 LDO 線性穩壓器優缺點比較如下表:

表 2. 2 NMOS 與 PMOS 傳輸電晶體 LDO 線性穩壓器的比較

PMOS 傳輸電晶體的 LDO 線性穩壓器 (圖 2.9) (Common Source Type)

NMOS 傳輸電晶體的 LDO 線性穩壓器 (圖 2.10) (Common Drain Type) 優點 1.低壓降電壓(Dropout Voltage) 2.低輸入電源電壓 1. 比較沒有穩定度的問題 (低輸出阻抗) 2.不需要大的外部電容 缺點 遭遇到穩定度問題 (整個閉回路至少有 2 個低頻極點) 需要外加 Charge Pump 電路

一般而言,Power PMOS 是操作在飽和區,如果所設計的 LDO 線性穩壓器的 Loop Gain 非常高,則 Power PMOS 也可以操作在線性區,如此 Power PMOS 可以設計比較小的尺寸, 節省面積。Power MOS 的大小是設計在最差的情況,也就是最大VSD(SAT),最大的負載電流, 及最大溫度下。 計算公式為: (max) ( )

2

( / )

oSD sat Drop out

p ox

I

V

V

C

W L

μ

−=

≈

max 22

PASS ox DSsatI

W

L

μ

C V

⎛

⎞

⇒

⎜

⎟

=

⎝

⎠

(2.23) 為了有最小的閘極寄生電容(Parasitic Capacitor),一般採用最小的電晶體長度,然後逐漸 增加電晶體寬度一直到符合壓降電壓(Dropout Voltage)的規格。而保守的電晶體大小是理論值的 1.1 倍到 1.2 倍。 VIN VOUT Cout Error Amplifier Vref R1 R2 Power PMOS VIN VOUT Cout Error Amplifier Vref R1 R2 Power NMOS Charge Pump

圖 2.9 PMOS 傳輸電晶體 LDO 圖 2.10 NMOS 傳輸電晶體 LDO

2.3.2 傳統 LDO 線性穩壓器的穩定度分析

gmp gma Cpar Roa A Vin Vref R2 R1 Vout Resr Co Cb RL IL Vfb Vin 圖 2. 11 傳統 PMOS LDO 線性穩壓器的架構 圖 2.11 為 傳 統 PMOS LDO 線 性 穩 壓 器 的 架 構 , 包 含 有 一 個 誤 差 放 大 器 (ErrorAmplifier),一個傳輸電晶體(Pass Transistor),回授電阻(Feedback Resistor),一個輸出 電容 Co 包含有串聯等效電阻(ESR),及旁路電容 Cb。旁路電容 Cb 的串聯等效電阻 ESR 很小,一般都忽略不計。整個傳輸電晶體(Pass Transistor)可以等效成一個轉導 gmp 及輸出 電阻 Ropass。回授電阻(Feedback Resistor)R2 是依據想設計的輸出電壓來決定,例如:如果 R2 是等於零,則輸出電壓就等於參考電壓。而 R1 是依據想設計流過 R1 及 R2 的靜態電流的大小來決定(R1=Vref/IR1)。為了有比較小的靜態電流,R1 阻值會設計比較大 。 一般 LDO 線性穩壓器為了達到系統的穩定,都會限制輸出電容的大小及串聯等效電 阻(ESR)的範圍。為了分析 LDO 線性穩壓器的頻率響應,一般會從 A 點(高阻抗節點)打斷 系統的閉迴路來分析,而整個系統的小信號模型如圖 2.12 所示。 gmeaVin Roea Cpar gmpVoea Ropass Vfb R2 R1 Resr Co RL Cb

Vin Voea Vout

圖 2. 12 傳統 PMOS LDO 線性穩壓器的小信號模型 [3]

傳統 PMOS LDO 線性穩壓器的 Loop Gain 計算如下:

1

1 2

(

||

)

fb

LoopGain mea oea par mp

in

V

R

A

g

R

sC

g

Z

V

R

R

=

=

×

×

× ×

+

(2.24) 其中 gmea 和 gmp 分別是誤差放大器(ErrorAmplifier)及傳輸電晶體(Pass Transistor)的轉導 (transconductance),Cpar 及 Roea 是誤差放大器(ErrorAmplifier)在輸出端的等效電容及電阻, R1 及 R2 是回授電阻,而 Z 是從 PMOS LDO 線性穩壓器的輸出端看到的等效阻抗,表示 如下: 1 2|| (

) || (

1/

) ||

|| (1/

)

opass esr o L bZ

=

R

R

+

R

R

+

sC

R

sC

(2.25) 其中 Ropass 是傳輸電晶體(Pass Transistor)等效輸出電阻,Cb 是高頻旁路電容。通常,Resr << Ropass << R 1+R2 ,所以忽略 R1+R2 後,將 (2.25)式代回(2.24)式,可得 到 :

(

||

) (

1)

(1

(

||

))(1

)(1

)

mea mp oea esr opass L o esr

LoopGain

o esr opass L par oea esr b

b g

g

R

R

R

R

sC R

A

sC R

R

R

sC

R

sR C

×

×

×

×

+

×

+

≈

+

+

+

+

(2.26) 其中 1 1 2R

b

R

R

=

+

,由(2.26)式可看出整個的轉移函數(Transfer Function)有三個極點及一 個零點。由於 Co 是外部電容,一般大概有幾個μF,所以主極點在 LDO 線性穩壓器的輸出 端表示為: 31

(

||

)

dB esr opass L oP

R

R

R

C

−=

+

×

(2.27)傳輸電晶體(Pass Transistor)的寄生電容 Cpar 一般大概有幾十 pF,與誤差放大器(Error Amplifier)的輸出電阻形成第二主極點,表示為: 2

1

oea parP

R

C

=

×

(2.28) 第三極點是由高頻旁路電容 Cb及串聯等效電阻(ESR)所組成,表示如下: 31

esr bP

R C

=

(2.29) 而唯一的零點由串聯等效電阻(ESR)及外部電容 Co所組成,表示如下:1

esr esr oZ

R C

=

(2.30) PMOS LDO 線性穩壓器的直流增益(dc gain)可以將 s=0 代入(2.23)式,得到:0 mea mp oea

(

esr opass||

L)

LG

= ×

b g

×

g

×

R

×

R

+

R

R

(2.31) 而增益頻寬乘積(GBW)為: 0 3 mea mp oea dB ob g

g

R

GBW

LG

P

C

−×

×

×

=

×

=

(2.29) 一般而言,三個極點的順序分別為 P-3dB < P2 < P3 。一個穩定的系統,必須至少有 45 度的相位邊限(Phase Margin),為了達到系統穩定, 通常只有一個極點 P-3dB位於單位增益 頻率之內,而P2可藉由 Zesr 來消除。P3則設計在大於或等於單位增益頻率。一個穩定的 傳統 PMOS LDO 線性穩壓器的頻率響應,如圖 2.13 所示。 Frequency [Hz] Frequency [Hz] 1k 10k 100k -45 0 40 0 Gain[dB] Phase [degree ] P1 P3 P2 Z1 圖 2. 13 傳統 PMOS LDO 線性穩壓器的頻率響應傳統 PMOS LDO 線性穩壓器的穩定度通常會與其它的設計項目之間有所衝突,例如: 最大的負載電流(maximum load current),靜態電流(quiescent current),輸出電容的大小,系 統的迴路直流增益(dc gain),及串聯等效電阻的容許範圍(tolerance range of the ESR)。

由(2.29)式,可看出當輸出負載電流IOMAX增加時,單位增益頻寬也將增加,頻寬的增 加將造成高頻的極點(P3)進入單位增益頻寬之內,而系統的相位邊限(Phase Margin)勢必減 少,造成系統不穩定。因此,最大負載電流IOMAX與穩定度之間是 trade off。所以最差的情 況是在最大負載電流IOMAX時,而頻率補償也是設計在這個情況,如圖 2.14。

另一方面,減少靜態電流(quiescent current)意味著將使得誤差放大器(Error Amplifier) 的輸出電阻 Roea 變大,由(2.28)式可知,將造成 P2 往低頻移動,系統的相位邊限(Phase Margin) 減少。因此,傳統 PMOS LDO 線性穩壓器的靜態電流(quiescent current)不能太小。由(2.27) 式可知主極點與輸出電容 Co 相關,為了有更低頻的主極點, 勢必增加更大的輸出電容 Co ,佔了很大的面積及成本。

增加直流增益(dc gain)可以改善輸出電壓的精確度,但同時也增大了單位增益頻寬造 成高頻的極點(P3)進入單位增益頻寬之內,系統的相位邊限(Phase Margin)減少,造成系統不 穩定。

傳統 PMOS LDO 線性穩壓器的頻率補償必須藉由P2與Zesr的抵消來增加相位邊限。 而Zesr零點是靠等效串聯電阻 ESR 來產生,為了精確的抵消P2,等效串聯電阻 ESR 因此被 受限於某個範圍內,太大的 ESR 將造成P3進入單位增益頻寬之內, 系統將變成兩個低頻 極點而造成不穩定,如圖 2.15 所示。太小的 ESR,零點會位於高頻,使得無法抵消P2,系 統同樣將變成兩個低頻極點而造成不穩定,如圖 2.16 所示。因此,傳統 PMOS LDO 線性 穩壓器必須小心選擇輸出電容的 ESR。一般廠商都會提供一個 ESR 有效範圍當作頻率補 償的參考,如圖 2.17 所示。 LoopGain [dB] Frequency 0dB P1' P1 最小負載電流 最大負載電流 P3 P3 P2 Ze 極零點對消 圖 2. 14 太大的負載電流將造成系統不穩定

P-3dB P2 Zesr P3 Gain [dB] Frequency 0dB 圖 2. 15 太大的 ESR 造成系統不穩定 Gain [dB] Frequency P-3dB P2 Zesr P3 0dB 圖 2. 16 太小的 ESR 造成系統不穩定 圖 2. 17 ESR 的穩定範圍 [2]

一般量測 AC Open-Loop Gain 的方法是從測試點 A 打斷,然後加入一個 AC 信號,很大 的電感LOPEN (1012H)以及很大的電容 COPEN (1012F),如圖 2.18 所示。電感 LOPEN形成一個 直流的回授路徑,阻斷了交流成份。直流回授路徑經由 LOPEN 設定了正確的工作點使得 LDO 閉回路能正常工作。而 AC 信號在不影響直流工作點的情形下能經由電容 COPEN耦 合(coupling)到放大器。如此的做法可以量測到非常低頻的開回路增益。 gma Cpar Roa Vin Vref R2 R1 Vout Resr Co Cb IL Vfb Copen Lopen VAC Test Ponit A

圖 2. 18 AC Open- Loop Gain 的 Simulation Circuit [5]

2.3.3 暫態響應分析

暫態響應是 LDO 線性穩壓器的重要規格。暫態響應是指當負載電流有瞬間全載的步 階變動(full load-current step change)時,輸出電壓的最大允許的變動範圍。

對於數位電路而言,這個規格可以比較寬鬆,因為數位電路有比較大的雜訊邊限(Noise Margin)。但對於類比電路而言,則不盡然。

暫態響應設計項目包含有輸出電壓變動量及變動之後的回復時間。此兩項目是越小 越好。暫態響應主要受到幾項因素影響,包含:輸出電容值,輸出電容的等效串聯電阻 (ESR),最大的負載電流,LDO 線性穩壓器的頻寬,以及 LDO 線性穩壓器的回轉率(Slew Rate)。一個可以量測 Load Transient 的電路,如圖 2.19 所示。將 LDO 線性穩壓器輸出端 接一個主動的電流鏡,再由ILoad產生一個步階的電流變化,然後觀察VOUT的變化情形。

典型的輸出電壓變化如圖 2.20 所示。當一個正的步階電流變化(positive step current change)加到 LDO 線性穩壓器的輸出端時,由於 LDO 線性穩壓器有限的頻寬無法即時提 供大的電流給負載,造成輸出電壓有一個 Vdrop 的下降。而在ΔT1這段時間,大部分的

負載電流是由輸出電容所提供,輸出電容之等效串聯電阻 ESR 與負載電流變化,會造成 輸出電壓有ΔILoad×RESR的瞬間壓降,Vdrop公式可以表示成:

max 1 Load drop ESR o b

I

V

T

V

C

C

−=

× Δ + Δ

+

(2.30) 因為Cb是高頻旁路電容,因此有比較低的 ESR,所產生的壓降可以忽略。ΔT1不只是與 LDO 線性穩壓器的閉回路頻寬有關也與系統內部的回轉率(Slew Rate)相

關,ΔT1 的表示式如下: 1

1

1

par sr par CloseLoop CloseLoop srV

T

t

C

BW

BW

I

Δ

Δ ≈

+

=

+

×

(2.31) 其中 BWCloseLoop是系統的閉回路頻寬,tsr 是與傳輸電晶體(Pass Transistor)寄生電容 Cpar相關的迴轉率時間(Slew Rate Time),ΔVpar 是在Cpar上所造成的壓差,Isr 是回轉率所 限制的最大電流。以一個例子說明,如果 BWCloseLoop是 500kHz,Cpar是 40pF,ΔVpar是 0.5V,Isr 是 5 μA,CO是 10μF,沒有 ESR,最大負載電流ILoad-max是 100mA。依據(2.30)式及(2.31) 式 可得,輸出壓降Vdrop =60mV。

由(2.30)式及(2.31)式可知,一個大頻寬及快速迴轉率(Slew Rate )的 LDO 線性穩壓器會 有比較小的ΔT1,並且使得輸出壓降 Vdrop 比較小。而比較大的輸出電容 CO也可以減少

輸出壓降 Vdrop。

當ΔT1的回轉率(Slew Rate)階段結束,則進入ΔT2這段時間,LDO 線性穩壓器閉回路

開始反應時,表示 LDO 線性穩壓器已經偵測到輸出壓降 Vdrop,傳輸電晶體(Pass Transistor) 開始提供電流給輸出電容 CO及負載,使得輸出電壓可以拉回到原來電位。由於有限的迴

路增益 Loop Gain 使得拉回的位準與原始的位準有一段 ΔV2的誤差,這就是 LDO 線性穩

壓器的負載穩壓(Load Regulation)效果。

ΔV2 = RO-REG ×ILoad-max,其中RO-REG是 LDO 線性穩壓器閉回路輸出電阻。

在ΔT2這段時間主要受限於傳輸電晶體(Pass Transistor)充飽輸出電容 CO的時間以及 閉迴路系統的相位邊限(Phase Margin)。

另外一個情形是當負載突然移除,也就是一個負的步階電流變化(negative step current change)加到 LDO 線性穩壓器的輸出端時,傳輸電晶體(Pass Transistor)來不及關閉,使得 輸出電壓突然上升,直到傳輸電晶體(Pass Transistor)完全關閉。

在傳輸電晶體(Pass Transistor)未完全關閉前,會有多餘的電流流到輸出節點,造成一 個VPeak的壓降,而VPeak的壓降是多餘的電流對輸出電容CO及等效串聯電阻 ESR 充電所 造成的。描述如下:

max max

3

1

load load

peak esr esr

o b o b Close loop

I

I

V

T

V

V

C

C

C

C

BW

−=

× Δ +

≈

×

+ Δ

+

+

(2.32) 其中 ΔV3與系統的閉迴路頻寬及誤差放大器的迴轉率(Slew Rate )電流相關。由於在ΔT1及ΔT3時 LDO 線性穩壓器的迴轉率(Slew Rate )並不相同,所以造成VPeak與Vdrop並不完 全對稱。當傳輸電晶體(Pass Transistor)完全關閉後,就進入ΔT4階段,輸出電壓將下降

ΔV4(=VPeak-△Vesr),在此時多餘的電流只能靠迴授網路放電到最終值。放電的電流為 VREF/R2是固定值,因為低靜態電流的需求,這個放電電流一般只有幾μA,所以會花費很 長的ΔT4,ΔT4描述如下: 4 2 4 o b ref

C

C

T

R

V

V

+

=

×

× Δ

(2.33) 總而言之,為了改善暫態響應,必須提升 LDO 線性穩壓器的頻寬,增加迴轉率(Slew Rate ),及減少輸出電容的等效串聯電阻 ESR。 Vref R1 Error Amp R2 Vout Vin Vin ILOAD ILOAD Resr Cb Co 圖 2. 19 量測負載暫態響應的測試電路 [5] ILoad=0A ILoad=MAX. Vdrop Vpeak Small-signal setting (dependent on phase margin and B.W.)Vout Time ILoad=0A 1 ΔT 2 ΔT 3 ΔT 4 ΔT 2 ΔV 3 ΔV 4 ΔV 圖 2. 20 LDO 線性穩壓器的負載暫態響應 [4]

2.3.4 參考電壓的設計考量

許多的 DC-DC Converter 電路都需要一個精準的參考電壓源。而這個參考電壓源理論 上必須是與製程,電源電壓及溫度無關(P.V.T. independent)。常用的參考電壓電路有: (1) 能 隙參考電壓電路( Bandgap Reference Voltage Circuit) (2)CMOS 參考電路(CMOS Voltage Reference Circuit)兩種。 第一種參考電壓源是利用 BJT 電晶體的 pn 接面產生 VBE電壓,其溫度係數約為-2.2mV/ o K。此外,pn 接面也產生一個熱電壓Vt (=kT/q),該值正比於絕對溫度(PTAT)且它在室溫 下的係數為+0.085mV/ oK,將熱電壓 Vt乘上常數 K 並加上VBE電壓,則參考電壓為 REF BE t V =V +KV

(2.34) 將(2.34)式的兩邊對溫度做微分,可得: t REF BE

V

V

V

K

T

T

T

∂

∂

=

∂

+

∂

∂

∂

(2.35) 其中 VBE -1.5mV / oK T ∂ ≅ ∂ , t 0.087mV / o V K T ∂ ≅ ∂ ,只要設計適當的 K 值就可使得 REF 0 V T ∂ = ∂ 而得到一個與溫度無關的參考電壓。K 值 = 1.5m / 0.087m =17.2,則17.2

1.25

REF BE TV

≈

V

+

V

≈

V

(2.36) 由於 VBE 與電源電壓之間的關連性很小,所以能隙參考電壓( Bandgap Reference Voltage) 與電源電壓之間的關連性也很小。如圖 2.21 所示。∑

t kT V q =k

t KV BE V REF BE t V =V +KV t V 圖 2. 21 能隙參考電壓電路的基本原理 [6]在標準 n-well 的 CMOS 製程技術中,可以利用垂直的 PNP BJT 電晶體來實現能隙參 考電壓電路。一般的晶圓廠都會提供這個 Model。如圖 2.22,利用在 n-well 中的 P+

當作射 極(emitter),n-well 本身當基極(base),P 型基底當做集極(collector)。

n-well P+ P+ n+ P-substrate C E B 圖 2. 22 在 CMOS 製程技術中垂直的 PNP BJT 電晶體結構 [7] 以一個實際的基本電路做說明,如圖 2.23 所示。利用 Op Amplifier A1 的高增益及負 回授所形成的虛短路,將使得VX與VY兩點等電位。可得到 1 2 3 3 3

ln

EB EB T RV

V

V

n

I

R

R

−

=

=

(2.37) 然後由IR3流過R2及R3再加上VEB2的電壓,最後可以得到 2 2 2 3 2 3 3ln

(

)

( ln )(1

)

T REF EB EB TV

n

R

V

V

R

R

V

V

n

R

R

=

+

+

=

+

+

。 (2.38) 其中 Q2 是 n 個單位的 PNP BJT 電晶體,Q1 是 1 個單位的 PNP BJT 電晶體,而為了 達到實體佈局的對稱性,一般選擇 n=8。 為了達到零溫度係數的參考電壓,將(2.37)式中 VT項的係數設計為: 2 3 2 3(1

+

R

/

R

) ln

n

= +

(1

R

/

R

) ln 8

=

K

≈

17.2

(2.39) 由(2.38)式,可得R2/R3=7.27。這個電阻的比值與溫度無關。實際上,(2.38)式必須考慮 Op Amplifier A1 的偏移電壓(Offset Voltage)所造成的誤差。VREF R2 R1 X Y R3 A nA Q1 Q2 A1 IR3 圖 2. 23 實際的基本能隙參考電壓電路 [7] 第二種參考電壓源是完全只使用 MOS 電晶體及電阻來實現,因此可減少晶片的面 積。這類的參考電壓源主要依靠 NMOS 及 PMOS 的臨限電壓(threshold voltage)對溫度變化 不同來做溫度補償,如圖 2.24 所示。以 K.N.Leung and P.K.T. Mok. 在 2003 年所提出的電 路來說明[8]。如圖 2.25 所示。參考電壓可很容易推導如(2.40)式。 1 2 (1 ) | | REF GSN GSP R V V V R = + ⋅ − (2.40) 當 R1 及 R2 很大時,則流經 R1 及 R2 的電流可忽略。經由設計 R1/R2 的比值及 NMOS 和 PMOS 的大小可以得到最佳的溫度係數。文獻所提出溫度係數可低到 24ppm/℃。 當IB受到VDD 的變動而增加/減少時,VGSN及 |VGSP|也會跟著增加/減少,所以 VREF 對於電源電壓的變動並不敏感。然而這個電路的一個大問題是VREF與製程是相依的(臨限 電壓會隨製程變動),所以VREF必須透過電阻的微調(trimming)來校正。

V

THN|V

THP|

Temperature 圖 2. 24 與溫度相依的 NMOS 及 PMOS 臨限電壓 [8]VDD VREF RB M1 M2 M5 M3 M4 R1 R2 MN MP IB 圖 2. 25 一個完全使用 MOS 電晶體的參考電壓源 [8] 在設計參考電壓源時,主要的考量是在改善精確度及減少誤差來源。包含在電路及 實體佈局的誤差來源。以一個簡單的能隙參考電壓電路(圖 2.26)來說明設計時的考量。分 成三部份來討論: (1)BJT 電晶體及電阻的佈局考量 (2)電流鏡(Current Mirror)及電壓箝位 (Voltage Clamping)的設計考量 (3)電源拒斥比(Power Supply Rejection Ratio)的考量 [8] [9]

(1) BJT 電晶體及電阻的佈局考量: 為了減少不必要的 Trimming,BJT 電晶體及電阻在實體佈局上必須考慮對稱性。而 最佳的方法是使用同心軸的佈局方式,如圖 2.27 所示。 BJT 電晶體的 Q1 與 Q2 尺寸比率為 1: N。而 N 值一般是選擇為 8,而且所有的 BJT 電晶體越靠近越好,比較大的 N 值將造成比較大的元件之間的距離,因此造成製程上比 較大的偏移。 對於電阻的實體佈局而言,最佳的方法也是使用同心軸的佈局方式。電阻的的排列 方式最好是長方形或正方形的型式如圖 2.27(b)所示。使用比較長及比較寬的電阻則可以 忽略 Contact 電阻的影響。

VDD X Y R2 R1 M1 M2 M5 M3 M4 VREF N 1 1 Q1 Q2 Q3 I I I Current Mirror Voltage clamping 圖 2. 26 簡單的能隙參考電壓電路 [8] Q2 Q1 Q1 Q1 Q1 Q1 Q1 Q1 Q1 dummy dummy du mm y du mm y (a) (b) 圖 2. 27 (a)BJT 電晶體及(b)電阻的同心軸佈局 [8].

(2)電流鏡(Current Mirror)及電壓箝位(Voltage Clamping)的設計考量:

在圖 2.26 簡單的能隙參考電壓電路中,由於電源電壓的變動,電流鏡(M1,M2,M5)和 電壓箝位(M3,M4)既使是使用長通道的 MOS 電晶體也無法完全將VX及VY兩點等電位。 而使用疊接的電流鏡(Cascode current mirror)是一種方法,但並不適用在低電壓的電路中。 一個比較廣泛使用的方法是以誤差放大器為基礎的電流鏡,如圖 2.28 所示。

在這架構中,理想的誤差放大器 A1 的電壓增益很高,使得 VA=VB。然後再經由設 計R2=R3,使得VDS1 = VDS2,因此 M1 與 M2 的電流 I 可以達到最佳的對稱性。而在這個 架構中的VREF並不須要額外的電流分支來產生,因此功率損耗及誤差均可以被有效的降 低。

實際的誤差放大器 A1 的電壓增益是有限值,使得 VA≠VB,因而造成能隙參考電壓 電路的主要誤差來源。這個誤差來源可表示:

/

ERR A B OFFR OFFS DD

V =V −V =V +V +V A (2.41)

其中 VOFFR是隨機誤差電壓(製程漂移造成),VOFFS是系統誤差電壓,VDD/A 是有限 增益的誤差電壓,A 是誤差放大器 A1 的電壓增益。

為了降低系統誤差(VOFFS),誤差放大器必須使用最簡單的架構。如圖 2.28(b)所示是 最佳選擇﹐只有 MA1,MA2 及 MA3,MA4 兩組差動對必須完全對稱。

一般VERR必須遠小於VEB2-VEB1 = VTln(N),因此必須使用比較大的 N 值。

在(2.40)式中,假設VOFFR及 VOFFS此兩項很大時,VERR將無法由很高電壓增益 A 來 降低。因此,簡單的誤差放大器架構將比高電壓增益來的重要。 在穩定度方面,共有三個高阻抗的節點需要考量,分別是 A 點,B 點及 C 點。為了 增加穩定度,必須加入補償電容到電路中,有三種方法,分析如下: (a)將補償電容加在 VDD 與 C 點之間形成主極點補償。此種方法所需要的補償電容必 須很大,而且 VDD 的電源雜訊很容易經由補償電容傳到 VREF 。 (b)將補償電容加在 C 點與地之間,此種方法的缺點是線上暫態反應(Line Transient Response)太慢,當電源 VDD 突然改變的時候,因為很大的補償電容,C 點的電壓無法即 時反應,而造成 VREF 必須花費很長的安定時間 (Settling Time)。

(c)最好的方法是將補償電容加在 A 點與 C 點之間形成米勒效應(Miller Effect),而補 償電容也可以做的很小,節省面積。

(3)電源拒斥比(Power Supply Rejection Ratio)的考量

一個改善電源拒斥比的能隙參考電壓電路如圖 2.29。分成三個部份來改善,第一個 部份在輸入側是由 RS,CIN及 ESRIN所組成的一階低通濾波器,其中 CIN及 ESRIN是由 N-Well 及 P-substrate 的 PN 接面所造成的寄生電容及電阻,如圖 2.30 所示。RS是外部電阻, 它可以用來阻隔高頻電源雜訊。CIN則提供一個高頻電源雜訊流失的路徑,ESRIN因為是 串聯在 CIN 而阻隔了高頻電源雜訊流失的路徑。因此為了得到比較好的電源拒斥比,必 須增加RS及CIN,減少ESRIN,但在考慮功率損耗時 Rs 也不能太大,如圖 2.31。

第二個部份在輸出側是由RF,COUT及ESROUT所組成的一階低通濾波器,其中RF, COUT是外部濾波電阻及電容,ESROUT是COUT的寄生串聯等效電阻。與第一個部份一樣, 為了得到比較好的電源拒斥比,必須增加 RF 及COUT,減少ESROUT,如圖 2.32。

第三個部份是利用長通道的 PMOS 電流鏡(M1,M2,M5)來增加汲極端的小信號電阻 (ro)以阻隔電源雜訊,短通道及長通道 PMOS 電流鏡的 PSRR 比較,如圖 2.33。但對於高 頻部份的電源雜訊,兩者並無差別。

VDD M1 M2 VREF A1 R3 R2 R1 N Q1 Q2 1 Vin+ V in-Vo VDD A B C I I MA4 MA3 MA1 MA2 2I C A B 圖2.28 (a)使用誤差放大器為基礎的能隙參考電壓電路. (b)簡單的差動對放大器[9]. Vdd VDD Rs CIN ESRIN R1 R2 RF VREF Q1 Q2 Q3 xN x1 x1 M1 M2 M3 M4 M5 Cout ESRout (1) (2) (3) Parasitic 圖2. 29 一個改善電源拒斥比的能隙參考電壓電路[9].

VDD n-well P-substrate N+ P+ GND CIN(parasitic) ESRIN(parasitic) 圖2. 30 PN 接面所形成的寄生電容及電阻[9]. 加上Cin 及大的ESR -40dB 0dB - 180dB 10 100 1k 10k 100k 1M 10M 100M Frequency (Hz) VREF(dB) 加上Cin 及小的ESR 加上Cin及ESR=0 S R ≠0 S R ≠0 S R ≠0 S R =0 圖2. 31 輸入側的 PSRR[9]. No Cout RF加上COUT及大的ESR -40dB 0dB -180dB 10 100 1k 10k 100k 1M 10M 100M Frequency (Hz) VREF(dB) RF加上COUT及小的ESR RF加上COUT及ESR=0 圖2. 32 輸出側的 PSRR[9].

Using Long channel length PMOS -26dB 0dB -34dB 10 100 1k 10k 100k 1M 10M 100M Frequency (Hz) VREF(dB) 1G 10G Using Short channel length PMOS 圖2. 33 長通道及短通道 PMOS 電流鏡的 PSRR[9]. 總而言之,為了改善參考電壓源的精確度及減少誤差來源,在元件佈局,電路的架 構及電源雜訊上都必須仔細考量。

2.3.5 誤差放大器的設計考量

誤差放大器的規格與 LDO 線性穩壓器的各項效能息息相關,包含有輸出阻抗,增益, 頻寬,輸出的迴轉率電流(output slew-rate current),輸出電壓的擺幅,及靜態電流。在傳統 LDO 線性穩壓器中(如 2.3.2 節),誤差放大器的輸出阻抗(Roea)很大,在加上傳輸電晶體(Pass Transistor)的閘級端的寄生電容(Cpar約幾十 pF)也很大,兩者所形成的極點 2 1 oea par P R C = × 限制了系統的頻寬。為了增加系統的頻寬,一般作法是在誤差放大器及傳輸電晶體(Pass Transistor)之間加入一個電壓緩衝器(Voltage Buffer),如圖 2.34 所示。 利用電壓緩衝器(Voltage Buffer)的低輸入電容及低輸出阻抗的特性,原本的 P2 將分 離成 P2'及 P2"。 ' " 2 2 1 1 ,par buf buf oea

P P

C R C R

= = (2.42)

其中Cpar是傳輸電晶體(Pass Transistor)閘級端寄生電容,Rbuf是電壓緩衝器的輸出阻抗, Cbuf是電壓緩衝器的輸入電容,Roea是誤差放大器的輸出阻抗。

因為Rbuf ,Cbuf 遠小於 Roea 及 Cpar使得P’2 及 P”2遠大於P2,一般由於Cpar很大, 所以P”2>> P’2 。

由於P’2 及 P”2 已經被分離到很高頻,原主極點 P1的CL可以做的很小,因此產生了 新的高頻的P”1。如圖 2.35 所示,整個 LDO 線性穩壓器的頻寬也因此增加。

但是使用電壓緩衝器的 LDO 線性穩壓器並不適合用在低電壓電源(~1.2V)的電路 中,主要是基於下列兩項原因:

(1) 有一個 VGS(或|VSG|)的電壓差跨在電壓緩衝器的輸入與輸出之間,造成傳輸電晶 體(Pass Transistor)不容易完全打開(對於 P-Type Pass Transistor)或完全關閉(對於 N-Type Pass Transistor),如圖 2.36。

(2) 由於使用電壓緩衝器所造成的 VGS電壓差,將使得誤差放大器的輸出電壓的擺幅

受到壓縮,而造成部份電晶體工作在線性區,誤差放大器的增益因此變小。

雖然採用電壓緩衝器的 LDO 線性穩壓器並不適合用在低電壓電源的電路,但對於標 準電壓電源的電路仍然是常用的架構。例如由 Ricon-Mora 所提出"Current Efficient Buffer"的 LDO 線性穩壓器[10],如圖 2.37。其中 Buffer Stage 是由一個 sensing MOS (Mps), 一對電流鏡,一個偏壓電流源 IBIAS 及一個 emitter follower 所組成。這個電路的工作原理 除了利用電壓緩衝器(Buffer)來改善頻寬之外,另一個功能就是可以增加暫態時的電流驅 動能力。經由 sensing MOS (Mps)部份的負載電流,再經由電流鏡將 sensing 的電流 IBOOST

傳回電壓緩衝器(Buffer),加速傳輸電晶體(Pass Transistor)的打開及關閉。

在輕載時,IBOOST幾乎為零。流到電壓緩衝器(Buffer)的電流只有偏壓電流 IBIAS。因此電

流效率很高。在重載時,IBOOST隨負載增加也同時增加了電壓緩衝器(Buffer)的電流,使得

電壓緩衝器(Buffer)的輸出阻抗變小,P2 變成更高頻,頻寬瞬間變大(如圖 2.38),而且所 增加的 IBOOST電流也加強了暫態時的迴轉率電流(output slew-rate current) (如圖 2.39)。

因此,此種 LDO 線性穩壓器的偏壓電流可以隨負載狀況來調整。不但兼顧了電流效 率,也同時改善了暫態時的效能。 Vref Vout Voltage Buffer Error Amplifier

Roea Cbuf Rbuf Cpar

Pass Transistor Vin ' 2 1 par buf P C R = " 2 1 buf oea P C R = R1 R2 ESR Co RL 圖 2. 34 使用電壓緩衝器的 LDO 線性穩壓器[11]

![圖 2.6 LDO 線性穩壓器的輸出雜訊[10]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/23.892.165.759.904.1084/圖26LDO線性穩壓器的輸出雜訊1.webp)

![圖 2. 12 傳統 PMOS LDO 線性穩壓器的小信號模型 [3]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/29.892.159.810.243.426/圖212傳統PMOSLDO線性穩壓器的小信號模型3.webp)

![圖 2. 35 使用電壓緩衝器的 LDO 線性穩壓器 Loop Gain[11]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/46.892.187.781.119.420/圖235使用電壓緩衝器的LDO線性穩壓器LoopGain11.webp)

![圖 2. 38 Current efficient-transient boost LDO 線性穩壓器的頻率響應[10]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/47.892.240.708.746.958/圖238CurrentefficienttransientboostLDO線性穩壓器的頻率響應1.webp)

![圖 2. 39 Current efficient-transient boost LDO 線性穩壓器的暫態響應[10]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/48.892.265.683.142.394/圖239CurrentefficienttransientboostLDO線性穩壓器的暫態響應1.webp)

![圖 2. 42 LDO With Buffer Impedance Attenuation 的負載暫態響應 [12]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592529.189828/51.892.241.708.143.502/圖242LDOWithBufferImpedanceAttenuation的負載暫態響應12.webp)