蕭基位障對奈米碳管電晶體與薄膜電晶體之影響

110

0

0

全文

(2) 蕭基位障對奈米碳管電晶體與薄膜電晶體之影響 Impact of Schottky Barrier on Carbon Nanotube FETs and Thin-Film Transistors. Student : Yi-Che Lee. 研究生:李宜澤. Advisor : Bing-Yue Tsui. 指導教授:崔秉鉞. 國立交通大學 電子工程學系. 電子研究所. 碩士論文 A thesis Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical Engineering and Computer Science National Chiao Tung University in Partial Fulfillment of the Requirement for the Degree of Master in Electronic Engineering July 2005 Hsinchu, Taiwan, Republic of China. 中華民國九十四年七月.

(3) 蕭基位障對奈米碳管電晶體與薄膜電晶體之影響. 研究生:李宜澤. 指導教授:崔秉鉞. 國立交通大學電子工程學系 電子研究所碩士班. 摘要. 自從奈米碳管於 1998 年被首次製作成奈米碳管電晶體之後,許多相關 的研究便如火如荼的進行著。而許多奈米碳管電晶體的相關性質如雙極性 電流特性等等也一一被發現。截至今日為止,蕭基位障模型是最普遍被人 們所接受用來解釋奈米碳管電晶體之雙極性電流特性之模型。然而,卻只 有一些直接證據可以證明奈米碳管電晶體是蕭基位障的元件。 在本論文中,我們提出了一種具有副閘極結構的元件結構,並且利用 ISE TCAD元件模擬程式來模擬在不同副閘極電壓下的蕭基位障元件之電 流特性。從模擬的結果中,我們發現因為蕭基位障會受到閘極電壓壓縮或 是增厚,蕭基位障元件之ID-VG電流特性會出現雙極性的電流特性。而ID-VD 特性則會因為汲極端的蕭基位障在不同的閘極電壓下,會受到汲極電壓的 增加而降低位障高度,或是簡少位障厚度始得電流的變化出現完全不同的 趨勢。 而當我們在副閘極施加正電壓時,也可以壓抑導帶的蕭基位障,並且 增厚價帶的蕭基位障,因而使得電子的導通電流增加,並且減少電洞的導 通電流,反之亦然。 實際的電性量測中發現蕭基位障薄膜電晶體與奈米碳管電晶體都可以 量測到與模擬結果有相同趨勢的電流特性,而副閘極也可以影響其電流特 i.

(4) 性。然而奈米碳管電晶體因為其細微的準一維結構,使得其電流特性受到 負閘極電壓的影響比起薄膜電晶體要小的多。 最後,我們將溫度模型引入模擬程式中來探討溫度對於蕭基位障薄膜 電晶體與奈米碳管電晶體之作用。實際的量測結果中發現奈米碳管電晶體 在不同溫度下的電流特性與模擬結果相符,但是蕭基位障薄膜電晶體會受 到通道中的晶界所影響而出現與模擬結果相當大的差距。總而言之,本論 文提出了數個直接證據說明奈米碳管電晶體可以視為一個單晶通道的蕭基 位障元件。. ii.

(5) Impact of Schottky Barrier on Carbon Nanotube FETs and Thin-Film-Transistors. Student: Yi-Che Lee. Advisor: Bing-Yue Tsui. Department of Electronics Engineering Institute of Electronics National Chiao Tung University Abstract Since the carbon nanotube field-effect transistor (CNTFETs) were proposed in 1998, lots of researches have been performed and many interesting properties have been reported, for example ambipolar behavior. Until now, Schottky barrier model (SB model) is the most accepted model to explain the ambipoar I-V behavior of CNTFETs. However, there are still little direct evidences to prove that the CNTFETs are Schottky barrier devices. In this work, we proposed a novel device structure with source/drain sub-gates and used ISE TCAD simulation program to reveal the behavior of the Schottky barrier devices with various sub-gate biases. From the simulation results, we found that due to the thickness of Schottky barrier would be thickened or be suppressed by the gate bias, the ID-VG behavior of SB devices shows ambipolar characteristic. Besides that, as a result of that the Schottky barrier at drain side is lowered or thinned at different gate bias, the ID-VD behavior shows completely different trend as the drain voltage increases. When we apply positive voltage at sub-gates, the Schottky barrier at conduction band will be suppressed and that at valance band will be thickened. iii.

(6) Therefore, the electron current will increase and the hole current will decreases and vice versa. Electrical measurement shows that the CNTFETs and TFTs exhibit the same I-V characteristics trend with the simulation results and that the sub-gates could affect the characteristics of both CNTFETs and SBTFTs. However, due to the tiny one-dimensional geometry of CNT, the sub-gates have much less effect on CNTFETs. Finally, we included temperature model into the simulation program to investigate the temperature effect of SBTFTs and CNTFETs. The measured temperature effect of CNTFETs shows quite good agreement with the simulation results. However, as a result of grain boundary in actual SBTFTs channel, the measured results are quite different from the simulattion results. Conclusively, this work provides several direct evidences to support that the CNTFETs could be treated as SB devices with single crystalline channel.. iv.

(7) 誌謝. 短短兩年碩士生活在一眨眼中飛逝,在這兩年中受到了許多人的幫助與指導,漸漸 從一個懵懂的大學生蛻變成一個對半導體技術略知一二的碩士學生,在這個即將離開栽 培我許久的環境之前,僅以本文略表我對於他們的感謝。 在其中,首要感謝的是我的指導教授 崔秉鉞老師在各方面的指導。老師在研究與 論文上都給予最大的支持與指導,因此才能順利的在短短的兩年中完成這份論文與研 究,此外,老師對於學生的照顧與待人處事的圓容更是大大的影響了我的做事方法。 其次要感謝的是同實驗室的林家彬學長,黃誌鋒學長與張志廉學長。三位學長在實 驗上提供了許多的寶貴意見,並且不厭其煩的指導我作實驗時的方法與心態,使我的實 驗得以順利的完成。還有謝志民學長在電子顯微鏡方面的大力支援,使元件製作過程中 遭遇的困難得以迅速解決。 此外,由清華大學蔡春鴻教授所領導的台灣聯合大學系統的奈米碳管研究計劃群以 及國家型奈米計劃研究群在奈米碳管的理論與元件的分析上提供了許多寶貴的意見,使 我的研究中所發現的許多有趣現象可以得到有力的理論說明,其中特別感謝辛坤瑩學長 在元件理論上的研究與討論,特別在此誌謝。 接著要感謝國家奈米元件實驗室與國立交通大學奈米中心提供優良的設備讓我的 實驗得以順利完成。其中,對於奈米元件實驗室的陳俊淇學長與范庭瑋小姐在微影製程 方面的大力支援,使我可以專注於奈米碳管的研究上,而不需要費神控制微影參數。 還有國家高速電腦中心提供 ISE TCAD 元件模擬程式,以及穩定的工作站環境,以 我的模擬可以順利的進行並得到相當完美的結果。 除了實驗上的幫助之外,本研究群中的黃祺聰學長,吳偉豪學長,方國龍學長,張 修維學長也對我作研究的態度與方法有相當的指導與幫助,還有在一起求學的兩年中與 本研究群中的薛聖銘,金立峰,與盧季霈同學互相砥礪向上,也是我求學中的一股動力。 而李佳蓉 ,吳明錡 ,林孟漢,黃永助等學弟妹則是在實驗與生活中的幫忙,對我也是 有相當大的助益。 最後,我要感謝我的父母與兄長,感謝他們在我求學的過程中的大力栽培與默默付 出,使我在生活上沒有後顧之憂,而得以順利的完成學業。 總而言之,感謝各位在我 兩年的碩士生活中的幫忙與指導,再次感謝。 v.

(8) 目錄 論文摘要(中文)........................... i. 論文摘要(英文)........................... iii. 誌謝....................................... v. 目錄....................................... vi. 圖目錄..................................... ix. 第一章 緒論 1-1 奈米碳管的發現與製作方式..................................1 1-2 奈米碳管的結構與特性......................................2 1-3 奈米碳管在電子元件上的應用 ...............................3 1-4 奈米碳管與金屬接觸面之蕭基位障............................6 1-5 蕭基位障之調變............................................6 1-6 論文結構..................................................7. 第二章 元件結構與製程步驟 2-1 緒論.....................................................16 2-2 元件模擬結構與所使用之模型...............................17 2-3 實作樣品之元件結構.......................................17 2-4 元件佈局.................................................18 2-5 元件製程步驟.............................................19 2-6 元件量測.................................................22. vi.

(9) 第三章 常溫電性模擬結果討論 3-1 緒論 ....................................................29 3-2 電極功函數對薄膜電晶體ID-VG特性之影響 ....................29 3-3 電極功函數對薄膜電晶體ID-VD特性之影響 ....................30 3-4 副閘極電壓對薄膜電晶體ID-VG特性之影響 ....................31 3-5 副閘極電壓對薄膜電晶體ID-VD特性之影響 ....................32 3-6 源極端副閘極電壓對基板電壓調變電流之影響 ................32 3-7 小結 ....................................................33. 第四章常溫元件量測結果與討論 4-1 緒論.....................................................44 4-2 副閘極結構對電性與製程之影響.............................44 4-3 金屬電極材料對薄膜電晶體與奈米碳管電晶體ID-VG特性之影響 ..45 4-4 金屬電極材料對薄膜電晶體與奈米碳管電晶體ID-VD特性之影響 ..47 4-5 副閘極電壓對薄膜電晶體與奈米碳管電晶體ID-VG特性之影響 ....48 4-6 副閘極電壓對薄膜電晶體與奈米碳管電晶體ID-VD特性之影響 ....49 4-7 源極端副閘極電壓對基板電壓調變電流之影響.................50 4-8 小結 ....................................................50. 第五章 低溫電性模擬結果與討論 5-1 緒論.....................................................69 5-2 溫度對薄膜電晶體ID-VG特性之影響 ..........................70 5-3 溫度對薄膜電晶體ID-VD特性之影響 ..........................71 5-4 副閘極電壓對薄膜電晶體在不同溫度下之ID-VG特性之影響 ......71 5-5 副閘極電壓對於薄膜電晶體在不同溫度下之ID-VD特性之影響 ....72 vii.

(10) 5-6 小結 ....................................................73. 第六章 低溫電性量測結果與討論 6-1 緒論.....................................................80 6-2 溫度對薄膜電晶體與奈米碳管電晶體ID-VG特性之影響 ...........80 6-3 溫度對薄膜電晶體與奈米碳管電晶體ID-VD特性之影響 ...........82 6-4 小結 .....................................................82. 第七章結論與展望 7-1 結論.....................................................87 7-2 未來展望.................................................88. 參考文獻 ..................................................90. viii.

(11) 圖目錄 第一章 圖 1-1. 三種奈米碳管成長方式之示意圖。(a)弧光放電法;(b)雷射熱熔法; (c)化學氣相沈積法。. 圖 1-2. 奈米碳管之結構,將片狀結構之石墨捲起,便可成為一管狀之奈 米碳管。[13]. 圖 1-3. 奈米碳管之管壁結構示意圖:(a) 單層壁奈米碳管; (b)多層壁奈米 碳管; (c) 奈米碳管束。[10]. 圖 1-4. 特徵向量與(n,m)關係。. 圖 1-5. 不同的(n,m)對有不同的奈米碳管結構。. 圖 1-6. 不同閘極結構之奈米碳管電晶體(a)背閘極奈米碳管電晶體之結 構[7] (b) 側閘極奈米碳管電晶體之結構[23](c)上閘極奈米碳管 電晶體之結構[24]。. 圖 1-7. 早期奈米碳管電晶體多半呈現 P-type 特性,必須要施加負的閘極 電壓才能使電晶體導通。[7]. 圖 1-8. 將奈米碳管置於真空中進行退火,可以將奈米碳管電晶體由 P-type 特性轉變成 N-type 特性。[29]. 圖 1-9. 利用鉀蒸汽使鉀吸附於奈米碳管上,可以將 P-type 特性之奈米碳 管轉並成 N-type 特性。[29]. 圖 1-10 使用一較高功函數之金屬與奈米碳管接觸時,由於較高的電子蕭基 位障,因此會產生 P-type 之特性:(a)正閘極電壓時,電子看到較 大蕭基位障,因此無電流傳導 (b)負閘極電壓時,電洞看到較小 的蕭基位障,因此可以穿過蕭基位障,使電晶體導通。[33] 圖 1-11 使用功函數位在能隙中央之金屬與奈米碳管接觸時,不論是給予正 或負的閘極電壓,載子所看到的蕭基位障皆小,所以可以導通。[33] ix.

(12) 第二章 圖 2-1 於源極與汲極下方增加副閘極之奈米碳管電晶體結構。 圖 2-2 模擬所用之薄膜電晶體結構。 圖 2-3 不同副閘極結構之奈米碳管電晶體/薄膜電晶體剖面結構圖:(a) N+/ P+副閘極 (b)高摻雜之多晶矽副閘極。 圖 2-4 元件之金屬電極與副閘極之佈局圖:(a)設計八個電極與副閘極以增 加製作出奈米碳管電晶體之機會(b)將副閘極延伸出金屬電極 0.1μm 寬度以克服微影之對準誤差。 圖 2-5 在元件兩側分別設計接觸窗,經過蝕刻後,製作鋁 Pad 與鋁閘極, 即完成元件的製作。 圖 2-6 將元件重複排列以增加晶圓中之元件數目。 圖 2-7 兩種不同副閘極結構之元件製程示意圖。 圖 2-8 利用 SEM 尋找有接觸到金屬電極之奈米碳管。. 第三章 圖 3-1. 不同電極功函數模擬之薄膜電晶體ID-VG特性模擬結果。(a)功函數 為 4.5eV之ID-VG特性模擬結果 (b)功函數為 4.8eV之ID-VG特性模擬 結果。. 圖 3-2 不同金屬電極功函數造成不同的蕭基位障高度:(a)較低的金屬功函 數造成電子的蕭基位障較低且較薄以及電洞的蕭基位障較高且較 厚,而有較大的電子電流,和較小的電洞電流。(b) 較高的金屬功 函數造成電子的蕭基位障較高且較厚以及電洞的蕭基位障較低且 較薄,而有較小的電子電流,和較大的電洞電流。 圖 3-3. 不同金屬電極功函數模擬之薄膜電晶體ID-VD特性模擬結果。(a)功 函數為 4.5eV之不同閘極電壓下的ID-VD特性模擬結果 (b)功函數 x.

(13) 為 4.8eV之不同閘極電壓下的ID-VD特性模擬結果 圖 3-4 不同閘極電壓下,當汲極電壓增加時,電晶體的能帶圖:(a)閘極施 加正電壓時,電流隨著汲極的蕭基位障減少而增加,最後達到飽 和 (b)當汲極電壓很大時,會產生電洞穿隧電流,使得飽和電流再 次增加(c)當閘極施加負電壓時,汲極電壓的增加會使的電洞穿隧 電流隨之增加。 圖 3-5. 不同的副閘極電壓對不同的金屬電極功函數之薄膜電晶體之ID-VG 特性模擬結果:(a)金屬電極功函數為 4.5eV之薄膜電晶體模擬結果 (b)金屬電極功函數為 4.8eV之薄膜電晶體模擬結果。. 圖 3-6 當副閘極施加不同電壓時,會造成電子與電洞在金屬與半導體介面 上的蕭基位障的厚度改變:(a)副閘極施加負電壓時,使的電子看 到的蕭基位障變厚,但使得電洞看到的蕭基位障變薄。(b) 副閘極 施加正電壓時,使的電子看到的蕭基位障變薄,但使得電洞看到 的蕭基位障變厚。 圖 3-7. 不同的副閘極電壓對不同的金屬電極功函數之薄膜電晶體的ID-VD 特性影響模擬結果:(a)金屬電極功函數為 4.5eV之薄膜電晶體模擬 結果(b) 金屬電極功函數為 4.8eV之薄膜電晶體模擬結果。. 圖 3-8 不同的源極端的蕭基位障對於導通電流的影響:(a)正閘極電壓時, 對導通電流有明顯影響(b)負閘極電壓時,對導通電流的影響較小。 圖 3-9. 不同基板電壓下,源極端副閘極電壓對於導通電流的影響模擬結 果:(a)基板電壓為 2.5V 模擬結果(b)基板電壓為-5V 模擬結果。. 第四章 圖 4-1 不同N+/P+副閘極電壓對薄膜電晶體之ID-VG特性之影響量測結果: (a)N+副閘極施加正電壓對於薄膜電晶體之影響。(b)P+副閘極施加 xi.

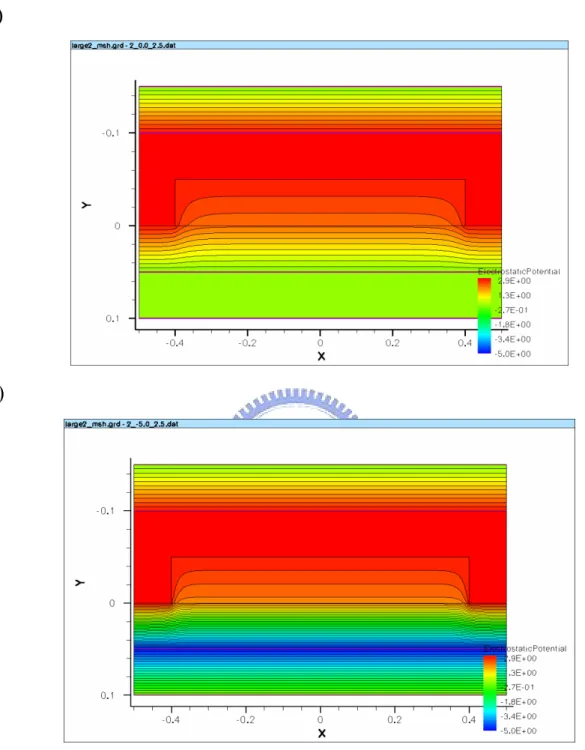

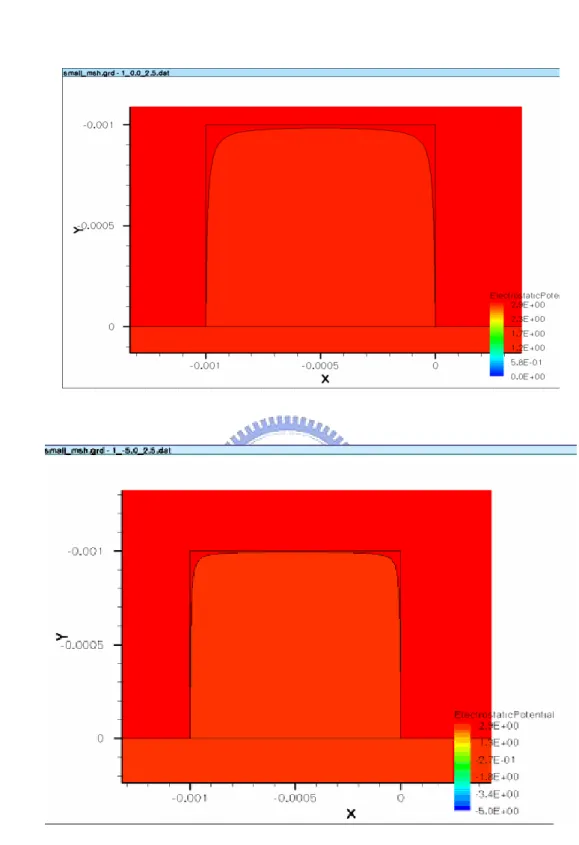

(14) 負電壓對薄膜電晶體之影響。 圖 4-2 不同多晶矽副閘極電壓對薄膜電晶體之ID-VG特性影響量測結果。 圖 4-3. 使用不同金屬電極材料之薄膜電晶體之ID-VG特性量測結果:(a)使 用鈦金屬電極之薄膜電晶體 (b)使用鉑金屬電極之薄膜電晶體。. 圖 4-4. 使用鈦金屬電極之奈米碳管電晶體之ID-VG特性量測結果:(a)偏向 N-type之雙極性特性 (b)偏向P type之雙極性特性。. 圖 4-5 使用鉑金屬電極之奈米碳管電晶體之ID-VG特性量測結果:(a)P-type 之ID-VG特性 (b) N-type之ID-VG特性。 圖 4-6. 使用不同金屬電極材料之薄膜電晶體之ID-VD特性量測結果:(a)使 用鈦金屬電極之薄膜電晶體 (b)使用鉑金屬電極之薄膜電晶體。. 圖 4-7. 使用不同金屬電極材料之奈米碳管電晶體之ID-VD特性量測結果:(a) 使用鈦金屬電極之奈米碳管電晶體 (b)使用鉑金屬電極之奈米碳 管電晶體。. 圖 4-8. 副閘極電壓對不同金屬電極之薄膜電晶體ID-VG特性的影響量測結 果:(a)鈦金屬電極薄膜電晶體施加不同副閘極電壓之ID-VG特性(b) 鉑金屬電極薄膜電晶體施加不同副閘極電壓之ID-VG特性。. 圖 4-9 副閘極電壓對不同金屬電極之奈米碳管電晶體之ID-VG特性的影響 量測結果:(a)鈦金屬電極奈米碳管電晶體施加+5V副閘極電壓之 ID-VG特性(b) 鉑金屬電極奈米碳管電晶體施加+5V副閘極電壓之 ID-VG特性。 圖 4-10 使用不同厚度與寬度的多晶矽通道來模擬通道的大小對於副閘極 的影響力的影響。(a)厚 50nm 寬 1μm 之多晶矽通道(b)厚與寬都是 1nm 之多晶矽通道。 圖 4-11 當 50nm 之多晶矽通道下方之副閘極施加 0V 與 5V 時,通道中的 xii.

(15) 電位分佈。(a)副閘極為 0V 時的電位分佈(b) 副閘極為-5V 時的電 位分佈。 圖 4-12. 當 1nm 之多晶矽通道下方之副閘極施加 0V 與 5V 時,通道中的電 位分佈。(a)副閘極為 0V 時的電位分佈(b) 副閘極為-5V 時的電位 分佈。. 圖 4-13 當施加極性相反的閘極與副閘極電壓時,會產生通道-通道穿隧 (Band to Band tunneling)之現象。 圖 4-14 鈦金屬電極薄膜電晶體在不同閘極電壓下,副閘極電壓對其ID-VD特 性之影響量測結果:(a)閘極施加正電壓(b)閘極施加負電壓。 圖 4-15 鈦金屬電極之奈米碳管電晶體在不同閘極電壓下,副閘極電壓對其 ID-VD 特性之影響量測結果:(a)閘極施加正電壓(b)閘極施加負電 壓。 圖 4-16 不同基板電壓下,源極端副閘極電壓對於薄膜電晶體導通電流的影 響:(a)基板電壓為 20V(b)基板電壓為-20V。 圖 4-17 不同基板電壓下,源極端副閘極電壓對於奈米碳管電晶體導通電流 的影響:(a)基板電壓為 15V(b)基板電壓為-20V。. 第五章 圖 5-1 蕭基位障能帶圖[39]。 圖 5-2 金屬電極功函數為 4.5eV之薄膜電晶體在不同溫度下之ID-VG特性模 擬結果。 圖 5-3 金屬電極功函數為 4.5eV之薄膜電晶體在不同溫度下之ID-VD特性模 擬結果:(a)正閘極電壓之ID-VD特性 (b)負閘極電壓之ID-VD特性。 圖 5-4 不同副閘極電壓下,電極功函數為 4.5eV之薄膜電晶體在不同溫度 下的ID-VG特性模擬結果:(a)副閘極施加正電壓 (b)副閘極施加負 xiii.

(16) 電壓。 圖 5-5 不同副閘極電壓下,薄膜電晶體在正閘極偏壓時的不同溫度之ID-VD 模擬結果:(a)副閘極施加正電壓之ID-VD特性(b)副閘極施加負 電壓之ID-VD特性。 圖 5-6 不同副閘極電壓下,薄膜電晶體在正閘極偏壓時的不同溫度之ID-VD 模擬結果:(a)副閘極施加正電壓之ID-VD特性(b)副閘極施加負 電壓之ID-VD特性。. 第六章 圖 6-1 鈦金屬電極薄膜電晶體在不同溫度下之ID-VG特性量測結果。 圖 6-2 鈦金屬電極奈米碳管電晶體在不同溫度下的ID-VG特性量測結果。 圖 6-3 晶界上的缺陷會造成晶界處出現位障[42]。 圖 6-4 多晶矽的電阻率會隨著溫度的下降而逐漸增加[43]。 圖 6-5. 不同閘極電壓下,溫度對鈦金屬電極薄膜電晶體之ID-VD特性的影 響量測結果 (a)正閘極電壓下的ID-VD 特性 (b)負閘極電壓下的 ID-VD特性。. 圖 6-6. 不同閘極電壓下,溫度對碳管電晶體之ID-VD特性的影響量測結果 (a)正閘極電壓下的ID-VD特性 (b)負閘極電壓下的ID-VD特性。. xiv.

(17) 第一章 緒論 1-1奈米碳管的發現與製作方式 從 1991 年時,日本飯島澄男博士(S. Iijima)經由穿隧式電子顯微鏡(TEM) 發現奈米碳管結構(Carbon nanotube, CNT)開始[1],在過去的十幾年間,經 過各種的實驗發現:奈米碳管除了其奈米尺度的大小外,還具有相當高的 機械強度[2,3]、高導熱度[4]、高負載電流密度[5,6]等等相當優異的物理特 性。此外,對於某些特殊原子排列方式組成的奈米碳管,還具有可以作為 近代電子開關元件的電場調變效應[7,8],由於以上種種的優越特性,使得 奈米碳管成為相當受到看好的下一代電子元件材料。 而若是要將奈米碳管應用於工業上,需要相當有效的方法加以生產奈米 碳 管 , 目 前 用 來 生 產 奈 米 碳 管 的 方 式 主 要 有 三 種 : 弧 光 放 電 法 (Arc discharge)[9] 、 雷 射 熱 融 法 (Laser ablation)[10] 、 以 及 化 學 氣 相 沈 積 法 (Chemical vapor deposition)[11](如圖 1-1) 。 弧光放電法是在腔體中以高電流流過兩石墨電極,透過放電時產生的高 溫電漿將石墨電極上的碳原子氣化後,讓碳原子自行重新組合成管狀結構 而形成奈米碳管。 雷射熱融法是使用雷射光束打在溫度約 1200℃並且摻有少量鈷(Co)或 鎳(Ni)等觸媒金屬的石墨靶材上,利用高能量的雷射激發靶材上的碳原子, 使其自行組合成管狀結構,形成奈米碳管。 化學氣相沈積法則是在高溫或是電漿腔體中,置入覆有鈷(Co)或是鎳(Ni) 等等觸媒金屬的基板,並且通入含有碳原子的氣體(如甲烷,乙炔) ,利用. 1.

(18) 高溫或是電漿使氣體分解出碳原子,當碳原子溶入觸媒金屬後,使觸媒中 的碳原子濃度超過飽和濃度時,碳原子便會以管狀結構析出,而形成奈米 碳管。 在上面的三個方法中,弧光放電法與雷射熱融法可以製做出純度較高的 碳管粉末,甚至可以製作出單層管壁的奈米碳管,但是其產量少、成本高, 且不易與目前的半導體製程整合,因此僅用在前瞻性的奈米碳管研究。而 化學氣相沈積法除了可以大量生產外,也可以與目前的半導體製程相整 合,且具有定位定向成長的特性,可以有效的控制碳管的位置,但是其所 成長出來的碳管的直徑,長度,純度均仍有相當的困難有待克服。. 1-2奈米碳管的結構與特性 奈米碳管是由碳原子以sp2鍵結成一管狀結構,其外型類似將石墨之片狀 結構加以捲曲而成(如圖 1-2)[12,13],因此,在計算碳管的理論模型時, 大多採用與石墨相同的分子結構加以計算,然後再另外考慮捲曲所帶來的 能階變化。 當碳原子僅形成一層管壁時,此類奈米碳管稱之為單層壁奈米碳管 (Single Wall Carbon Nanotube, SWNT)(如圖 1-3(a))[9]此類碳管因為只有單 一層碳管壁,因此直徑多半在 1~2 奈米之間。 當碳原子形成多個同軸之碳管壁時,此類奈米碳管稱之為多層壁奈米碳 管(Multi-Wall Carbon Nanotube, MWNT) (如圖 1-3(b))[9]此類多層壁奈米 碳管由於有多層管壁,因此其直徑會隨著管壁層數的不同而由數奈米到數 百奈米不等。 此外,由於奈米碳管直徑小,且重量輕,因此當許多奈米碳管放置在一 起時,容易因為凡德瓦力(Van Der Waals force)之作用而彼此吸附形成奈 米碳管束(Nanotube rope/Nanotube bundle) (如圖 1-3(c))[10]。 2.

(19) 由於奈米碳管是一個奈米尺度之管狀結構,因此電子於其中運動時,僅 能沿著軸心方向運動,因此實際上奈米碳管中的電子之動量 k 並不能如石墨 結構中有兩個維度,而僅能隨著碳管軸心方向而固定在單一的方向,因此 可以先利用石墨之分子結構套用物理模型計算出石墨在sp2鍵結之片狀結構 時的能量-動量圖(E- k diagram),再利用碳管之軸心方向,進而確定奈米 碳管之E- k 關係,而得到半導體與導體兩種完全不同的奈米碳管之理論結 果。 因此,可以在石墨之片狀結構中,定義特徵向量(Chiral Vector) Ch=na1+ma2=(n,m)(如圖 1-4)為與碳管之軸向垂直之向量 [12],其中n,m 為整數。經由計算可以知道:當n-m為 3 的倍數時,其以此特徵向量為垂直 軸心方向之奈米碳管的E- k 關係中的能隙相當小,因此可以視為金屬性質之 奈米碳管。而以其他特徵向量為其軸心方向之碳管則有較大之能隙,因此 是半導體性質之奈米碳管。 此外,由於以不同特徵向量為垂直軸心方向的奈米碳管其外觀也會有所 不同,因此以(n,0)特徵向量為垂直軸心方向之奈米碳管稱之為 Zigzag 奈米 碳管。以(n,n)特徵向量為垂直軸心方向之奈米碳管則稱之為 armchair 奈米 碳管。其它則稱之為 Chiral 奈米碳管(如圖 1-5)[12]。 除了理論上的 E- k 關係造成之能隙外,實驗與理論計算上也發現奈米碳 管的能隙與其直徑也有成反比之關係[12,14]。當奈米碳管的直徑愈大時, 其能隙也會隨之減小。因此,一般的多層壁奈米碳管因為其外層之碳管壁 多在數十奈米以上,導致其能隙多半小於 0.1eV 以下。所以多層壁奈米碳 管大多顯示金屬性質,而無法當作一般半導體使用在電子開關元件上。. 1-3奈米碳管在電子元件上的應用 金屬性質的奈米碳管在實驗中發現其電流負載密度可以到達 10μA/nm2 3.

(20) 的數量級程度,與傳統的金屬導線之電流負載密度約 10nA/nm2相比,是相 當大的優勢[15]。因為在傳統的製程微縮的同時,電路中的導線寬度也會隨 之下降,因此造成導線的電阻增加及電流減小,進而嚴重影響電路的速度。 使用如金屬性質奈米碳管般高電流負載的材料去取代傳統的金屬導線將可 以有效的改善這個問題[16]。 此外,奈米碳管是由整齊的碳原子鍵結所組成,因此具有相當良好的抵 抗電致遷移(Electron migration)的能力[17],以及良好的熱傳導能力,可 以有效的傳出電路中所產生之熱量[4]。因此金屬性質的奈米碳管目前主要 的應用目標是磁性的碳管研究[18],掃描探針顯微鏡的探針[19],奈米碳管 場發射顯示器[20],或是取代傳統電路中的金屬導線與金屬栓(Plug) [21,22]。 半導體性質的奈米碳管則可以與傳統的半導體材料一般,透過電場的調 變改變其本身的阻抗,而可以製作成如傳統的場效應電晶體特性的奈米碳 管電晶體(CNT field effect transistor, CNTFET)[7,8]。 目前的奈米碳管電晶體主要結構有三種:背閘極(Back gate)奈米碳管 電晶體,側閘極(Side gate)奈米碳管電晶體,與上閘極(Top gate)奈米碳管電 晶體。 這三種奈米碳管電晶體的主要差異在於其閘極的製作方式。背閘極奈米 碳管電晶體的結構(如圖 1-6(a))[7],主要是使用基板(substrate)當作閘 極,並施加電壓產生電場去空乏(deplete)或是累積(accumulate)絕緣層上 的奈米碳管中的電子或電洞,進而改變奈米碳管的阻抗。由於背閘極結構 使用整片基板作為閘極,因此結構簡單,容易製作。但是由於整片基板都 是施加相同電壓,所以無法同時對不同的奈米碳管施加不同的閘極電壓, 因此不能用來製作邏輯電路。側閘極奈米碳管電晶體的結構(如圖 1-6(b)) [23],則是將閘極獨立成一個靠近奈米碳管的金屬電極,利用此金屬電極所. 4.

(21) 產生的電場來影響奈米碳管中的載子。側閘極結構改善了背閘極無法分別 控制不同的電晶體的缺點,但是因為其閘極是靠微影技術製作,因此閘極 與奈米碳管之間距不易縮小,且用來當作絕緣之材料為空氣,因此側閘極 奈米碳管電晶體之調變能力不佳。上閘極奈米碳管電晶體是使用類似傳統 的 CMOS 電晶體結構(如圖 1-6(c))[24],在奈米碳管上覆蓋一層絕緣層, 再製作閘極。上閘極結構不但可以單獨控制不同的奈米碳管電晶體,也擁 有較佳的奈米碳管調變能力。 除了一般的閘極設計外,有文獻使用電解液取代傳統的電極[25],或是 用高介電常數材料取代傳統的二氧化矽,而得到更好的電晶體特性[26,27]。 較 早 期 所 製 作 的 奈 米 碳 管 電 晶 體 大 多 顯 示 為 P-type 特 性 ( 如 圖 1-7)[7,24,25,26,27],但是後來的實驗中發現將奈米碳管電晶體置於高溫的真 空腔中進行退火,可以把原先是 P-type 特性的奈米碳管電晶體轉變成 N-type 特性[28,29]。因此推斷可能是奈米碳管在空氣中會吸附氧氣,由於氧分子 為一極性分子,所以當吸附在奈米碳管上時,會減少奈米碳管中的電子濃 度,因此使奈米碳管電晶體產生 P-type 效果,而當在高溫的真空腔中,吸 附在奈米碳管上的氧分子會離開奈米碳管,而使奈米碳管回復到 N-type 的 特性(如圖 1-8)。 除了利用高溫真空烘烤的方式使奈米碳管形成 N-type 特性外,也有文獻 指出可以利用鉀蒸氣(Potassium Vapor)去摻雜奈米碳管,將奈米碳管置於 鉀蒸氣中,使鉀吸附在奈米碳管上。利用鉀容易放出電子的特性,提高奈 米 碳 管 中 的 電 子 濃 度 , 使 其 特 性 由 P-type 轉 變 成 為 N-type( 如 圖 1-9)[29,30,31]。除了使用鉀蒸氣達成摻雜的效果外,也可以使用其他材料達 成增加奈米碳管中的電子濃度的作用[32]。. 5.

(22) 1-4奈米碳管與金屬接觸面之蕭基位障 除了上面所提到奈米碳管會因為吸附的雜質而產生不同的特性之外,最 近也有文獻認為奈米碳管電晶體的 P-type 特性是因為源極與汲極電極與奈 米碳管產生蕭基位障(Schottky barrier)的關係[33,34]。 在奈米碳管電晶體結構中,其汲極與源極大多都是使用鉑(Pt)或是鈦 (Ti)等金屬直接與奈米碳管接觸,其中鉑的功函數(Work function)大約是 5.65eV,而一般半導體性質的奈米碳管之費米能階(Fermi level)大約是 4.5eV 並且具有約 0.6eV 之能隙。因此,當奈米碳管電晶體當閘極施加正電壓時, 會在源極與汲極處形成電子的蕭基位障(如圖 1-10(a)) 。此蕭基位障會阻止 電子穿過源極與汲極接面,且電洞也會受到閘極所產生的位障而無法流過 奈米碳管,因此閘極給予正電壓時,奈米碳管電晶體會處於關閉的狀態。 反之,當閘極給予負電壓時,電子受到閘極所產生的位障影響,但是電洞 卻沒有蕭基位障可以阻擋(如圖 1-10(b)) ,因此當閘極給予負電壓時,奈米 碳管是呈現導通的狀態。所以使用鉑製作源極與汲極電極的奈米碳管電晶 體大多呈現 P-type 之電晶體特性。 若是使用如鈦(Ti)的功函數僅有 4.32eV 等功函數位在奈米碳管能隙中央 的金屬製作源極與汲極電極,則由於不論閘極給予正電壓或是負電壓時, 都會在源極與汲極產生電子或是電洞的蕭基位障,所以其導通電流會比較 小。但是當閘極電壓加大時,其蕭基位障的厚度會隨之變薄,使得載子可 透過穿隧效應(Tunneling effect)穿過蕭基位障形成電流(如圖 1-11) 。因此不 論是閘極施加正電壓或是負電壓均會使奈米碳管電晶體導通而形成雙極性 奈米碳管電晶體(Ambipolar CNTFET)[33,34,35]。. 1-5蕭基位障之調變 由於蕭基位障對於奈米碳管電晶體的電性有相當重要之影響,因此在目 6.

(23) 前缺乏一個有效控制奈米碳管摻雜的方法的情況下,藉由調變奈米碳管電 晶體之蕭基位障達到所需之電晶體特性是一個較為可行之方法。 目前調變奈米碳管與金屬接觸面的蕭基位障之方法主要可以分為使用 化學物質改變蕭基位障之高度或是使用電場改變蕭基位障之厚度兩種。當 化學物質(如:H2S或是alkanethiol等等)吸附在金屬電極上時,可以改變 金屬之功函數而得到不同位障高度的蕭基位障,進而得到不同的電氣特性 [36,37]。 此外,也可以藉由改變接觸面附近電場,進而改變金屬電極接觸附近奈 米碳管之位能。當奈米碳管在接觸面上的位能改變時,便可以有效的改變 蕭基位障的厚度,而蕭基位障的電流傳導機制中的穿隧電流(Tunneling current)與蕭基位障的厚度成一自然對數的反比關係,因此當蕭基位障受到 電場作用而改變其厚度時,便可以有相當明顯的電流特性改變,甚至決定 奈米碳管電晶體的導通與否[34,38]。. 1-6論文結構 本論文主要目的是在於實作一個三閘極之奈米碳管電晶體與薄膜電晶 體,利用源極與汲極下方之副閘極(sub-gate)產生電場,調變源極與汲極 之蕭基位障。利用不同的電場關係瞭解奈米碳管或是多晶矽與金屬電極之 間的蕭基位障對於奈米碳管電晶體與薄膜電晶體的電流傳導特性之影響。 第二章中會說明元件的結構與製作方法,包括元件結構之設計,詳細的 元件製程與定位方式以及所使用的儀器設備。 第三章中則是使用 ISE 公司的 TCAD 元件模擬軟體模擬一個三閘極結構 的薄膜電晶體在各種偏壓狀況下的電流特性,並且使用能帶圖(Band Diagram)加以解釋。 第四章中則是實際量測利用不同的金屬電極材料製作奈米碳管電晶 7.

(24) 體,測量各種偏壓下的電晶體的電流電壓特性,並且與第二章之模擬結果 作一比較,討論其中的相同處與差異處。。 第五章則是將 temperature model 引入模擬程式中,對薄膜電晶體進行低 溫時,在不同偏壓下的電性模擬,並且由蕭基位障的電流傳導機制以及載 子的遷移率來解釋電流對於溫度變化的反應。 第六章將實作出的奈米碳管電晶體與薄膜電晶體置於低溫量測系統 中,量測元件在低溫下的電流特性,並與第五章中的模擬結果作比較。 第七章是本論文最後的結論與對後續研究之建議. 8.

(25) 圖1-1. 三種奈米碳管成長方式之示意圖。(a)弧光放電法;(b)雷射熱熔法;. (c)化學氣相沈積法。. 9.

(26) 圖1-2. 奈米碳管之結構,將片狀結構之石墨捲起,便可成為一管狀之奈米. 碳管[13]。. (a). 圖1-3. (b). (c). 奈米碳管之管壁結構示意圖:(a) 單層壁奈米碳管; (b)多層壁奈米碳. 管; (c) 奈米碳管束[10]。. 10.

(27) 圖1-4 特徵向量與(n,m)關係。. 圖1-5 不同的(n,m)對有不同的奈米碳管結構。. 11.

(28) (a). (b) Gate. CNT. (c). 圖 1-6 不同閘極結構之奈米碳管電晶體(a)背閘極奈米碳管電晶體之結構 [7] (b) 側閘極奈米碳管電晶體之結構[23](c)上閘極奈米碳管電晶體之結 構[24]。. 12.

(29) 圖 1-7 早期奈米碳管電晶體多半呈現 P-type 特性,必須要施加負的閘極電 壓才能使電晶體導通[7]。. 圖 1-8 將奈米碳管置於真空中進行退火,可以將奈米碳管電晶體由 P-type 特性轉變成 N-type 特性[29]。. 13.

(30) 圖 1-9 利用鉀蒸汽使鉀吸附於奈米碳管上,可以將 P-type 特性之奈米碳管 轉並成 N-type 特性[29]。 (a). (b). 圖 1-10 使用一較高功函數之金屬與奈米碳管接觸時,由於較高的電子蕭基 位障,因此會產生 P-type 之特性:(a)正閘極電壓時,電子看到較大蕭基位 障,因此無電流傳導 (b)負閘極電壓時,電洞看到較小的蕭基位障,因 此可以穿過蕭基位障,使電晶體導通[33]。. 14.

(31) 圖 1-11 使用功函數位在能隙中央之金屬與奈米碳管接觸時,不論是給予正 或負的閘極電壓,載子所看到的蕭基位障皆小,所以可以導通[33]。. 15.

(32) 第二章 元件結構與製程步驟. 2-1 緒論 在前人對於奈米碳管之研究中,發現奈米碳管電晶體在使用鈦(Ti) 當作電極材料時,會發現奈米碳管電晶體出現雙極性(ambipolar)之電流 特性[33,34,35]。因此 IBM 研究人員認為之所以在奈米碳管上會出現雙極性 電流特性,是因為奈米碳管與金屬接觸面上之蕭基位障(Schottky Barrier) 受到背閘極(back gate)所產生的電場調變,因而在負閘極電壓下產生電洞 穿隧電流,以及正閘極電壓下產生電子穿隧電流,而形成雙極性之電流特 性[33,34]。 為了詳細探討奈米碳管與金屬電極之接觸面的性質,是否如同 IBM 所 稱之的蕭基位障造成奈米碳管的電流調變,我們將傳統的奈米碳管電晶體 結構稍作修改,使用上閘極結構,並且在源極與汲極(Source/Drain)下方各 增加一個副閘極(Sub-gate) ,如圖 2-1。利用所增加的兩個副閘極產生局部 的電場,進而影響奈米碳管位於源極與汲極處的位能。若是奈米碳管電晶 體是蕭基位障造成電流調變,副閘極便可以有效的影響奈米碳管電晶體之 電流特性。 而為了確定副閘極所造成之影響是在於源極與汲極處之接觸面,我們 將奈米碳管替換成未摻雜之多晶矽薄膜(Undoped poly silicon film)並使用 相同的電極結構製作出相同結構的多閘極薄膜電晶體。由於多晶矽與金屬 接觸面上必定存在有蕭基位障,因此,若多閘極奈米碳管電晶體展現出與 多閘極薄膜電晶體相同之電流特性,我們便可以確定奈米碳管電晶體的確 16.

(33) 是蕭基位障主控之元件。. 2-2 元件模擬結構與所使用之模型 首先我們使用ISE TCAD這套程式進行元件特性之模擬。先使用ISE中 的DEVISE程式繪製如圖 2-2 之 2D薄膜電晶體元件結構,元件中之Channel 使用 50nm之Silicon薄膜,以及 50nm之SiO2作為絕緣層。各個電極則是使用 宣告在介面上之方式,如此可以簡化元件的格點數,並且可以直接宣告各 電極為歐姆接觸或是蕭基接面,以及宣告電極之功函數。 電性模擬則是使用 ISE 中的 DESSIS 程式,並設定計算 Schottky Barrier tunneling current 以及 Thermionic emission current。載子之遷移率(Mobility) 之模型則是使用 Doping dependant mobility model,High field saturation model 以及 Normal field model。由於計算上發散的問題,Schottky barrier lowering model 並沒有使用在電性的計算中。 而 Schottky barrier tunneling 為了減少計算之負擔,所以在計算時設定 了一個穿隧長度作為限制,以簡化計算。. 2-3 實作樣品之元件結構 實際上的元件製作,由於目前缺乏有效的奈米碳管定位成長技術,因 此我們無法將奈米碳管使用傳統的方式沈積在晶圓上來製作出奈米碳管電 晶體。因此,在本實驗中,奈米碳管是採用懸浮於二甲基甲醯胺(Dimethy Formamide, DMF)之有機溶劑中,再以旋塗(Spin coating)之方式塗佈在 晶圓表面。但是旋塗方式的結果受到晶圓表面粗糙度影響相當大,因此元 件的製作上,採用兩種方式製作副閘極: 第一種方式是使用離子佈植方式(Ion implantation)在N-type基板上產 生P+ 區域,或是在P-type 基板上產生N+區域作為副閘極,如圖 2-3(a)。這 P. 17.

(34) 種方法所製作出的副閘極,不會使得晶圓表面有不平整的區域,因此在旋 塗奈米碳管時,不會發生奈米碳管卡在突出的表面的情形,而會有較均勻 的分佈。但是由於副閘極是利用離子佈植產生,因此副閘極的電壓必須與 基板的電壓維持在逆偏的狀況下,以免所施加於副閘極的電壓擴散到整個 元件之基板而影響所要觀測的元件特性。此外,為了觀察副閘極在正電壓 與負電壓下的電晶體特性,我們必須同時製作N substrate/P+ sub-gate與P substrate/N+ sub-gate之元件。 除了使用離子佈植方式製作次電極外,我們另外使用高摻雜的多晶矽 (In-situ doped poly silicon)來製作副閘極,如圖 2-3(b)。使用摻雜的多晶 矽製作的副閘極雖然會造成晶圓表面的高低起伏,但是由於不需要擔心副 閘極與基板之間的電壓關係,因此可以在副閘極上施加任意的電壓,也不 需要製作不同基板之元件。 除了副閘極結構之改變外,由於奈米碳管或是多晶矽與金屬接觸面上 的蕭基位障會受到金屬材料本身的功函數(Work function)影響,我們也分 別使用鈦(Ti)與鉑(Pt)作為接觸電極金屬來得到不同的蕭基位障高度。 但是鈦在後續的蝕刻製程中無法抵擋 BOE(Buffered Oxide Etchant)之蝕刻, 因此在鈦薄膜上增加一層鉑薄膜以抵擋蝕刻。而鉑與二氧化矽之接觸附著 力不佳,因此摻入微量的鉭(Ta)以增加鉑的附著力。. 2-4 元件佈局 由於在本實驗中,奈米碳管是採用旋塗的方式隨機塗佈於晶圓上,為了 增加奈米碳管與金屬電極接觸機會,我們在一個元件中設計了八個金屬電 極,如圖 2-4(a)。每個金屬電極的下方各設計一個次電極,而由於 i-line stepper 在不同層次光罩之間有對準誤差,因此副閘極的寬度均比金屬電極 左右各寬 0.1um,如圖 2-4(b),避免對準時產生的誤差使副閘極無法影響全 18.

(35) 部的金屬電極之接觸面。 由於副閘極與金屬電極位在同一位置上,僅有垂直高度的不同,所以 為了將金屬電極與副閘極分別接出,所以我們分別在元件的兩邊設計接觸 窗(Contact hole) ,並在蝕刻時增加蝕刻的時間,同時將兩種不同深度的接 觸窗挖開後,在製作後續的鋁 Pad 與鋁閘極,完成元件的製作,如圖 2-5。 為了增加晶圓上的元件密度以提高製造出奈米碳管電晶體的機會,我們 將五種不同金屬電極間距的元件分別複製 10 次,形成一個晶方(die),如 圖 2-6。再利用 i-line stepper 之重複曝光的特性,在一片晶圓上得到為數眾 多的元件。. 2-5 元件製程步驟 本實驗之元件樣品是在國家奈米元件實驗室之 Class 10 與交通大學奈米 中心 Class 10000 之無塵室中完成。詳細之元件製程如圖 2-7 所示,並詳細 說明如下: 1. 使用 Clean Track 以及 i-line stepper 進行零層光罩曝光。曝光完 成後再使用 TEL5000 Oxide etcher 進行零層蝕刻並使用 O-Zone asher 與硫酸清洗去除剩餘光阻。 2. a. 若是要製作N+/P+ 副閘極樣品,則使用Clean track以及i-line stepper進行N+/P+ 副閘極光罩曝光。曝光完成後,使用離子佈 植機對N substrate進行能量 90keV劑量 1e14 之BF2+離子佈植, 或是對P substrate進行能量 100keV 劑量 1e14 之As-之離子佈 植。離子佈植完成後,使用O-zone asher與硫酸清洗去除光阻, 再用Wetbench進行STD clean process,清洗完成後,送入Oxide RTA進行 1000℃ 10sec之退火,進而將雜質活化,形成摻雜之. 19.

(36) N+或是P+副閘極,如圖 2-7 (a)右圖。 P. b. 若是要製作多晶矽副閘極樣品,則將晶圓經過 STD clean process 後,送入垂直爐管(Vertical Furnace)中進行 100nm 二 氧化矽薄膜沈積以及 50nm 之摻雜多晶矽(in-situ doped poly silicon)薄膜沈積。沈積完成後,使用 Clean track 以及 i-line stepper 進 行 多 晶 矽 副 閘 極 光 罩 曝 光 。 曝 光 完 成 後 , 送 入 TCP-9400 poly-Si etcher 中進行多晶矽之蝕刻,蝕刻完成後,送 入 O-zone asher 與硫酸清洗去除光阻,即完成多晶矽副閘極之 製作,如圖 2-7(a)左圖。 3. 使用 RCA clean process 清洗完成副閘極的晶圓,再將晶圓送入 LPCVD 爐管中進行 30nm 之 TEOS oxide 沈積,形成副閘極之閘極 氧化層,如圖 2-7(b)。 4. a. 若是要製作成奈米碳管電晶體之樣品,則先使用 1mg 奈米 碳管與 40ml 之二甲基甲醯胺溶液比例泡好,並且經過 24 小時 超音波震盪。之後再將震盪好的奈米碳管溶液酌量滴在晶圓 上,並且先用 500rpm 轉速旋轉 30sec 將溶液分佈在晶圓上,再 用 4000rpm 之高速旋轉 1 分鐘,將溶液旋乾,留下附著於晶圓 表面之碳管。 b. 若是要製作薄膜電晶體之樣品,則先將晶圓再次經過 RCA clean process 清潔後,送入 LPCVD 爐管中沈積不含雜質之多晶 矽約 60nm。多晶矽沈積完成之後,在利用 Clean Track 與 i-line stepper 進行 Channel 之曝光。曝光完成後再使用 TCP-9400 poly-Si etcher 進行多晶矽之蝕刻,形成一個長條狀之多晶矽通 道(Poly silicon channel)。 5. 當完成奈米碳管之塗佈或是多晶矽之蝕刻之後,我們利用 Clean 20.

(37) Track 與 i-line stepper 進行金屬電極光罩之曝光。曝光完成後,將 樣品送入 Helix sputter 中進行金屬電極之沈積。 a. 若是要沈積鈦金屬電極,則在 4.5mTorr 之 Ar 氣壓下使用 sputter 之 DC gun 承載鈦(Ti)金屬靶並使用 0.4 安培的定電流點 起電漿,而 RF gun 則用以承載鉑(Pt)金屬靶,並用 100W 的定 功率方式點起電漿。最後利用 sputter 機台之 shutter 之開關使 DC gun 先行濺鍍於樣品上 7 分鐘,再關閉 DC gun 之 shutter 以 及打開 RF gun 之 shutter 使金屬濺鍍在樣品上同樣為 7 分鐘。 而得到下層為鈦金屬,上層為鉑金屬之金屬薄膜共約 25nm 厚。 b. 若是要沈積鉑金屬電極,則是在 4.5mTorr 之 Ar 氣壓下使用 sputter 之 DC gun 承載鉭(Ta)金屬靶,並使用 0.06 安培之定電流 方式點起電漿,而 RF gun 則用以承載鉑(Pt)金屬靶,並用 100W 之定功率方式點起電漿。最後將兩個 gun 之 shutter 同時打開進 行共濺鍍(co-sputtering)7 分鐘使表層沈積之金屬層成為鉑鉭合金薄膜。之後將 DC gun 之 shutter 關閉,再進行鉑金屬的 濺鍍 7 分鐘,使上層的金屬為純鉑金屬,完成金屬薄膜之沈積。 6. 將完成金屬薄膜沈積之晶圓,浸泡在丙酮溶液中 5 分鐘,之後 再放入超音波震盪機中進行震盪 10 分鐘,進行 lift-off 製程。將震 盪完成之晶圓取出沖水後,再放入乾淨之丙酮中再震盪 5 分鐘後再 取出沖水,以去除殘留在晶圓表面之金屬碎屑。完成 lift-off 製程之 樣品即完成金屬電極之製作,如圖 2-7(c)。 7. 由於奈米碳管在晶圓表面是隨機分佈,因此,對於奈米碳管電 晶體之樣品,我們使用 In-line SEM(Scanning Electron Microscopy) 針對各個電極之間進行地毯式的搜尋,一旦發現有與金屬電極接觸 之奈米碳管,如圖 2-8,立即標定金屬電極之位置,以便日後之量. 21.

(38) 測。 8. 將找到接觸到金屬電極之奈米碳管電晶體之樣品,或是已完成 金屬電極之薄膜電晶體樣品,送入基板溫度 300C之PECVD(Plasma Enhanced Chemical Vapor Deposition)機台中,通入 10sccm之TEOS 以及 600sccm之O2點起電漿 1 分鐘,使晶圓表面沈積約 50nm之 PECVD二氧化矽薄膜做為金屬電極與鋁閘極之絕緣以及鈍化層 (passivation layer) 。 9. 使用 Clean Track 以及 i-line stepper 進行接觸窗(Contact hole) 光罩曝光。曝光完成後,使用 BOE(Buffered Oxide Etchant)進行接 觸窗蝕刻約 1 分鐘,將接觸窗中的二氧化矽去除,使金屬電極與副 閘極露出。 10. 使用 Thermal Coater 在樣品上蒸鍍 300nm 之鋁薄膜。最後在使 用 Clean Track 與 i-line stepper 進行閘極與 Pad 光罩曝光。最後使用 濕式蝕刻方式蝕刻出鋁閘極以及 pad,即完成整個元件製作,如圖 2-7(d)。. 2-6 元件量測 製作完成之奈米碳管電晶體以及薄膜電晶體,置於室溫下之針測台 (Probe station)下使用 Agilent4156 半導體參數分析儀加以量測其電流與電 壓關係。 元件之低溫電流與電壓量測則是將元件置於高真空之腔體中,將元件降 至低溫(100K 以下)進行或是將元件置於有微探針系統的掃瞄式電子顯微 鏡中進行低溫量測。. 22.

(39) Top gate Source. Drain Carbon nanotube. Subgate. Subgate. 圖 2-1 於源極與汲極下方增加副閘極之奈米碳管電晶體結構。. 圖 2-2 模擬所用之薄膜電晶體結構。. 23.

(40) (a) Al top gate Ti/Pt. PECVD oxide. Ti/Pt. Undoped poly/Carbon nanotube. LPCVD oxide N+(P+). N+(P+). P(N) type substrate. (b). Ti/Pt. Al top gate PECVD oxide. Ti/Pt. Undoped poly/Carbon nanotube Poly Si. LPCVD oxide LPCVD oxide. Poly Si. P(N) type substrate. 圖 2-3 不同副閘極結構之奈米碳管電晶體/薄膜電晶體剖面結構圖: (a)N+/P+ 副閘極 (b)高摻雜之多晶矽副閘極。. 24.

(41) (a). Subgate. Electrode. (b). 0 .1 u m S u b g a te. E le c tr o d e. 圖 2-4 元件之金屬電極與副閘極之佈局圖:(a)設計八個電極與副閘極以增 加製作出奈米碳管電晶體之機會(b)將副閘極延伸出金屬電極 0.1μm 寬度 以克服微影之對準誤差。. 25.

(42) Contact hole. Al top gate. Contact hole. 圖 2-5 在元件兩側分別設計接觸窗,經過蝕刻後,製作鋁 Pad 與鋁閘極, 即完成元件的製作。. 圖 2-6 將元件重複排列以增加晶圓中之元件數目。. 26.

(43) (a) As-(BF2+). Poly Si. As-(BF2+). Poly Si. LPCVD oxide N+(P+). P/N type substrate. N+(P+). P/N type substrate. (b) Poly Si. LPCVD oxide LPCVD oxide. Poly Si. LPCVD oxide N+(P+). P/N type substrate. N+(P+). P/N type substrate. (c) Ti/Pt. Ti/Pt Undoped poly(Carbon nanotube). Poly Si. LPCVD oxide LPCVD oxide. Ti/Pt. Poly Si. Ti/Pt Undoped poly(Carbon nanotube). LPCVD oxide N+(P+). P/N type substrate. N+(P+). P/N type substrate. (d) Ti/Pt. Al top gate PECVD oxide. Ti/Pt. Al top gate. Undoped poly(Carbon nanotube) Poly Si. LPCVD oxide LPCVD oxide. Ti/Pt. Poly Si. PECVD oxide. Ti/Pt. Undoped poly(Carbon nanotube). LPCVD oxide N+(P+). P/N type substrate. N+(P+). P/N type substrate. 圖 2-7 兩種不同副閘極結構之元件製程示意圖。. 27.

(44) 圖 2-8 利用 SEM 尋找有接觸到金屬電極之奈米碳管。. 28.

(45) 第三章 常溫電性模擬結果討論. 3-1 緒論 在本章中,我們使用 ISE TCAD 這套元件模擬軟體模擬薄膜電晶體在 不同金屬電極功函數以及不同副閘極偏壓下的電流與電壓特性,並且由能 帶圖(Band diagram)討論其展現出的電流特性之原因。. 3-2 電極功函數對薄膜電晶體ID-VG特性之影響 圖 3-1 顯示所模擬出將電極功函數設定為 4.5eV與 4.8eV之薄膜電晶體 之ID-VG特性。由圖中我們可以發現:不論金屬電極的功函數為何,電子電 流會隨著閘極電壓的提昇而逐漸增加,而電洞電流會隨著閘極電壓的提昇 而逐漸減少。這是因為當閘極電壓提高時,閘極所產生的電場可以降低通 道中的電子位能而提高通道中的電子濃度而使電子易於導通,但是卻會提 高通道中的電洞位能而減少電洞的濃度因此減少電洞的導通電流。 此外閘極產生的邊緣電場可以影響到一部份的金屬與通道接觸面上的 蕭基位障,進而減少蕭基位障的寬度,使得電子容易利用穿隧效應穿過蕭 基位障,產生穿隧電流。但是因為大部分閘極產生的電場會被源極與汲極 電極所遮蔽,並不能有效的影響蕭基位障的寬度,因此即使在電子或是電 洞電流導通的狀態下,仍然可以看出電流有受到壓抑的狀況。 而當我們比較使用不同電極功函數的薄膜電晶體的ID-VG特性,我們也 發現電極功函數設定為 4.5eV之薄膜電晶體在正閘極電壓時的導通電流會 比在負閘極電壓下的電洞導通電流來的大,使得薄膜電晶體整體之ID-VG特 29.

(46) 性會比較偏向N-type,而反之,當電極功函數為 4.8eV時,其ID-VG特性會比 較偏向P-type。 這是因為當電極功函數較小時,在正閘極電壓下,電子所看到之金屬 與半導體之接觸面上的蕭基位障高度較低,所以電子可以利用熱游離發射 (Thermionic emission)機制越過蕭基位障進入通道中,而產生導通電流。而 且所看到的蕭基位障厚度也會比較薄,而有較大的穿隧電流。而當施加負 閘極電壓時,因為電洞看到的蕭基位障高度較高,因此電洞不易利用熱游 離發射方式進入通道中且所看到的蕭基位障較厚,因此也不易產生穿隧電 流,而使得導通電流降低,所以電極功函數較低的薄膜電晶體有較大的電 子電流與較小的電洞電流,形成類似 N-type 的特性,如圖 3-2(a)。反之, 當電極功函數較高時,薄膜電晶體在正閘極電壓下有較小的電子電流而在 負閘極電壓下有較大的電洞電流,形成類似 P-type 的電流特性。如圖 3-2(b)。. 3-3 電極功函數對薄膜電晶體ID-VD特性之影響 圖 3-3 顯示電極功函數為 4.5eV與 4.8eV之薄膜電晶體結構所模擬出的 ID-VD特性。由圖中可以發現當金屬電極功函數較低時,電晶體在正閘極電 壓下的導通電流較大,且會隨著汲極電壓的增加而逐漸達到飽和。而負閘 極電壓下的導通電流較小,但是卻會隨著汲極電壓的增加而呈現對數形式 的增加,而不會達到飽和。而較高金屬電極功函數之薄膜電晶體則有相反 的結果,而且當汲極電壓提高時,正閘極電壓下的電流最後仍然會出現對 數形式增加的現象。 當施加正閘極電壓時,電流之所以隨著汲極電壓提昇而增加是因為汲 極端對於電子的蕭基位障隨著汲極電壓的提昇而降低,如圖 3-4(a),因此使 得能夠越過汲極端的蕭基位障的電子愈來愈多,而導致電流逐漸增加。當 汲極端的蕭基位障隨著增加的汲極電壓而完全消失後,汲極電壓的提昇便 30.

(47) 無法對電子導通電流有明顯的幫助,因此導通電流便呈現飽和的狀態。 若是汲極電壓再繼續增加時,汲極端價帶(Valance band)會逐漸彎曲, 使電洞看到的蕭基位障逐漸變薄,電洞的穿隧電流開始出現,如圖 3-4(b)。 因此,當汲極電壓持續增加時,即使是在閘極施加正電壓,仍然可以看到 電流飽和後又再度的隨著汲極電壓的提昇而增加,這個再度增加的電流與 汲極電壓是一個指數的關係。 但是當施加負電壓於閘極上時,因為汲極端對於電洞的蕭基位障會隨 著汲極電壓的提昇而逐漸變薄,使得電洞的穿隧電流逐漸增加,如圖 3-4(c)。而蕭基位障的穿隧電流與蕭基位障之厚度為指數關係,因此導通電 流會隨著汲極電壓的增加而呈現指數形式的上升。又因為除非施加很大的 電壓使得蕭基位障的厚度變得極薄,否則蕭基位障並不會隨著汲極電壓的 提昇而完全消失,因此導通電流並不會隨著汲極電壓提昇而達到飽和。. 3-4 副閘極電壓對薄膜電晶體ID-VG特性之影響 圖 3-5 顯示在不同的副閘極偏壓下,電極功函數 4.5eV與 4.8eV之薄膜 電晶體所模擬出之ID-VG特性。由圖中可以發現,當副閘極施加負電壓時, 不論電極功函數為 4.5eV或是 4.8eV之薄膜電晶體之ID-VG特性中,施加正閘 極電壓時的導通電流均會下降,而負閘極電壓下的導通電流均會上升,反 之亦然。 我們將不同副閘極偏壓下的薄膜電晶體的能帶圖畫出,可以發現當副 閘極施加負電壓時,源極與汲極端的多晶矽的電子位能會被提升,使得介 面上的蕭基位障變的比較厚,因而阻止了電子的穿隧效應,使得正閘極電 壓下的電子導通電流減少。但是所施加的電場卻使得電洞所看到的蕭基位 障變薄,而增加負閘極電壓下電洞的穿隧電流,而使得導通電流增加,如 圖 3-6(a)。反之,當副閘極施加正電壓時,會使得電子所看到蕭基位障變薄, 31.

(48) 但會是電洞看到的蕭基位障變厚,如圖 3-6(b),使得電子電流增加和電洞電 流減少。. 3-5 副閘極電壓對薄膜電晶體ID-VD特性之影響 圖 3-7 為不同副閘極電壓下,不同的金屬電極功函數所模擬出的ID-VD 圖。圖中顯示當副閘極施加正電壓時,可以有效的提昇在正閘極電壓下的 導通電流,並壓抑負極電壓下的電流,反之亦然。 這也是因為副閘極的電壓可以有效的減少或是增加金屬電極與半導體 之接面上的蕭基位障的厚薄,進而影響導通電流的大小。 此外由於副閘極並不能影響蕭基位障的高度,因此對於正閘極電壓下 的導通電流進入飽和區的位置,並沒有明顯的影響。但是由於施加負電壓 的副閘極會壓縮汲極端的蕭基位障,因此當閘極施加正電壓時,因為汲極 電壓提高而產生的電洞穿隧電流會較大,產生如圖 3-7(b)圖中所顯示的當汲 極電壓較大時,副閘極為-5V 下的電流比 0V 下的電流為大的現象。. 3-6 源極端副閘極電壓對基板電壓調變電流之影響 而我們由前面的ID-VD特性模擬結果可以知道,當閘極施加正電壓而汲 極的電壓逐漸增加時,所流過的電流主要是因為汲極端的蕭基位障高度減 少而增加,當汲極端的蕭基位障因為汲極電壓的提高而消失時,導通電流 會出現飽和的現象,此時若是可以將源極端的蕭基位障加以改變,因為影 響導通電流的唯一位障只剩下源極端的蕭基位障,所以該蕭基位障的厚薄 或是高度會對電流有相當大的影響,如圖 3-8(a)。 但是當閘極為負電壓時的導通電流主要是同時受到源極與汲極端的兩 個蕭基位障影響,若是我們只改變源極端的蕭基位障,對於電流的影響將 不會很明顯,如圖 3-8(b)。 32.

(49) 為了避免上閘極的電壓產生邊緣電場對蕭基位障產生調變,我們改用 基板(substrate)來當作閘極施加電壓。由於副閘極的存在,因此基板電壓 所產生的電場在源極與汲極附近都會被副閘極所遮蔽,因此基板電壓對於 源極與汲極的蕭基位障不會產生調變的效果。 此外,因為當汲極施加負電壓時的元件能帶圖會變得與汲極施加正電 壓但是閘極電壓相反的時候相同。所以我們除了模擬正汲極電壓的狀態, 也一併模擬了負汲極電壓的情況。模擬的結果如圖 3-9 所示: 由圖中我們可以發現當基板電壓為 5V 時,源極端的副閘極電壓對於 正汲極電壓時的導通電流有相當大的影響,但是對於負汲極電壓時的電流 影響較少,反之,當基板電壓為-5V 時,源極端副閘極的電壓對負的汲極電 壓下的導通電流有較大的影響,而對正汲極電壓時的導通電流幾乎沒有影 響。. 3-7 小結 由以上的模擬結果,我們可以預測蕭基位障元件的特性:當使用不同 金屬材料當作電極時,由於所形成的蕭基位障的位障高度不同,所以會出 現偏向N-type與P-type的雙極性特性。而其ID-VD特性,在正閘極電壓下的導 通電流會因為蕭基位障的降低而隨著汲極電壓逐漸增加最後達到飽和。但 是負閘極電壓下的導通電流則是因為汲極電壓的增加而使得蕭基位障逐漸 變薄而出現與汲極電壓成指數關係增加的電流。 而當我們在副閘極施加正電壓時,因為可以壓縮電子所看到的蕭基位 障寬度,並增加電洞所看到蕭基位障寬度,所以可以增加正閘極電壓下的 電子電流,並且壓抑負閘極電壓下的電洞電流。反之,當副閘極施加負電 壓時,則可以壓抑電子電流,並增加電洞電流。 此外,當改用基板來調變電流時,因為基板產生的電場會受到副閘極 33.

(50) 遮蔽,因此,當基板施加正電壓時,在正汲極電壓下的導通電流因為只有 受到源極端的蕭基位障影響,所以源極端副閘極的電壓會對電流有相當大 的影響。而負汲極電壓下的電流因為同時受到兩個蕭基位障的影響,所以 源極端的副閘極電壓對電流的影響較小,反之亦然。. 34.

(51) ID(nA). (a) 1E4 1E3 100 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 1E-7 1E-8 1E-9 -6. Electron Current Hole Current Total Current. -4. -2. 0. 2. 4. 6. VG(V). ID(nA). (b) 1E6 1E5 1E4 1E3 100 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 1E-7 1E-8 1E-9 1E-10 -6. Electron Current Hole Current Total Current. -4. -2. 0. 2. 4. 6. VG(V). 圖 3-1 不同電極功函數模擬之薄膜電晶體ID-VG特性模擬結果。(a)功函數為 4.5eV之ID-VG特性模擬結果 (b)功函數為 4.8eV之ID-VG特性模擬結果。. 35.

(52) (a). (b). 圖 3-2 不同金屬電極功函數造成不同的蕭基位障高度:(a)較低的金屬功函 數造成電子的蕭基位障較低且較薄以及電洞的蕭基位障較高且較厚,而有 較大的電子電流,和較小的電洞電流。(b) 較高的金屬功函數造成電子的蕭 基位障較高且較厚以及電洞的蕭基位障較低且較薄,而有較小的電子電 流,和較大的電洞電流。. 36.

(53) (a) 3. 8.0x10. VG=5V VG=2.5V VG=0V VG=-2.5V VG=-5V. 3. ID(nA). 6.0x10. 3. 4.0x10. 3. 2.0x10. 0.0 0. 1. 2. 3. 4. 5. 3. 4. 5. VD(V). (b) VG=5V VG=2.5V VG=0V VG=-2.5V VG=-5V. 5. 1.2x10. 5. 1.0x10. 4. ID(nA). 8.0x10. 4. 6.0x10. 4. 4.0x10. 4. 2.0x10. 0.0 0. 1. 2. VD(V). 圖 3-3 不同金屬電極功函數模擬之薄膜電晶體ID-VD特性模擬結果。(a)功函 數為 4.5eV之不同閘極電壓下的ID-VD特性模擬結果 (b)功函數為 4.8eV之不 同閘極電壓下的ID-VD特性模擬結果。 37.

(54) (a). VD=0V. VD=1V. VD=0V. VD=1V. (b). (c). 圖 3-4 不同閘極電壓下,當汲極電壓增加時,電晶體的能帶圖:(a)閘極施 加正電壓時,電流隨著汲極的蕭基位障減少而增加,最後達到飽和 (b)當汲 極電壓很大時,會產生電洞穿隧電流,使得飽和電流再次增加(c)當閘極施 加負電壓時,汲極電壓的增加會使的電洞穿隧電流隨之增加。. 38.

(55) (a) 1E6 1E5 1E4 1E3 100. Vsubgate=5V VD=1V Vsubgate=2.5V Vsubgate=0V Vsubgate=-2.5V Vsubgate=-5V. ID(nA). 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 -6. -4. -2. 0. 2. 4. 6. VG(V). (b) 1E5. Vsubgate=5V Vsubgate=2.5V Vsubgate=0V Vsubgate=-2.5V Vsubgate=-5V. VD=1V. 1E4 1E3 100. ID(nA). 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 -6. -4. -2. 0. 2. 4. 6. VG(V). 圖 3-5 不同的副閘極電壓對不同的金屬電極功函數之薄膜電晶體之ID-VG特 性模擬結果:(a)金屬電極功函數為 4.5eV之薄膜電晶體模擬結果 (b)金屬電 極功函數為 4.8eV之薄膜電晶體模擬結果。 39.

(56) (a). (b). 圖 3-6 當副閘極施加不同電壓時,會造成電子與電洞在金屬與半導體介面 上的蕭基位障的厚度改變:(a)副閘極施加負電壓時,使的電子看到的蕭基 位障變厚,但使得電洞看到的蕭基位障變薄。(b) 副閘極施加正電壓時,使 的電子看到的蕭基位障變薄,但使得電洞看到的蕭基位障變厚。. 40.

(57) (a) 4. 4. 3.5x10. 4. 3.0x10. 3.5x10. Vsubgate=5V Vsubgate=0V Vsubgate=-5V VG=5V. 4. 3.0x10. 4. 4. 2.5x10. 4. 2.0x10. 2.5x10. Vsubgate=5V Vsubgate=0V Vsubgate=-5V VG=-5V. ID(nA). ID(nA). 4. 2.0x10. 4. 1.5x10. 4. 1.5x10. 4. 4. 1.0x10. 3. 5.0x10. 1.0x10. 3. 5.0x10. 0.0. 0.0 0. 1. 2. 3. 4. 5. 0. 1. 2. VD(V). 3. 4. 5. 3. 4. 5. VD(V). (b) 3. 1.2x10. 3. 1.0x10. Vsubgate=5V Vsubgate=0V Vsubgate=-5V VG=5V. 5. 1.4x10. 5. 1.2x10. 2. 5. 1.0x10. ID(nA). 8.0x10. ID(nA). Vsubgate=5V Vsubgate=0V Vsubgate=-5V VG=-5V. 2. 6.0x10. 4. 8.0x10. 4. 6.0x10. 2. 4.0x10. 4. 4.0x10 2. 2.0x10. 4. 2.0x10. 0.0. 0.0 0. 1. 2. 3. 4. 5. 0. VD(V). 1. 2. VD(V). 圖 3-7 不同的副閘極電壓對不同的金屬電極功函數之薄膜電晶體的ID-VD特 性影響模擬結果:(a)金屬電極功函數為 4.5eV之薄膜電晶體模擬結果(b) 金 屬電極功函數為 4.8eV之薄膜電晶體模擬結果。. 41.

(58) (a). (b). 圖 3-8 不同的源極端的蕭基位障對於導通電流的影響:(a)正閘極電壓時, 對導通電流有明顯影響(b)負閘極電壓時,對導通電流的影響較小。. 42.

(59) ID(nA). (a) 1E9 1E8 1E7 1E6 1E5 1E4 1E3 100 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 1E-7 1E-8 1E-9 1E-10. Vsubgate,source=5V Vsubgate,source=0V Vsubgate,source=-5V Vsubstrate=5V. -5. -4. -3. -2. -1. 0. 1. 2. 3. 4. 5. 3. 4. 5. VD(V). ID(nA). (b) 1E9 1E8 1E7 1E6 1E5 1E4 1E3 100 10 1 0.1 0.01 1E-3 1E-4 1E-5 1E-6 1E-7 1E-8 1E-9 1E-10 1E-11 1E-12 1E-13 1E-14. Vsubgate,source=5V Vsubgate,source=0V Vsubgate,source=-5V Vsubstrate=-5V. -5. -4. -3. -2. -1. 0. 1. 2. VD(V). 圖 3-9 不同基板電壓下,源極端副閘極電壓對於導通電流的影響模擬結 果:(a)基板電壓為 5V 模擬結果(b)基板電壓為-5V 模擬結果。. 43.

(60) 第四章 常溫元件量測結果與討論. 4-1 緒論 在本章中,我們實作出N+/P+副閘極與多晶矽副閘極的奈米碳管電晶體 與薄膜電晶體。我們首先量測不同的副閘極結構是否會對於電晶體的特性 有不同的影響,之後將所量測得到的電性與前一章模擬的電性結果相互對 照,並解釋其中的相同點與差異點之原因。. 4-2 副閘極結構對電性與製程之影響 我們實作出具有N+/P+ 副閘極結構之薄膜電晶體以及具有多晶矽副閘 極之薄膜電晶體。我們分別對N+副閘極與P+副閘極分別施加正電壓與負電 P. 壓之後,量測副閘極電壓對於薄膜電晶體的ID-VG電性之影響,如圖 4-1。 我們在施加相同的電壓在多晶矽副閘極上,量測多晶矽副閘極之電壓對於 薄膜電晶體的ID-VG特性的影響,如圖 4-2。 由圖 4-1 與圖 4-2 之ID-VG圖中可以發現,雖然我們所使用的副閘極結 構並不相同,但是對於薄膜電晶體的ID-VG特性的影響是類似的。當副閘極 施加正電壓時,同樣都會壓抑施加負閘極電壓時的電洞導通電流,並且提 昇施加正閘極電壓時的電子導通電流。 但是因為N+/P+ 副閘極必須維持副閘極的電壓在正電壓或是負電壓以 免PN junction進入順偏狀態而使得通道下方的基板電壓受到副閘極電壓的 影響,所以在元件樣品的量測上便會受到限制,而且我們必須製作兩倍數 目的樣品才能與多晶矽副閘極樣品一樣在副閘極施加正與負的電壓,因 44.

(61) 此,我們後面的元件製作,均只製作多晶矽副閘極的元件樣品,以簡化實 作與量測上的負擔。 此外,原先認為多晶矽副閘極會對奈米碳管的旋塗造成不利的影響, 但是實際進行製程時,發現多晶矽副閘極造成之表面凹凸,反而可以有效 的使奈米碳管停留在電極的區域而提高發現接觸到金屬電極之奈米碳管的 數目,因此,奈米碳管電晶體之副閘極也只使用多晶矽副閘極之結構。. 4-3 金屬電極材料對薄膜電晶體與奈米碳管電晶體ID-VG 特性之影響 我們使用鈦金屬以及鉑金屬來製作薄膜電晶體之電極,並量測其ID-VG 特性,如圖 4-3。我們從兩圖中可以發現薄膜電晶體,在不施加副閘極電壓 的狀況下,都會與前一章中的模擬結果相似:在正閘極電壓與負閘極電壓 時,都會因為源極與汲極端接面上的蕭基位障的寬度受到閘極電壓的邊緣 電場壓縮,因而出現導通電流,呈現雙極性(ambipolar)的特性。 當我們使用鈦當作金屬電極時,因為鈦的功函數大約在 4.32eV 左右, 比起矽的功函數 4.52eV 都要來的小,所以當鈦與未摻雜的多晶矽或是奈米 碳管接觸時,電子所看到的蕭基位障高度會比電洞所看到的蕭基位障高度 低,使得正閘極電壓時電子的導通電流會比負閘極電壓時的電洞導通電流 大,而應該與前一章中使用 4.5eV 作為電極功函數所模擬出的結果類似, 形成偏向 N-type 雙極性特性。但是當我們實際製作鈦金屬電極之奈米碳管 電晶體與薄膜電晶體時,在金屬與奈米碳管或多晶矽的接觸面上會存在有 許多的介面態(interface state),這些介面態會影響真正的金屬與半導體形 成蕭基位障時的位障高度。由文獻可知,實際量測到的鈦金屬對於 N-type Silicon 之位障高度為 0.5eV,而對於 P-type Silicon 之位障高度為 0.61eV, 僅僅只有 0.11eV 之差距[41]。因此,我們只能發現在正閘極電壓下的電子 45.

(62) 導通電流比起負閘極電壓下的電洞導通電流略高一點。 當我們改用鉑當作金屬電極時,鉑的功函數為 5.65eV,比矽的功函數 高,且文獻中所量測到鉑金屬與 N-type Silicon 之位障高度為 0.9eV[41],因 此電子會看到比電洞高的蕭基位障,而使得正閘極電壓下的電子導通電流 較小,因而使電晶體的特性與前一章中使用 4.8eV 當作電極功函數的模擬 結果相似,而偏向 P-type 特性。 我們再使用鈦金屬以及鉑金屬來製作奈米碳管電晶體之電極,並量測 其ID-VG特性。但是與薄膜電晶體不同的是,因為我們所使用的奈米碳管是 使用雷射熱融法所製造的,奈米碳管本身的旋度(Chiral angle) 、直徑、甚 至長度並不固定,因此不能有效的確定奈米碳管的功函數與能隙 (Bandgap),所以我們在量測上,必須先用電性量測所製造出的奈米碳管 電晶體才能確定奈米碳管的特性。 因此,我們大量的量測所找到的奈米碳管電晶體元件,並且將所量測 得到的元件特性加以分類並統計。在使用鈦金屬電極之奈米碳管電晶體元 件中,我們剔除掉調變能力差的元件之後,可以量測到如圖 4-4 的ID-VG特 性。幾乎所有調變能力佳的奈米碳管電晶體都會顯示如圖 4-4 中的雙極性特 性,但是不同的元件會有正閘極電壓或是負閘極電壓下的導通電流略大的 特性。 我們推測,這是因為使用的奈米碳管之功函數大約與鈦金屬的功函數 相近,所以會出現雙極性的電流特性。但是奈米碳管的功函數會隨著其旋 度而有些微差異,因此造成其正負閘極下的導通電流有所差異的現象。 而在使用鉑金屬的奈米碳管電晶體中,我們剔除掉沒有調變能力的元 件之後,可以量測到如圖 4-5 的元件特性。 絕大多數使用鉑金屬電極之奈米碳管電晶體的ID-VG 特性是屬於圖 4-5(a)中的P-type特性。只有在負閘極電壓下有較大的導通電流,而正閘極. 46.

(63) 電壓下只有少許的電流增加的現象。這是因為鉑金屬的功函數為 5.65eV, 我們所使用的奈米碳管功函數要大的多,因此即使是在正閘極電壓下,電 子所看到的蕭基位障高度很高,不易透過熱游離發射機制越過蕭基位障, 只能靠較大的閘極電壓時的邊緣電場壓抑蕭基位障的厚度後,再利用穿隧 效應進入奈米碳管產生導通電流,因此在正閘極時的電子電流便會比較 小。但是電洞所看到的蕭基位障高度小的多,所以可以輕易的利用熱游離 發射方式越過蕭基位障而進入奈米碳管中而在負閘極電壓時產生導通電 流。 而除了大部分出現 P-type 特性的鉑金屬電極的奈米碳管外,有很少數 的樣品會出現如圖 4-5(b)的 N-type 特性。 我們推測這是因為奈米碳管接觸到了我們用來增加鉑金屬附著力時所 摻入的鉭金屬。鉭的功函數僅僅只有 4.25eV,比起鉑金屬或是鈦金屬要來 的更小,因此,當使用鉭金屬與奈米碳管接觸時,所產生的蕭基位障便會 使得元件的特性偏向 N-type。. 4-4 金屬電極材料對薄膜電晶體與奈米碳管電晶體ID-VD特 性之影響 圖 4-6 與圖 4-7 是分別使用鈦金屬與鉑金屬來製作金屬電極之薄膜電 晶體與奈米碳管電晶體的ID-VD特性。 我們由圖中可以看出當使用鈦金屬當作電極時的薄膜電晶體與奈米碳 管電晶體都與前一章中使用 4.5eV當作電極功函數的模擬結果類似。在正閘 極電壓下的導通電流都會隨著汲極電壓的提昇而出現飽和的現象,而負閘 極電壓下的導通電流都會出現與汲極電壓成指數關係增加的現象。而當使 用鉑金屬當作金屬電極時,所量測到的ID-VD特性,則與前一章中使用 4.8eV 作為電極功函數所模擬出的結果相近。 47.

(64) 因此,由前一章的模擬結果我們可以推論奈米碳管電晶體與薄膜電晶體 都會受到蕭基位障的控制而影響其電流的導通特性。. 4-5 副閘極電壓對奈米碳管電晶體與薄膜電晶體ID-VG特 性之影響 我們接著在副閘極上施加不同的電壓,觀察不同的副閘極電壓對於薄 膜電晶體與奈米碳管電晶體之ID-VG 特性是否會有如同模擬時所顯示的影 響。 圖 4-8 則是使用鈦金屬與鉑金屬作為金屬電極的薄膜電晶體受到不同 副閘極電壓影響後的ID-VG特性。圖 4-9 是使用有偏向N-type的雙極性特性 的鈦金屬電極之奈米碳管電晶體與展現出P-type特性的鉑金屬電極奈米碳 管電晶體受到+5V與-5V之副閘極電壓影響後的ID-VG特性。 由圖中我們可以發現薄膜電晶體與奈米碳管電晶體同樣展現出會受到 正的副閘極電壓影響而壓抑負閘極電壓時的電洞導通電流並且提昇正閘極 電壓時的電子導通電流,反之亦然。 這樣的實驗結果與前一章模擬結果有相同的趨勢。但是奈米碳管電晶 體所受到副閘極電壓的影響遠比薄膜電晶體要來的小,我們推測這是因為 奈米碳管是一個接近一維的結構(1D structure) ,絕大部分的碳管表面與金 屬電極直接接觸,能夠讓副閘極電場進入碳管進而影響到蕭基接面電位的 開口極小,所以接觸面上的蕭基位障比較不易受到副閘極電壓的影響而改 變其厚薄。 為了驗證上面的推論,我們再度的使用 ISE TCAD 元件模擬軟體來模 擬不同大小的矽通道對於副閘極電壓的影響。圖 4-8 是我們所用來模擬的元 件結構,圖 4-10(a)是一個矽通道為 50nm 厚 1μm 寬的薄膜電晶體位於汲極. 48.

數據

![圖 1-8 將奈米碳管置於真空中進行退火,可以將奈米碳管電晶體由 P-type 特性轉變成 N-type 特性[29]。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8707849.199825/29.892.261.678.545.913/將奈碳管置於真空中進行退火可以將奈米碳管電晶體由特性轉變特性.webp)

![圖 1-9 利用鉀蒸汽使鉀吸附於奈米碳管上,可以將 P-type 特性之奈米碳管 轉並成 N-type 特性[29]。 (a) (b) 圖 1-10 使用一較高功函數之金屬與奈米碳管接觸時,由於較高的電子蕭基 位障,因此會產生 P-type 之特性:(a)正閘極電壓時,電子看到較大蕭基位 障,因此無電流傳導 (b)負閘極電壓時,電洞看到較小的蕭基位障,因 此可以穿過蕭基位障,使電晶體導](https://thumb-ap.123doks.com/thumbv2/9libinfo/8707849.199825/30.892.255.680.113.447/圖位障因此會產之特性正閘極電壓時電子看到較大蕭基此無體導.webp)

![圖 1-11 使用功函數位在能隙中央之金屬與奈米碳管接觸時,不論是給予正 或負的閘極電壓,載子所看到的蕭基位障皆小,所以可以導通[33]。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8707849.199825/31.892.135.748.119.395/碳管接觸時不論是給予或負閘極電壓載子所看蕭基位障皆小所以可以.webp)

+7

Outline

相關文件

→一般常用的矽源材料氣體 (Silicon Source Gases)是矽烷(SiH 4 )、二氯矽烷(DCS,Si H 2 Cl 2 ) 、三氯矽烷(TCS,SiHCl 3 ).. 了解 磊晶 磊晶 磊晶 磊晶

• 雙極性電晶體 (bipolar junction transistor , BJ T) 依結構區分,有 npn 型及 pnp 型兩種. Base

• 雙極性電晶體 (bipolar junction transistor , BJ T) 依結構區分,有 npn 型及 pnp 型兩種. Base

802.14為主流,參與成員多為電腦及電話 公司,協定的主體已經確立,預計在今年 十一月完成標準草案的制定,1998年六月 正式成為IEEE標準。基本上來說,IEEE 802.14受到四個標準單位影響:

• 接續之前的例子,若原為 0.288 pF 的液晶 電容 C LC ,再並聯一個亦為 0.288 pF 的電 容C st ,則電位保持的變化值為.

在1980年代,非晶矽是唯一商業化的薄膜型太 陽能電池材料。非晶矽的優點在於對於可見光

受試者包括了54 名便秘型大腸激躁症患者以及16 名健康者,共70 位,平均年齡28 .4歲,其中IBSC

魚油 + 運動 魚油 紅花油 豬油 對生理的影響 左心室收縮壓、.