第四章 實驗平台設計與系統測試

本章主要介紹 ARM CPU 指令模擬測試與實驗平台規劃、系統 測試,ARM CPU 測試流程為:先將 ARM CPU 設計完畢後,利用 Xilinx ISE 設 計 軟 體 與 模 擬 工 具 Model Sim 來 進 行 Function Simulation 的測試(ARM CPU 指令模擬測試),確認所有功能皆已 達到設計者的需求,再進行 Implementation 動作,最後下載燒錄於 實驗平台,透過實驗平台周邊 I/O 裝置與測試程式(例如:24 小時時 間計數程式、計算機..等應用程式),對整個 ARM CPU 系統執行完 整測試。

本章共分為三節,第一節是介紹 ARM CPU 指令模擬測試,ARM CPU 的每道指令都有詳細測試過,在此只挑選每種指令中最常用的 指令作為測試範例,第二節介紹實驗平台之規劃,第三節介紹整個 ARM CPU 系統測試,則選用比較易觀測的 24 小時時間計數器測試 程式,作為測試範例。

第一節 ARM CPU 指令模擬測試

建立 ARM_TEST.coe 檔並將欲測試程式編輯成 16 進制的機械 碼輸入,在開啟 Xilinx ISE Core Generator,將 ARM_TEST.coe 載入 ARM CPU 的 Memory 中,使用 Model Sim 來進行 Function Simulation 的測試,確認各種指令的功能正確與否。

一、Signal Data Transfer(LDR/STR)指令測試

LDR 指令是將所指定的記憶體位址的資料,載入 Rd 暫存器中,

STR 指令將 Rd 暫存器中的值儲存到指定的記憶體位址中,測試程 式如表 4-1 所示,軟體模擬結果如圖 4-1 所示:

表 4-1 LDR/STR 指令測試程式

Program Memory Address Machine Code Action MOV R0,#20 00 E3A00014 R0=14 MOV R1,#30 04 E3A0101E R1=1E

STR R0[R0,#12] 08 E5A0000C MEM[20]=R0 LDR R3[R1,#2] 0C E5B13002 R3=14

圖 4-1 中所表示的是經過表 4-1 LDR/STR 指令測試程式最後一道指 令之結果, 第一道指令是將 R0 放入立即值 0x14,第二道指令將 R1 放 入立即值 0x1E,第三道指令將 R0 的值(R0=0x14)存入記憶體 0x20

(0x20=R0+#0x0c)的位址中,最後一道指令為 LDR R3[R1,#2],是到 記憶體 0x20 (0x20=R1+0x02)的位址,將位址中的資料 0x14 存入 R3 暫 存器。

圖 4-1 Signal Data Transfer(LDR/STR)指令測試結 LDR R3 [R1,#02]

(E5B13002)

R1=0000001E R1+#02=00000020 R3=00000014

二、Multiple Register Transfer Instruction(LDM/STM)指令測試

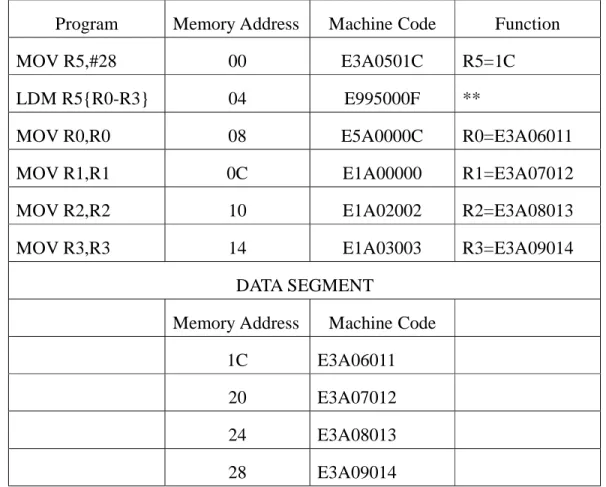

LDM/STM 指令功能是用來做暫存器與記憶體間多筆資料的存 取功能,LDM 指令在一個指令下從記憶體載入多筆資料到暫存器 中,STM 指令可以將多個暫存器資料在一個指令下寫入記憶體,測 試程式如表 4-2 所示,測試程式如圖 4-2、圖 4-3 所示:

表 4-2 Multiple Register Transfer Instruction(LDM/STM)測試程式

Program Memory Address Machine Code Function MOV R5,#28 00 E3A0501C R5=1C LDM R5{R0-R3} 04 E995000F **

MOV R0,R0 08 E5A0000C R0=E3A06011 MOV R1,R1 0C E1A00000 R1=E3A07012 MOV R2,R2 10 E1A02002 R2=E3A08013 MOV R3,R3 14 E1A03003 R3=E3A09014

DATA SEGMENT

Memory Address Machine Code 1C E3A06011

20 E3A07012 24 E3A08013 28 E3A09014

圖 4-2 所表示為執行 LDM R5{R0-R3}這道指令後 R0~R3 中的值,如 下所示:

**LDM R5{R0-R3}:

(i)R0=*R5(R5=0000001C) = E3A06011

(此時 R5=0000001C,將 Memory Address 0000001C 中的值存入 R0)

(ii) R1={*(R5+04)=00000020} = E3A07012

(此時將 R5+04=00000020,將 Memory Address 00000020 中的值存入 R1) (iii) R2={*(R5+08)=00000024} = E3A08013

(此時將 R5+08=00000024,將 Memory Address 00000024 中的值存入 R2) (iv)R3={*(R5+12)=00000028} = E3A0901

(此時將 R5+12=00000028,將 Memory Address 00000028 中的值存入 R3)

圖 4-3 所示為經過 LDM R5{R0-R3}指令後,利用 mov 指令觀察將 R0~R3 的值是否正確。

- 55 -

圖 4-2 Multiple Register Transfer Instruction(LDM/STM)指令測試結果

LDM R5{R0-R3}

(E995000F)

01C:E3A06011 020:E3A07012 024:E3A08013 028:E3A09014

圖 4-3 Multiple Register Transfer Instruction(LDM/STM)指令測試結果 R0=E3A06011

M OV R0,R0 (E1A00000)

M OV R1,R1 (E1A01001)

M OV R2,R2 (E1A02002)

MOV R3,R3 (E1A03003) R3=E3A09014 R2=E3A08013

R1=E3A07012

二、Branch(B/BL)指令測試

B(Branch)指令是用來改變指令執行順序的一道指令,也就是用 來改變目前程式計數器(PC)的值,將運算完新的 PC 值存入 R15(PC)

中,測試程式如表 4-3 所示,測試結果如圖 4-4 所示:

表 4-3 Branch 指令測試程式

Program Memory Address Machine Code Function ADD R0,R0,#01 00 E2800001 R0=01

B 0x00 04 EA000000 Branch to 0x00

圖 4-4 所式為經過表 4-3Branch 指令測試程式後的結果,第一道指令是 將 R0 加上立即值 0x01 放入 R0 中,第二道指令為 Branch 到 0x00 的位 址讓程式重新執行。

三、Swap memory and Register Instructions(SWP)指令測試

SWP 主要功能是將暫存器的資料與記憶體的資料作交換,將 Rn 所 對應的記憶體位址中的資料存入 Rd,再將 Rn 中的資料存入 Rm 中,測 試程式如表 4-4 所示,測試結果如圖 4-5 所示:

表 4-4 SWP 指令測試程式

Program Memory Address Machine Code Function MOV R2,#0C 00 E3A0200C R2=0C SWP R0,R1[R2] 04 E1001092 R0= [R2]

R1=R2 DATA SEGMENT

0C E3A0501C

圖 4-5 所示為執行表 4-4 SWP 指令測試程式的最後結果,第一道指 令先將 R2 放入立即值 0x0C,第二道指令動作為先將到記憶體中將 0x0C (R2=0x0C)位址中的資料(E3A0501C)存入 R0 中,再將 R2 的值(R2=0x0C) 存入 R1 中,此時最後的結果為:

R0=E3A0501C, R1=0000000C

- 59 -

圖 4-4 Branch 指令測試測試結果 ADD R0,R0,#01

(E2800001)

R0=00000001

B 0x00 (EA000000) B 0x00

(EA000000)

PC = 00

圖 4-5 SWP 指令測試結果

SWP R0,R1[R2]

(E1001092) R0=E3A0501C R1=0000000C

四、Data Processing 指令測試

Data Processing 指令主要執行一個或兩個運算元作指定的算術或邏 輯運算,來獲得一個結果並將運算完的結果存入目的暫存器(Rd)中,

測試程式如表 4-5、表 4-6 所示,測試結果如圖 4-6、圖 4-7、圖 4-8 所 示:

表 4-5 Data Processing 指令測試程式 1

Program Memory Address

Machine Code Function

MOV R0,#15 00 E3A0000F R0=15 MOV R1,#3 04 E3A01003 R1=03 MOV R2,#5 08 E3A02005 R2=05

MUL R3,R2,R1 0C E0030192 R3=15(R1*R2) MLA R3,R2,R1,R0 10 E0203192 R3=30(R1*R1+R0) UMULL R3,R2,R1,R0 14 E0832091 R3=00, R2=45

(R1*R2)= R3 R2

表 4-5 Data Process 指令測試程式 1(乘法指令測試)後的結果,經 過 前 三 道 指 令 後 R0=0x15 、 R1=0x03 、 R2= 0x05 , 第 四 道 指 令 後 R3=15(R1*R2)(圖 4-6 所示),第五道指令後 R3=30(R1*R1+R0)(圖 4-6 所示),第六道指令執行後(R1*R2)= R3 R2,R3=00, R2=45 (圖 4-7 所 示)。

表 4-6 Data Processing 指令測試程式 2

Program Memory Address

Machine Code Function

MOV R0,#01 00 E3A00001 R0=01 MOV R1,#03 04 E3A01003 R1=03 MOV R2,#05 08 E3A02005 R2=05 ADD R3,R1,R0 0C E0813000 R3=04

ADD R3,R2,R1,LSL #3 10 E0823181 R3=29 (R1+R2) R1=24 (LSL #3)

圖 4-8 所示為執行表 4-6 Data Processing 指令測試程式 2 後的結果,經 過前三道指令後 R0=0x01,R1=0x03,R2=0x05,經過第四道指令後 R3=0x04(R0+R1),第五道指令的動作為將先 R1 左移 3bits 後(R1=24 ),

再將 R1 與 R2 作相加存入 R3 中(R3=29 (R1+R2))。

- 63 -

圖 4-6 Data Processing 指令測試 1 結果

MUL R3,R2,R1 (E0030192)

R0=15 R1=03 R2=05

R3=15 MLA R3,R2,R1 (E0030192)

R3=30

圖 4-7 Data Processing 指令測試 1 結果 UMULL R3,R2,R1,R0

(E0832091)

R0=15 R1=03

R2=45 R3=00

- 65 -

圖 4-8 Data Processing 指令測試 2 結果 ADD R3,R1,R0

(E0813000)

R0=01 R1=03

R3=04

ADD R3,R2,R1 LSL#3 (E0823181)

R3=29 (R1+R2) R1=24

五、Floating-Point 指令測試

Floating-Point 指令主要執行兩個運算元作指定的浮點算術運算,來 獲得一個結果並將運算完的結果存入目的暫存器(Rd)中,測試程式如 表 4-7 所示,測試結果如圖 4-9、圖 4-10、圖 4-11、圖 4-12 所示:

表 4-7 Floating-Point 指令測試程式

Program Memory Address Machine Code Function LDR R1[R0,#28] 00 E5B0101C R1=42800000 LDR R2[R3,#28] 04 E5B32020 R2=41400000 FADD R5,R1,R2 08 EE115002 R5=42980000 FSUB R6,R1,R2 0C EE216002 R6=42500000 FDIV R8,R1.R2 10 EE818002 R8=43C00000 FMUL R7,R1,R2 14 EE417002 R7=412AAAAA

B #24 18 EA000018 BRANCH 0X18

DATA SEGMENT 1C 42800000

20 41400000 R1=42800000=1.0×27,R2=41400000=1.1×24 R5=R1+R2=42980000

R6=R1-R2=42500000 R7=R1*R2=43C00000 R8=R1/R2=412AAAAA

表 4-7Floating-Point 指令測試程式中,將過第一道與第二道指令後 R1=42800000,R2=41400000,圖 4-9 為執行浮點加法後的結果,圖 4-10 為執行浮點減法後之結果,圖 4-11 為執行浮點除法後之結果,圖 4-12 為執行浮點乘法後之結果。

- 67 -

圖 4-9 Floating-Point 指令測試結果 FADD R5,R1,R2

(EE115002)

R1=42800000

R2=41400000 R5=429800000

圖 4-10 Floating-Point 指令測試結果 FSUB R6,R1,R2

(EE216002)

R1=42800000

R2=41400000 R6=425000000

- 69 -

圖 4-11 Floating-Point 程式測試結果

FDIV R8,R1,R2 (EE818002)

R1=42800000

R2=41400000 R8=412AAAAA

圖 4-12 Floating-Point 指令測試結果 FMUL R7,R1,R2

(EE417002)

R1=42800000 R2=41400000

R7=43C00000

六、ARM CPU 指令 Clock Cycle 統計

如表 4-8 所示為 ARM CPU 各類指令執行完畢,所花費的 Clock Cycle。

表 4-8 ARM CPU 指令 Clock Cycle 統計

Instruction Clock Cycle

Data Process 3

Multiply / Mmultiple Long 3 / 4 Branch / Branch with Link 3 / 4

LDR、STR、SWP 4

LDM、STM 18

Floating Point 8

第二節 實驗平台規劃設計

本研究自製的 FPGA 實驗平台使用 Xilinx Virtex XCV800 之 FPGA 晶片約為 80 萬邏輯閘數(Gate Count),並搭配其他 I/O 模組,

組成 ARM CPU 電路實驗平台。

實驗平台包含 FPGA 晶片板、電源電路(Power Circuit)、傳輸埠 (Print Port)、輸入元件、輸入元件,其中 FPGA 晶片板使用 Xilinx Virtex XCV800 晶片,是一顆 HQ 包裝 240 pin 的 FPGA,並利用轉 接板的連接將 FPGA 各接腳連接至外部的 I/O 模組。實驗平台如下 如圖 3-16 所示:

圖 4-13 FPGA 實驗平台

FPGA 實驗平台實體圖,如圖 3-17 所示。

Power Circuit

Programming Module

Xilinx Virtex XCV800 800k Gate Count

FPGA XILINX ISE

+ Model Sim

PrintPort

Text LCD Module (16 x 2) Seven Segment

LED Bar LED Bar LED Bar LED Bar

Dip Switches

4x4 Key Pad

Dip Switches Dip Switches Push Buttoms

圖 4-14 FPGA 實驗平台實體圖

第三節 系統測試示範

壹、 系統測試流程

首先,在個人電腦建立 ARM_TEST.coe 檔並將欲測試程式編輯 成 16 進制的機械碼輸入,在開啟 Xilinx ISE Core Generator,將 ARM_TEST.coe 載入 ARM CPU 的 Memory 中,並執行 Implement Design 測試無誤後,開啟實驗平台電源,接上 Print Port 排線,執 行 Generate Programming File 進行程式下載至 FPGA 中。

貳、 測試程式

系統測試程式如表 4-9 所示,測試程式以 24 小時時間計數器程式 為範例,該程式分為時、分、秒三個計數器,當秒計數器計數到 59 時則分計數器會加 1,並將秒計數器歸零,當分計數器計數到 59 時 則時計數器會加 1,並將分計數器歸零,依此類推,因 ARM CPU 送出的顯示資料為十六進制,必須再用軟體指令修正為十進制顯 示,輸出結果可由實驗平台的文字型 LCD 觀測,可利用指撥開關 輸入,顯示 ARM CPU 的暫存器中的數值。圖 4-15 為測試程式執行 結果。

表 4-9 系統測試程式

PROGRAM Memory Address Machine Code

START: MOV R0,#0 00 E3A00000

MOV R1,#0 04 E3A01000

MOV R2,#0 08 E3A02000

SEC : MOV R3,R0 0C E1A03000

ORR R3,R3,R1 LSL #8 10 E1833401

ORR R3,R3,R2LSL #16 14 E1833802

CMPS R0,#59 18 E3500059

BEQ MIN 1C 0A000038

ADD R0,R0,#01 20 E2800001

MOV R6,R0 24 E1A06000

AND R6,R6,#0F 28 E206600F

TEQS R6,#0A 2C E336000A

ADDEQ R0,R0,#06 30 02800006

B SEC 34 EA00000C

MIN: CMPS R1,#59 38 E3510059

BEQ HOUR 3C 0A00005C

MOV R0,#0 40 E3A00000

ADD R1,R1,#01 44 E2811001

MOV R4,R1 48 E1A04001

AND R4,R4,#0F 4C E204400F

TEQS R4,#0A 50 E334000A

ADDEQ R1,R1,#06 54 02811006

B SEC 58 EA00000C

HOUR: CMPS R2,#23 5C E3520023

BEQ START 60 0A000000

MOV R0,#0 64 E3A00000

MOV R1,#0 68 E3A01000

ADD R2,R2,#01 6C E2822001

MOV R5,R2 70 E1A05002

AND R5,R5,#0F 74 E205500F

TEQS R5,#0A 78 E335000A

ADDEQ R2,R2,#06 7C 02822006

B SEC 80 EA00000C

24 小時時間計數程式下載結果,如圖 4-15、圖 4-16 所示。

圖 4-15 24 小時時間計數程式下載結果

圖 4-16 24 小時時間計數程式下載結果

參、 各模組 Gate Count 耗費統計數

ARM CPU 硬體電路於 Xilinx ISE 實現後各模組消耗之 Gate Count 數統計表如表 4-10 所示:

表 4-10 ARM CPU 整個程式模組耗費的 Gate Count 數統計

Module Name Gate Counts 備註 Control Unit 1,014

Data Path 154,252

DPU 23,051 包含 ALU、Barrel

Shifter、乘法器,Barrel Shifter 使用 2,151 個 Gate Counts

Instruction Register 904 Register Bank 17,334 Memory 66,016 Float-Point Unit 50,582 total 157,770

由以上的統計數據顯示,選用 800k Gate Count 的 FPGA 晶片,最 多約用了 18%的 Gate Counts,因此未來再進行擴充設計的彈性很大。

![圖 4-1 Signal Data Transfer(LDR/STR)指令測試結LDR R3 [R1,#02]](https://thumb-ap.123doks.com/thumbv2/9libinfo/7223449.58243/3.1188.92.1088.100.689/圖41SignalDataTransferLDRSTR指令測試結LDRR3R12.webp)