科技部補助專題研究計畫報告

2.4-/24-GHz 雙頻共存感測器接收機射頻前端電路之整合設計

(第2年)

報 告 類 別 : 成果報告 計 畫 類 別 : 個別型計畫 計 畫 編 號 : MOST 107-2221-E-006-200-MY2 執 行 期 間 : 108年08月01日至109年07月31日 執 行 單 位 : 國立成功大學電機工程學系(所) 計 畫 主 持 人 : 黃尊禧 共 同 主 持 人 : 黃至堯 計畫參與人員: 碩士班研究生-兼任助理:李東諺 碩士班研究生-兼任助理:劉益愷 碩士班研究生-兼任助理:卓晉宇 碩士班研究生-兼任助理:王先宸 碩士班研究生-兼任助理:劉健安 碩士班研究生-兼任助理:張又升 博士班研究生-兼任助理:林憶源 報 告 附 件 : 出席國際學術會議心得報告本研究具有政策應用參考價值:■否 □是,建議提供機關

(勾選「是」者,請列舉建議可提供施政參考之業務主管機關)

本研究具影響公共利益之重大發現:□否 □是

中 華 民 國 109 年 10 月 30 日

中 文 摘 要 : 本計畫規劃為期二年,將研發『2.4-/24-GHz 雙頻共存感測器接收 機射頻前端電路之整合設計』。主要開發一款雙頻共存感測器接收 機射頻前端電路並整合實驗室前年開發之新型六角電感於該前端電 路設計中。近年來由於物聯網的技術發展需求不斷上升。以萬物皆 可上網的概念,對於無線通訊系統網路的公司無不積極地看準毫米 波波段之頻道,以便高速處理大量的無線資料傳輸。但另一方面 ,所謂的感測器網路也在興起。與通訊網路不同的是目前的感測器 網路著眼點在於低功耗的網路設計,以認知式的操作為目的來做資 料傳輸而較少強調對於毫米波頻帶通道的需求。但我們觀察到雷達 感測器在未來的感測應用中也已經變成一個重要的感測元件。部分 的應用情境(如氣象雷達)還是需要毫米波雷達的元件。我們相信未 來會存在很多低頻帶及毫米波頻帶的感測器一起應用的需求。故本 計畫擬開發一個常用的2.4-GHz 和 24-GHz ISM 頻帶共存的感測器 接收器,以便提供未來感測器網路中接收機的另一項選擇。利用將 24-GHz毫米波前端電路的降頻作用將其訊號降頻到2.4-GHz,然後 ,再利用一個切換開關電路選擇與2.4-GHz 前端電路合併以達電路 共用的目的並期降低晶片成本。此外,前年實驗室執行科技部計畫 (MOST-105-E-2221-006-243)開發一個新型之六角形電感(中華民國 專利申請號:106113993)。該電感類似8-字型電感具有抑制電磁輻射 干擾的能力,比起傳統的平面螺旋電感大約有+15dB的干擾抑制效果 。且初步研究成果也顯示該電感特性在K-頻帶下有較好的Q值。但是 因為天生磁通密度較傳統電感於相同面積下有較高的趨勢,所以這 個電感在低頻帶(如2.4 GHz – 5 GHz)Q值較低。目前本實驗室已於 tsmc 0.18-um CMOS製程及MEMS後製製程驗證電感Q值改善的先期研 究,並分別以一個原始的六角形電感和利用MEMS挖空矽基底的六角 形電感來完成一個18-GHz的壓控振盪器測試鍵模擬並已於十一月透 過CIC下線製作。初步模擬結果顯示後者在相位雜訊上有0.5 dB的改 善。本計畫另一目的是透過計畫的執行將此電感整合於此感測器接 收機內,以期觀察在一個真正收發機電路內該電感對於電路特性的 影響。若驗證確實電路整合特性可以有較高的電感佈局密度且不劣 化整體電路特性,未來我們將推廣這個新型六角形電感於IC設計業 界使用。 中 文 關 鍵 詞 : 雙頻共存系統、電磁干擾、感測器接收機、六角形電感、毫米波前 端電路

英 文 摘 要 : This two-year project entitled “2.4-/24-GHz Dual-band Coexistence

Sensor Receiver RF Front-end Integration Design,” will study and

develop a dual-band sensor receiver which will be also integrated with

our proposed novel hexagonal-type (i.e., honeycomb-like) inductor

developed in the last two year. In the recent years the demands of

Internet-of-Things (IOT) technology gradually increase. This tide of

trend is so huge that people cannot stop it. Due to the concept of

internet-of-everything, some communication alliances seek for the

operation channel in millimeter-wave band to make the massive data

transmission possible in high speed. On the other hand, so-called sensor network is under progress. Different to the communication network, the present sensor network focus on the low-power operation based on low data rate with

cognitive radios rather than try to access the millimeter-wave channel for high-data rate transmission. However, we find that in the future applications radar sensors become a kind of important key sensor component. Some parts of

application scenarios (e.g., weather radars) need millimeter-wave radars. We believe there will be many

sensors either in low-frequency-band or high-frequency-band in the future. Therefore, in this project, we would like to develop a sensor receiver topology in the popular 2.4 GHz and 24 GHz ISM bands, which will provide another choice of sensor networks. With the down conversion

of a 24 GHz signal to 2.4 GHz, then via a switch circuit, we can build the 24-GHz and 2.4-GHz receivers together to reduce the chip cost. Moreover, a novel hexagonal-type inductor (ROC patent, filed no. 106113993) has been

developed in our Lab last year. Such inductor, similar to the 8-shape inductors, has the capability of

electromagnetic interference suppression. The present experimental data show this novel inductor has over +15 dB of interference suppression as compared with a conventional spiral inductor. And the pre-study also shows that this novel inductor exhibits a better Q-factor in K-band. But with a higher magnetic flux density, the Q-factor will be low in a low-band (e.g., 2.4 GHz – 5 GHz). So far, the pre-study of Q-factor improvement by way of tsmc 0.18-um CMOS technology as well as MEMS post-process has been proceeded in our Lab. We have implemented two 18-GHz VCO circuits with the original hexagonal-type inductor and the MEMS hexagonal-type inductor in hollow substrate,

espectively, in this November. The simulation results show the later has an improvement of 0.5 dB in phase

noise. Another target of this project is to integrate our novel inductor (either non-MEMS or MEMS) to the proposed dual-band sensor receiver and to investigate the influence of circuit characteristics in a real receiver. If we can successfully prove that the receiver integration has a higher layout density but without the performance degrades, we will promote this novel inductor to the

industry.

英 文 關 鍵 詞 : Dual-band coexistence system, Electromagnetic interference, Sensor

科技部補助專題研究計畫成果報告

(

□期中進度報告/■期末報告)

(24-/2.4-GHz 雙模共存感測器接收機射頻前端電路之整合設計)

計畫類別:■個別型計畫 □整合型計畫

計畫編號:MOST

107-2221-E-006-200-MY2

執行期間:2018 年 8 月 1 日至 2020 年 7 月 31 日

執行機構及系所:國立成功大學 電機工程學系

計畫主持人:黃尊禧

共同主持人:黃至堯

計畫參與人員:林憶源、張又升、劉健安、王先宸

、卓晉宇、劉益愷、李東諺

本計畫除繳交成果報告外,另含下列出國報告,共 _2_ 份:

□執行國際合作與移地研究心得報告

■出席國際學術會議心得報告

□出國參訪及考察心得報告

中 華 民 國 109 年 10 月 29 日

研究計畫中英文摘要

計畫中文關鍵詞 雙頻共存系統、電磁干擾、感測器接收機、六角形電感、毫米波前端電路

計畫英文關鍵詞 Dual-band coexistence system, Electromagnetic interference, Sensor receiver, Millimeter-wave front-end. 計畫中文摘要 本計畫規劃為期二年,將研發『2.4-/24-GHz 雙頻共存感測器接收機射頻前端電路 之整合設計』。主要開發一款雙頻共存感測器接收機射頻前端電路並整合實驗室 前年開發之新型六角電感於該前端電路設計中。近年來由於物聯網的技術發展需 求不斷上升。以萬物皆可上網的概念,對於無線通訊系統網路的公司無不積極地 看準毫米波波段之頻道,以便高速處理大量的無線資料傳輸。但另一方面,所謂 的感測器網路也在興起。與通訊網路不同的是目前的感測器網路著眼點在於低功 耗的網路設計,以認知式的操作為目的來做資料傳輸而較少強調對於毫米波頻帶 通道的需求。但我們觀察到雷達感測器在未來的感測應用中也已經變成一個重要 的感測元件。部分的應用情境(如氣象雷達)還是需要毫米波雷達的元件。我們相信 未來會存在很多低頻帶及毫米波頻帶的感測器一起應用的需求。故本計畫擬開發 一個常用的2.4-GHz 和 24-GHz ISM 頻帶共存的感測器接收器,以便提供未來感 測器網路中接收機的另一項選擇。利用將24-GHz毫米波前端電路的降頻作用將其 訊號降頻到2.4-GHz,然後,再利用一個切換開關電路選擇與2.4-GHz 前端電路合 併以達電路共用的目的並期降低晶片成本。 此外,前年實驗室執行科技部計畫(MOST-105-E-2221-006-243)開發一個新型之六 角形電感(中華民國專利申請號:106113993)。該電感類似8-字型電感具有抑制電磁 輻射干擾的能力,比起傳統的平面螺旋電感大約有+15dB的干擾抑制效果。且初 步研究成果也顯示該電感特性在K-頻帶下有較好的Q值。但是因為天生磁通密度 較傳統電感於相同面積下有較高的趨勢,所以這個電感在低頻帶(如2.4 GHz – 5 GHz)Q值較低。目前本實驗室已於TSMC18-um CMOS製程及MEMS後製製程驗證 電感Q值改善的先期研究,並分別以一個原始的六角形電感和利用MEMS挖空矽 基底的六角形電感來完成一個18-GHz的壓控振盪器測試鍵模擬並已於十一月透 過CIC下線製作。初步模擬結果顯示後者在相位雜訊上有0.5 dB的改善。本計畫另 一目的是透過計畫的執行將此電感整合於此感測器接收機內,以期觀察在一個真 正收發機電路內該電感對於電路特性的影響。若驗證確實電路整合特性可以有較 高的電感佈局密度且不劣化整體電路特性,未來我們將推廣這個新型六角形電感 於IC設計業界使用。

計畫英文摘要 This two-year project entitled “2.4-/24-GHz Dual-band Coexistence Sensor Receiver RF Front-end Integration Design,” will study and develop a dual-band sensor receiver which will be also integrated with our proposed novel hexagonal-type (i.e., honeycomb-like) inductor developed in the last two year. In the recent years the demands of Internet-of-Things (IOT) technology gradually increase. This tide of trend is so huge that people cannot stop it. Due to the concept of internet-of-everything, some communication alliances seek for the operation channel in millimeter-wave band to make the massive data transmission possible in high speed. On the other hand, so-called sensor network is

under progress. Different to the communication network, the present sensor network focus on the low-power operation based on low-data rate with cognitive radios rather than try to access the millimeter-wave channel for high-data rate transmission. However, we find that in the future applications radar sensors become a kind of important key sensor component. Some parts of application scenarios (e.g., weather radars) need millimeter-wave radars. We believe there will be many sensors either in low-frequency-band or high-frequency-low-frequency-band in the future. Therefore, in this project, we would like to develop a sensor receiver topology in the popular 2.4 GHz and 24 GHz ISM bands, which will provide another choice of sensor networks. With the down-conversion of a 24 GHz signal to 2.4 GHz, then via a switch circuit, we can build the 24-GHz and 2.4-GHz receivers together to reduce the chip cost.

Moreover, a novel hexagonal-type inductor (ROC patent, filed no. 106113993) has been developed in our Lab last year. Such inductor, similar to the 8-shape inductors, has the capability of electromagnetic interference suppression. The present experimental data show this novel inductor has over +15 dB of interference suppression as compared with a conventional spiral inductor. And the pre-study also shows that this novel inductor exhibits a better factor in K-band. But with a higher magnetic flux density, the factor will be low in a low-band (e.g., 2.4 GHz – 5 GHz). So far, the pre-study of Q-factor improvement by way of TSMC.18-um CMOS technology as well as MEMS post-process has been proceeded in our Lab. We have implemented two 18-GHz VCO circuits with the original hexagonal-type inductor and the MEMS hexagonal-type inductor in hollow substrate, respectively, in this November. The simulation results show the later has an improvement of 0.5 dB in phase noise. Another target of this project is to integrate our novel inductor (either non-MEMS or MEMS) to the proposed dual-band sensor receiver and to investigate the influence of circuit characteristics in a real receiver. If we can successfully prove that the receiver integration has a higher layout density but without the performance degrades, we will promote this novel inductor to the industry.

目錄

頁次

一、 前言

5

二、 研究目的

6

三、 文獻探討

7

四、 研究成果

9

五、 結論

28

六、參考文獻

29

成果報告自評表

30

出席國際學術會議心得報告 (2份)

32

一、前言

本專題主要整合一個 2.4 GHz / 24 GHz 射頻前端電路(含 LNA+Mixer+VCO);為執行科技部計畫 2.4/24-GHz 雙頻共存感測器機收機所規劃之電路設計,如圖 1 所示。考量現今感測器常用之通訊頻帶, 此射頻前端系統可接收 2.4-及 24-28GHz 之 ISM 頻帶訊號並降頻,未來透過後端基頻系統處理可完成 一完整感測接收器系統。因應5G 通訊趨勢的規畫[1],高頻前端電路之接收範圍可以延伸至 28-GHz。 將操作頻帶轉移至毫米波以增加資料傳輸率(data rate)是 5G 通訊的必然趨勢。隨著物聯網的蓬勃發展, 將提升對通訊硬體的需求,加上新世代5G 通訊的來臨,為了達到萬物聯網的目標,感測器的配置將無 所不在。感測器將在智慧家電、交通、物流、安全監控系統、生醫輔助裝置等產生多方面應用,幫助提 升人類生活品質。而如何完成終端感測器與資料網路間的無線傳輸為其關鍵技術。此計畫概念起始於 採用雙頻系統架構[2][3]達到多模態操作,但創新性在於選擇 2.4-及 24-28 GHz ISM 頻段來設計,如圖 1 所示,以建構一個以感測器為主的簡易收發機系統。 本專題研究規劃之系統可靈活運用24-GHz 頻道的獨立性。目前 24-GHz 頻帶規畫用於雷達偵測, 常見如車用輔助系統、生醫應用及物件偵測等;而 2.4-GHz 為常見的無線通訊使用頻帶(IEEE 802.11 b/g/ax)。許多裝置如手機、筆記型電腦、感測器等皆應用於此,2.4-GHz 頻帶的應用發展已經成熟。現 在已經相當發達的 2.4-GHz 無線通訊或感測應用,頻帶使用過於壅塞,頻道間容易互相干擾,故開發 24-28 GHz 頻帶與之共存,有助於改善頻帶壅塞的問題。 考慮透過24-28 GHz新型感測元件或是雷達感測元件來負責偵測物體或環境資訊,透過此接收機接 收電磁波經過物體反射之訊號,經過兩次降頻後至基頻解調待測物所帶有的資訊。本計畫著重在雙頻 帶的接收端,如何能夠完成接收資訊、忠實呈現給後端電路進行訊號處理。應用場景如:高齡化社會-居家監測、無人機防撞措施等等。本架構利用其優勢,將24-GHz高頻訊號即時交付至2.4-GHz系統處理, 可節省因應新型通訊規則大量翻新硬體設施的成本,達到通訊品質與實現成本雙贏的局面。 在本研究專題所擬採用的系統架構中,如圖 1 所示,未來並設定 2.4-/24-28 GHz 雙頻頻帶將利用 開關切換。24-GHz 頻帶訊號透過兩次降頻至基頻(baseband)進行訊號處理,而 2.4-GHz 頻帶訊號經由 一次降頻後送至後端系統。為因應此目標,前端電路的寬頻設計為一大挑戰,24-28 GHz 之寬頻低雜訊 放大器(Low noise amplifier, LNA)及 21.6-25.6 GHz 之本地振盪源(Local Oscillator, LO),經由混頻器 (Mixer)降頻至 2.4-GHz,再透過開關切換接收之頻率訊號。 本次專題射計即著眼在 24-28 GHz 射頻前 端電路之設計整合,並完成一個 26GHz 接收機的雛型驗證。 圖 1、本研究專題所提出之雙頻感測器接收機系統架構示意圖 24-28 GHz LO1 21.6-25.6 GHz LO2 1.8-2.4 GHz SW1 IF Buffer amp. 2.4 GHz This Work二、研究目的

近年來由於物聯網的技術發展需求不斷上升。以萬物皆可上網的概念,對於無線通訊系統網路的 公司無不積極地看準毫米波波段之頻道,以便高速處理大量的無線資料傳輸。但另一方面,所謂的感 測器網路也在興起。與通訊網路不同的是目前的感測器網路著眼點在於低功耗的網路設計,以認知式 的操作為目的來做資料傳輸而較少強調對於毫米波頻帶通道的需求。但我們觀察到雷達感測器在未來 的感測應用中也已經變成一個重要的感測元件。部分的應用情境(如氣象雷達)還是需要毫米波雷達的 元件。我們相信未來會存在很多低頻帶及毫米波頻帶的感測器一起應用的需求。故本計畫係開發一個 常用的2.4-GHz 和 24-GHz ISM 頻帶共存的感測器接收器,以便提供未來感測器網路中接收機的另一 項選擇。利用將 24-GHz 毫米波前端電路的降頻作用將其訊號降頻到 2.4-GHz ,然後,再利用一個切 換開關電路選擇與2.4-GHz 前端電路合併以達電路共用的目的並期降低晶片成本。 在這個專題計畫中,第一年我們完成下列四顆晶片的設計、下線及整合,包括: (1) 毫米波 24-28 GHz 低雜訊放大器設計;(2) 26 GHz 振盪器設計; (3) 24-28 GHz 混頻器設計;和(4) 整合前 3 項子 電路的射頻接收機的電路。但因第一顆晶片的特性需要持續改進,於是今年第二年我們重新設計在 24-28 GHz 頻帶的子電路及其整合的收發機電路。另外,依計畫的規劃,我們也於今年度設計 2.4 GHz 之 前端電路各子電路及其整合。 此外,前些年實驗室執行科技部計畫(MOST-105-E-2221-006-243)開發一個新型之六角形電感(中華 民國專利申請號:106113993)。該電感類似 8-字型電感具有抑制電磁輻射干擾的能力,比起傳統的平面 螺旋電感大約有+15dB 的干擾抑制效果。且初步研究成果也顯示該電感特性在 K-頻帶下有較好的 Q 值。 但是因為天生磁通密度較傳統電感於相同面積下有較高的趨勢,所以這個電感在低頻帶(如 2.4 GHz – 5 GHz) Q 值較低。目前本實驗室已於 tsmc 0.18-m CMOS 製程及 MEMS 後製製程驗證電感 Q 值改善的 先期研究,並分別以一個原始的六角形電感和利用MEMS 挖空矽基底的六角形電感來完成一個 18-GHz 的壓控振盪器測試鍵模擬並已於完成下線製作且發表於WPTC 2019。本計畫另一目的是透過計畫的執 行將此電感整合於此感測器接收機內,以期觀察在一個真正收發機電路內該電感對於電路特性的影響。 在今年第二年的計畫執行中,我們亦完成了一個 3 級低雜訊放大器電路並結合一個回授電路來探討六 角形電感對於接收機抑止電磁輻射干擾的效應。另外,今年度設計2.4 GHz 之前端電路各子電路及其 整合中,我們亦整合了六角形電感於接收機中。三、文獻探討

近期研究常見的雙頻系統多為GSM(Global System for Mobile Communications)或 WLAN(Wireless Local Area Network)應用。900-MHz/1.9-GHz 收發機應用於全球行動通訊系統(GSM)[5],如圖 2(a)所示, 採用外差架構經過兩次降頻至IF 頻段後,交給後端訊號處理。其中 RF 前端電路為典型的架構,將接 收和發射分成兩路設計,運用較多高速操作的子電路,功耗相對提升。而鏡像頻率的抑制透過濾波器 及Hartley 架構達到 45 dB 的抑制效果;頻率合成部分,使用振盪器搭配除頻器產生多個頻率訊號或使 用PLL 系統提供精準的頻率輸出,但相對的電路複雜度較高。 利用離散式元件整合,針對WLAN所設計的2.4- /5.2-GHz雙頻、多模態/規格應用之收發機系統[2],如 錯誤! 找不到參照來源。2(b)。將原本兩路並聯的雙頻前端電路共用以節省功耗及設計成本。其挑戰在 於如何設計雙頻的射頻放大器及濾波器,以利兩個頻段訊號都能通過。頻率合成則透過PLL及除數搭配 以提供2.4-/5.2-GHz訊號進行降頻。另外,或採用電流再利用架構結合單平衡式混頻器及VCO達到低功 耗目的[3],並整合至單晶片CMOS製程,達到總功耗 10 mW的低功耗設計。 (a) (b) 圖 2 (a) 900-MHz/1.9-GHz收發機架構[5] 及 (b) 2.4- /5.2-GHz收發機架構[2]

多模態操作的收發機常會使用 VCO 搭配除頻器提供一個較低頻的 LO 訊號,但本專題研究所擬開 發之接收機設計中兩個 LO 頻率差距約 10 倍,除頻器的實現上較複雜,故採用兩個獨立的 VCO 以提 供穩定的 LO 訊號。當受到 PVT 變異(process, voltage and temperature variation)時各自的 VCO 具有頻率 調整的靈活度,同時減輕頻率合成設計之負擔。而此次的雙頻系統採取分時雙工機制,利用開關切換 從 24-GHz 雷達系統或 2.4-GHz 無線通訊/感測器所接收之訊號,共用後端 2.4-GHz 混頻器及基頻放大 器,縮小晶片面積以利系統整合。

而目前 K-band 24-28 GHz 頻帶的規劃多為雷達感測系統,可依調變方式分為頻率調變(Frequency Modulated Continuous Wave, FMCW)或脈衝雷達,長距離雷達偵測在窄頻範圍內具有高發射功率的優 勢、短距離雷達及超寬頻脈衝雷達具有高解析度、低傳輸洩漏等特色[6],可應用於高精密度工業測量、 車用輔助系統,如:死角偵測、防撞機制、停車輔助等[7][8]。隨著 5G 通訊時代來臨,操作頻帶轉移至 毫米波以增加資料傳輸率(data rate),並使用天線陣列之架構[9]搭配相位調整機制(phased array system), 同步多路訊號將其加總以彌補高頻電磁波傳輸損耗(path loss)及提升系統訊雜比,利於後端系統進行訊 號處理。並透過調整時間延遲(相位)及陣列數量達到波束集中(beamforming)及調整零點的位置以抑制 干擾訊號之效果[10][11],預計規劃 28-GHz 頻帶於 5G 行動通訊,使用相位調整陣列應用於 28-GHz 收 發機系統[12][13]。上述為現有技術應用面的簡單說明。考量物聯網的需求,未來將有更多的無線感測 器元件的開發及應用。雖然現有的 5G 通訊技術也已經將物聯網的應用需求納進了系統規劃中,但我們 相信也會有許多的獨立感測網路應用需要有收發機之設計。考量這些獨立感測網路應用時,較低規格 但符合成本的收發機有其相當的必要性。

四、研究成果

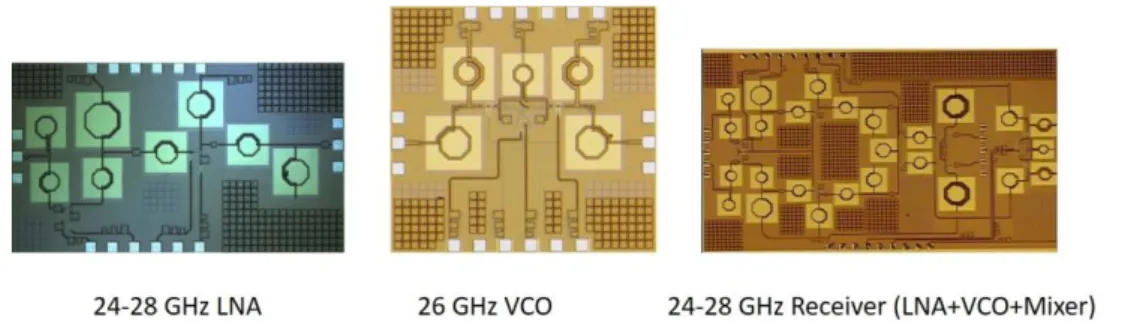

以下節錄本計畫執行所設計之各前端電路設計、模擬及量測結果。在這個專題計畫中,第 一年我們完成下列四顆晶片的設計、下線及整合,包括: (1) 毫米波24-28 GHz 低雜訊放大器設 計;(2) 26 GHz 振盪器設計; (3) 24-28 GHz 混頻器設計;和(4) 整合前3項子電路的射頻接收 機的電路。所完成的晶片照相圖如圖3所示。 但因第一顆晶片的特性需要持續改進,於是今年第二年我們重新設計在24-28 GHz 頻帶的 子電路及其整合的收發機電路。另外,依計畫的規劃,我們也於今年度設計2.4 GHz 之前端電 路各子電路及其整合。此2.4 GHz放大器電路及混頻器電路,透過個別之設計及模擬,並將之整 合下線驗證。研究成果將呈現於下列各節。 24 GHz 低雜訊放大器 (LNA)

此接收機中低雜訊放大器採用架構為三級串接,根據 NF 和 IIP3 的公式可得知前級應較注重 雜訊的表現,線性度則是看後級,因此此低雜訊放大器第一級使用共源級放大器,且藉由電感的 Source degeneration 能同時達到雜訊匹配及功率匹配。第二級做為整個放大器的增益核心,採用 共閘級和共源級疊接的方式。第三級則是利用較高的偏壓和電感的Source degeneration 方式來維 持整個放大器的線性度。完整電路圖如圖 3。而在此低雜訊放大器的設計過程中,將所有模擬元 件做佈局上的考量,考慮讓佈局所必須的走線盡量短而平順,並將額外加入的走線或特殊轉彎處 理皆使用ADS momentum 進行 EM 模擬作為 post-simulation。此 24 GHz 低雜訊放大器最大增益為 22.2 dB,在 24 GHz 時 NF 為 4.47 dB,S11 在使用頻帶 皆有小於 -10 dB 的表現,電路全頻段穩定。

表 1、24 GHz LNA 模擬特性總表

24 GHz CMOS LNA

Parameter Pre-sim. Post-sim.

Input return loss (dB) -33 -12.6

Power Gain (dB) 24 22.2

NF(dB) 3.4 4.47

Power consumption (mW) 4.1 5.88

VIN VG1 VG2 VG3 VOUT M1 M2 M3 M4 C1 L1 R1 L2 R2 R3 L3 L6 L4 L5 VDD VDD VDD VDD C2 C3 圖 3、24 GHz 低雜訊放大器

24 GHz 混頻器 (Mixer)

混頻器部分在 RF 輸入端使用共閘級放大器,有別於一般使用共源級放大器的原因是為了降低 CGD (米勒電容)的影響來提高頻寬和線性度,且對於 RF 輸入和 LO 輸入之間也有較好的隔離度, 以方便壓控震盪器的整合。另外於 RF 和 LO 級間置放一個電感來與寄生電容達到並聯諧振的效 果,提高轉換增益。由於第一次降頻後的頻率是2.4 GHz,因此在混頻器的輸出端使用了 LC 共振 腔來達到帶頻濾波器的效果。至於Buffer 則使用了共汲級放大器來達到 50 歐姆的輸出匹配,且藉 由共汲級放大器電壓增益趨近為1 的同時將大阻抗轉換成小阻抗的特性,也能提供功率增益。 表 2、24 GHz Mixer 模擬特性總表24 GHz Single-Balanced Gilbert Cell Mixer

Parameter Pre-sim. Post-sim.

RF frequency(GHz) 24 24 CG (dB) 8.2 6.6 NF (dB) 11 13 IP1dB (dBm) -13 -13 IIP3(dBm) -2 -2.5 Power consumption (mW) 14.7 14.84

VIN M1 L1 C1 L2 VG M2 M3 C2 C3 L2 L3 VDD LO+ LO-IF+ IF-圖 4、24 GHz 單平衡式混頻器

21.6 GHz 壓控振盪器

本次 VCO 設計架構如圖 5 所示,電晶體選用 NMOS,相比於 PMOS,NMOS 可以用較小的尺

寸達到跟PMOS 相同的轉導值,故其寄生效應較小,對共振腔的共振頻率及頻率調整範圍影響較

小,較適用於高頻操作。由於Drain 端與 Source 端為同相位,電晶體 Source 電壓可以透過變壓器 耦合到Drain 端,使電晶體的輸出電壓可以高於 Vdd 及低於 0V,利於低電壓操作,同時減少整體 功耗。 振盪器後端因量測需求接上50 歐姆負載,或接至混頻器、除頻器,需要使用緩衝器降低後端負 載效應,並提高輸出功率以量測或驅動後級電路。在此設計使用一級CS 放大器提高隔離度以及放 大輸出功率的效果,並且調整放大器負載電感及電容,對量測端(50 歐姆)進行匹配,減少訊號之 反射。 (a) (b) M1 M2 Mb1 Mb2 Voutp Voutn

Vb Voff Vtune Voff Vb

Ld1 Ld1 Ls1 Ls1 Rb C1 Cv1 Cv1 C1 C2 C2 Rb Rb Rb Rb Lb Lb

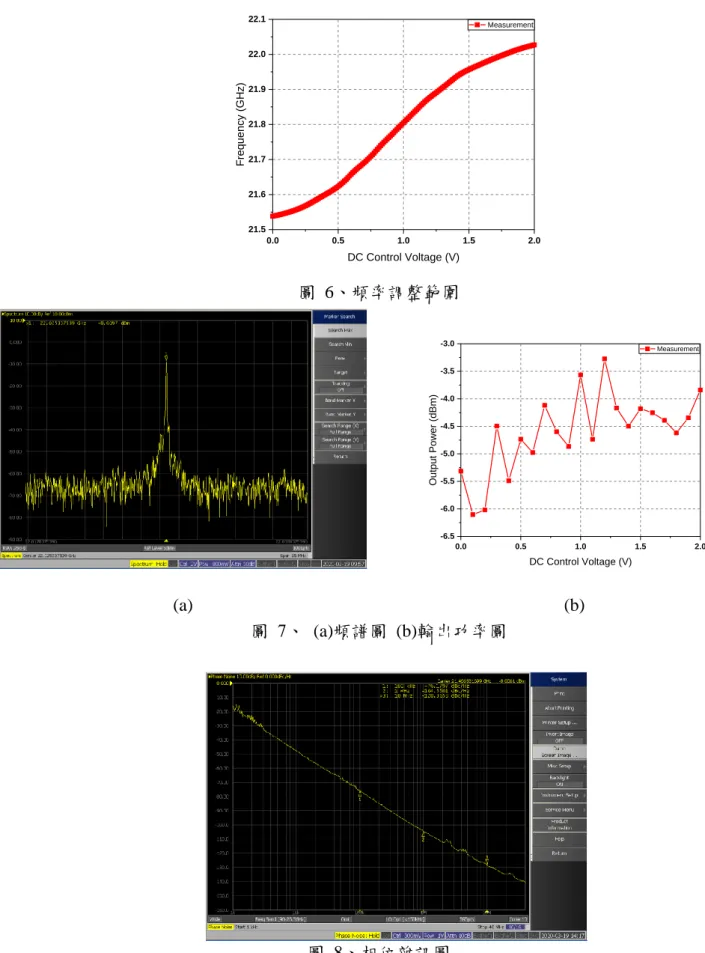

圖 5、壓控振盪器 (a)電路圖 (b)照相圖 此晶片之量測結果節錄於下: 圖 6、頻率調整範圍 (a) (b) 圖 7、 (a)頻譜圖 (b)輸出功率圖 圖 8、相位雜訊圖 0.0 0.5 1.0 1.5 2.0 21.5 21.6 21.7 21.8 21.9 22.0 22.1 Fr eq ue ncy ( GHz) DC Control Voltage (V) Measurement 0.0 0.5 1.0 1.5 2.0 -6.5 -6.0 -5.5 -5.0 -4.5 -4.0 -3.5 -3.0 Out pu t Power (d Bm) DC Control Voltage (V) Measurement

(a) (b) 圖 9、相位雜訊@ (a)1 MHz (b)10 MHz 透過晶片量測結果得知,振盪器操作頻率與模擬結果相比往低頻些微飄移,但仍還涵蓋接收 機所需頻率。由於量測出的操作頻率與模擬的誤差,導致該 LC 共振腔的整體 Q 值下降,造成相 位雜訊較模擬不佳。

24 GHz LNA+Mixer 模擬與量測結果:

將上述之 24 GHz LNA 和 Mixer 電路做整合並下線製作與量測。下圖(圖11)即為各參數之 模擬與量測之比較圖和晶片照相圖。 (a)S11 (b)S22(c)Conversion gain (d)Noise figure

0.0 0.5 1.0 1.5 2.0 -103.0 -102.5 -102.0 -101.5 -101.0 -100.5 -100.0 -99.5 -99.0 -98.5 PN @ 1 MHz ( dBc/Hz) DC Control Voltage (V) Measurement 0.0 0.5 1.0 1.5 2.0 -127.5 -127.0 -126.5 -126.0 -125.5 -125.0 -124.5 -124.0 -123.5 PN @ 10 M Hz (d Bc/Hz) DC Control Voltage (V) Measurement

(e)P1dB (f)IIP3

圖 10、24 GHz LNA+Mixer 各種特性之模擬與量測比較圖(a)~(f)和晶片照相圖。

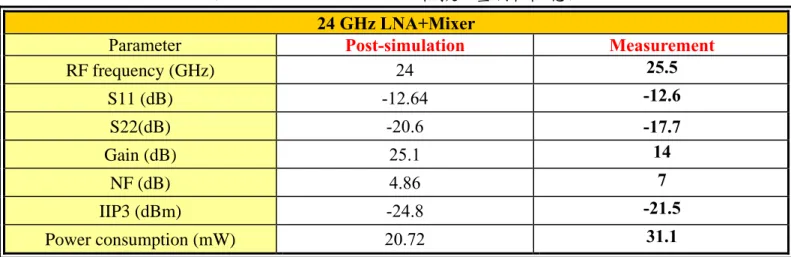

表 3、24 GHz LNA+Mixer 模擬及量測特性總表

24 GHz LNA+Mixer

Parameter Post-simulation Measurement

RF frequency (GHz) 24 25.5 S11 (dB) -12.64 -12.6 S22(dB) -20.6 -17.7 Gain (dB) 25.1 14 NF (dB) 4.86 7 IIP3 (dBm) -24.8 -21.5 Power consumption (mW) 20.72 31.1 從量測結果可看到 post-simulation 與 measurement 在效能最好的值與最佳效能的頻率上是有誤差 的,推測最大的原因是因為24 GHz 的電感 model 精確度不夠高,導致 LNA 三級的級間匹配跑掉,解 決辦法為用自製電感來輔助設計。

24 GHz Receiver 模擬與量測結果:

此節是將上述的24 GHz LNA+Mixer 的晶片再加上VCO 電路的整合設計並下線製作。下圖 (圖12) 即為模擬與量測之比較圖和晶片照相圖。(a)S11 (b)S22

(c)Conversion gain (d)Noise figure

(e) P1dB 圖 11、24 GHz Receiver 之模擬與量測比較圖及晶片照相圖 0 5 10 15 20 25 30 -25 -20 -15 -10 -5 0 S11 ( dB) Frequency (GHz) Measurement Simulation 0 2 4 6 8 10 -20 -15 -10 -5 0 S22 ( dB) Frequency (GHz) Measurement Simulation 23.8 24.0 24.2 0 2 4 Conve rsion Ga in ( dB) RF Frequency (GHz) Conversion Gain 23 24 25 15 16 17 NF ( dB) Frequency (GHz) NF -40 -35 -30 -25 -20 -15 -10 0 1 2 3 Conve rsion Ga in ( dB) RF power (dBm) Conversion Gain

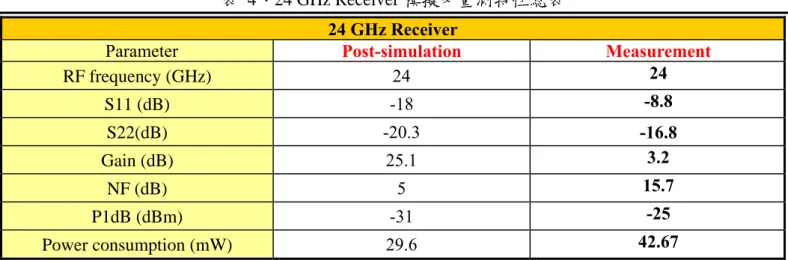

表 4、24 GHz Receiver 模擬及量測特性總表

24 GHz Receiver

Parameter Post-simulation Measurement

RF frequency (GHz) 24 24 S11 (dB) -18 -8.8 S22(dB) -20.3 -16.8 Gain (dB) 25.1 3.2 NF (dB) 5 15.7 P1dB (dBm) -31 -25 Power consumption (mW) 29.6 42.67 根據前面分別驗證的結果,得知LNA 與 Mixer 的操作頻率往高頻偏移,因此 24 GHz 時的表現相 較Post-simulation 降低了不少。

2.4 GHz 低雜訊放大器 (LNA)

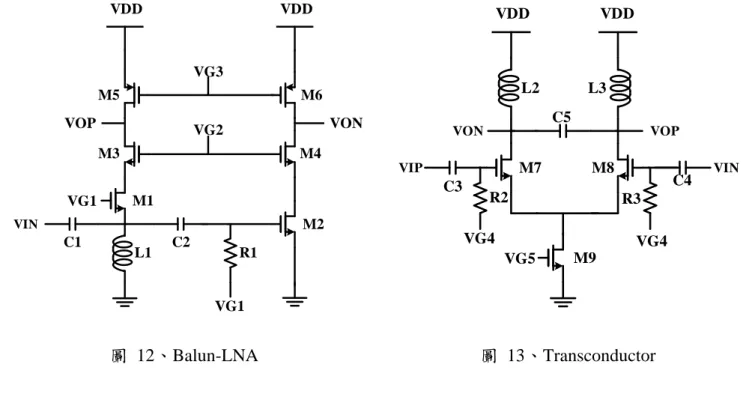

此2.4 GHz 接收機中低雜訊放大器,如圖 12,使用 Balun-LNA 的架構,其原理為利用一個單 端輸入分別透過共閘級放大器與共源級放大器來產生兩個反相的訊號。除此之外,共閘級放大器 的電晶體產生的雜訊能藉由輸入節點出現在共源級放大器輸出端,其相位與共閘級放大器輸出端 的雜訊相位相同,因此能藉由適當的設計來消除共閘級放大器的雜訊。且將負載電阻改成主動負 載,能在相同的Voltage drop 下提高增益和降低雜訊。 由於混頻器使用電流模態被動式混頻器,是由電流來驅動,因此需要在低雜訊放大器和混頻器 之間需要再加個轉導放大器將電壓訊號轉成電流訊號。事實上,此兩種放大器的功能可使用一個 低雜訊轉導放大器(LNTA)來實現。但一般的 LNTA 都是使用雙端輸入,在本次設計中不加以考 量。且Balun-LNA 的輸出端為不平衡的,此轉導放大器除了能將電壓轉換成電流之外,也能作 為低雜訊放大器的Buffer 來達到雙端輸出阻抗相同的效果。VIN C1 C2 VG1 VG3 VG2 VG1 R1 M5 M6 M4 M3 L1 M2 VDD M1 VDD VOP VON C4 R3 VOP VON VG5 C5 VIN L2 C3 VG4 R2 VIP M7 VDD M9 L3 VG4 M8 VDD 圖 12、Balun-LNA 圖 13、Transconductor

2.4 GHz 混頻器

電流模態被動式混頻器因為不被電壓擺幅的限制影響,有較佳的線性度,且無直流電流所導 致的閃爍雜訊。缺點為負增益,再來需要較大的LO Power 來驅動開關,且隔離度也是一個很大 的問題。電流模態被動式混頻器的輸出Buffer 需要有低輸入阻抗及濾波器的特性。一般常見的作 法有共閘級放大器或運算放大器兩種方式。考量到功率消耗與設計複雜度,本次設計選擇共閘級 放大器作為Buffer,並在其輸出端使用 RC-Tank 來做為低通濾波器。此系統最後一級則使用共汲 級放大器來做為量測用Buffer。C9

C8

C6

LON

VOPLOP

M10

VIP VONM11

C7

VIP VOPM12

VIN VONLOP

M13

VINVG7

VG6

C10

M17

M16

R5

R4

VIN VIPM15

M14

VDD

VDD

VON VOP 2.2 GHz 壓控震盪器

2.2 GHz 壓控振盪器設計架構如圖 16 錯誤! 找不到參照來源。所示,使用一條電流同時流過 PMOS 及 NMOS 電晶體,並且 PMOS 及 NMOS 同時提供轉導值,相對於只使用 PMOS 及 NMOS 時,減少額外一條電流,故可以有效降低功耗。由於本次使用Colpitts VCO 架構,相對於一般 VCO, 有較嚴格的起振條件,因此將 Mn1 電晶體的 gate 端與 MP1電晶體Source 連接,由於兩點為相反 極性,可以有效增加 gm,另外將輸出點接至電流源 Gate 端,藉此增加整體迴圈增益,透過此種 架構,可降低電流以達到Coplitts VCO 起振條件,達到較低功耗。 諧振腔電感使用實驗室開發之六角形電感,如圖 17 圖 17

、

六角形電感 所示,採用特殊繞線方式與對稱設計,且不論電流方向為何,當電流流經電感時,產生電磁感應, 根據安培右手定則,皆可產生三個射出紙面方向與三個射入紙面方向之磁場,共三對互相相反之 磁矩,此三對相反向量之磁場,可將磁矩相互抵消,降低對外影響之磁場大小。電容部分透過切 Mn1 Mbn Voutp Voutn Vtune Cv C2 Mbn C1 C2 C1 Ld Mn2 Mp1 Mp2 R1 R1 Mbp Mbp Cv Vsw (a) (b) 圖 16、壓控振盪器 (a)電路圖 (b)照相圖換式電容增加頻率可調範圍,利用並聯電容同時加入NMOS 開關,使開關為 0 與 1 時,有部分頻 帶重疊,藉此增加頻率可調範圍。振盪器後端緩衝器使用一級電阻回授反相器提供隔離度以及放 大輸出功率的效果。 圖 17

、

六角形電感 量測結果如下: 圖 18、頻率調整範圍 (a) (b) 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 1.8 1.9 2.0 2.1 2.2 2.3 2.4 Fr equenc y (GHz) DC Control Voltage (V) vsw=0(measurement) vsw=1(measurement) 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 -19.5 -19.0 -18.5 -18.0 -17.5 -17.0 -16.5 -16.0 Power (dBm) DC Control Voltage (V) vsw=0(measurement) vsw=1(measurement)圖 19、(a)頻譜圖 (b)輸出功率圖 圖 20、相位雜訊圖 (a) (b) 圖 21、相位雜訊@ (a)1 MHz (b)10 MHz 透過晶片量測結果得知,振盪器操作頻率與模擬結果相近,涵蓋接收機所需LO 頻率。相位雜 訊由於電感量測Q 值與模擬有誤差,導致該 LC 共振腔的整體 Q 值下降,造成相位雜訊較模擬不 佳。

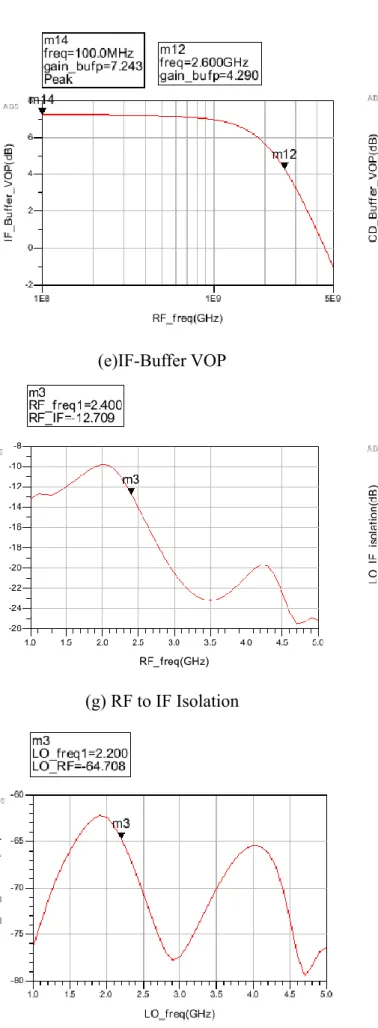

2.4 GHz LNA+Mixer 模擬結果

下圖(圖 23) 為 2.4 GHz LNA+Mixer 的電路設計模擬結果。此電路並與上述的 24 GHz Receiver 做整合下線,並量測。完成本專題計畫的雙頻接收機的整合。 (a),(b)為 Balun-LNA 雙端輸出的增益,需盡量設計為相同且相位相反。 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 -117.0 -116.5 -116.0 -115.5 -115.0 -114.5 -114.0 -113.5 PN @ 1 MH z (dBc /Hz) DC Control Voltage (V) vsw=0(measurement) vsw=1(measurement) 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 -142 -140 -138 -136 -134 -132 PN @ 10 MHz (dBc/Hz ) DC Control Voltage (V) vsw=0(measurement) vsw=1(measurement)(c),(d)為轉導放大器的增益,藉由負載端 LC 共振腔與下級的 DC Block 諧振在 2.4 GHz,可達最 好的表現。 (e)為 IF Buffer 的波德圖,雖然前面提到頻寬應設置在 IF 頻率 200MHz,將高頻雜訊濾除掉。但 由於會影響到增益,且高頻的雜訊為2 階項大約坐落於 4 GHz 的位置,因此將 IF Buffer 的 RC Corner 往後推到 2.6 GHz,減少對基頻增益的影響也能濾掉 2 階項的雜訊。 (f)為 CD Buffer 的波德圖,共汲級放大器的特性為接近 1 的電壓增益,由模擬可看出大概少了 1dB。此 Buffer 為量測用,需將輸出阻抗匹配到 50 歐姆。

(g),(h),(i)分別為 RF 對 IF 的隔離度,LO 對 IF 的隔離度,LO 對 RF 的隔離度。

(a)LNA VOP (b)LNA VON

(e)IF-Buffer VOP (f)CD-Buffer VOP

(g) RF to IF Isolation (h) LO to IF Isolation

(i) LO to RF Isolation

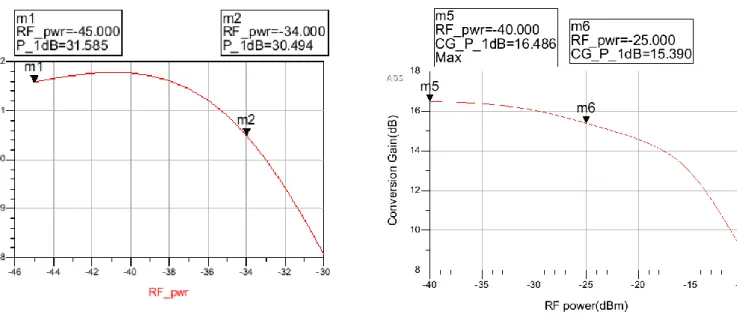

24 GHz and 2.4 GHz Receiver 模擬與量測結果

我們將上述的 2.4 GHz LNA+Mixer 與上述的 24 GHz Receiver 做整合下線,並量測。完成本 專題計畫的雙頻接收機的整合。模擬時,第一種考量Path 1 為 24 GHz 輸入經過兩次降頻,第一 種考量Path 2 為 2.4 GHz 輸入經過一次降頻。設計結果呈現如下,並整合晶片下線製作並量測。 i. S-parameter Path 1-S11 Path 2-S11 Path 1-S22 Path 2-S22ii. Conversion Gain

Path1-Conversion Gain Path2-Conversion Gain iii. Noise Figure

iv. P1dB

Path1-P1dB Path2-P1dB

表 5、雙模共存感測器接收機模擬特性表

2.4-/24-GHz Dual-band Coexistence Sensor Receiver

Parameter Path1 Path2

Conversion gain (dB) 31.6 16.45 Noise figure(dB) 5.1 7.05 IP1dB (dBm) -36 -25 Power consumption (mW) 82.24 52.63 圖 23、24-/2.4-GHz 雙模共存感測器接收機晶片照相圖 24 GHz Receiver 2.4 GHz Receiver

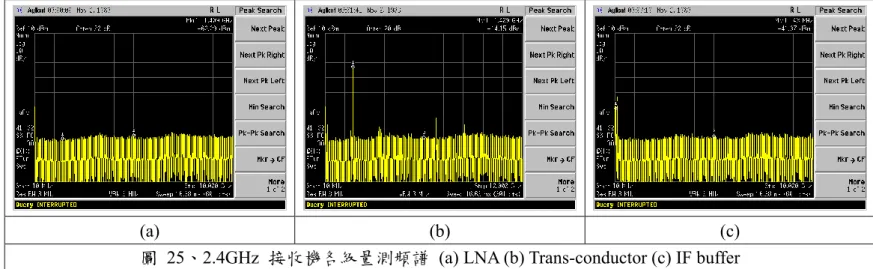

整合晶片之量測結果如下:

圖 24、24-/2.4-GHz 雙模共存感測器接收機量測頻譜

(a) (b) (c)

圖 25、2.4GHz 接收機各級量測頻譜 (a) LNA (b) Trans-conductor (c) IF buffer

從圖25 可看出本晶片出現振盪現象,由於 24 GHz 接收機部分已在前一梯次單獨驗證,雖然有操 作頻率偏移的現象但電路是可正常運作,接著從圖26 各級獨立量測結果來判斷,可推測是 2.4 GHz 接收機部分之第二級的Trans-conductor 電路出現振盪,導致整個系統運作失常。

五、結論

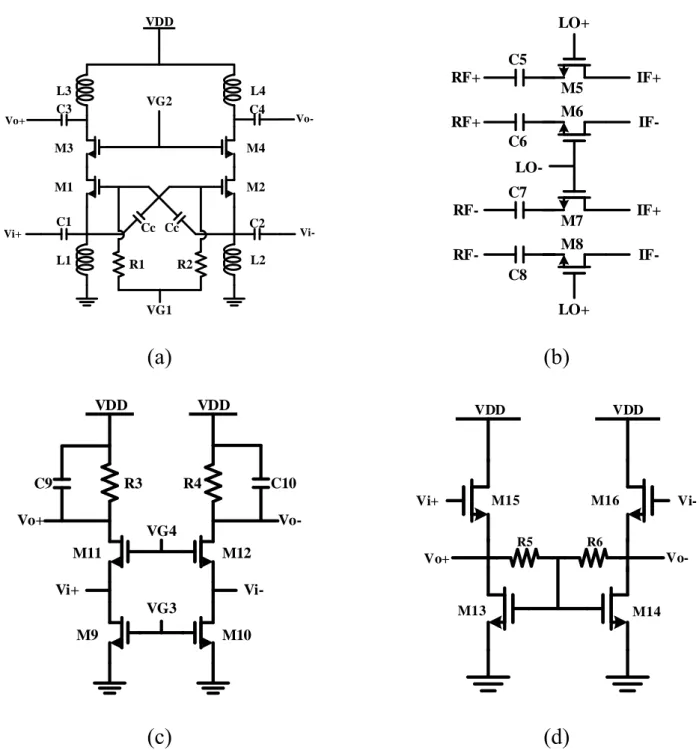

本專題計畫執行兩年,依計畫完成24 GHz 接收機(LNA+VCO+Mixer) 之各子電路設計驗證及整 合電路晶片設計。2.4 GHz 接收機亦完成各子電路設計驗證及整合電路晶片設計。最後在整合 2.4 GHz 及 24 GHz 的設計時,因為 2.4 GHz 接收機部分之第二級的 Trans-conductor 電路出現振盪,而使 得此雙頻接收機的量測無法正常。礙於計畫時程已到期,故目前結論因電路振盪而導致計畫尚未達成 雙頻接收機的目標。但目前仍有針對2.4 GHz 接收機部分下線再進行一次驗證(CIC T18-109C)。由於 晶片尚未製作完成,於此先附上電路架構與模擬結果供參考。 Cc Cc L4 L3 C4 C3 C2 VDD Vi-Vi+ C1 VG2 VG1 R2 L1 R1 L2 Vo+ Vo-M1 M3 M2 M4 C8 C7 C5 LO-IF+ LO+ M5 RF+ IF-M6 C6 RF+ IF+ M7 RF- IF-LO+ M8RF-(a)

(b)

C10 R3 C9 VG3 VG4 M10 M9 R4 Vi-Vi+ M12 M11 VDD VDD Vo-Vo+ R6 R5 M14 M13 Vi-M16 M15 VDD VDD Vo-Vo+ Vi+(c)

(d)

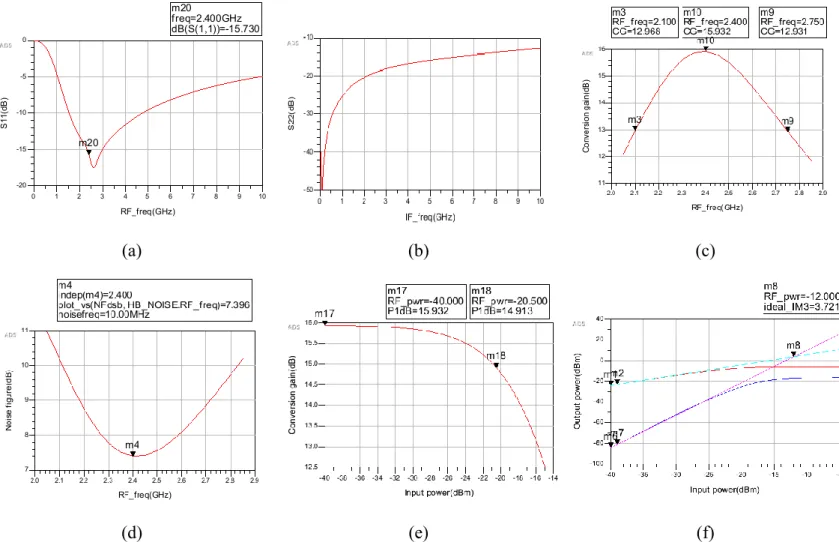

有別於上一個晶片使用LNA 及 Trans-conductor,這一次的 LNA 架構選用將兩者結合在一起的 LNTA,好處為避免兩級電路之間可能造成的振盪現象,且能更有效的降低直流功率消耗。至於混頻 器與緩衝放大器部分則無太大更改,幾乎沿用上次架構。模擬結果如下:

(a) (b) (c)

(d) (e) (f)

圖 27、2.4 GHz 接收機模擬結果(a) S11 (b) S22 (c) conversion gain (d) Noise figure (e) P1dB (f) IIP3

表六 2.4 GHz 接收機模擬規格比較表

2.4 GHz CMOS Receiver

Parameter Pre-sim. Post-sim.

Input return loss (dB) @ 2.4 GHz -10.3 -15.7

Output return loss (dB) @ 0.2 GHz >>-10 >>-10

Voltage Gain (dB) @ 2.4 GHz 17.77 15.92

NF(dB) @ 10 MHz 6.14 7.4

IIP3 (dBm) -14 -12

六、參考文獻

[1] 5G spectrum recommendations - April 2017. Available on:

http://www.5gamericas.org/files/9114/9324/1786/5GA_5G_Spectrum_Recommendations_2017_FINAL.pdf

[2] Sheng-Fuh R. Chang, Wen-Lin Chen, et al., “A dual-band RF Transceiver for multistandard WLAN applications,”

IEEE Trans. Microw. Theory Tech., vol. 53, no. 3, pp. 1048-1055, Mar. 2005.

[3] Hung-Sheng Hsu, Qiu-Yue Duan, Yu-Te Liao, “A low power 2.4/5.2 GHz concurrent receiver using current-reused architecture,” IEEE International Symposium on Circuits and Systems, 2016, pp. 1398-1401.

[4] Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications, 2016.

[5] Joo Leong Tham, Mihai A. Margarit, Bernd Pregardier, et al., “A 2.7-V 900-MHz/1.9-GHz dual-band transceiver IC for digital wireless communication,” IEEE J. Solid-State Circuits, vol. 34, no. 3, pp. 286-291, Mar. 1999.

[6] Gitae Pyo, Jaemo Yang, Choul-Young Kim, and SongCheol Hong, “K-Band single-path dual-mode CMOS transmitter for FMCW/UWB Radar,” IEEE Microw. Wireless Compon. Lett., vol. 26, no. 10, pp. 858-860, Oct. 2016.

[7] Christian Bredendiek, Nils Pohl, Timo Jaeschke, et al., “A 24GHz wideband single-channel SiGe bipolar transceiver chip for monostatic FMCW radar systems,” European Microwave Integrated Circuits Conference, Oct.2012, pp. 309-312.

[8] Juntaek Oh, Jingyu Jang, and Songcheol Hong, “Millimeter wave UWB pulse radar front-end ICs,” Global Symposium

on Millimeter Waves, May 2015.

[9] Ali M. Niknejad, Hossein Hashemi, mm-Wave Silicon Technology 60GHz and Beyond, Springer, 2008. [10] Yikun Yu, et al., Integrated 60GHz RF Beamforming in CMOS, Springer, 2011.

[11] M. Reil, G. Lloyd, Millimeter-wave beamforming: antenna array design choices & characterization white paper, Rohde & Schwarz GmbH & Co. KG, München, 2016.

[12] Hong-Teuk Kim, et al., “A 28GHz CMOS direct conversion transceiver with packaged antenna arrays for 5G cellular system,” IEEE Radio Frequency Integrated Circuits Symp., July 2017, pp. 69-72.

[13] Bodhisatwa Sadhu, Yahya Tousi, et al., “A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications,“ IEEE J. Solid-State Circuits, vol. 52, no. 12, pp. 3373-3391, Dec. 2017.

科技部補助專題研究計畫成果自評表

請就研究內容與原計畫相符程度、達成預期目標情況、研究成果之學術或應用價

值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性)

、是否適

合在學術期刊發表或申請專利、主要發現(簡要敘述成果是否具有政策應用參考

價值及具影響公共利益之重大發現)或其他有關價值等,作一綜合評估。

1. 請就研究內容與原計畫相符程度、達成預期目標情況作一綜合評估

□ 達成目標

■未達成目標(請說明,以

100 字為限)

□ 實驗失敗

□ 因故實驗中斷

■ 其他原因

說明:依計畫規劃完成多項

24 GHz 和 2.4 GHz 接收機之各別子電路及整合

電路晶片設計及晶片製作量測。唯最後一顆雙頻收發機的晶片整合,因

2.4 GHz

接收機部分之第二級

Trans-conductor 電路產生振盪現象,而使得晶片無法順利

量測特性。

2. 研究成果在學術期刊發表或申請專利等情形(請於其他欄註明專利及技轉之

證號、合約、申請及洽談等詳細資訊)

論文:□已發表□未發表之文稿 ■撰寫中 □無

專利:□已獲得□申請中 ■無

技轉:□已技轉□洽談中

■無

其他:(以

200 字為限)

於本計畫的執行中,我們亦探究本實驗室所開發的六角形電感應用於壓

控振盪器及低雜訊放大器電路中,並獲得電路設計成果。應用於壓控振盪器

的部分,我們已於第一年時發表於

APMC 2019 的研討會。目前我們亦完成利

用一個

3 級放大器電路並結合正回授電路架構來驗證此六角電感有優異的抑

止電磁輻射干擾的效果。目前正在整理資料,準備投稿事宜。

3. 請依學術成就、技術創新、社會影響等方面,評估研究成果之學術或應用價

值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性,以

500

字為限)。

本計畫旨在開發一個常用的

2.4-GHz 和 24-GHz ISM 頻帶共存的感測

器接收器,以便提供未來感測器網路中接收機的另一項選擇。利用將

24-GHz

毫米波前端電路的降頻作用將其訊號降頻到

2.4-GHz,然後,再利用一個切換

開關電路選擇與

2.4-GHz 前端電路合併以達電路共用的目的並期降低晶片成

本。我們預期這樣的雙頻接收機概念是有助於未來

5G 通訊世代的一些感測

器的應用。

在本計畫的執行成果上,雖在

24 GHz 接收機端是有正常運作,但由於後

端的

2.4 GHz 接收機出現振盪現象而導致整個系統無法順利量測。藉由此計

畫除了讓本實驗室學生累積了在毫米波頻段電路的設計及電磁模擬經驗,也

學習到了如何整合雙接收機電路於系統中。

4. 主要發現

本研究

具有政策應用參考價值: ■

否 □是,建議提供機關_______

(勾選「是」者,請列舉建議可提供施政參考之業務主管機關)

本研究具影響公共利益之重大發現:■否 □是

說明:(以 150 字為限)

附件六

科技部補助專題研究計畫出席國際學術會議心得報告

日期:108 年 12 月 23 日一、參加會議經過

此出國報告書為此次參加 IEEE MTT-S (微波理論及技術協會) 在新加坡舉辦的亞洲太平洋微 波 研 討 會 (Asia-Pacific Microwave Conference,APMC2019) 的學習心得。此次會議舉辦日期為 12/10~12/13 四天,地點位於新加坡金沙國際會議中心。筆者本人於 12/9 搭乘飛機至新加坡轉市區 巴士到新加坡G 旅店(Hotel G Singapore)以便於參加 12/10 早上開始舉行的開幕儀式。 在 12/10 早上搭捷運到 Bayfront 站下車,從車站走一走就連接到濱海灣金沙購物商城,搭電梯 到 4 樓就能看到會議中心,我先去簽到和拿到展覽的相關資料和會議時程再去熟悉環境、拍照紀 念,之後是在濱海灣金沙購物商城逛街,欣賞異國氛圍和風景,且準備好在12/13 下午的演講。 在 12/13 整天,一早我就在金沙國際會議中心裡參加各個時段的會議,包括Microwave/mm-計畫編號

MOST 107-2221-E-006-200-MY2

計畫名稱

2.4-/24-GHz 雙頻共存感測器接收機射頻前端電路之整合設計

出國人員

姓名

李東諺

服務機構

及職稱

國立成功大學電機系

碩士班研究生-兼任助理

會議時間

108 年 12 月 10 日

至

108 年 12 月 13

日

會議地點

新加坡金沙國際會議中心

會議名稱

(中文) 2019 亞洲太平洋微波研討會

(英文) 2019 Asia-Pacific Microwave Conference

發表題目

(中文) 具有諧波反向散射檢測功能的 2.4 GHz 射頻能量收集整流器晶

片

(英文) 2.4 GHz RF Energy Harvesting Rectifier Chip With Harmonic

Backscattering Detection Capability

wave Applications、RF Wireless Power for Low Power Applications、Microwave Biomedical applications, 在這些時間,我看到各國的演講方式和精彩的內容,聽到各式各樣口音,尤其對日本來的講者的口 音最為特別,也發現並不是每位講者的英文口說都很流利,讓我更有信心,最後會議是 RF and Microwave ICs 也是我要上台報的會議,在我演講結束後,雖然台下觀眾沒有舉手問問題,但主席 有發問給我空間表達,剛好問的問題有所準備,因此順利答完下台,聽完一整天的會議使我的知識 又往前了一大步。

二、與會心得

此次出國參加 APMC,了解到除了專業知識還有許多專業知識需學習外,英語的表達仍需多 加練習,但由另一個角度看,因為微波領域分為主動電路和被動電路研究,其涵蓋甚廣,這次出國 發表的經驗可以讓我了解在國際上,不僅專業知識要充足,即使自己的研究沒有涵蓋,仍需盡力去 了解,充實自己在專業領域的廣度,更重要的是要有英語口說能力,並且勇於主動舉手發問、表達 自己觀點,因為是第一次出國,心中難免產生不安和激動,但在整個會議的過程中,看到各國來的 新手或老手,大家都是做好準備把知識分享出來,使我開闊視野吸收到了不少知識,很感恩有一次 這樣的經驗。三、發表論文全文或摘要

Chiao-Chieh Yang, Dong-Yan Li and Tzuen-Hsi Huang, " 2.4 GHz RF Energy Harvesting

Rectifier Chip With Harmonic Backscattering Detection Capability," in 2019 IEEE

Asia-Pacific Microwave Conference (APMC), Singapore, 2019.

本次發表論文為我們設計了一個 2.4 GHz 射頻能量收集整流器晶片,該晶片可以通過反向散射二 次諧波信號進行識別。對於傳統的射頻能量整流器,反向散射諧波通常被視為可用能量的損失部分。 與傳統的整流器不同,我們提出了一種集成整流器電路設計,同時結合了能量收集和諧波位置檢測功 能。該整流器在位置檢測模式下工作時具有較強的反向散射諧波,而在能量收集模式下則具有更好的 功率轉換效率(PCE)。

圖1. 具有諧波反向散射位置檢測功能的能量收集器的架構圖 所提出的能量收集器的框圖如圖1 所示。假定將直流輸出電壓施加到 PMOS 開關的柵極以連接或 斷開二次諧波諧振器。 整流器最初處於位置檢測模式,由於輸出電壓為 0 V,因此 PMOS 開關處於導 通狀態,較強的二次諧波被反向散射。 隨著基波信號的充電,輸出電壓逐漸飽和,然後整流器進入能 量收集模式,因為PMOS 開關關閉,反向散射的二次諧波變得更低,並且能量收集電路的 PCE 增大。 採用的2.4 GHz 能量收集整流器電路由三級 FGCC 整流器和一對可開關控制的並聯 LC 諧振器構成, 如圖2.所示。通過在第一級 FGCC 整流器中使用可開關控制的並聯 LC 諧振器, 開關 Msw1 / Msw2 的 截止電阻大於Mp1 / Mp2。 它確保幾乎沒有信號流過開關,因此整流器在能量搜尋模式下可以獲得更 高的PCE。 在開始時,當 Mp1 / Mp2 打開時,部分輸入功率將分配給諧振電路,以增強位置檢測模式 下的二次諧波反向散射。 圖2. 二次諧波 LC 諧振器集成的 2.4 GHz 整流器的電路

為了公平地評估能量收集整流器電路設計的優勢和性能,我們提出了兩個 FOM 作為整流器電路 性能的評估指標,以進行公平的比較。 通過考慮整流器的最大 PCE(百分比)和輸出電壓為 1 V 時的 靈敏度(以mW 為單位)來設置第一個 FOM(FOM1)。儘管通常將靈敏度標識為系統開始向其提供的 最小輸入功率在工作中,可能很難獲得有用的輸出電壓 Vout 來驅動一般的晶片正常工作。 因此,我 們建議Vout = 1 V 時的輸入功率為靈敏度,因為許多當前的低功率電路都設計有大約 1V 的電源電壓。 此外,我們新引入了第二個FOM(FOM2)的輸入功率範圍(IPR)。 考慮到各向同性 RF 發射源 的最大發射功率為 1 W,並且接收器使用 2.15 dBi 定向增益的半波長偶極天線。 根據 Friis 的傳輸公 式,在遠場輻射假設下,當傳輸距離是波長的10 倍時,接收機可以接收到約 0.1 mW(即-10 dBm)。 因此,對於所需的輸出負載,我們將有效IPR(以 dB 為單位)定義為 PCE = 10%的最小輸入功率與-10 dBm 的輸入功率之間的功率範圍。 圖3.(a)和(b)分別示出了在能量收集模式和位置檢測模式下的 PCE 的測量結果。顯然,可 以在能量收集模式下獲得更好的PCE。 在能量收集模式下,當輸入功率為-7.2 dBm 並且負載為 10k Ω時,最大PCE 達到 72%。 當負載為 100kΩ時,在-19.4 dBm 輸入功率下,峰值 PCE 為 60%。 圖 4.顯示了能量搜尋模式下的輸出電壓,當輸入功率為-7.2 dBm,負載為 10kΩ時,輸出電壓為 1.2V。 圖5. 顯示出了隨著開關的柵極電壓增加的二次諧波功率變化,當輸入功率為+5 dBm 時,整流器可以 提供接近40 dB 的二次諧波信號功率差用於位置檢測,當輸入功率為-5 dBm 時,其檢測差仍約為 20 dB,相對於 100kΩ負載,測得的輸入功率範圍為 14 dB。 表一總結了這項工作與以前的論文[1]-[3] 之間的電路性能比較。 量測到整流器晶片的 FOM1 和 FOM2 分別為 39.97 和 54.97 dB。 圖3. 測量整流器的 PCE 在(a)能量收集模式和(b)位置檢測模式下 𝐹𝑂𝑀1 = 𝜂𝑚𝑎𝑥(%) − Sensitivity(dBm)@ 𝑉𝑜=1 V

圖4. 在能量收集模式下測得的整流器輸出電壓

圖5. 在 100kΩ負載下具有可調 PMOS 開關柵極偏置的二次諧波的測量輸出功率

本次設計之晶片照相圖如圖6.,採用 TSMC 90 nm 製程,面積為 1.26mm × 0.65mm。測試版 PCB 照相圖如圖7.,使用 FR4 (two-layer)板材量測,面積為 50 mm × 82.5 mm。 圖6. 晶片照相圖 圖7. PCB 照相圖

四、建議

(無)

五、攜回資料名稱及內容

研 討 會 會 議 議 程 及 相 關 論 文 資 料 的 隨 身 碟( 大 會 開 放 與 會 人 員 直 接 由 網 站 下 載 壓 縮 檔 案 http://www.apmc2019.org/)六、其他

(無)

科技部補助專題研究計畫出席國際學術會議心得報告

日期:109 年 10 月 23 日

一、參加會議經過

此出國報告書為本人參加 IEEE MTT-S (微波理論及技術協會) 在英國倫敦舉辦的 IEEE 2019 無線能量傳輸研討會 (Wireless Power Transfer Conference, WPTC2019)的學習心得。事實上,今年 的WPTC 大會是與 IEEE PELS Workshop on Emerging Technology: Wireless Power 合辦, 大會名稱 或稱Wireless Power Week (WPW 2019)。此次會議舉辦日期為 6/17~6/21 五天,地點位於英國倫敦 的IET London: Savoy Place。本人於 6/16(日) 於台北桃園國際機場搭乘飛機至泰國曼谷機場再轉飛 英國倫敦希斯洛機場都並搭乘地鐵到下榻的飯店(Kyoto Garden Palace)以便於參加 6/17 早上開始舉 行的Short Course。之後,參加接續四天的研討會議議程。因會議結束後適逢周末,故安排個人行 程拜訪英國利物浦大學電機系周佳峰老師並參觀他的研究室。隨後在周一時間返回倫敦參觀大英 博物館,並於 6/25(二) 搭機返回台灣。這之間的插曲是適逢國內長榮航空的罷工事件,所以改搭 中華航空公司的飛機回到台灣。下列照片是大會於閉幕儀式時邀請與會人士上台照相的相片,我是 站在照片最後排最右側第三位(旁邊有人舉手)。

計畫編號

MOST 107-2221-E-006-200-MY2

計畫名稱

2.4-/24-GHz 雙頻共存感測器接收機射頻前端電路之整合設計

出國人員

姓名

黃尊禧

服務機構

及職稱

國立成功大學電機系

教授

會議時間

108 年 6 月 17 日至

108 年 6 月 21 日

會議地點

英國倫敦

會議名稱

(中文) IEEE 2019 無線能量傳輸研討會

(英文) IEEE 2019 Wireless Power Transfer Conference (WPTC2019)

發表題目

(中文) 應用於無線傳能 IC 設計之微機電蜂巢型電感電磁輻射抑制

(英文) EMI Suppression of MEMS Honeycomb-Shaped Inductor on

Oscillators for Wireless-Powered IC Design

(大會閉幕照片)

第一天參加的 Short Course 的地點在倫敦帝國學院(Imperial College London),共計有十個講題。 這十個講題分別是: Practical Rectenna Design, Multi-band Rectenna Data for Radio Frequency Energy, Enviroment aware battery-less IOT Frontend, Battery-less UWB indoor location is the way forward for industry 4.0, How to detect position of user to keep high beam efficiency on wireless power transfer, Optimize, Learn and Prototype wireless communications and power transfer, Combining backscatter communication with WPT, the new wireless power communication paradigm, Inductive resonant WPT: design equations for different operative regimes, Analytical and numerical design of non-static WPT system, and Wireless grid interation of EVs for V2G application。整天的課程,個人覺得每一場都獲益匪淺。 特別是這些議題對於射頻獵能的議題皆有實質的助益。

如上說明,WPW 2019 包含了兩個協會的會議,並分為四個 Tracks 進行。此四個 Tracks 分 別 是: Track 1 (WoW1/ WPTC1): Technologies for Wireless Power ; Track 2 (WoW2/WPTC2): Applications of Wireless Power Transfer and Energy Harvesting ; Track 3 (WPTC3): Transmitters, Receivers, Circuits and Systems for Wireless Power Transfer and Energy Harvesting ; Track 4 (WoW3/WPTC4): Devices, Systems and Technologies Related to Wireless Power Transfer and Energy Harvesting。由於本人的研究興趣與專長還是偏向於射頻獵能技術(RF Energy Harvesting Technology) 方面,所以除了大會將兩個協會共邀的重要演講外,我還是選擇參加WPTC 的 Sessions 為主。也

就是說以相對傳能能量小於 5W 的研究為分水嶺。大功率者如大會這次的重點技術為汽車充電技

術,小功率者如手機充電技術。我則參加偏重於小功率傳輸的議題。換言之,本人參加的Sessions 有: Systems for power and data transfer, Novel rectifier solutions, Wearable and biomedical systems, Microwave power converters, …等等。其中,個人覺得有幾場的邀請演講是給自己印象最深刻的,

如: Witricity 公司的 CEO, Alex Gruzen, 演講的 Wireless Charging: Driving EV Adoption and the Autonomous Future 和 Raython 公司的 Hooman Kazemi 演講的 Millimeter Wave Wireless Power Transmission-Technologies and Applications。

在我們實驗室的論文發表方面,此次我們的論文是互動式海報展示與討論(編號: WPP83)。時 間是在大會期間週四的下午。由於這篇論文主要是探討微機電蜂巢型電感對於壓控振盪器的 EMI 抑制效果對無線傳能IC 的展示,相對於其他研究學者而言可能比較陌生,所以會場上詢問的問題 僅有兩人。但我也盡可能地介紹論文的想法內容。另一方面,趁此機會我也拜訪了會場中做 RF Energy Harvesting 的研究者,詢問他們對於如何評估整流晶片的效率? 對於現有學術論文報告晶 片整流效率的公式看法。但獲得的答案是大部分說是要我注意整體系統的效率。此外,我也瀏覽了 所有在會場張貼的海報,看到部分國外學生的研究成果其實也満豐富的。 最後,這次出國會後的個人行程是到利物浦大學電機系拜訪周佳峰老師的研究室參觀行程。除 了有機會跟他的指導學生對談及展示他的研究(無線傳能)成品外,也參觀了實驗室。印象最深刻的 就是實驗室除了一般實驗室有量測室外,還有一間頗大的微波散射實驗室,可測試一般汽車的微波 散射的響應。利物浦大學亦有產出諾貝爾的得獎者。當然,兼具有古老建築及現代建築的大學校園, 讓人對西方科學研究的點點滴滴不得不讚賞。

二、與會心得

此次出國參加 WPTC 2019 最大的收穫在第一天的 Short Course。各個講師的投影片內容也都 非常豐富,實在令我自己非常的佩服。當然,攜回的講義冊對於我自己在教學上也有極大的助益。 在研討會上,因為所討論的議題就更廣泛,有些研究議題就超出了我自己的理解範圍。但整體而言, 在參加的過程中,自己也學習到了一些新的概念。特別是一些邀請的演講,有些數據資料並不容易 在網路上看到的,這讓我自己覺得受益匪淺。三、發表論文全文或摘要

H. Wu, P. Wang, T. Huang and S. Yang, "EMI Suppression of MEMS Honeycomb-Shaped

Inductor on Oscillators for Wireless-Powered IC Design," 2019 IEEE Wireless Power

Transfer Conference (WPTC), London, United Kingdom, 2019, pp. 565-568, doi:

10.1109/WPTC45513.2019.9055652.

“This paper shows the operation of honeycomb-shaped inductors with or without

micro-electromechanical systems (MEMS) post-process in Ku-band and their application to VCOs

in terms of circuit performances like crosstalk and injection pulling effects. The unique

layout pattern of honeycomb-shaped inductor can provide almost omnidirectional

electromagnetic interference (EMI) suppression to adjacent noise interferes. In this work,

MEMS process is adopted to remove the silicon substrate for improving the inductor quality

factor. The honeycomb-shaped inductors either with or without MEMS post-process and the

single-turn octagonal inductor are implemented to Ku-band VCOs operated at 17 GHz,

respectively, with the same dc power consumption of 5.29 mW at VDD = 1.8 V, as an

experimental set for comparison. The experiment results indicate that the

honeycomb-shaped inductor exhibits better injection pulling mitigation than the single-turn octagonal

inductor by more than 15 dB. This feature would be helpful to the design of

wireless-powered sensor integrated circuits (ICs) with more EMI suppression capability in 5G

communication environment.”

透過本計畫的支持下線並利用執行計畫下的蜂巢型電感架構,此論文重要的成果,如下附圖所示。 分別是: 電路圖 晶片照相圖,和與其他過去研究論文的比較表。四、建議: (無)

五、攜回資料名稱及內容:

研討會會議議程及相關之論文集之隨身碟一支及短期課程紙本講義 一份。六、其他: (無)

PERFORMANCE COMPARISONS OF VCO_2 WITH PREVIOUS KU/K-BAND VCOS.

Reference CMOS Technology VDD (V) Frequency Range (GHz) (%) Phase Noise @ Δf (dBc/Hz) Pdc* (mW) FOM** (dBc/Hz) FOMT# (dBc/Hz) [6] 180 nm 2 14.75 ~ 15 (1.7%) -112.2 @ 1 MHz 52 -178.56 -163.17 [7] 180 nm 1.5 24.7 ~ 25.3 (2.4%) -103.1 @ 1 MHz 13.2 -179.85 -167.46 [8] 180 nm 1.8 16.6 ~ 17.4 (4.7%) -107 @ 1 MHz 7.2 -181 -174.48 This work (VCO_2) 180 nm 1.8 16.71 ~ 17.52 (4.7%) -103.53 @ 1 MHz## 5.29 -180.74 -174.24

* VCO core only; ** FOM = L(Δf)-20log(fo/Δf)+10log(Pdc/1mW) # FOM

T = L(Δf)-20log{(fo/Δf)(FR/10%)}+10log(Pdc/1mW)

科技部補助專題研究計畫出席國際學術會議心得報告

日期:109 年 10 月 23 日

一、參加會議經過

此出國報告書為本人參加 IEEE MTT-S (微波理論及技術協會) 在英國倫敦舉辦的 IEEE 2019 無線能量傳輸研討會 (Wireless Power Transfer Conference, WPTC2019)的學習心得。事實上,今年 的WPTC 大會是與 IEEE PELS Workshop on Emerging Technology: Wireless Power 合辦, 大會名稱 或稱Wireless Power Week (WPW 2019)。此次會議舉辦日期為 6/17~6/21 五天,地點位於英國倫敦 的IET London: Savoy Place。本人於 6/16(日) 於台北桃園國際機場搭乘飛機至泰國曼谷機場再轉飛 英國倫敦希斯洛機場都並搭乘地鐵到下榻的飯店(Kyoto Garden Palace)以便於參加 6/17 早上開始舉 行的Short Course。之後,參加接續四天的研討會議議程。因會議結束後適逢周末,故安排個人行 程拜訪英國利物浦大學電機系周佳峰老師並參觀他的研究室。隨後在周一時間返回倫敦參觀大英 博物館,並於 6/25(二) 搭機返回台灣。這之間的插曲是適逢國內長榮航空的罷工事件,所以改搭 中華航空公司的飛機回到台灣。下列照片是大會於閉幕儀式時邀請與會人士上台照相的相片,我是 站在照片最後排最右側第三位(旁邊有人舉手)。