國

立

交

通

大

學

電機學院 電機與控制學程

碩

碩

碩

碩

士

士

士

士

論

論

論

論

文

文

文

文

操作於次臨界電壓區

操作於次臨界電壓區

操作於次臨界電壓區

操作於次臨界電壓區之

之

之

之數位

數位

數位

數位動態電壓調整系統

動態電壓調整系統

動態電壓調整系統

動態電壓調整系統

Dynamic Voltage Scaling for the Digital

Sub-Threshold Operation

研 究 生:林佳宏

指導教授:蘇朝琴 教授

中

中

中

中 華

華

華

華 民

民

民

民 國

國

國

國 一百

一百 年

一百

一百

年

年

年 六

六

六

六 月

月

月

月

操作於次臨界電壓區之數位動態電壓調整系統

Dynamic Voltage Scaling for the Digital Sub-Threshold

Operation

研 究 生:林佳宏 Student : Chia Hung Lin

指導教授:蘇朝琴 教授 Advisor : Chau Chin Su

國 立 交 通 大 學

電機學院 電機與控制學程

碩 士 論 文

A Thesis

Submitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in

Electrical and Control Engineering June 2011

Hsinchu, Taiwan, Republic of China

操作於次臨界電壓區之數位動態電壓調整系統

研究生 :林佳宏 指導教授 : 蘇朝琴 教授

國 立 交 通 大 學 電 機 學 院 電 機 與 控 制 學 程 碩 士 班

摘 要

本論文提出一個動態電壓調整系統(Dynamic Voltage Scaling),我們藉由動態的調整 數位電路上的工作電壓來克服當數位電路操作於次臨界電壓時,製程與溫度的變化對數 位電路工作頻率造成的影響。我們讓數位電路允許的最高工作頻率能夠不因操作在次臨 界電壓的條件下而產生劇烈的變化,使數位電路能夠工作在符合操作頻率要求的最低工 作電壓以降低能量消耗。此系統是使用鎖頻迴路的概念來完成(Frequency Loop Lock), 利用頻率偵測器(Frequency Detector)來比較數位電路內的關鍵路徑(Critical Path)與外部 參考頻率兩者之間的頻率高低後,適當的調整數位電路的操作電壓以改變關鍵路徑的延 遲時間,使數位電路能夠工作在符合外部參考頻率要求的最低工作電壓,而不受製程與 溫度變化的影響。動態電壓調整系統中的電壓調整電路,是使用交換式電容來當作電壓 轉換器,使用交換式電容作為電壓轉換器的好處是,不需要使用到電感,並可將電容直 接在 IC 內部製作完成,讓整個系統更容易達成系統晶片整合的目的。所提出的電路架 構在 TSMC 0.18µm 1P6M CMOS 製程下模擬,經模擬結果顯示數位電路的操作電壓漣 波可小於 1mV,工作頻率誤差小於 3%。 關鍵字: 動態電壓調整、鎖頻迴路、交換式電容、次臨界電壓

Dynamic Voltage Scaling for the Digital Sub-Threshold

Operation

Student: Chia Hung Lin Advisor: Dr. Chau Chin Su

Department of Electrical and Control Engineering

National Chiao Tung University

Abstract

In this thesis we propose a dynamic voltage scaling system, we have by dynamically adjust the digital circuit operating voltage to overcome frequency impact when the digital circuit is operating in the sub-threshold region with process violation and temperature change. And maintain the operating frequency will not have a dramatic change due to operate in the

sub-threshold region. This system use the concept of frequency loop lock, using the frequency detector to compare the critical path of the digital circuits and the reference frequency. Then appropriate adjustments to the operating voltage of the digital circuit to change the critical path delay, so that digital circuits can work at the reference frequency in minimum operating voltage and not restricted by the process and temperature variations. In dynamic voltage scaling system we use a switch capacitor voltage converter to adjust the operating voltage, the use of switched capacitor voltage converter as a benefit is not required to use the inductor. The capacitance can produced directly in the IC, SoC integration is easier to achieve the purpose. The proposed circuit architecture in TSMC 0.18µm 1P6M CMOS process simulated, the simulation results show that the operation of the digital circuit voltage ripple can less than 1mV, frequency error is less than 3%.

Keyword: Dynamic Voltage Scaling, Frequency Loop Lock, Switch-Capacitor, Sub-Threshold voltage

誌

誌

誌

誌 謝

謝

謝

謝

首先要感謝的是我的指導教授 蘇朝琴教授,這幾年的辛勤指導,讓我在知識與技術上 有了明顯的成長。接下來要感謝的是博士班的盈杰學長、老師的助理豐文小姐,以及公司 的同事們文賓、文男、啟鐘,他們時常熱心的跟我討論、在我遇到瓶頸時能夠花時間與我 討論。當然還有我的學長與同學們:偉勇、東樺、貴園、俊褀、泰綸、聖昕、建玶,在課 業上互相討論,在研究的過程中互相勉勵與打氣,感謝大家,因為有你們,讓我研究生涯 不止在求得學識上的精進,也有了互相扶持的伙伴。 最後要感謝我的父親、母親,感謝你們的鼓勵與陪伴,能夠支持我繼續的進修,讓我 能夠順利的完成碩士學位,謝謝你們的支持和照顧,你們的鼓勵成為我求學生涯最大支柱, 讓我能夠順利完成學業,謝謝。 林佳宏 2011/06/01目錄

目錄

目錄

目錄

摘

摘

摘

摘 要

要

要

要 ... I

Abstract ... II

誌

誌

誌

誌 謝

謝

謝

謝 ... III

目錄

目錄

目錄

目錄 ... IV

表目錄

表目錄

表目錄

表目錄 ... VI

圖目錄

圖目錄

圖目錄

圖目錄 ... VII

第一章

第一章

第一章

第一章、

、

、

、緒論

緒論

緒論

緒論 ... 1

1.1 簡介 ... 1 1.2 研究動機 ... 2 1.3 論文結構 ... 2第二章

第二章

第二章

第二章、

、

、

、次臨界電壓下的電路特性

次臨界電壓下的電路特性

次臨界電壓下的電路特性

次臨界電壓下的電路特性 ... 4

2.1 功率消耗 ... 4 2.2P、NMOS 電流驅動能力 ... 102.3 電壓轉換曲線(VOLTAGE TRANSFER CURVE) ... 12

2.4 次臨界電壓下的延遲速度 ... 14 2.5 總結 ... 18

第

第

第

第三

三

三

三章

章

章

章、

、

、

、動態電壓調整系統

動態電壓調整系統

動態電壓調整系統

動態電壓調整系統 ... 19

3.1 系統架構簡介 ... 19 3.2 交換式電容電壓轉換器 ... 203.3 有限狀態機(FINITE STATE MACHINE) ... 24

3.4 頻率偵測器(FREQUENCY DETECTOR) ... 26

3.5 電壓準位轉換器(VOLTAGE LEVEL SHIFT) ... 27

3.6 壓控環型振盪器(VOLTAGE CONTROL RING OSCILLATOR) ... 29

3.7 負載電路 ... 30

第

第

第

第四

四

四

四章

章

章

章、

、

、

、模擬結果

模擬結果

模擬結果

模擬結果 ... 35

4.1 系統行為模擬 ... 35 4.2 環型振盪器之電壓頻率曲線 ... 38 4.3 理想電流負載與數位電路負載的差異 ... 40 4.4C2 改變時對工作頻率與電壓變化的影響 ... 43 4.5C1 改變時對工作頻率與電壓變化的影響 ... 48第五章

第五章

第五章

第五章、

、

、

、結論

結論

結論

結論 ... 51

參考文獻

參考文獻

參考文獻

參考文獻 ... 52

附錄

附錄

附錄

附錄 ... 54

表目錄

表目錄

表目錄

表目錄

表格 2.1N/PMOS 電流驅動能力比例 ... 11 表格 3.1 交換式電容電路參數表 ... 21 表格 3.2 穩態 VO與 C1 關係表 ... 23表格 3.3TAPS FOR MAXIMUM-LENGTH LFSRCOUNTERS ... 33

表格 4.1 負載電路消耗電流 ... 36 表格 4.2 預期負載電路操作於 10UA 時的GATE COUTE數量 ... 36 表格 4.3 頻率偵測器 0.8%誤差對負載電壓的影響 ... 39 表格 4.4 動態電壓調整系統頻率 3%誤差對負載電壓的影響 ... 40 表格 4.5C2 值對 VC2P-P的影響 ... 44 表格 4.6C2 改變時的最大頻率誤差與電壓變化 ... 47

圖目錄

圖目錄

圖目錄

圖目錄

圖 2-1 靜態電流示意圖 ... 5 圖 2-2 次臨界電流與二極體逆向電流示意圖 ... 6 圖 2-3 電晶體 IDS對 VGS曲線量測電路 ... 6 圖 2-4 以對數的方式表示電晶體的 IDS對 VGS曲線 ... 7 圖 2-5 反向器充放電模型 ... 7 圖 2-6 含輸出入曲線的反向器充放電模型 ... 9圖 2-7DRIVING CURRENT OF P、NMOS IN MINIMUM SIZE ... 10

圖 2-8DRIVING CURRENT OF P、NMOS ... 11

圖 2-9 操作在次臨界電壓反向器的電壓轉換曲線(P:N=4:1) ... 12 圖 2-10TT、SF、FS 三種不同製程變異下,反向器的電壓轉換曲線(P:N=4:1) ... 13 圖 2-11 三種不同溫度下,反向器的電壓轉換曲線(P:N=4:1) ... 13 圖 2-12 七級環型振盪器 ... 14 圖 2-13 電壓對環型振盪器的影響 ... 16 圖 2-14 溫度對環型振盪器的影響 ... 17 圖 2-15 製程對環型振盪器的影響 ... 18 圖 3-1 動態電壓調整方塊圖 ... 20 圖 3-2 交換式電容電路 ... 20 圖 3-3C1 電容可調之交換式電容電路 ... 22 圖 3-4 開關NON-OVERLAP線路 ... 24 圖 3-5 雙向移位暫存器 ... 25 圖 3-6 頻率偵測器 ... 26 圖 3-7 轉態速度較快之電壓準位轉換器 ... 27 圖 3-8 轉態速度較慢之電壓準位轉換器 ... 28 圖 3-9 靜態時序分析 ... 29 圖 3-10 壓控環型振盪器 ... 30 圖 3-11 負載電路 ... 31 圖 3-12 三位元線性反饋位移暫存器 ... 32 圖 3-131-BIT全加器 ... 34 圖 3-144-BIT漣波加法器 ... 34 圖 4-1 動態電壓調整系統架構圖 ... 35 圖 4-2 負載電路 ... 37 圖 4-3 壓控振盪器在CORNER FF 之下的電壓頻率曲線 ... 38 圖 4-4 壓控振盪器在CORNER SS 之下的電壓頻率曲線圖 ... 38

圖 4-5 壓控振盪器在CORNER TT 之下的電壓頻率曲線圖 ... 39 圖 4-6 數位電路負載時之頻率誤差與漣波大小 ... 41 圖 4-7 理想電流負載時之頻率誤差與電壓變化 ... 43 圖 4-8C2 為 1UF 時之頻率誤差與電壓變化 ... 45 圖 4-9C2 為 5UF 時之頻率誤差與電壓變化 ... 47 圖 4-10C1 為 16X1.4PF 時之頻率誤差與電壓變化 ... 49 圖 4-11C1 為 8X2.8PF 時之頻率誤差與電壓變化 ... 50 附錄-1 數位電路負載時之頻率誤差與漣波大小 ... 60

第一章

第一章

第一章

第一章、

、

、

、緒論

緒論

緒論

緒論

1.1 簡介

簡介

簡介

簡介

隨著個人行動裝置的發展,例如智慧型手機、掌上型電子遊樂器、平板電腦以及生 醫元件的日漸普及,對於能增加行動裝置的使用及待機時間的低功率設計方式也就越趨 重要。將數位電路操作在次臨界電壓範圍內則是一種解決的方式,並能有效的大幅降低 電路的功率消耗,但操作在次臨界電壓下的電路延遲時間,容易受到製程(P)、電壓(V)、 溫度(T)的變化而有劇烈的影響。動態電壓調整系統(Dynamic Voltage Scaling)則能夠讓操 作在次臨界電壓的數位電路,不論在製程、電壓或溫度的變異下都能夠工作在符合工作 頻率要求的最低工作電壓。動態電壓調整系統是利用鎖頻迴路(Frequency Loop Lock)來達成,其中包含頻率比 較器(Frequency Detector)、電壓轉換電路(DC-DC Converter)以及環形震盪器(Ring

Oscillator)等主要元件。其中、環形震盪器的結構,即是複製數位電路中的關鍵路徑 (Critical Path)串接後而成,亦即環型振盪器所產生的頻率即是數位電路所允許的最高工 作頻率。我們藉由頻率偵測器來判斷環型振盪器上的工作頻率是否符合我們所需求的工 作頻率,並使用電壓轉換電路來適當的調整數位電路的工作電壓,藉以控制數位電路所 允許的最高工作頻率的高低,使數位電路所允許的最高工作頻率恰好等同於系統需求的 工作頻率。利用動態電壓調整系統,我們就可以使操作在次臨界電壓下的數位電路,工 作在符合工作頻率要求的最低工作電壓,以降低功率的消耗。

1.2 研究動機

研究動機

研究動機

研究動機

操作在次臨界電壓的數位電路具有較低的工作電壓與較少的功率消耗等優點,但相 對的電路延遲時間則會隨著製程、電壓、溫度的飄移有劇烈的變化。若我們為了克服製 程、電壓與溫度的變化對數位電路的影響,最簡單的方法是定義一個較高的工作電壓, 使操作在次臨界電壓下的數位電路不論製程與溫度飄移在一定的範圍之內,其關鍵路徑 的電路延遲時間都能夠符合要求的工作頻率。但如此一來,便無法使所有的 IC 都能夠 工作在符合工作頻率要求的最低工作電壓。在某些條件下,仍需配合整體的製程變化定 義出一個較高的安全工作電壓,而額外浪費了許多功率的消耗,因此單純的使數位電路 工作在次臨界電壓是不夠的,還需要一個系統,使 IC 能依照其 PVT 特性,來定義其工 作電壓,以降低功率消耗,即動態電壓調整系統。 動態電壓調整電路中,最關鍵的部份是使用了交換式電容(Switch Capacitor)電路來 完成電壓轉換器,使用交換式電容來完成電壓轉換的好處是,可以節省一般升壓/降壓式 電壓轉換器(BOOST/BUCK Converter)上所使用到的電感。在不使用電感來完成動態電壓 調整系統後,也更容易達成數位電路製程的提升與系統晶片整合 (System on Chip)。交 換式電容的電壓轉換電路中,電容值的選擇與使用,讓電路能夠工作在符合工作頻率要 求的最低工作電壓,是我們研究的重點。期望在不同工作環境下,都能夠達到最佳的功 率消耗與效能。1.3 論文結構

論文結構

論文結構

論文結構

本論文內容分成五個章節。第一章為緒論,說明動態電壓調整系統的研究動機以及 論文結構。第二章為介紹當電路操作在次臨界電壓時,在功率消耗上的優勢,以及功率 消耗模型的說明,並說明當電路操作在次臨界電壓時的電路特性,包含了電流驅動能力、 電壓轉換曲線以及在不同電壓、溫度與製程變化之下的電路延遲特性,藉由本章的討論 了解操作在次臨界電壓下的電路特性後,方能依照電路特性設計出符合要求的電路。第 三章為動態電壓調整系統的結構說明與設計實現,並解說如何以鎖頻迴路的概念來達成數位動態電壓調整系統,且詳細的說明鎖頻迴路內的工作電路。在本論文中的鎖頻迴路 的特色在於,我們利用交換式電容的方式做為電壓轉換器,以減少電感的使用,使用交 換式電容電壓轉換器在減少了電感的使用後,也可以使動態電壓調整系統更容易達成系 統晶片整合的目的。第四章為動態電壓調整系統的模擬結果及特性,並觀察與討論其結 果。第五章為結論,討論電路設計結果。

第二

第二

第二

第二章

章

章

章、

、

、

、次臨界電壓下的

次臨界電壓下的

次臨界電壓下的

次臨界電壓下的電路

電路

電路特性

電路

特性

特性

特性

2.1 功率消耗

功率消耗

功率消耗

功率消耗

本節將介紹操作在次臨界電壓的功率消耗與比較,功率分析主要可分為動態功率消 耗(Dynamic Power Dissipation)與靜態功率消耗(Static Power Dissipation)。經由電流與功 率的討論,可明顯的比較出操作在次臨界電壓的電路在功率消耗上的優勢。下列式子為 功率消耗表示式。 = + (2.1) 靜態功率消耗 靜態功率消耗 靜態功率消耗 靜態功率消耗 當系統處於穩態狀態下,CMOS 仍然會有漏電流的產生,因此電路會產生靜態功率 消耗,漏電流的產生是由於次臨界電流(Sub-Threshold Current)所產生的,除此之外,擴 散區(Diffusion Region)到基座(Substrate)間的二極體也會產生逆向漏電流(Reverse-Biased Leaking) ,如下式所示。 = × (2.2) = + (2.3) = !"#$# − 1' (2.4) 當電路的工作電壓操作在次臨界電壓區時,其次臨界電壓操作下的漏電流會與次臨 界工作電流相近,如下式所示:= (× "! #)*+#$, -#$ '× .1 − "+#/*#$ 0 × "1#/*1#$ (2.5) ( = 2(3 4567 − 18 9 (2.6) =:; (2.7) 其中,VGS為電晶體閘極到源極的電壓,VDS為電晶體汲極到源極電壓,VTH為臨界

電壓,η 是 Drain Induction Barrier Lower(DIBL)係數,Cox為氧化層電容值,µ0為載子

移動率,W、L 為閘極寬度與長度,VT為熱電壓,K 為波茲曼常數=1.38X10-23焦耳/每 度凱氏溫標,T=凱氏溫標定義之絕對溫度=273+攝氏溫度,q=電子電荷之大小 =1.602X10-19庫侖。 圖 2- 1 靜態電流示意圖 VDD n+ p+ p+ n -n+ p+ n+ p -VSS VDD n+ p+ p+ n n+ p+ n+ p -VDD

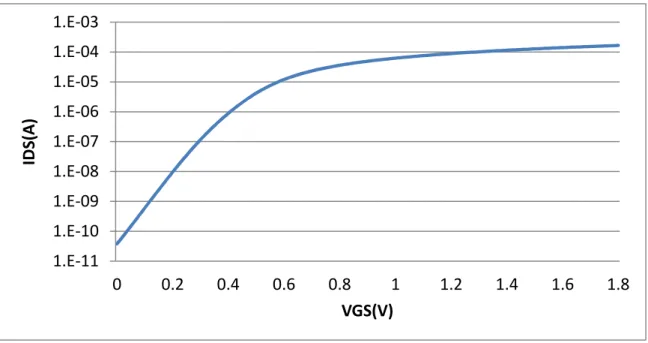

圖 2- 2 次臨界電流與二極體逆向電流示意圖 以圖 2.3 的方式,使用 HSPICE 模擬,在 TSMC 0.18µm 1P6M CMOS 的製程條件下。 當 VGS由 0V 至 1.8V 變化時,我們以對數的方式來表示 IDS對 VGS的曲線,如圖 2.4。圖 2.4 的曲線中可看出,當 MOS 處於次臨界電壓(約 0.2V~0.5V)與強反轉區(1V 至 1.8V) 操作時,MOS 電流約可相差 101至 104倍。 圖 2- 3 電晶體 IDS對 VGS曲線量測電路 p Sub-Threshold Current Reverse-biased Current p n n Bulk Source Gate Drain VDD = 1.8V Static Current VGS

圖 2- 4 以對數的方式表示電晶體的 IDS對 VGS曲線 動態功率消耗 動態功率消耗 動態功率消耗 動態功率消耗 動態功率消耗可分為兩部份討論,分別為切換功率(Switching Power)與短路電流功 率(Short Circuit Power),以下分別討論:

切換功率是由於暫態切換電流與負載電容間的充放電所產生的動態功率消耗。以下 將以一個反向器(Inverter)為例,說明反向器在轉態時所消耗的動態功率。 圖 2- 5 反向器充放電模型 1.E-11 1.E-10 1.E-09 1.E-08 1.E-07 1.E-06 1.E-05 1.E-04 1.E-03 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 IDS (A ) VGS(V) CL VDD VIN IP IN CL VDD RP IN CL RN (a) (b) (c) IP

圖 2-5(a)中,當 PMOS 導通時,電源(VDD)會對負載電容(CL)充電,而 NMOS 導通

時,則將儲存在負載電容上的電荷經由 NMOS 放電。可將充放電的動作以圖 2-5(b)及圖

2-5(c)作為等效模型觀察其能量特性,其中 RP代表 PMOS 的阻抗、RN代表 NMOS 阻抗。

電源(VDD)經由 PMOS 導通傳送出的總能量為 Edeliver,儲存在負載電容上的能量為 Ecload,

Edeliver與 Ecload可由(2.8)式、(2.9)式兩式表示,其中 VC為負載電容所儲存之電壓。 < = =(A >6?8 @?= = 3(A BC @? = 3 9 (2.8) < = =(A >6?8 D@?= = 3(A BC D@? =E93 9 (2.9) 由(2.8)式、(2.9)式中可看出,電源(VDD)所提供的能量大於負載電容所儲存的能量,兩者 相減則為電源對負載電容充電時 PMOS(RP)所消耗的能量即為下式: < − < =E93 9 (2.10) 當 NMOS 導通時,負載電容上所儲存的電荷,會經由 NMOS(RN)釋放出來,因此, 當反向器經過一個週期的充放電變化之後,所消耗掉的整體能量為3 9 。根據功率的 定義為單位時間內所消耗的能量,因此反向器的功率消耗如下式所示: P = f × 3 × 9 (2.11) 再更進一步可以考慮觸發參數 α(Switching Activity),α 代表訊號轉態的發生機率,因為 動態功率消耗是發生在訊號轉換的時機,因此動態功率消耗可以重新由下式表示: P = α × f × 3 × 9 (2.12) 由 (2.12)式可看出,降低動態功率最有效的方式是降低 VDD的電壓,VDD的降低會以平 方項的影響減少功率消耗。我們考慮在相同條件下,以相同的轉態時間、負載電容、工 作頻率下,由(2.12)式可知,若工作電壓由原本的 1V 至 1.8V 之間,降低為 VDD在 0.2V 至 0.5V 之間,其動態功率可降低 4 至 81 倍。 短路電流功率則是當訊號轉態時,除了切換功率消耗之外,還會額外的產生短路電 流,因而產生短路電流功率、如圖 2.6 所示,這是由於 CMOS 在轉態時,當輸入電壓介 於 NMOS 的臨界電壓(VTN)與 VDD-|VTP|時,電晶體會有一小段的時間 PMOS 與 NMOS

同時處於導通的狀態,此時,會產生一條由 VDD流至 VSS的短路路徑,由這條電流路徑 所產生的功率消耗稱為短路電流功率。 圖 2- 6 含輸出入曲線的反向器充放電模型 D=I D× (2.13) 在數位電路中,欲降低短路電流所造成的功率消耗,除了考慮適當的電晶體大小外, 應該要提高輸入訊號的轉態速度,亦即在設計電路時要考慮到電路的驅動能力(Driving Strength)以及扇出(Fan Out)個數,才能夠有效的降低短路功率消耗。但若數位電路的驅 動能力不足時,電路操作速度會變慢且訊號斜率加大,因此短路電流漏電的時間會增加, CL(t) VDD VIN(t) ISC(t) VTN VDD - |VTP| VIN(t) ISC(t) VOUT(t) 0 t0 t1 VOUT(t)

但即使如此,如(2.13)式所示,降低 VDD仍可有效的減少短路電流功率。

2.2 P、

、

、N MOS 電流

、

電流

電流

電流驅動能力

驅動能力

驅動能力

驅動能力

由於操作在次臨界電壓時的電晶體元件速度變慢,且電流驅動能力減弱。當要設計 操作於次臨界電壓的電路時,首先需要了解操作在次臨界電壓下的電路特性。本節討論 要如何安排 CMOS 中 P、N MOS 的比例(Ratio),使 P、N MOS 的電流驅動能力相近。

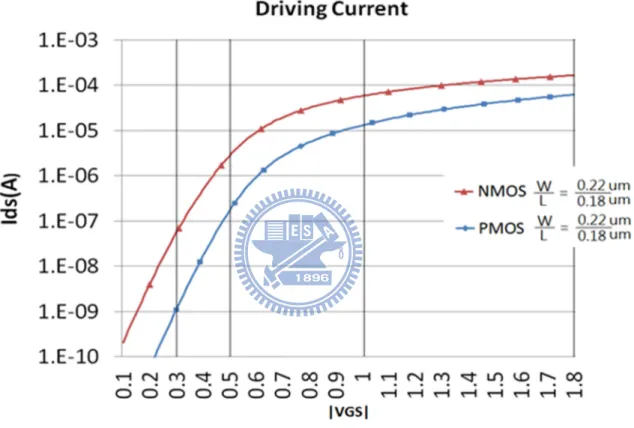

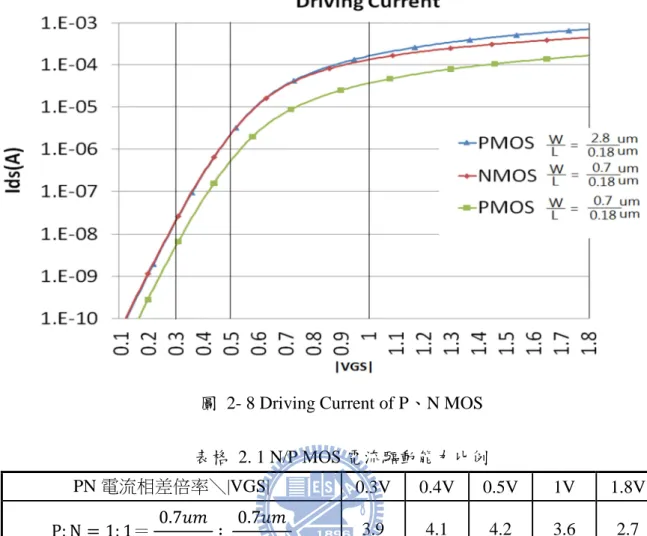

圖 2- 8 Driving Current of P、N MOS 表格 2. 1 N/P MOS 電流驅動能力比例

PN 電流相差倍率\|VGS| 0.3V 0.4V 0.5V 1V 1.8V

P: N 1: 1= 0.7OP

0.18OP ∶ 0.18OP 0.7OP 3.9 4.1 4.2 3.6 2.7 P: N 4: 1= 2.8OP

0.18OP ∶ 0.18OP 0.7OP 1.0 1.0 1.0 0.8 0.6

我們將圖 2-7 及圖 2-8 所繪製的 P、N MOS 電流驅動能力整理為表 2.1,當操作電 壓越低,相同尺寸的 P、N MOS 電流驅動能力相差越大。由表 2.1 可看出,我們試著將 工作電壓由 0.3V 變化至 1.8V 時,V >電流比例相差 3.9 倍至 2.7 倍。亦即,當電路操作於 次臨界電壓時,若 P、N MOS 非為最小尺寸,且 P:N=4:1 時,操作於次臨界電壓的 P、 N MOS 電流驅動能力相近。

2.3 電壓轉換曲線

電壓轉換曲線

電壓轉換曲線(Voltage Transfer Curve)

電壓轉換曲線

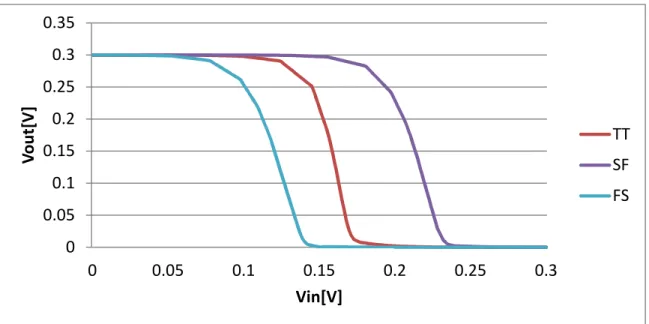

我們觀察反向器操作在次臨界電壓時的電壓轉換曲線,如圖 2-9 所示。我們可以看 出反向器操作在次臨界電壓與強反轉區(Strong Inversion) 時的電壓轉換曲線相當接近, 也是因為此類似的曲線,可以讓數位電路操作在次臨界電壓時,仍能夠分辨出邏輯 1 與 邏輯 0,也才能夠達成降低電源電壓以減少功率消耗的同時,仍能夠完成所需的功能。 圖 2- 9 操作在次臨界電壓反向器的電壓轉換曲線(P:N = 4:1) 電壓轉換曲線對 電壓轉換曲線對 電壓轉換曲線對 電壓轉換曲線對製程變化的影響製程變化的影響製程變化的影響製程變化的影響 我們接下來觀察當操作於次臨界電壓區時,電壓轉換曲線對製程飄移與溫度變化的 影響。由 (2.5)式己知,操作在次臨界電壓下的電流與 VGS呈指數關係,但除了 VGS會 對操作在次臨界電壓的電晶體電流造成影響外,製程變異對電晶體特性的影響亦不容忽 視,若忽略此一影響,有可能造成在某些電路上無法正常工作,或良率不佳。圖 2-10 表示 P、N 電晶體比例為 4:1 的反向器在 TT、SF、FS 三種不同製程變異下的電壓轉換 曲線。 0 0.1 0.2 0.3 0.4 0.5 0.6 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 V o u t[ V ] Vin[V] 0.5V 0.4V 0.3V 0.2V圖 2- 10 TT、SF、FS 三種不同製程變異下,反向器的電壓轉換曲線(P:N = 4:1) 電壓轉換曲線對溫度變化的影響 電壓轉換曲線對溫度變化的影響 電壓轉換曲線對溫度變化的影響 電壓轉換曲線對溫度變化的影響 當電晶體操作在強反轉區時,溫度升高會造成電子移動率的下降,因此降低電晶體 的電流能力,而造成電晶體轉態速度變慢。但當電晶體操作在次臨界電壓時,溫度的上 升會使臨界電壓降低,而使電流能力以指數的方式提高,當提升的電流能力超過由電子 移動率降低所造成的電流能力衰減時,則電晶體操作速度會變快。亦即當電晶體操作於 次臨界電壓時,溫度上升會提高電晶體的操作速度。圖 2-11 表示不同溫度對 P、N 電晶 體比例為 4:1 的反向器,在電壓轉換曲線上所造成的影響。 圖 2- 11 三種不同溫度下,反向器的電壓轉換曲線(P:N = 4:1) 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0 0.05 0.1 0.15 0.2 0.25 0.3 V o u t[ V ] Vin[V] TT SF FS 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0 0.05 0.1 0.15 0.2 0.25 0.3 V o u t{ v ] Vin[V] 0℃ 25℃ 75℃

2.4 次臨界電壓下的延遲速度

次臨界電壓下的延遲速度

次臨界電壓下的延遲速度

次臨界電壓下的延遲速度

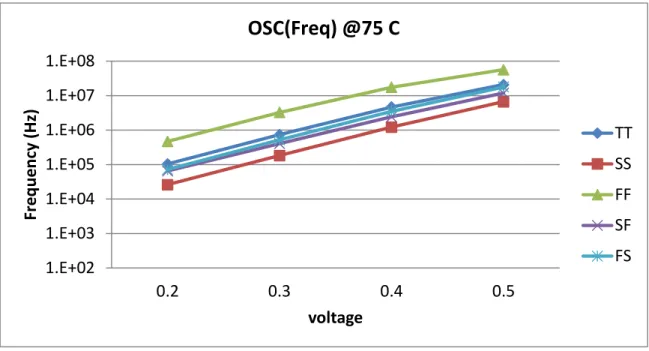

在本節中我們使用由反向器組成的一個操作在次臨界電壓的七級環型振盪器(Ring Oscillator),用來觀察當不同的電壓、溫度與製程變異下會對電路延遲程度造成的影響, 經由本節的討論,方可了解操作在次臨界電壓時的數位電路操作特性,在了解了電路特 性之後,再依照相對應的電路特性設計出符合要求的數位電路。如圖 2-12 為一個七級 環型振盪器,其中每個反向器的扇出數均為 4、反向器內的 P、N 電晶體比例為 4:1、並 使用 TSMC 0.18µm 1P6M CMOS 製程模擬並觀察其結果。 圖 2- 12 七級環型振盪器 電壓變化下 電壓變化下 電壓變化下 電壓變化下對對對對振盪頻率振盪頻率振盪頻率振盪頻率的的的的影響影響影響影響 之前章節己提到,操作在次臨界電壓時的電路操作速度會明顯變慢,我們接下來討 論當工作電壓由 0.2V 變化至 0.5V 時,操作在次臨界電壓下的電路工作頻率的變化。經 由模擬圖 2-12 的電路,並調整電壓與製程的變化後,將振盪器的工作頻率繪製成圖 2-13。 由圖 2-13 可以看出,當溫度在 0℃時,電壓每上升 0.1V,會使工作頻率提高約 14 倍。 當溫度在 25℃時,電壓每上升 0.1 V,會使工作頻率提高約 10 倍。當溫度在 75℃時, 電壓每上升 0.1V,會使工作頻率提高約 7 倍。亦即操作在次臨界電壓時工作電壓每上升 0.1 V,會使電路的工作頻率提升約 10 倍,並依工作溫度的不同而使電壓對工作頻率的 Load OUTLoad Load Load Load

Load Load

影響稍有差異,當溫度降低時,電壓對環型振盪器的工作頻率影響較大,當溫度升高, 電壓對環型振盪器的工作頻率影響較小。 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 0.2 0.3 0.4 0.5 F re q u e n cy ( H z) voltage

OSC (Freq) @0 C

TT SS FF SF FS 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 0.2 0.3 0.4 0.5 F re q u e n cy ( H z) voltageOSC (Freq) @25 C

TT SS FF SF FS圖 2- 13 電壓對環型振盪器的影響 溫度 溫度 溫度 溫度變化下變化下變化下變化下對對對對振盪頻率振盪頻率振盪頻率振盪頻率的的的的影響影響影響影響 接下來我們討論溫度對環型振盪器振盪頻率的影響,我們己知操作在次臨界電壓區 與強反轉區時的電晶體工作特性不同,當電晶體工作於強反轉區時,當溫度上升,電晶 體操作速度會變慢,而當電晶體工作於次臨界電壓時,溫度上升反而會讓工作頻率提高。 電晶體在工作溫度提高的同時能夠增加工作頻率,是因為操作於次臨界電壓時,溫度的 上升會使電晶體的臨界電壓降低,而使電流能力以指數的方式提高,當提升的電流能力 超過因溫度提升而降低的電子移動率時,則電晶體操作速度會變快。由圖 2-14 中可知, 在次臨界電壓時,隨著溫度提高,電晶體的操作速度確實會變快,但溫度的變化對操作 頻率的影響明顯不如電壓對操作頻率的影響,但溫度對工作速度的影響同樣是不容忽視 的,當溫度由 0℃提升至 25℃時,環型振盪器的操作頻率約升高 1.3 至 3 倍。當溫度由 25℃提升至 75℃時,操作頻率約升高了 1.3 至 5 倍。在不同的操作電壓下,對溫度的影 響亦不同,當工作電壓越高,溫度對振盪頻率的影響越低。 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 0.2 0.3 0.4 0.5 F re q u e n cy ( H z) voltage

OSC(Freq) @75 C

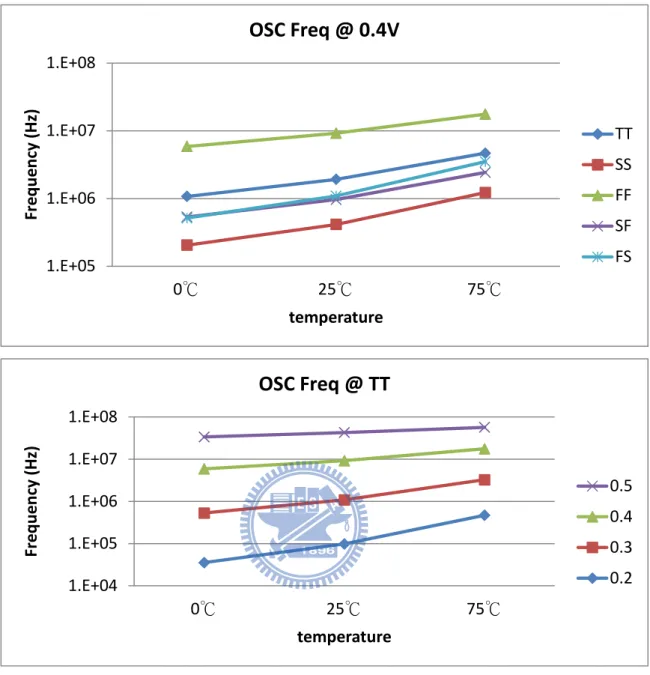

TT SS FF SF FS圖 2- 14 溫度對環型振盪器的影響 製程變化下對振盪頻率 製程變化下對振盪頻率 製程變化下對振盪頻率 製程變化下對振盪頻率的的的的影響影響影響影響 除了電壓與溫度會對數位電路的工作頻率產生影響之外,製程飄移亦會對工作頻率 產生影響,尤其是當電路工作於次臨界電壓時,製程變異對工作頻率的影響變的更加劇 烈。由圖 2-15 中可看出,當工作在相同電壓與溫度時,製程 SS 到 FF 所造成的頻率飄 移約 13 到 27 倍。 1.E+05 1.E+06 1.E+07 1.E+08 0℃ 25℃ 75℃ F re q u e n cy ( H z) temperature

OSC Freq @ 0.4V

TT SS FF SF FS 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 0℃ 25℃ 75℃ F re q u e n cy ( H z) temperatureOSC Freq @ TT

0.5 0.4 0.3 0.2圖 2- 15 製程對環型振盪器的影響

2.5 總結

總結

總結

總結

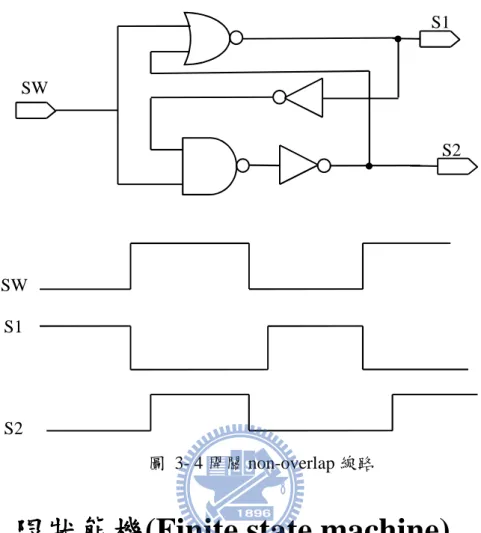

在本章節中,我們探討了在次臨界電壓下的電流驅動能力、電壓轉態特性以及電路 延遲特性。我們己知,操作於次臨界電壓的數位電路在 TSMC 0.18µm 1P6M CMOS 製 程下,當 P、N 電晶體尺寸比例為 4:1 時,可使 P、N 電晶體有相近的電流驅動能力。 在經由電壓轉換曲線的觀察後,我們可以確定當工作電壓小於臨界電壓時,電晶體依舊 可以有邏輯 1 與邏輯 0 的變化。最後使用環型振盪器來了解電壓、溫度與製程在次臨界 電壓時對電路的影響。亦即,當操作於次臨界電壓時,電壓變化 0.1V,會造成工作頻率 約 7 到 14 倍的變化。溫度由 0℃到 75℃變化時,會造成頻率 3 到 16 倍的變化。當製程 SS 到 FF 的變異時,會造成頻率 13 到 27 倍的變化。由這些數據可看出,當電路工作於 次臨界電壓時,電壓、溫度與製程只要稍有變動,電路允許的最高工作頻率就會有非常 劇烈的變動,尤其是電壓、溫度與製程同時飄移時,對電路允許的最高工作頻率的影響 更可能相差到百倍以上。經由本章節的探討,對操作在次臨界電壓下的電路特性有了基 本的了解後,才能夠依其特性設計出一個工作在次臨界電壓的電路系統。 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 SS FS SF TT FF F re q u e n cy ( H z) temperatureOSC Freq @ 25

℃

℃

℃

℃

0.5 0.4 0.3 0.2第

第

第

第三

三

三

三章

章

章

章、

、

、

、動態電壓調整系統

動態電壓調整系統

動態電壓調整系統

動態電壓調整系統

3.1 系統

系統

系統架構簡介

系統

架構簡介

架構簡介

架構簡介

為了達成操作在次臨界電壓的省電操作方式,讓數位電路能夠工作在符合工作頻率 要求的最低工作電壓。我們使用的電路架構如圖 3-1 所示,以鎖頻迴路的概念來達成動 態電壓調整系統。我們有一組操作在次臨界電壓的數位電路,在此系統中,數位電路即 為動態調整系統的負載。我們經由交換式電容來調整數位電路的工作電壓,使用交換式 電容來調整工作電壓的好處是,可以節省一般電壓轉換器上電感的使用,也更容易達成 系統晶片整合的目標。在數位電路中,必定有一組關鍵路徑(Critical Path),我們複製一 組關鍵路徑,並串接為環型振盪器,利用頻率比較器將環型振盪器與參考頻率作比較, 當環型振盪器的頻率大於參考頻率時,所代表的即是數位電路所允許的最高工作頻率大 於需求的工作頻率,我們便減少交換式電容對數位負載電路電荷的傳輸,數位負載電路 的工作電壓便會下降,即數位負載電路允許的最高工作頻率降低。反之我們則增加數位 負載電路上的工作電壓,藉由上述的方式使數位電路工作在符合工作頻率要求的最低工 作電壓,以降低電路的功率消耗。20 圖 3- 1 動態電壓調整方塊圖

3.2 交換式電容

交換式電容

交換式電容電壓轉換器

交換式電容

電壓轉換器

電壓轉換器

電壓轉換器

圖 3- 2 交換式電容電路 如圖 3-2 所示,我們使用交換式電容電路取代一般的降壓式電壓轉換電路(BULK), 利用 S1 與 S2 的開關,將電荷經由 C1 傳遞至 C2。C1 傳遞至 C2 的電荷量與開關 S1、 S2 的切換時間、負載電流 IL以及負載電壓 VO之間的關係式表示如下: ∆Q=CE× 6V[− V\8 I]× T (3.1) 每次由 C1 傳遞至 C2 的電荷會造成 VO上微小的電壓改變,每次充電所產生的電壓漣波 大小表示如下: ∆V_ `[aabc =∆def ghe×if ej×6kefl km8 (3.2) Ring Oscillator (Critical Path)Sub-Threshold Voltage Level Shift FD FSM DC-DC Converter (Switch-Capacitor) Fref Fvco Voltage Transfer Power = 1V Loading Digital Circuit VO=0.3V~0.6V VI S1 S2 C2 VO IL C1

對於交換式電容電路上 S1 與 S2 的開關週期,以及電容 C1 與 C2 的選擇方式,可 經由(3.1)式與(3.2)式整理得出下列三式: CE ≥okglh×ik op (3.3) C9 ≥∆kgm qlrrsth×i (3.4) T ≤ej×6kl km8 gh ef×∆km qlrrst gh (3.5) (3.3)式、 (3.4)式與 (3.5)式可看出,交換式電容電路 C1 與 C2 的值與開關切換週 期(T)相互關連。C2 值的大小與 VO上的漣波電壓、負載電流以及開關切換週期相關。 再由(3.3)式中得知,C1 的值會影響到 VO最終的穩態電壓以及所允許的最大負載電流 IL, 但與 VO上每次充電時所產生的漣波電壓大小無關。在使用交換式電容電路時,我們必 需先定義出工作條件,如負載電流大小、開關切換頻率、以及預期的 VO漣波電壓大小, 經由這些參數定義完畢後,才能求得實際要應用在電路上的最小的 C1 與 C2 值。 如圖 3-1 所示,我們定義數位負載電路工作於 1MHz 時,所消耗的最大平均電流為 10uA,亦即輸入之參考頻率與交換式電容開關切換頻率為 1MHz。為了使圖 3-1 的環型 振盪器較為穩定,我們定義每次對 VO充電時所允許的最大漣波為 1uV,且 VO工作於次 臨界電壓區、即 VO電壓操作在 0.3V~0.6V 間,經由上述定義,我們可以得到所需要的 C1 與 C2 大小如表格 3. 1 所示: 表格 3. 1 交換式電容電路參數表 VI Vo IL T △Vo p-p(V) C1 設定值 C2 設定值

1V 0.6V 10uA 1uS 1uV 25pF 10uF

1V 0.5V 10uA 1uS 1uV 20pF 10uF

1V 0.4V 10uA 1uS 1uV 16.7pF 10uF

1V 0.3V 10uA 1uS 1uV 14.3pF 10uF

1V 0.6V 1uA 1uS 1uV 2.5pF 1uF

1V 0.5V 1uA 1uS 1uV 2pF 1uF

1V 0.4V 1uA 1uS 1uV 1.7pF 1uF

22 經由表格 3.1 可知,當 C2 為 10uF 時,可使每次 C1 對 C2 充電時,VO所產生的漣 波電壓小於 1uV,且 VO的漣波電壓大小與 C1 值無關。如果我們要改變數位負載電路上 的工作電壓 VO,使 VO工作於 0.3V 至 0.6V 之間,我們只需變更 C1 的值即可達成負載 電壓的轉換。同時 C1 的值也會與負載電流相關,當我們需要使 VO工作於某一固定電壓 時,負載電流愈大所需的 C1 值愈大。亦即,當我們欲使 VO處於 0.3V 至 0.6V 之間的動 態電壓調整系統,若負載電流為 10uA,此時的 C1 則需要在 25pF 與 14pF 之間變化。但 若是使負載電流降低為 1uA 時,C1 的值僅需在 2.5pF 與 1.4pF 間變化即可完成 VO工作 於 0.3V 至 0.6V 之間的動態電壓調整系統。 此時,我們知道在使用交換式電容電路當作電壓轉換電路時,我們需要一個較大的 C2 以降低 C1 對 C2 充電時的電壓漣波,以及較小的 C1 來調整 VO的工作電壓。且當開 關頻率固定時,為了調整 VO的電壓,我們需要將 C1 細分為許多小電容的並聯,並依實 際的電壓需求在 C1 端並連適當的電容個數,當 VO需要較高的電壓時,C1 端就並連較 多的小電容,反之,若 VO需要較低的電壓時,則減少 C1 端電容並聯的數量,以得到較 小的穩態 VO電壓。如圖 3-3 所示,當 C1 由數量越多、電容值越小的電容並聯組成時, 我們能夠對 VO穩態電壓刻度的調整就越精細。 圖 3- 3 C1 電容可調之交換式電容電路 VI S1 S2 C2 VO IL C11 C12 C1N

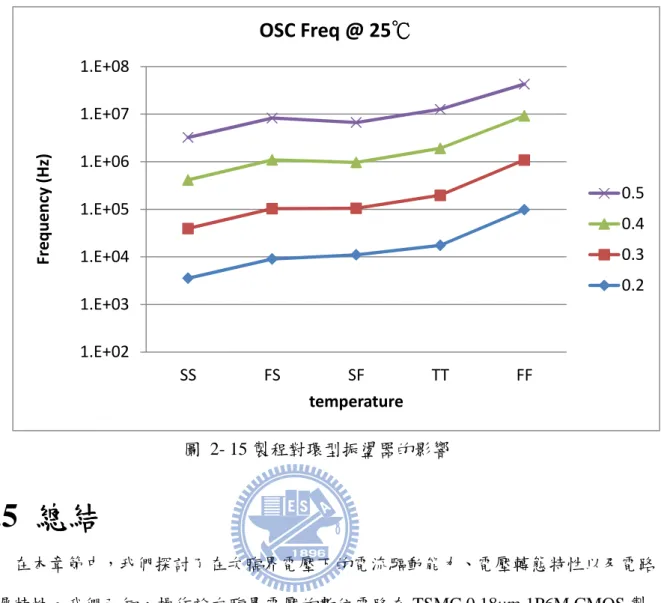

表格 3. 2 穩態 VO與 C1 關係表 IL=1uA、T=1uS IL=10uA、T=1uS C1 Vo C1 Vo C1 Vo C1 Vo 0.7p -0.429V 6.3p 0.841 V 11.9p 0.160 V 17.5p 0.429 V 1.4p 0.286 V 7p 0.857 V 12.6p 0.206 V 18.2p 0.451 V 2.1p 0.524 V 7.7p 0.870 V 13.3p 0.248 V 18.9p 0.471 V 2.8p 0.643 V 8.4p 0.881 V 14p 0.286 V 19.6p 0.490 V 3.5p 0.714 V 9.1p 0.890 V 14.7p 0.320 V 20.3p 0.507 V 4.2p 0.762 V 9.8p 0.898 V 15.4p 0.351 V 21p 0.524 V 4.9p 0.796 V 10.5p 0.905 V 16.1p 0.379 V 21.7p 0.539 V 5.6p 0.821 V 11.2p 0.911 V 16.8p 0.405 V 22.4p 0.554 V 表格 3-2 中,我們將 C1 拆成 32 個 0.7pF 的小電容。因此,當我們需要使 VO工作 在 0.3V 至 0.55V 之間變化時,不論負載電流為 1uA 或 10uA,我們都可以調整 C1 電容 的並連數量以達到所需要的 VO電壓。若我們需要在負載電流為 10uA 時達到更高的 VO 電壓時,只需要再增加 C1 上並連的電容數量即可。 依表格 3-1 所定義,由於每次 C1 對 C2 充電時僅會對 VO增加 1uV 的電壓,以開關 切換週期為 1uS 計算,VO初始電壓由 0V 充電至 0.3V 需要 0.3 秒的時間,為了節省電 路的初始化時間,也為了減少系統模擬時所需要的資源消耗,交換式電容在開關的設計 上,可以讓開關在初始化狀態時,使開關 S1 與 S2 同時處於關閉(Close)的狀態,以加速 VO充電至所需的電壓準位。另外還有一點必需注意的是,除了於初始狀態時可以使兩 個開關同時處於關閉的狀態以加速 VO的充電外,其餘任何時間,開關 S1 與 S2 僅能有 一個為關閉狀態,以避免電荷直接由電源端 VI傳輸至 VO。在控制 S1 與 S2 的切換開關 間,可以使用一組 Non-Overlap 電路,以避免 S1 與 S2 有同時關閉的情況發生,如圖 3-4 所示:

24

圖 3- 4 開關 non-overlap 線路

3.3 有限狀態機

有限狀態機

有限狀態機(Finite state machine)

有限狀態機

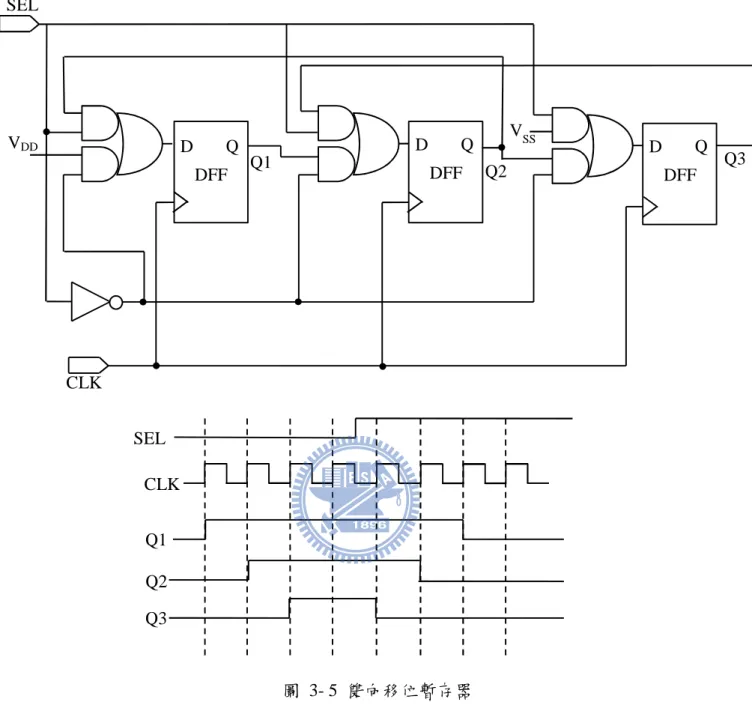

在我們的動態電壓調整系統內,由上一小節中己了解使用交換式電容所達成的電壓 轉換電路中,C1 需要由許多包含開關的小電容組成。有限狀態機電路即是為了控制 C1 電容並聯數量的一個數位電路。在此處我們使用雙向移位暫存器來完成 C1 開關的控制, 如圖 3-5 所示。 S1 SW S2 SW S1 S2

圖 3- 5 雙向移位暫存器 圖 3-5 中,Q1、Q2 和 Q3 分別控制一組 C1 的電容開關,若將 C1 細分為 32 個小電 容時,則雙向移位暫存器亦增加至 32 組輸出(Q1、Q2至 Q32)。當交換式電容電壓轉換器 需要較高的輸出電壓或負載電流時,此時雙向移位暫存器會使 Q 輸出為 1 的數量持續增 加,也就是增加電容 C1 端並聯電容的個數,亦即得到較大的整體 C1 值。若交換式電 容電壓轉換器需要較小的輸出電壓或負載電流時,則雙向移位暫存器會使 Q 輸出為 1 的數量依續遞減,以減少 C1 端並聯電容的個數,亦即得到較小的 C1。 在此處我們使用雙向移位暫存器而非上數/下數計數器來控制 C1 端並聯電容的數量 SEL D Q DFF D Q DFF D Q DFF VDD VSS CLK Q1 Q2 Q3 Q1 Q2 Q3 CLK SEL

26 的好處是,其一、使用雙向移位暫存器時,可使用較少的邏輯閘完成 C1 端開關的控制, 其二、使用上數/下數計數器在計數值的轉換時,會有一段不穩定的資料輸出,若對應到 C1 端的開關,則有可能造成 C1 端並聯電容數量瞬間的改變及不穩定,這是我們不期望 看到的,因此在此處我們使用雙向移位暫存器來控制電容式電壓轉換器的 C1 電容並聯 數量。

3.4 頻率偵測器

頻率偵測器

頻率偵測器(Frequency detector)

頻率偵測器

圖 3-1 的動態電壓調整系統中包含了一組頻率偵測器,用來比較參考頻率(Fref) 與壓 控振盪器所產生出的頻率(FVCO)。我們使用兩組 7 位元的計數器來達成頻率比較的功能, 如圖 3-6 所示。 圖 3- 6 頻率偵測器 在圖 3-6 中,我們僅對兩組七級計數器的最後一級暫存器的輸出值做比較,而非完 全比較兩組七位元計數器的大小值,以簡化設計。當參考頻率(Fref)與壓控振盪器所 產生的頻率(FVCO)變化時,A1 及 A2 亦會先後變化,經由比較器判斷 A1 及 A2 的產 生順序後,我們能夠判斷出兩個輸入訊號的頻率高低,最後經由比較器產生兩個輸出訊 Fref T Q TFF R T Q TFF R T Q TFF R 7 級 counter Fvco T Q TFF R T Q TFF R T Q TFF R 7 級 counter>

CLK SEL A1 A2 CLR號 CLK 與 SEL 至上節中的有限狀態機,如此一來,我們就能夠依照參考頻率(Fref)與壓 控振盪頻率(FVCO)兩者間的頻率高低來調整電容式電壓轉換器中的 C1 電容並聯個數, 用來控制交換式電容電壓轉換器輸出電壓的高低,進而產生一個鎖頻迴路。在使用計數 器來完成頻率偵測器時,對參考頻率與壓控振盪頻率兩者間的頻率判斷會有一定範圍內 的誤差,以七級計數器為例,當兩個輸入訊號頻率誤差小於 0.8%(9Ew E9xE ≅ 0.8%)時, 此頻率偵測器無法正確的判斷出兩者間的頻率高低。

3.5 電壓準位轉換器

電壓準位轉換器

電壓準位轉換器(Voltage Level Shift)

電壓準位轉換器

在我們的動態電壓調整系統中包含了兩組不同的電位,其中一組電路工作在較高的 電壓,包含了頻率偵測器與有限狀態機。而另一組電路則工作於次臨界電壓之下,如數 位負載電路與壓控環型振盪器。為了使工作於次臨界電壓下的數位負載電路的工作頻率 能夠透過壓控環型振盪器迴授至工作於較高電壓準位的頻率偵測器中,我們在壓控環型 振盪器與頻率偵測器之間加入電壓準位轉換器,以做為兩者工作於不同電壓下的電路訊 號傳遞的橋梁。以下我們介紹兩種不同型式的電壓準位轉換器。 轉態速度較快之電壓準位轉換器 轉態速度較快之電壓準位轉換器 轉態速度較快之電壓準位轉換器 轉態速度較快之電壓準位轉換器 圖 3- 7 轉態速度較快之電壓準位轉換器 MP1 MP3 MN1 MN2 MP2 MP4 VDD VH OUTPUT Sub-Threshold voltage input

28 圖 3-7 中,VDD代表較高之電位,VH 代較低之電位,在此處我們使 VH 電壓小於 臨界電壓。此種電路型式的優點是電壓轉準位轉換速度較快,當臨界電壓介電 0.3V 至 0.5V 時,輸入至輸出延遲時間可小於 10nS。缺點是電路較為複雜且消耗電流較大。 轉態速度較慢之電壓準位轉換器 轉態速度較慢之電壓準位轉換器 轉態速度較慢之電壓準位轉換器 轉態速度較慢之電壓準位轉換器 圖 3- 8 轉態速度較慢之電壓準位轉換器 要使電壓準位轉換器操作於次臨界電壓時,並不需要如同圖 3-7 一樣那麼複雜,我 們同樣可以使用較簡單的架構來達成電壓準位轉換的目的。如圖 3-8 所示,使用一組 Non-Overlap 電路以及簡單的差動電路即可完成。以此種架構完成之電壓準位轉換電路, 當工作於 0.3V 至 0.5V 時,其輸入至輸出延遲時間約為數百個微秒(uS)。 MP1 MN1 MN2 MP2 VDD OUTPUT Sub-Threshold voltage input Normal Voltage Region Sub-Threshold Circuit Region

3.6 壓控

壓控

壓控環型振盪器

壓控

環型振盪器

環型振盪器

環型振盪器(Voltage Control Ring

Oscillator)

圖 3- 9 靜態時序分析 當我們要決定一塊數位電路最高的工作頻率時,我們所需要分析的是在兩個暫存器 之間的邏輯電路最大的延遲時間是多少,而使 Clock 變化的週期大於邏輯電路之最大延 遲時間。如圖 3-9 所示,我們必需使 CLK 訊號的變化時間大於訊號由 Q1 傳遞至 Q2 所 需花費的時間,因此訊號由 Q1 傳遞至 Q2 所需花費的時間,即是決定電路允許的最高 工作頻率最重要的因素。我們在第二章己知,製程與溫度的變異會造成電路延遲速度巨 大的改變,為了使在規定的溫度變化範圍內以及所有的製程飄移下,都能夠讓數位電路 工作在符合要求的工作頻率,我們必需讓數位電路工作在一個較高的操作電壓,以符合 所有的溫度與製程上的變異。但是如此一來,在某些溫度與製程下,並不需要如此高的 電壓即能達成工作頻率的求,因此會產生功率消耗上的浪費。為了使工作於次臨界電壓 的數位電路都能夠操作在滿足工作頻率要求的最低工作電壓,我們藉由複製一份圖 3-9 中的最大延遲路徑所經過的所有邏輯閘,並讓這些邏輯閘串接為一組環型振盪器,如圖 3-10 所示。此一環型振盪器所產生的頻率即可代表圖 3-9 中所允許的最大工作頻率。我 們經由偵測環型振盪器的工作頻率,當發現操作在次臨界電壓下的數位電路工作頻率低 於我們的需求時,我們便稍微的提高包含環型振盪器在內的整體數位電路的工作電壓, 直至環型振盪器達到我們需求的工作頻率為止。反之、若經由偵測環型振盪器的工作頻 率,發現數位電路的工作頻率高於我們所需求的工作頻率時,便稍微的降低包含環型振 CLK D Q Combination Logic D Q DFF DFF Q1 Q230 盪器在內的整體電路的工作電壓。如此一來,我們就可以利用對環型振盪器的頻率偵測, 使工作在不同溫度與製程變異下的數位電路操作在滿足工作頻率要求的最低工作電壓 以降低能量消耗。 圖 3- 10 壓控環型振盪器 圖 3-10 中,N 必需為奇數。N 的數量必需大於等於數位電路中最長路徑所經過的邏 輯閘數量,在經過一個週期,即正負半週轉態之後,實際上環型振盪器一個週期的時間 代表了經歷兩次最長路徑所需的時間。因此 N 的數量應該為數位電路之最長路徑所經過 的邏輯閘數量除以二,並額外加上數個邏輯閘,以確保環型振盪器在經歷一個週期後, 其延遲時間不會低於數位電路之最長路徑所產生的延遲。

3.7 負載電路

負載電路

負載電路

負載電路

在實際的動態電路調整系統中,系統的負載電路是將來 IC 設計時,依實際應用需 求而產生的數位邏輯電路,並藉由操作在次臨界電壓下的數位邏輯電路所產生的電流消 耗,做為交換式電容電壓轉換器上的電流負載。在此處我們使用一組十六位元的漣波進 位加法器(Ripple Carry Adder; RCA)、三十二位元的線性反饋位移暫存器(LinearFeedback Shift Register; LFSR)以及十七位元的D型暫存器作為動態電路調整系統的

負載電路,用來模擬將來可能實際應用的數位電路。如圖 3-11 所示,由線性反饋位移 暫存器產生的三十二元位輸出作為十六位元漣波進位加法器的輸入,並由十七位元的D

OUT

Voltage control input

型暫存器儲存加法器的運算結果。其中十六位元漣波進位加法器所產生的最長延遲路徑, 也就是壓控環型振盪器所要複製的關鍵路徑(Critical Path)。 圖 3- 11 負載電路 線性反饋位移暫存器 線性反饋位移暫存器 線性反饋位移暫存器

線性反饋位移暫存器((((Linear Feedback Shift Register;;;; LFSR))))

線性反饋位移暫存器是由移位暫存器(Shift Register)與互斥或閘(Exclusive Or)所組 成的,移位暫存器的輸入位元是由上一次移位暫存器的狀態經一線性函數轉換後所產生 的,也是就移位暫存器的某些位元經由互斥或閘的運算之後,輸入至移位暫存器的輸入 端,如圖 3-12 所示。線性反饋位移暫存器可以產生偽隨機訊號(Pseudo-Random Bit Sequence; PRBS)的輸出,但移位暫存器的初值不可為零,若初值為零則會使線性反饋位 移暫存器鎖住(Locked-Up),訊號將不再改變。我們可以利用三十二位元的線性反饋位移 暫存器所產生的隨機訊號作為十六位元加法器的輸入訊號。 32-bit LSFR A B SUM[16:0] Q[31:0] D Q DFF SUM Q[15:0] Q[31:16] CLK 16-bit 加法器

32 圖 3- 12 三位元線性反饋位移暫存器 線性反饋位移暫存器若經過適當的選擇回授位元,則最大可產生2 − 1筆隨機序列, 之後便不斷重復,若回授位元選擇不當則會產生較少的隨機序列數量。可以將被選擇到 的回授位元以回授多項式(Feedback Polynomial)表示,如圖 3-12,當回授多項式為 {|+ {9+ 1時,可產生最多組的隨機序列。且若要產生最多組數量的隨機序列,其回授 位元數量的選擇必為偶數、只有在回授位元數量為二或四時才會產生最多組數量的隨機 序列,且可產生最多數量的隨機序列的回授多項式可能不只一組。表格 3-3 列出可產生 最大隨機數列數量的回授位元,即回授多項式表示表。 CLK D Q DFF D Q DFF D Q DFF Feedback polynomial = X3 + X2 + 1 X3 X2 X1 初值為 011 之 LSFR X1 X2 X3 S0 = 0 1 1 S1 = 0 0 1 S2 = 1 0 0 S3 = 0 1 0 S4 = 1 0 1 S5 = 1 1 0 S6 = 1 1 1 S7 = S0 = 0 1 1

表格 3. 3 Taps for Maximum-Length LFSR Counters n 回授位元 n 回授位元 n 回授位元 n 回授位元 3 3,2 28 28,25 53 53,52,38,37 78 78,77,59,58 4 4,3 29 29,27 54 54,53,18,17 79 79,70 5 5,3 30 30,6,4,1 55 55,31 80 80,79,43,42 6 6,5 31 31,28 56 56,55,35,34 81 81,77 7 7,6 32 32,22,2,1 57 57,50 82 82,79,47,44 8 8,6,5,4 33 33,20 58 58,39 83 83,82,38,37 9 9,5 34 34,27,2,1 59 59,58,38,37 84 84,71 10 10,7 35 35,33 60 60,59 85 85,84,58,57 11 11,9 36 36,25 61 61,60,46,45 86 86,85,74,73 12 12,6,4,1 37 37,5,4,3,2,1 62 62,61,6,5 87 87,74 13 13,4,3,1 38 38,6,5,1 63 63,62 88 88,87,17,16 14 14,5,3,1 39 39,35 64 64,63,61,60 89 89,51 15 15,14 40 40,38,21,19 65 65,47 90 90,89,72,71 16 16,15,13,4 41 41,38 66 66,65,57,56 91 91,90,8,7 17 17,14 42 42,41,20,19 67 67,66,58,57 92 92,91,80,79 18 18,11 43 43,42,38,37 68 68,59 93 93,91 19 19,6,2,1 44 44,43,18,17 69 69,67,42,40 94 94,73 20 20,17 45 45,44,42,41 70 70,69,55,54 95 95,84 21 21,19 46 46,45,26,25 71 71,65 96 96,94,49,47 22 22,21 47 47,42 72 72,66,25,19 97 97,91 23 23,18 48 48,47,21,20 73 73,48 98 98,87 24 24,23,22,17 49 49,40 74 74,73,59,58 99 99,97,54,52 25 25,22 50 50,49,24,23 75 75,74,65,64 100 100,63 26 26,6,2,1 51 51,50,36,35 76 76,75,41,40 101 101,100,95,94 27 27,5,2,1 52 52,49 77 77,76,47,46 102 102,101,36,35 資料來源:[15] 漣波加法器 漣波加法器 漣波加法器

漣波加法器((((Ripple carry adder;;;; RCA))))

漣波加法器是由全加器(Full Adder)串接而成,全加器可以用圖 3-13 的方式來完成。 由全加器的 CO(Carry Out)端串接至下一及全加器的 CI(Carry In)端即完成漣波加法器, 圖 3-14 為四位元漣波加法器。

34 圖 3- 13 1-bit 全加器 圖 3- 14 4-bit 漣波加法器 在圖 3-1 中的環型振盪器,我們便是使用將漣波加法器的最高位元 CO(Carry Out) 經由一個反向器後,連接至漣波加法器的第零個位元的 CI(Carry In), 並將漣波加法器 的輸入端 A 接至邏輯零、將輸入端 B 接至邏輯 1。經由漣波加法器的頭尾串接後所產生 的環型振盪器,其振盪頻率即可代表漣波加法器的最大延遲時間,此時環型振盪器產生 的一個週期的時間代表了經歷兩次最長路徑所需的時間。 CI A B S CO A B CI CO S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 A B CI CO S 1-bit FA A B CI CO S 1-bit FA A B CI CO S 1-bit FA A B CI CO S 1-bit FA C0 C1 C2 C3 C4 A0 B0 A1 B1 A2 B2 A3 B3 S3 S2 S1 S0

第

第

第

第四

四

四

四章

章

章

章、

、

、

、模擬結果

模擬結果

模擬結果

模擬結果

4.1 系統行為模擬

系統行為模擬

系統行為模擬

系統行為模擬

圖 4- 1 動態電壓調整系統架構圖 Fref 1M, 1.25M, 1.5M FD FSM VDD = 1V VO=0.3~0.6V C2 C1C1 control Loading Circuit

Ring Oscillator (Critical Path) 27 級 ring osc

Level Shift

36

在本節我們使用 HSPICE,且利用 TSMC 0.18µm 1P6M CMOS 製程來模擬整個動態 電壓調整系統,如圖 4-1 所示。在此處我們定義操作在次臨界電壓下的負載電路所消耗 的最大電流為 10uA,並模擬負載電路消耗於 2uA、5uA 與 10uA 時,對系統穩定度的影 響。負載電路是將來 IC 設計時,依實際應用需求而產生的數位邏輯電路,在此處我們 使用三十二位元的線性反饋位移暫存器、十六位元的漣波加法器與十七位元的 D 型暫存 器,來模擬將來可能使用到的數位邏輯電路,如圖 3-11 所示、共計使用了 426.5 個邏輯 閘(Gate Count)。表格 4.1 為圖 3-11 的負載電路在不同製程變異與操作頻率下,模擬出 來的消耗電流大小。表格 4.2 為利用表格 4.1 的結果,計算出當負載電流為 10uA 時,預 期的負載電路最多可使用的邏輯閘數量。由表格 4.2 可知,若我們定義負載電路工作於 10uA 時,將來在負載電路的應用上,最多僅能使用約 2078.2 個邏輯閘數量。 表格 4. 1 負載電路消耗電流 消耗電流 1M 1.25M 1.5M TT 1.14 uA 1.46 uA 1.79 uA SS 1.31 uA 1.68 uA 2.05 uA FF 0.98 uA 1.26 uA 1.53 uA

表格 4. 2 預期負載電路操作於 10uA 時的 gate coute 數量 預期 GATE COUNT 1M 1.25M 1.5M TT 10uA 3730.1 2917.8 2382.5 SS 10uA 3251 2543.4 2078.2 FF 10uA 4362.2 3397.6 2781.9 圖 4-1 中,我們藉由調整 C1、C2 的電容值與負載電流的大小,來觀察這三個變數 對整體系統的影響。即 C1、C2 的電容值與負載電流改變時,對負載電路工作頻率的影 響(經由環型振盪器量測得出),以及對負載電路上工作電壓變化的大小。在接下來的模 擬中,我們使用兩種方式來做為電路的負載電流,其一、使用理想電流源,其二、使用 數位線路所產生的電流消耗。在使用第二種方法做為負載電流時,為了調整負載電流的

大小,我們並非直接使用表格 4.2 的邏輯閘數量來增加或減少負載電流消耗,而是在圖 3-11 中的負載電路上增加負載電容、如圖 4-2 所示,並藉由負載電容大小的調整改變數 位電路上的平均電流消耗,以減少模擬時資源的消耗。 圖 4- 2 負載電路 32-bit LSFR A B SUM[16:0] Q[31:0] D Q DFF SUM Q[15:0] Q[31:16] CLK 16-bit 加法器 CLOAD C LOAD CLOAD C LOAD CLOAD X32 Q[31:0] Q

38

4.2 環型振盪器之電壓頻率曲線

環型振盪器之電壓頻率曲線

環型振盪器之電壓頻率曲線

環型振盪器之電壓頻率曲線

本節模擬 27 級之環型振盪器的電壓頻率曲線,並藉由此曲線來了解動態電壓調整 系統中的頻率誤差與工作電壓的關連。 圖 4- 3 壓控振盪器在 Corner FF 之下的電壓頻率曲線 圖 4- 4 壓控振盪器在 Corner SS 之下的電壓頻率曲線圖 0.E+00 2.E+05 4.E+05 6.E+05 8.E+05 1.E+06 1.E+06 1.E+06 2.E+06 2.E+06 2.E+06 0.35 0.355 0.36 0.365 0.37 0.375 0.38 0.385 0.39 0.395 0.4 F re q u e n cy Voltage Kvco FF 0.E+00 5.E+05 1.E+06 2.E+06 2.E+06 3.E+06 0.52 0.525 0.53 0.535 0.54 0.545 0.55 0.555 0.56 0.565 0.57 F re q u e n cy Voltage Kvco SS圖 4- 5 壓控振盪器在 Corner TT 之下的電壓頻率曲線圖 由圖 4-3、圖 4-4 以及圖 4-5,我們使用 27 級的環型振盪器作為我們的壓控振盪器, 並在不同的製程變異下觀察當振盪頻率介於我們的工作頻率 1MHz 至 1.5MHz 之間的電 壓頻率轉換曲線。在動態電壓調整系統中,我們使用 7 級計數器(Counter)作為頻率比較 器,其中包含了約 0.8%的基本誤差,若考慮此誤差,我們可以在負載工作電壓上看到 一定的電壓漂移量,我們由圖 4-3、圖 4-4 以及圖 4-5 整理出,僅考慮頻率偵測器上的誤 差對負載工作電壓的漂移量、如表格 4.3 所示: 表格 4. 3 頻率偵測器 0.8%誤差對負載電壓的影響 TT SS FF

1MHz ± 0.8% ±360uV ±370uV ±390uV

1.25MHz ± 0.8% ±310uV ±360uV ±420uV

1.5MHz ± 0.8% ±360uV ±420uV ±400uV

當頻率誤差大於頻率偵測器基本的 0.8%誤差時,相對的對負載上的工作電壓漂移 量亦會增大。若動態電壓調整系統的整體誤差量為 3%時,我們以線性的方式推測在負 載上的工作電壓漂移量應如表格 4.4 所示 0.E+00 5.E+05 1.E+06 2.E+06 2.E+06 3.E+06 0.45 0.455 0.46 0.465 0.47 0.475 0.48 0.485 0.49 0.495 0.5 F re q u e n cy Voltage Kvco TT

40

表格 4. 4 動態電壓調整系統頻率 3%誤差對負載電壓的影響 TT SS FF

1MHz ± 3% ±1350uV ±1390uV ±1460uV 1.25MHz ±3% ±1160uV ±1350uV ±1580uV 1.5MHz ± 3% ±1350uV ±1570uV ±1500uV

4.3 理想電流負載與數位電路負載的差異

理想電流負載與數位電路負載的差異

理想電流負載與數位電路負載的差異

理想電流負載與數位電路負載的差異

實際電路負載時的工作頻率與 實際電路負載時的工作頻率與 實際電路負載時的工作頻率與 實際電路負載時的工作頻率與電壓變化電壓變化電壓變化電壓變化 我們利用 HSPICE 幫助我們完成系統行為模擬,在此處我們使用圖 4-2 的負載電路, 並調整負載電流為 2uA、5uA 與 10uA,且參考頻率分別輸入 1MHz、1.25MHz 與 1.5MHz, 電容式電壓轉換器的參數如下:C1 為 32 個 0.7PF 的小電容,C2 為 10uF。我們觀察在 此參數下,環型振盪器所產生出來的頻率與實際輸入參考頻率之間的誤差值,再觀察在 此條件下時,負載電路(環型振盪器)上的電壓變化大小為何,負載電路上的頻率變化與 電壓變化波形可參考附錄,並整理繪製成圖 4-6。由附錄我們可以觀察到幾個現象,製 程由 SS 到 TT 之間,以及由 TT 到 FF 之間的變異,會造成操作在次臨界電壓下的數位 電路的最低工作電壓約 70mV 至 90mV 之間的變化。由圖 4-6 可以看出我們所提出的動 態電壓調整系統可以使環型振盪器產生的頻率與輸入的參考頻率之間的頻率誤差最大 值約為 2.7%,亦即數位電路的關鍵路徑所允許的最高工作頻率與參考頻率之間會有 2.7%的誤差,我們只需在設計環型振盪器時,使環型振盪器的振盪頻率,慢於數位電路 的關鍵路徑 2.7%以上,即可確保數位電路可工作於輸入的參考頻率,且在此條件下, 數位電路上的最大電壓漣波約為 1mV。圖 4- 6 數位電路負載時之頻率誤差與漣波大小 0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading Current

Corner FF

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner FF

1M 1.25M 1.5M 0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading CurrentCorner SS

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner SS

1M 1.25M 1.5M 0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading CurrentCorner TT

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner TT

1M 1.25M 1.5M42 理想電流負載時的工作頻率與 理想電流負載時的工作頻率與 理想電流負載時的工作頻率與 理想電流負載時的工作頻率與電壓變化電壓變化電壓變化電壓變化 在此處我們使用理想電流源做為動態電壓調整系統的負載,並調整負載電流為 2uA、 5uA 與 10uA,且參考頻率分別輸入 1MHz、1.25MHz 與 1.5MHz,電容式電壓轉換器的 參數如下:C1 為 32 個 0.7PF 的小電容,C2 為 10uF。我們觀察在此參數下,環型振盪 器所產生出來的頻率與實際輸入參考頻率之間的誤差值,再觀察在此條件下時,負載電 路(環型振盪器)上的電壓漣波大小為何,並將模擬結果繪製成圖 4-7。圖 4-7 中,可知數 位電路的關鍵路徑所允許的最高工作頻率與參考頻率之間會有 2.8%的誤差,略大於使 用數位電路負載時的 2.7%。且數位電路上的最大電壓漣波約為 1.3mV,略大於使用數 位電路負載時的 1mV。由圖 4-6 與圖 4-7 比較,可知使用實際數位電路負載與使用理想 電流負載所模擬出的結果相近,因此在接下來的模擬條件中均使用理想電流負載。 0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading Current

Corner FF

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 1400 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner FF

1M 1.25M 1.5M圖 4- 7 理想電流負載時之頻率誤差與電壓變化

4.4 C2 改變時對

改變時對

改變時對

改變時對工作頻率與

工作頻率與

工作頻率與

工作頻率與電壓變化

電壓變化

電壓變化的影響

電壓變化

的影響

的影響

的影響

經由第三章的交換式電容電路中的說明後己知,由 C1 每次對 C2 充電時,在穩定 的狀態下 C2 端上的電壓變動大小與 C1 無關,僅與 C2 相關。在本節我們使用到的 C2 值分別為 10uF、5uF 與 1uF,且對應到每次充電時,C2 端的理想電壓變化為量如表格

4.5 所示。以負載電流為 10uA 時為例,C2 的電容值由 10uF 減小為 1uF 時,則每次對

0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading Current

Corner SS

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 1400 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner SS

1M 1.25M 1.5M 0 0.5 1 1.5 2 2.5 3 2u 5u 10u F re q u e n cy E rr o r( % ) Loading CurrentCorner TT

1M 1.25M 1.5M 0 200 400 600 800 1000 1200 1400 2u 5u 10u V o la tg e R ip p le (± u V ) Loading CurrentCorner TT

1M 1.25M 1.5M44

C2 充電時,C2 端上的電壓變化會由 1uV 增加至 10uV,我們再觀察 C2 值的改變會對電

路的工作頻率與漣波電壓造成什麼樣的影響。

表格 4. 5 C2 值對 Vc2 p-p的影響

IL T C2 △VC2p-p(V)

2uA 1uS 10uF 0.2uV 5uA 1uS 10uF 0.5uV

10uA 1uS 10uF 1uV

2uA 1uS 5uF 0.4uV

5uA 1uS 5uF 1uV

10uA 1uS 5uF 2uV

2uA 1uS 1uF 2uV

5uA 1uS 1uF 5uV

10uA 1uS 1uF 10uV

C2 為為為為 1uF 時之時之時之時之工作頻率與工作頻率與工作頻率與工作頻率與電壓變化電壓變化電壓變化 電壓變化 使用理想電流源做為動態電壓調整系統的負載,並調整負載電流為 2uA、5uA 與 10uA,且參考頻率分別輸入 1MHz、1.25MHz 與 1.5MHz,電容式電壓轉換器的參數如 下:C1 為 32 個 0.7PF 的小電容,C2 為 1uF,再觀察在此條件下時,環型振盪器所產生 出來的頻率與實際輸入參考頻率之間的誤差值,以及負載電路(環型振盪器)上的電壓漣 波大小為何,並將模擬結果繪製成圖 4-8。

圖 4- 8 C2 為 1uF 時之頻率誤差與電壓變化 0 5 10 15 20 2u 5u 10u F re q u e n cy E rr o r( % ) Loading Current