行政院國家科學委員會專題研究計畫 成果報告

嵌入式系統硬體平台開發與整體發展環境設計(I)

計畫類別: 個別型計畫

計畫編號: NSC92-2213-E-011-062-

執行期間: 92 年 08 月 01 日至 93 年 07 月 31 日 執行單位: 國立臺灣科技大學電子工程系

計畫主持人: 林銘波

計畫參與人員: 施宏霖 林晉禾

報告類型: 精簡報告

處理方式: 本計畫可公開查詢

中 華 民 國 93 年 9 月 21 日

行政院國家科學委員會專題研究計畫成果報告

嵌入式系統硬體平台開發與整體發展環境設計(I)

The Development and Design of an Embedded Hardware Platform and its Integrated Design Environment

計畫編號: NSC 92-2213-E-011-062

執行期限: 92 年 08 月 01 日至 93 年 07 月 31 日

主持人: 林銘波 國立台灣科技大學電子工程系 計畫參與人員: 施宏霖 林晉禾

國立台灣科技大學電子工程系

一、摘要 A. 中文摘要

由 於 積 體 電 路 積 集 密 度 的 高 度 發 展 與 成 熟,將計算機系統當作一個元件,設計複雜的數 位系統,已經成為一種可行而且最具成本效益的 方 式 。 這 種 系 統 稱 為 嵌 入 式 系 統 (embedded system)或是系統晶片(system on a chip,SOC)。

一個嵌入式系統的成功與否,必須下列三大 技術互相配合:嵌入式硬體平台的建立、整體發 展環境的發展、與嵌入式系統軟體設計,方能成 功。其中前兩者為提供硬體平台及發展環境;後 者則為應用系統的應用軟體系統設計,以定義最 後的應用產品規格。在本計畫中,我們主要著重 於設計嵌入式硬體平台與發展一個相關的整體 發展環境(integrated development environment,

IDE),以提供應用領域的使用者可以據以發展 與定義其最後的嵌入式系統。

由於目前與未來的 ASIC/嵌入式系統實現技 術,均以CPLD/FPGA 與 cell-based library 兩項技 術為主,因此在硬體平台的設計上將以Soft IP 為 主要考量,而整體發展環境(IDE)則提供 C 語 言與組合語言的程式設計環境,以適應時代的潮 流。

本計畫所設計完成的 Proto-II-6502-with-ICE 已經分別在Xilinx 的 Virtex XCV-400 FPGA 以及 TSMC 0.25 µm 元件庫(cell library)上實現以及 驗證。在FPGA 設計的部分,其系統工作頻率為 15.9 MHz,硬體模擬器工作頻率為 1.5 MHz。在 元件庫設計的部分,系統工作頻率為100 MHz,

硬體模擬器工作頻率為10 MHz,核心(core)面 積為459 µm

×

459 µm,晶片功率消耗為 78.55 mW。關鍵字:嵌入式系統,整體發展環境(IDE)、

Soft IP、SOC、FPGA/CPLD、cell-based library。

B. 英文摘要

With the advent of VLSI technology, the use of computer as a component to design a complex digital system has become a feasible and cost- effective manner. A system embedded with a computer system is usually called an embedded system or SOC (system on a chip).

Whether an embedded system is successful or not depends on how the following three techniques are cooperated: embedded hardware platform, integrated development environment (IDE), and embedded system software. The former two techniques provide a basic platform for developing the specific system; the last defines the end product based on the embedded hardware platform by the use of software tools providing by the IDE. In this project, we will concentrate on the development and realization of a new embedded hardware platform and a user friendly IDE so that the product engineers can use it to develop their specific embedded systems easily.

Since CPLD/FPGA and cell-based library are the two primary techniques for constructing ASICs and embedded system platforms for current and in the near future, our major concern in the project is to develop a soft IP for the hardware platform so that we can make full use of the flexibility of soft IPs. As for IDE, we will provide both C and assembly languages as the application development tools to fit the industry trend.

In this project, Proto-II-6502-with-ICE has been implemented and verified with Xilinx Vertex XCV-400 FPGA and TSMC 0.25 µm cell library.

In the FPGA part, the entire proto-II-6502 operates at the frequency of 15.9 MHz and ICE block operates at the frequency of 1.5 MHz. In the

the frequency of 100 MHz, ICE block operates at the frequency of 10 MHz, the core occupies the area of 459 µm

×

459 µm, and power dissipation is about 78.55 mW in the chip.Key words: embedded system, integrated

development environment (IDE), Soft IP, SOC, FPGA/CPLD, cell-based library.二、研究動機

由 於 積 體 電 路 積 集 密 度 的 高 度 發 展 與 成 熟,以往使用PCB 完成的系統,現在只需要一小 塊矽晶片即可,也因為如此大部分的消費性產品

(手機、數位相機、Camcorder、等等)均內嵌 微處理器(有些會再加上DSP 處理器)系統(即 將計算機系統當作一個元件,因而稱為嵌入式系 統),以簡化系統的設計。至於微處理器是多少 個位元(8、16、32)則依實際上的產品需要而 定。嵌入式系統有著降低成本與減少功率消耗等 絕對性的優點,因此目前及未來的電子相關產 品,將以此為主要的設計平台而不是傳統性的 PCB。

在整個電子相關產業中,嵌入式系統現在及 未來將成一個非常重要的核心,在數量上它的需 求量比桌上型電腦多 100 倍以上,單單在 1997 年,總產值就已經超過 9,408 M 美元,其中 Motorola 就已經賣掉 20 億個以上的 MC68HC11 系統。目前與未來的嵌入式系統之主要應用市場 為:通信產品、汽車控制、軍事設備、醫學儀器、

消費性電子產品、機器控制等。

由於有廣大而具有潛力的商機,目前工業界 與學術界莫不致力於發展各式各樣的嵌入式系 統,以期在此市場上佔有一席之地。然而,一個 嵌入式系統的成功與否,必須下列三大技術互相

發展、與嵌入式系統軟體設計,方能成功。其中 前兩者為提供硬體平台及發展環境;後者則為應 用系統的應用系統軟體設計,其最後的軟體則由 實際上的應用產品規格決定。

在本計畫中,我們主要著重於設計嵌入式硬 體平台與發展一個相關的整體發展環境(IDE),

以提供應用領域的使用者可以據以發展與定義 其最後的嵌入式系統。由於目前與未來的 ASIC/

嵌 入 式 系統實 現 技 術,絕 大 多 數會以 CPLD/

FPGA 與 cell-based library 兩項技術為主,因此在 硬體平台的設計上將以Soft IP 為主要考量,而整 體發展環境(IDE)則以 C 語言配合組合語言的 程式發展為主,以適應時代的潮流。

本計畫在第一年中,預計完成8 位元的 CPU 與BDM 模組 IP 的設計、驗證及 C 編譯程式、組 譯程式、模擬程式的建立。其完整的系統架構如 圖1 所示。

Data SRAM Instruction

SRAM

下載電纜

Comput er

IDE

FPGA 模擬版 Proto-II-

6502- with-ICE

圖 1 系統架構圖

在 CPU 的設計方面,我們採用 Rockwell R6502 的 ISA(Instruction set architecture)為參 考 CPU,其原因有下列幾點:一、該 CPU 的智 慧財產權已經解除;二、它與目前在8 位元市場 中廣泛使用的MC68HC11/12 系列的 CPU 具有相 當類似的架構;三、它過去為APPLE II 的 CPU,

目前在嵌入式系統上依然佔有相當大的市場;

四、在網路上可以獲取相當多的免費軟體,對於 整體發展環境(IDE)的建立頗有助益。

三、 Proto-II-6502-with-ICE 系統架構與設計

基本硬體模擬器的功能須具備:設定中斷 點、讀寫暫存器、讀寫記憶體、設定程式計數器、單步執行等。在目前具備嵌入式硬體模擬器功能 的微處理器[5][6],大多使用 IEEE 1149.1 邊緣掃 描 架 構 為 嵌 入 式 硬 體 模 擬 器 的 輸 入 輸 出 埠 介 面,本計畫亦使用IEEE 1149.1 標準來設計此崁 入式硬體模擬器。

為 了 增 加 設 計 上 的 便 利 性 , 本 計 畫 使 用 Synopsys 公司提供的 DesignWare Library[7]來進 行設計。DesignWare Library 提供 IEEE 1149.1 標 準中相關的邊緣掃描元件,包括了可參數化的測 試存取埠控制器(DW_tap)與各式的邊緣測試細 胞(DW_bc1~5、DW_bc7),可讓使用者在晶片 中快速建構出符合需求的IEEE 1149.1 邊緣掃描 測試功能。本計畫以DesignWare Library 中提供 的邊緣掃描元件為基礎,增加額外相關的電路元 件,以滿足崁入式硬體模擬器的功能。

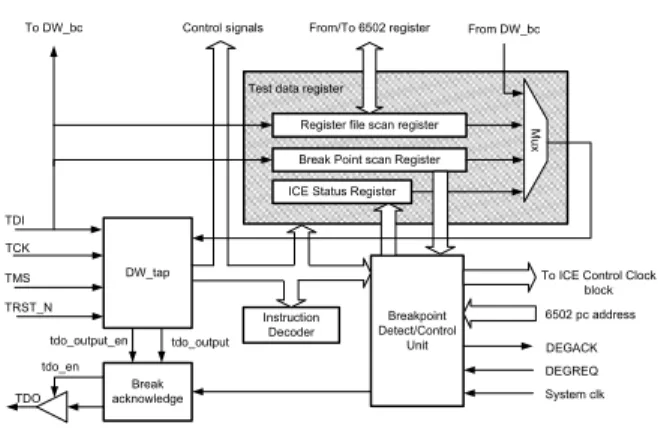

圖2 為 Proto-II-6502-with-ICE 的系統架構方 塊圖,我們將原Proto-II-6502 加入嵌入式硬體模 擬器相關的電路元件,使Proto-II-6502 具備硬體 模擬器的功能。

Proto-II-6502

E-ICE TDI

TMS TCKTRST_N DW_bc

TDO

DEGREQ DEGACK

6502 input port

6502 output port

6502 bidirectional port

Proto-II-6502-with-ICE

ICE Control

Clock

System clk

圖 2.Proto-II-6502-with-ICE 系統架構方塊圖

圖3 為嵌入式硬體模擬器架構方塊圖,所有 的硬體模擬指令和測試資料,可以藉由測試存取

埠輸入到Proto-II-6502-with-ICE 內部電路或輸出 到外部儀器。本計畫也參考ARM7TDMI 硬體模 擬器[5]設計,另設計 DEGREQ(Debug Request)

以及DEGACK(Debug Acknowledge)兩支控制 接腳,可讓外部邏輯電路或外部晶片以交握式方 法來控制Proto-II-6502-with-ICE 進入除錯模式。

DW_tap

Instruction Decoder

Break Point scan Register Register file scan register

ICE Status Register

Mux

Breakpoint Detect/Control

Unit

DEGREQ DEGACK From DW_bc

To DW_bc From/To 6502 register

6502 pc address Control signals

To ICE Control Clock block

System clk TDI

TCK

TDO TRST_N TMS

Break acknowledge

tdo_output tdo_output_en tdo_en

Test data register

圖 3. 嵌入式硬體模擬器架構方塊圖

四、硬體模擬指令與操作模式

嵌入式硬體模擬器可以根據不同的硬體模 擬指令,解碼出不同的控制訊號,並執行不同的 動作。基本硬體模擬器須具備設定中斷點、讀寫 暫存器、讀寫記憶體、設定程式計數器、單步執 行等功能,因此我們可以定義的以下指令。

1.

SETBRK: 設定中斷點2. READREGF: 讀取暫存器檔案

3.

WRITEREGF: 寫入所有的暫存器檔案 4. INSTDEGREQ: JTAG 中斷指令5.

SSTEP: 單步執行6.

READSTS: 讀取 ICE 狀態暫存器7.

RESTARTE: 返回 Emulation Mode8.

RESTARTN: 返回 Normal Mode9.

BYPASS: JATG 標準10.

SAMPLE/PRELOAD: JATG 標準11.

EXTEST: JATG 標準硬 體 模 擬 器 可 以 根 據 輸 入 的 硬 體 模 擬 指

及外部晶片產生的控制訊號,決定進入何種操作 模式。

我 們 設 計 的 硬 體 模 擬 器 具 有 三 種 操 作 模 式。(1) 正常模式(Normal mode),(2) 模擬模 式 (Emulation mode),(3)除錯模式(Debug mode)。當 Proto-II-6502-with-ICE 位於正常模式 時,硬體模擬器不會去執行中斷點檢查,就如同 Proto-II- 6502-with-ICE 不具備任何硬體模擬功 能,當外部晶片送入中斷要求訊號,或送入強制 中斷的硬體模擬指令,才會進入除錯模式。進入 模擬模式,硬體模擬器會執行中斷點檢查,當 Proto-II-6502- with-ICE 執行結果符合硬體模擬器 的中斷要求,則會進入除錯模式。當進入除錯模 式 時 , Proto-II-6502-with-ICE 會 暫 停 內 部 Proto-II-6502 的執行動作,此時晶片由硬體模擬 器控制,並可執行讀寫記憶體,讀寫微處理器內 部暫存器、設定中斷點、執行單步執行、回傳微 處理器狀態、進入正常模式,以及進入模擬模式 等硬體模擬功能。圖4 為硬體模擬器操作模式轉 移圖。

1 0

Proto-II-6502 Core Clock

Breakpoint Detect/Control

Unit System Clock

Instruction Decoder

DW_tap

break_occur update_en

update_dr

圖 4. 硬體模擬器操作模式轉移圖

當晶片進入除錯模式時,內部Proto-II-6502 的電路狀態必須保持不變,因為Proto-II-6502 微 處理機不具有管線化架構與動態電路,將微處理 器的時脈訊號停止,是最簡單的方式,而且也不

態。當執行寫入微處理器內部暫存器的動作,可 由DW_tap 與指令解碼器的控制訊號產生寫入資 料所需要的時脈。圖5 為 Proto-II-6502-with-ICE 系統時脈控制架構。

Normal Mode

RESTARTN

RESTARTE

DEGREQ or INSTDEGREQ or Break Point Detected or

6502 BRK instruction Debug

Mode

Emulating Mode DEGREQ or

INSTDEGREQ

圖 5. Proto-II-6502-with-ICE 系統時脈控制架構圖

五、整合開發環境的架構

我們使用 Borland C++ Builder 5.0 來開發 6502 IDE,它包含以下的功能:

1. 文字編輯 2. 檔案和專案管理 3. 程式的編譯和組譯 4. 模擬器呼叫的功能 5. ICE 控制介面

其中ICE 控制介面是針對 Proto-II-6502-with-ICE 所設計,其具有程式下載、ICE 指令控制、以及 記憶體存取的功能。另外,我們選擇兩套網路上 的免費軟體:6502SIM (DOS 介面)以及 6502 Simulator (Windows 介面)作為 6502 的模擬器,

這兩套程式可以直接由IDE 呼叫執行。

圖6 為 6502 IDE 的主視窗,其中包含功能表 列、功能快捷列、專案檔案顯示列以及專案執行 訊息視窗四個部分。功能表列主要是將IDE 所有 的功能一一分類,以表單的格式顯示,使用者可 依欲執行工作的類別點選功能表列,視窗便會出

現該功能的列表或直接執行點選的工作。而功能 快捷列則是列出最常被使用者使用的功能,由左 至 右 分 別 為 : NewProject 、 OpenProject 、 NewEditor、Debugger、DosSIM 以及 WinSim 的 功能,使用者只須在功能快捷列點選便能執行這 些功能。

專案建構訊息視窗 專案檔案

顯示列

功能快捷列功能表列

圖 3.1.1 6502 IDE 主視窗

圖 6. 6502 IDE 的主視窗

在訊息顯示方面,使用者在執行建構(make)

之後,專案建構訊息視窗會顯示檔案輸出結果,

如圖7 所示。圖中的專案建構訊息視窗顯示右邊 顯示列中專案建構的結果,其包含編譯、組譯和 連結的檔案及程式庫,最後顯示輸出的檔案。

圖 7. 專案建構之後的訊息顯示

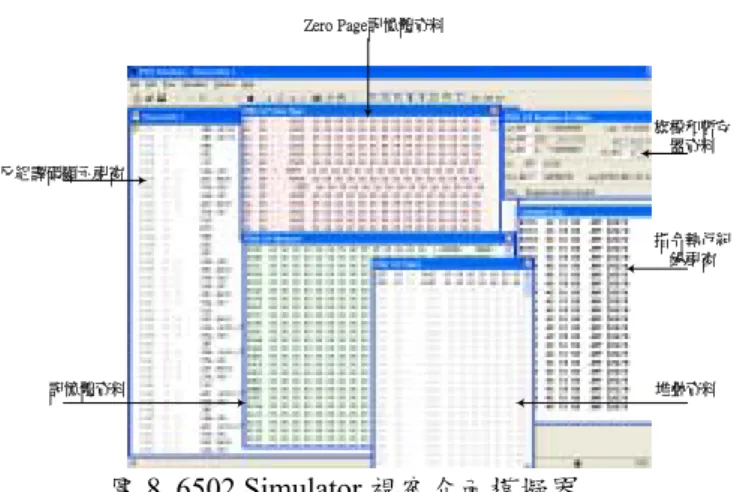

在功能表列點選 Simulator->WinSim 便會出 現圖8 的視窗,這是一個視窗介面的模擬器,當 檔案被載入時會同時出現反組譯碼、Zero Page 記憶體資料、記憶體資料、堆疊資料、指令執行

紀錄以及旗標和暫存器六個視窗,使用者可以很 清楚的觀察指令執行的結果。

Zero Page記憶體資料

記憶體資料 反組譯碼顯示視窗

旗標和暫存 器資料

指令執行紀 錄視窗

堆疊資料

圖 8. 6502 Simulator 視窗介面模擬器

Proto-II-6502-with-ICE 是透過 JATG 的傳輸 介面和電腦的並列埠建立連線,因此在ICE 控制 介面的控制介面當中須嵌入JTAG 驅動程式來達 到傳輸的功能。在視窗設計的考量上,我們加入 Parallel port control 視窗來測試電腦的並列埠是 否正常;除此之外,我們也設計 Virtex JTAG control 視窗來執行 Xilinx Virtex FPGA 晶片上的 JTAG 基本功能,藉以測試 JTAG 連線是否有產 生問題。

圖 9. ICE JTAG 命令功能視窗

圖 9 的視窗中主要有兩個功能:下達 ICE 指令以及接收暫存器的資料。視窗下方 ICE JATG command 中有許多按鍵,每一個都分別對 應 Proto-II-6502-with-ICE 指令,除了做指令執 行 、 單 步 執 行 功 能 外 , 還 可 以 藉 此 讀 取

Register/Flags 的顯示列裡,或將 Register/Flags 的顯示列的資料寫回Proto-II-6502-with-ICE 的暫 存器內。

在 ICE 控制介面的視窗上按下 Hex file download 的選項,便會出現圖 10 的視窗,這個 是視窗主要的功能是載入並分析專案建構後所 產生的*.hex 檔,將其個別的位址和資料抽出分 成視窗中Hex file list 的格式,即前四個字元是位 址後兩個字元是資料。當按下 Download 的按鍵 之後,程式會把Hex file list 中的資料透過 JTAG 傳 送 到 Proto-II-6502-with-ICE , 並 由 Proto-II- 6502-with-ICE 依位址寫入資料到記憶體。

圖 10. Hex file download 功能視窗

在 ICE 控制介面的視窗上按下 Hex file download 的選項,便會出現圖 11 的視窗,這個 視窗主要用來控制Proto-II-6502-with-ICE 存取記 憶體之用。除了可以對單一位址的記憶體寫入和 讀取之外,Write Loop 的功能是對 0~FF 這個區 段的記憶體寫入同一筆資料,藉以測試記憶體寫 入是否正常。而Read Loop 則可設定起始位址和 讀取範圍(0~FFFF),藉以讀取記憶體的資料以 觀察資料是否正確。

圖 11. Memory control 功能視窗

六、FPGA 設計實現與驗證流程圖 12 為 FPGA 測試系統線路圖,其基本的 邏輯架構與暫存器轉換層測試平台一致。整個測 試環境包括電腦印表機埠(Printer Port),FPGA,

兩個32 k × 8 的 SRAM 以及根據平行下載電纜系 統(Parallel Download Cable Scheme)[8]所擴展 而成的JTAG 電纜電路。

Proto II 6502 Core with ICE

A15 A[15:0]

D[7:0]

NMI IRQ

READY RST

R_WB

FPGA TDI

TCK TMS TRST_N TDO

Data SRAM 32K X 8 CE WE A[14:0]

D[7:0]

OE

Instruction SRAM 32K X 8 CE WE A[14:0]

D[7:0]

OE A15

DEGREQ

Printer Line

Computer

JTAG Cable Circuit

圖 12. Proto-II-6502-with-ICE FPGA 測試系統線路圖

圖13 為測試流程圖。整體發展環境中的 ICE 控 制 介 面 , 首 先 使 Pro-to-II-6502-with-ICE 的 RESET 訊號保持為 1,使內部 Proto-II-6502 進入 RESET 狀態。再利用嵌入式硬體模擬器的寫入記 憶 體 功 能 , 將 機 器 碼 下 載 至 指 令 記 憶 體(instruction memory)內,使用控制軟體執行硬 體模擬器功能,並將Proto-II-6502 啟動,觀察嵌 入式硬體模擬器功能是否正確。

S ta rt

C h e c k th e IC E fu n c tio n a n d c o m p a re th e c a lc u la tio n re s u lt w ith

e x p e c te d d a te

P ro g ra m fin is h e d ?

N o m o re p a tte rn s ?

E n d D o w n lo a d th e

R O M c o d e b y IC E fu n c tio n K e e p C P U in th e

re s e t s ta te

N o

N o Y e s

Y e s S e t IC E fu n c tio n

R e le a s e th e re s e t s ig n a l o f C P U

圖 13. FPGA 測試流程圖

七、 Proto-II-6502-with-ICE 元件庫設計與驗 證

經 自 動 化 佈 局 驗 證 完 畢 後 , 我 們 使 用 Cadence 公司的 Dracula 軟體做 LVS 驗證,並使 用 Mentor 公司的 Calibre 軟體做 DRC 驗證,以 確保晶片在下線時的正確性。經驗證後的晶片,

我們使用 Calibre LPE 淬取其等效之電晶體層電 路,並以 Synopsys 公司的 Nanosim Timemill/

Powermill 功能做電晶體層模擬驗證。

執行Timemill 模擬時,依照 TSMC 0.25 µm 元件庫規格所設定的三種操作條件,FF(Fast NMOS Fast PMOS model)、TT(Typical NMOS Typical PMOS model)、SS(Slow NMOS Slow PMOS model),分別以 100 MHz 的操作頻率進 行模擬驗證,其結果均與暫存器轉換層模擬結果 一致。

使用 Powermill 模擬可知,當晶片操作環境 在TT 條件下,且系統工作時脈為 100 MHz、嵌 入式硬體模擬器工作時脈為10 MHz 時,核心平 均 電 流 為 13.49 mA,核心消耗功率為 48.35 mW;I/O 平均電流為 8.85 mA,I/O 消耗功率為 29.20 mW,故晶片消耗功率為 78.55 mW。

八、結論

在本計畫中,我們設計了Proto-II-6502-with- ICE 8 位元微處理器 Soft IP;在 PC 上建立 Proto- II-6502-with-ICE 的整體發展環境(IDE),以提 供使用者設計、驗證、實現其最後規格的嵌入式 系統。

基於此Soft IP 的建立,在未來的 SOC 相關 研究問題的研究上,例如低功率SOC 設計問題、

SOC 測試問題、16/32 位元 CPU、及時作業系統,

將有相當大的助益。完成的系統亦可以技術轉移 予相關業者使用。

本計畫所設計的Proto-II-6502-with-ICE 已分 別在Xilinx 的 Virtex XCV-400 FPGA 以及 TSMC 0.25 µm 元件庫(cell library)上實現以及驗證。

在 FPGA 設計的部分,其系統工作頻率為 15.9 MHz,硬體模擬器工作頻率為 1.5 MHz。在元件 庫設計的部分,系統工作頻率為100 MHz,硬體 模擬器工作頻率為10 MHz,核心(core)面積為 459 µm

×

459 µm,晶片功率消耗為 78.55 mW。晶 片 的 規 格 表 歸 納 於 表 1 , 而 Proto-II-6502- with-ICE 晶片的實體圖如圖 14 所示。

表 1 晶片規格表

製程 TSMC 0.25 µm 包裝種類 SB40 核心面積(不含 I/O

pad 和 Power ring) 459 µm × 459 µm 晶片面積 1574.34 µm × 1574.34 µm 工作頻率 (系統/硬

體模擬器) 100 MHz / 10 MHz 工作電壓

(extVDD/VDD) 3.3 V / 2.5 V

晶片功率消耗 78.55 mW

圖 14. Proto-II-6502-with-ICE 晶片實體圖

九、參考文獻

1. 張慈牧,6502指令集架構相容之微處理器智產 設計與實現,國立台灣科技大學電子工程系,

2003。

2. Judi N. Fernandez, Donna N. Tabler, and Ruth Ashley, 6502 Assembly Language Programming, STG, 1983.

3. Richard Haskell, APPLE II 6502 Assembly Language Tutor, Prentice-Hall, Inc., 1983.

4. IEEE Standard Test Access Port and Boundary- scan Architecture, IEEE Std. 1149.1-2001, 2001.

5. The ARM7TDMI Debug Architecture Application Note 28, Advanced RISC Machines Ltd (ARM), Dec. 1995.

6. Barbara Johnson, Programming the DSP56300 Once and JTAG ports, Motorola Semiconductor Products Sector Application Note, 2000.

7. Guide to DesignWare Library Documentation, Synopsys, Inc., May 2002.

8. JTAG Programmer Guide, Xilinx, Inc. 2000.

![圖 11. Memory control 功能視窗 六、FPGA 設計實現與驗證流程 圖 12 為 FPGA 測試系統線路圖,其基本的 邏輯架構與暫存器轉換層測試平台一致。整個測 試環境包括電腦印表機埠(Printer Port),FPGA, 兩個 32 k × 8 的 SRAM 以及根據平行下載電纜系 統(Parallel Download Cable Scheme)[8]所擴展 而成的 JTAG 電纜電路。 Proto II 6502 Core with ICE A15A[15:0] D[7:0]N](https://thumb-ap.123doks.com/thumbv2/9libinfo/9127095.411327/8.892.100.422.90.322/Memory功能視窗設計實現與驗證流測試系統線路圖其基本的邏輯台一致整.webp)