台灣師範大學機電科技學系 -1-

第二章 第二章 基礎 基礎 VLSI VLSI 製程模組技術 製程模組技術

2-1 矽晶的性質與加工成型 2-2 CMOS的結構與作用原理 2-3 薄膜沈積

2-4 黃光微影製程 2-5 溼式與乾式蝕刻 2-6 熱製程與離子摻雜 2-7 無塵室工作須知

C. R. Yang, NTNU MT

半導體 半導體 IC製造流程 IC 製造流程

台灣師範大學機電科技學系 -3-

2- 2 -1 1 矽晶的性質與加工成型 矽晶的性質與加工成型

1780~2000℃

純度98%

(反應消耗電功率極大12~14KW-hr/公斤) 首先生成SiC,SiC再與SiO2作用,形成Si, SiO, CO

在坩堝內加熱使矽融溶,藉由種晶(seed)的帶領,以 拉昇器將鑄棒往上拉,造成一個固-液相的界面。

雜質原子會往液相跑,留在鑄棒尾端,因此尾端必 須切掉拋棄。

決定拉昇速度因素:

• 矽融溶潛熱

• 固化速率

• 溫度梯度

• 固液兩相的熱導係數 (長一根8吋晶圓鑄棒約 需兩天)

必須再精煉

CZ長晶法 CZ

長晶法C. R. Yang, NTNU MT

台灣師範大學機電科技學系 -5-

Miller indices

<100> <110> <111> (

<100> <110> <111> (堆積最密 堆積最密) )

轉450 轉450三個晶格平面與結晶軸交點座標之倒數 三個晶格平面與結晶軸交點座標之倒數

(h k l ( h k l ) )平面米勒指數

平面米勒指數{ {h k l h k l } }平面族

平面族((對立方晶格而言

對立方晶格而言)) [h k l [ h k l ] ]方向指數

方向指數< <h k l h k l > >方向族

方向族((對立方晶格而言

對立方晶格而言))

C. R. Yang, NTNU MT

八面體代表的涵意 八面體代表的涵意

z

z 點 點 :<100> : <100>

z z 稜線:<110> 稜線: <110>

z z 面 面 :<111> : <111>

矽為矽為四價鍵四價鍵 矽為

矽為鑽石立方結構 鑽石立方結構

台灣師範大學機電科技學系 -7-

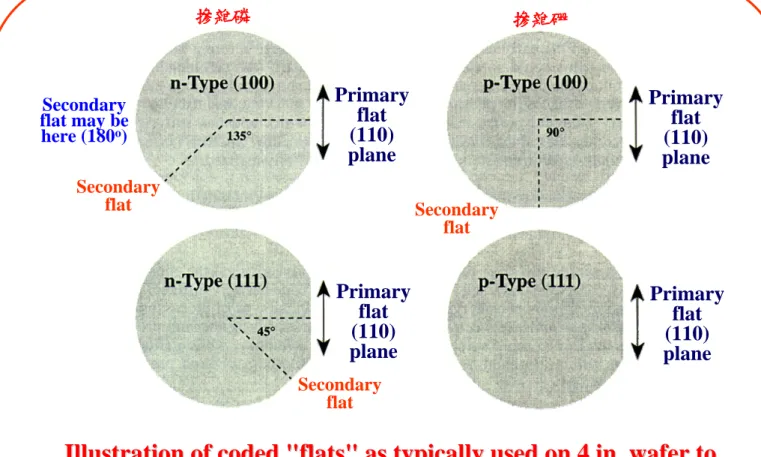

Primary flat (110) plane

Primary flat (110) plane

Primary flat (110) plane

Primary flat (110) plane Secondary

flat

Secondary flat

Secondary flat Secondary

flat may be here (180

o)

Illustration of coded "flats" as typically used on 4 in. wafer t Illustration of coded "flats" as typically used on 4 in. wafer to o

help identify them (SEMI standard).

help identify them (SEMI standard).

摻雜磷 摻雜硼

C. R. Yang, NTNU MT

注意各流程說明與目的!注意各流程說明與目的!

台灣師範大學機電科技學系 -9-

方位指定加工 方位指定加工

平邊與V 平邊與 V- -型槽 型槽

Flat & Notch Grinding

C. R. Yang, NTNU MT

切片 切片 (Slicing) (Slicing)

台灣師範大學機電科技學系 -11-

圓邊 圓邊 (Edge Profiling) (Edge Profiling)

高速旋轉 低速旋轉

C. R. Yang, NTNU MT

研磨 研磨 &拋光 & 拋光

Lapping & Polishing Lapping & Polishing

•除去切片或輪磨所造成的鋸痕及表面損傷

•改善晶圓的曲度、平坦度、平行度

•具單面研磨機與雙面研磨機

具SiO2的微細懸浮矽酸膠 及NaOH(或KOH、NH4

OH)

台灣師範大學機電科技學系 -13-

正摻雜(摻入的三族元素稱為受體) 負摻雜(摻入的五族元素稱為施體)

C. R. Yang, NTNU MT

晶圓最大及最小的厚度差 彎曲度/撓曲度

P type, 摻雜硼

CZ長晶方法

晶圓為Test等級

晶圓為Prime等級

矽晶圓的規格 矽 晶圓的規格

(晶片等級區分:Prime, Test, Dummy)

台灣師範大學機電科技學系 -15-

比例與時間各家會有所差異 比例與時間各家會有所差異

SiO

2會沾水Si不沾水

或是旋乾(spinning dry) 去除有機物

去除氧化膜

去除微粒子與有機物 去除金屬

去除氧化膜

相當重要!!

C. R. Yang, NTNU MT

2 2 -2 CMOS - 2 CMOS的結構與作用原理 的結構與作用原理

Metal-Insulator-Semiconductor (MIS) The heart of a MOSFET SiO

2Si

V

gM O S

Metal-Oxide-Silicon Field Effect Transistor

V

g台灣師範大學機電科技學系 -17-

依其傳導載子的不同可以分為PMOS及NMOS 二種。若將這二種MOS合在一起使用則稱為互 補式金屬氧化半導體電晶體,即為MOSFET

CMOS(Complementary MOS)。

CMOS的優點為操作時比較省電,因此一般電

路佈局設計就是以CMOS為基本單元來設計。MOSFET

金屬Al 或多晶矽(摻雜磷)

場氧化層 防止相臨電晶體

發生短路

N (P) N (P)

P (N)型底材

C. R. Yang, NTNU MT

MOS電晶體構成四接點電子元件

V

d> 0

V

g> 0

V

sV

sub(接地)

電晶體可視為一種固態開關

(接地) (決定開關)

(決定電流大小)

電子流(接地) V

g< 0

V

d< 0

V (接地)

台灣師範大學機電科技學系 -19-

NMOS

當在閘極施以正偏壓時,就會在氧化層下方薄區內感應出許多電子。當在汲極施加一個正偏 壓之後,聚集的電子就可經由源極與汲極之間 的電子通道導通。

PMOS

當在閘極(gate)施以負偏壓時,就會在氧化層下 方薄區內感應出許多電洞,當在汲極(drain)施 加一個負偏壓之後,聚集的電洞就可經由源極

(source)與汲極之間的通道導通。

C. R. Yang, NTNU MT

2- 2 -3 3 薄膜沈積 薄膜沈積

Chemical Vapor Deposition (CVD) Chemical Vapor Deposition (CVD)

z

PECVD

z

LPCVD

z

APCVD

z

MOCVD

(光電薄膜沈積)台灣師範大學機電科技學系 -21-

氧化矽薄膜沈積 氧化矽薄膜沈積

z 磷矽玻璃(PSG)

APCVD (400℃左右@ 常壓下)

PECVD (400℃以下)

PSG與BPSG的用途說明

離子轟擊(Ion bombardment)的效用

z熱流動(flow):將PSG與BPSG加熱至其玻璃 轉換溫度(glass transition temperature, Tg)以上

(850~950℃, 20~40 min),使它們產生流動現象

,達到表面平坦化的目的,以利後續製程的進 行。

z 硼磷矽玻璃(BPSG)

APCVD (400℃左右@ 常壓下)

C. R. Yang, NTNU MT

氮化矽薄膜的應用 氮化矽薄膜的應用

Si

3N

4不易被氧所滲透,可作為進行場氧化層(field oxide)製作時,防止晶片表 面的主動區域(active area)遭受氧化的幕罩層,此即為LOCOS(Local oxidation of silicon)製程。

Si

3N

4對鹼金屬離子的防堵能力佳,且不易被水氣(moisture)所滲透,廣泛應用 於半導體元件的保護層(passivation)

SiO

2的蝕刻幕罩(mask),並可作為矽晶圓以KOH蝕刻,製作矽微結構時的蝕

刻幕罩(MEMS應用)

台灣師範大學機電科技學系 -23-

LPCVD (700~800℃@ 0.1~1Torr)

3SiH 2 Cl 2(g) +7NH 3 (g) → Si 3 N 4(s) +3NH 4 Cl (s) +3HCl (g) +6H 2 (g)

PECVD (450℃以下)

SiH 4(g) +NH 3(g) RF+N →

2(g)SiN x :H (s) + +3H 2 (g) x: 0.8~1.2

(應力問題說明) (Silane)

易爆炸 室溫為液態

C. R. Yang, NTNU MT

Sputtering Sputtering

TiN, TiW

Physical Vapor Deposition (PVD)

Physical Vapor Deposition (PVD)

台灣師範大學機電科技學系 -25-

Evaporation (PVD) Evaporation (PVD)

(Joule heat or Electron beam) (Joule heat or Electron beam)

Dual E-gun evaporator (交大半導體技術中心)

蒸鍍對合金或是化合物的沈 積成份控制性差C. R. Yang, NTNU MT

台灣師範大學機電科技學系 -27-

CVD與 CVD 與 PVD的比較 PVD 的比較

( c )

( d )

PVD的缺點︰

階梯覆蓋(Step coverage)能力較差(CVD>濺鍍>真空蒸鍍

>E-gun)

沈積薄膜的純度不易控制(蒸鍍時坩鍋材質亦會析出附著)

對合金或是化合物的沈積成份控制性差(不同材料蒸發速 率不同)

先進的VLSI製程裡,僅Al金屬仍應用濺鍍長膜外

,其餘均改以CVD進行薄膜沈積

C. R. Yang, NTNU MT

2- 2 -4 4 黃光微影製程 黃光微影製程

台灣師範大學機電科技學系 -29-

基板

光罩 光阻 紫外光曝光

薄膜

基板 基板

薄膜

正光阻 顯影 負光阻

薄膜

基板 薄膜

蝕刻

薄膜 基板

基板 薄膜

光阻去除

薄膜 基板

正、負光阻微影製程示意圖

黃光微影製程 黃光微影製程

C. R. Yang, NTNU MT

光罩的設計技巧 光罩的設計技巧

z

光罩繪製是微影製程最基本步驟,透由光刻程序將光罩上的圖案的轉移 至光阻,才能在基材上製作微結構。

圖案(Layout)設計

CADENCE L-EDIT AUTOCAD

轉檔成GDS格式

送件製作光罩

交大半導體技術中心奈米元件實驗室 台灣光罩 新台科技 光罩的設計製作流程

GDS圖檔送至光罩製作單位後,須註明圖案的範圍與邊界座標、最小線寬,並指定 透光(Clear)與不透光(Dark)區域。Clear表示製作的光罩繪圖的區域為可透光,而 Dark表示繪圖的區域為不可透光。Clear與Dark區域的選擇,則視採用的光阻種類(

正、負光阻)與製程需要而定。圖案設計可由不同層(Layer)之Layout一起組成,並 以不同數字編號及顏色區分層次,這些層號資料必須提供給光罩製作單位。通常每 層Layout做一片光罩,同層圖案只能指定都是Clear或都是Dark,不可要求同層圖 案有些作成Clear區域,有些則作成Dark區域。

台灣師範大學機電科技學系 -31-

光罩的設計技巧

光罩的設計技巧 (續 ( 續) )

微致動器設計與製作

微致動器設計與製作

1. 電路圖案

2. 犧牲層圖案 3. 結構圖案

■ 透光區

■透光區

■

不透光區光罩佈局設計,共三道光罩

C. R. Yang, NTNU MT

光阻的微影程序 光阻的微影程序

Dehydration Bake

resist

resistVacuum

Spin Coating

Soft Bake

Exposure UV

Post Exposure Bake

10-15min @ 250℃(optional)

? dosage/?thickness

Development

(agitation)

? min @ ? ℃

(Rinse)

(Priming)

台灣師範大學機電科技學系 -33-

微影程序說明 微影程序說明

z晶片前處理:去水烘烤與塗底(Hexamethyldi-silazane, HMDS)增加光阻附著性

z旋轉塗佈:影響P.R.厚度之因素有注入P.R.之體積、晶圓之大小、轉速、 P.R.黏度

(光阻必須存放於冷藏櫃中,使用前再拿出室溫中放置至少30分鐘)

HMDS Oven (精儀中心)

Spin coater ( I ) (精儀中心)

Spin coater ( II ) RC-6 (交大機械系)

C. R. Yang, NTNU MT

微影程序說明 微影程序說明 (續 ( 續 ) )

z 預烤(pre-bake)或稱軟烤(soft-bake)

Hot plate

台灣師範大學機電科技學系 -35-

微影程序說明 微影程序說明 (續 ( 續 ) )

z 曝光(exposure)與光罩對準(mask align)

C. R. Yang, NTNU MT

微影程序說明

微影程序說明( (續 續) )

台灣師範大學機電科技學系 -37- 玻璃鍍鉻光罩

石英鍍鉻光罩

X-ray光罩

汞弧光燈光譜(過濾後)0.5μm 解析度線寬

0.35μm

0.25μm 0.18μm

曝光源的分類 曝光源的分類

解析度=Kλ/NA

C. R. Yang, NTNU MT

單面光罩對準 單面光罩對準

光罩

上視顯微鏡

矽晶片

對準記號

以可見光做單面對準

光阻

台灣師範大學機電科技學系 -39-

光罩 光罩 -晶圓對準示意圖 - 晶圓對準示意圖

Patterned Wafer Mask 2

Mask 3

C. R. Yang, NTNU MT

實際aligner key的大小

台灣師範大學機電科技學系 -41-

Wafer chuck

Mask holder

單面光罩對準設備 單面光罩對準設備

C. R. Yang, NTNU MT

量產型曝光設備 量產型曝光設備

Source: KarlSuss technology report

台灣師範大學機電科技學系 -43-

以可見光做雙面對準

放入矽晶片

雙面光罩對準 雙面光罩對準

C. R. Yang, NTNU MT

微影程序說明 微影程序說明( (續 續 ) )

z 顯影(development)

驟:

顯影

顯微鏡觀察系統

台灣師範大學機電科技學系 -45-

微影程序說明 微影程序說明( (續 續) )

z 光阻去除(strip)

溼式去光阻:有機溶劑如丙酮

無機溶液如硫酸(H2SO4)加 雙氧水(H2O2)

乾式去光阻:氧電漿(O2plasma)

z 硬烤(post-bake or hard-bake)

C. R. Yang, NTNU MT

Cr-7

2 2 -5 - 5 溼式與乾式蝕刻 溼式與乾式蝕刻

台灣師範大學機電科技學系 -47-

感應耦合電漿蝕刻(ICP-RIE)系統,

PIDC

反應性離子蝕刻(RIE)系統,

NTNU MOEMS Lab.

C. R. Yang, NTNU MT

濕式蝕刻法 乾式蝕刻法

溼式與乾式蝕刻 溼式與乾式蝕刻

電 漿

台灣師範大學機電科技學系 -49-

溼式蝕刻 溼式蝕刻

蝕刻是緊接著微影後的一個重要製程,當微影步驟將光罩上的圖案轉移到光 阻後就可以進行蝕刻,此時薄膜上黏有光阻的部分不會被蝕刻,所以光罩上 的圖案也間接的轉移到薄膜上,平常我們所說的線寬不儘是指微影製程後的 寬度,而是蝕刻後薄膜的線寬,因此除了微影製程解析度要高外,蝕刻製程 後薄膜截面的輪廓更值得我們注意。

選擇性 (selectivity) 是指薄膜的蝕刻率與光阻或蝕刻幕罩的蝕刻率之比,選擇 性愈高表示蝕刻大部分對欲蝕刻的薄膜進行,對光阻或蝕刻幕罩的影響愈小

,則薄膜重現光阻圖案的準確性愈高。

z 溼蝕刻 (wet etching)

C. R. Yang, NTNU MT

基板 基板

薄膜 光阻

等向性蝕刻

基板

非等向性蝕刻 基板

完全非等向性蝕刻

等向性蝕刻、非等向性蝕刻與完全非等向性蝕刻

在進行蝕刻時如果對每個方向 (xyz) 的蝕刻速率都一樣則稱為等向性蝕刻

(isotropic etching) ,這種蝕刻線寬會變大而側壁 (side wall) 呈弧形,稱額外

被蝕刻的部份為切底 (undercut) ;反之若每個方向的蝕刻率不同則稱為非等

向性蝕刻,此時切底較改善且側壁趨向垂直,完全非等向性蝕刻是專指對垂

直方向 (z) 進行蝕刻,側壁達到垂直 90° 而且沒有切底。

台灣師範大學機電科技學系 -51-

常見半導體材料的蝕刻藥品 常見半導體材料的蝕刻藥品

資料來源:交通大學半導體技術管理中心

C. R. Yang, NTNU MT

二氧化矽的蝕刻主要以氫氟酸來進行,例如氫氟酸與氟化氨 (NH

4F) 混合 的緩衝氧化矽蝕刻液(BOE),氫氟酸直接與矽反應,氟化氨則補充在蝕 刻反應中消耗的氟離子,反應式如式 2-1 。由於二氧化矽的生長方式有 溼氧、乾氧、化學氣相沈積等,而且還有經過摻雜的磷矽玻璃與硼磷矽 玻璃,對氫氟酸的蝕刻速率都不一樣,基本上以氧化方式的二氧化矽緻 密最高,所以蝕刻率較慢,高摻雜硼會降低蝕刻率,而高摻雜磷則會增 加蝕刻率。

SiO

2+ 6HF → H

2+ SiF

6+ 2H

2O (式 2-1)

二氧化矽的蝕刻

二氧化矽的蝕刻

台灣師範大學機電科技學系 -53-

Resist

SiO

2Si

Mask

Si Si

Si Si

SiO

2Si

SiO

2SiO

2SiO

2SiO

2Positive Resist Negative Resist

C. R. Yang, NTNU MT

半導體常用的材料如單晶矽、多晶矽、二氧化矽、鋁等物質的蝕刻液對光阻的 選擇性都很高,但氮化矽的蝕刻液磷酸對光阻的選擇性就很差,所以可以在氮 化矽上先長一層二氧化矽,微影後蝕刻二氧化矽再利用二氧化矽當幕罩來蝕刻 氮化矽,事實上溼蝕刻的進行與蝕刻液組成、攪拌 (stirring) 、溫度、薄膜生 長條件、緻密度等都有關係,以下介紹幾種常用材料的溼蝕刻。

基板 基板

微影

蝕刻二氧化矽 蝕刻氮化矽

氮化矽 二氧化矽蝕刻幕罩 光阻圖案

基板 基板

氮化矽 二氧化矽蝕刻幕罩

利用二氧化矽當作氮化矽之蝕刻幕罩

氮化矽的蝕刻

氮化矽的蝕刻

台灣師範大學機電科技學系 -55-

蝕刻液 蝕刻物

質

單晶 矽

多晶 矽

二氧 化矽

磷矽 玻璃

氮化 矽

鋁 鎢 鈦 光阻

49% HF 二氧化

矽

* 0 2300 3600 14 4.2 <5 >1000 0

10H2O:1HF(49%) 二氧化 矽

* 0.7 23 470 1.1 250 0 1100 0

85% H3PO4160 °C 氮化矽 * 0.7 0.07 2.4 2.8 980 * * 55

126HNO3:60H2O:5NH4F 矽 150 310 8.7 170 0.2 400 13 300 0

33% KOH 80 °C 單晶矽 1400 >1000 7.7 38 0 >1000 0 * >1000

16H3PO4:1HNO3:1CH3COO H:2H2O 50 °C

鋁 * <1 0 <1 0 660 * 0 0

20H2O:1H2O2:1HF 鈦 * 1.2 12 210 0.8 >10 0 880 0

H2O2 鎢 * 0 0 0 0 <2 19 0 <0.2

50H2SO4:1H2O2120 °C 金屬有 機

* 0 0 0 0 180 * 240 >1000

CH3COCH3(ACE) 光阻 * 0 0 0 0 0 * 0 >4400

幾種常用薄膜溼蝕刻液與蝕刻率 (nm/min) 比較 (本表節錄自 Journal of Micro-Electro-

Mechanical Systems,Vol.5 , No.4 ,第256頁)

註:單晶矽為 <100> 矽;多晶矽為 n+ ;二氧化矽為溼氧化;磷矽玻璃為經過退火處理;鋁含 2% 的矽;鎢與鈦都是利用濺鍍沈積;光阻為 OCG 820 PR

C. R. Yang, NTNU MT

Lift- Lift -off off 製程說明 製程說明

基板 模板層

微影 基板

濺鍍金屬

金屬圖案

模板層圖案

掀離(lift-off)是一種不經由蝕刻而定義出薄膜 (主要是金屬) 圖案的方法。 首先沈積一層較厚 的模板層 (stencil layer) ,以微影製程定義出與需要相反的圖案,之後濺鍍或蒸鍍較薄的金 屬在整個晶片上,關鍵是基板與模板層上的金屬沒有連在一起,所以將晶片浸入模板層的蝕 刻液時,模板層連同其上的金屬會整個掀開,留在基板上的就是所需要的圖案了,當某種薄 膜不易找到適當的蝕刻液,亦即其蝕刻液對光阻或其他薄膜的選擇性很差時,剝離製程就變 得非常重要,尤其是針對金屬圖案的定義。

台灣師範大學機電科技學系 -57-

substrate resist

(a) Define resist

(b) Metal deposition

Metal source

Acetone

(c) Strip resist

Construction of metallization patterns by life

Construction of metallization patterns by life- -off process off process

C. R. Yang, NTNU MT

台灣師範大學機電科技學系 -59-

乾蝕刻沒有液態的蝕刻 溶液,主要分為物理濺 擊或離子銑削、電漿蝕 刻、與介於兩者之間的 活性離子蝕刻三類,右 圖 是三者蝕刻特性與壓 力、激發能量的分類關 係圖。

z 乾蝕刻 (dry etching)

小於 100 millitorr

100 millitorr 範圍

壓力較高

物理濺擊或離子銑削 物理動能傳輸 非等向性蝕刻 表面破壞

活性離子蝕刻

兼具物理與化學 可控制蝕刻之非等向性 選擇性適中

化學反應, 速度快 等向性蝕刻 選擇性較高 表面較少破壞

高激發能量

電漿蝕刻

物理濺擊或離子銑削、電漿蝕刻、與 活性離子蝕刻之關係

C. R. Yang, NTNU MT

Plasma

etch stop

substrate mask

PR, metal, Si

3N

4, SiO

2, Si, Polysilicon…...

PR, metal, SiO

2, Si, Polysilicon…...

Mask材料選擇的原則:高選擇比, 蝕刻深度, 非等向性…

乾式蝕刻 乾式蝕刻

台灣師範大學機電科技學系 -61-

物理濺擊或離子銑削與濺鍍非常相似,偏向於物理性的碰撞與能量轉移,

首先將氣體解離或激發成電漿同時施予一陰極電壓,此時帶正電的離子會 因為電位差而加速往電極板表面衝撞,稱為離子轟擊,若將晶片置於電極 板就可以對薄膜進行離子轟擊,所以具有非等向性蝕刻的特性,但相對的 選擇性較差且容易造成薄膜表面的破壞。

電漿蝕刻比較依賴化學反應來進行蝕刻,所以偏向等向性蝕刻,選擇性較 高且對薄膜表面的破壞較少,其原理是將反應氣體解離成對薄膜具有反應 性的離子 (電漿) ,離子與薄膜進行化學反應 (蝕刻) 產生輝發性物質,再經 由真空系統抽出。

C. R. Yang, NTNU MT

活性離子蝕刻兼具物理與化學的特性,係適當的選擇與薄膜進行反應 (蝕 刻) 之氣體,通入反應室中並解離成電漿,並施與一偏壓,讓離子轟擊與 電漿蝕刻同時進行,所以具有某種程度的非等向性蝕刻,而且選擇性足 以讓人接受,所以應用比較廣,下圖是活性離子蝕刻系統的示意圖。

射頻電源

晶片 進氣

氣體

流量控制

真空幫浦

節流閥 +

活性離子蝕刻系統示意圖

台灣師範大學機電科技學系 -63-

幾種常用薄膜活性離子蝕刻之氣體與蝕刻率

幾種常用薄膜活性離子蝕刻之氣體與蝕刻率 (nm/min) 比較 (nm/min) 比較 ( (本表節錄自 本表節錄自 Journal Journal of Micro

of Micro- -Electro Electro- -Mechanical Systems Mechanical Systems, ,Vol.5 Vol.5 , , No.4 , No.4 ,第 第262 262頁 頁) )

註:單晶矽為 <100> 矽;多晶矽為 n+ ;二氧化矽為溼氧化;磷矽玻璃為經過退火處理;

鋁含 2% 的矽;鎢與鈦都是利用濺鍍沈積;光阻為 OCG 820 PR

蝕刻氣體 (sccm) 蝕刻 物質

單晶 矽

多晶 矽

二氧化 矽

磷矽 玻璃

氮化 矽

鋁 鎢 鈦 光阻

90CF4/30CHF3/120He 二氧 化矽

>10 190 470 620 180 * >10 >10 220

13SF6/21He 氮化矽 30 73 31 48 82 * >10 >10 69

45CF4/15CHF3/60He 富矽氮化 矽

>10 35 32 45 76 * >10 >10 40

180Cl2/400He 矽 >10 340 0.8 14 56 >10 >10 * 300

30Cl2/50BCl3/20CHCl

3/50N2

鋁 >10 450 68 74 93 600 >10 * 630

80SF6 鎢 >10 580 120 150 260 * 280 >10 240

51O2 光阻 * 0 0 0 0 0 0 * 340

C. R. Yang, NTNU MT

2 2 -6 - 6 熱製程與離子摻雜 熱製程與離子摻雜

z 熱製程:熱氧化層成長(thermal oxide layer)

把矽晶片曝露於高溫且含氧的環境中一段時間之後,即可在晶片表面長成(grow) 一層與矽的附著性良好,且電性符合絕緣體要求的SiO2,可作為MOS結構中的墊

氧化層(pad oxide)、場氧化層(field oxide),及犧牲氧化層(sacrificial oxide)。事實

上,矽晶片於室溫空氣中即可產生厚度約數Å到20 Å的SiO2層,稱為原始氧化層(native oxide)。

Si (s) +O 2(g) → SiO 2(s) 乾式氧化(dry oxidation)

Si (s) +2H 2 O (g) → SiO 2(s) +2H 2 (g) 溼式氧化(wet oxidation)

900℃以上

600℃以上 Δ

Δ

台灣師範大學機電科技學系 -65-

熱製程 熱製程

熱氧化處理需要在高溫爐管區中進行,爐內溫度控制在800 - 1000℃。矽晶圓在爐內高 溫環境下,晶圓表面會與通入爐管內之氧氣作用而形成二氧化矽膜(SiO2

)。

氧化矽成長 氧化矽成長

SiO

2Si

(a) 熱氧化成長SiO

2(b) 微影及BOE蝕刻SiO

2Si SiO

2PR

Si

(c) TMAH蝕刻液中以不同操作條件蝕刻 SiO

2氧化矽作為蝕刻遮罩 氧化矽作為蝕刻遮罩

C. R. Yang, NTNU MT

z 回火(annealing): 回火在半導體製程的應用,主要是著眼於恢復或改善半導 體材料的電子性能,或降低因製程所產生的內應力。主要的回火製程應用於:

(a)後離子植入(post ion implantation)的回火, (b)金屬矽化物(silicide)的回火, (c)薄 膜沈積或薄膜成長後的應力消除。

熱製程 熱製程 (續 ( 續 ) )

z 矽化反應(silicide reaction):Ti (s) + 2Si (s) →

ΔTiSi 2(s)

為何要作矽化反應? Si – Al – TiN - TiSi

2的關係說明

Al是半導體製程最常用的金屬,但Si與Al的介面並不安定

在Si與Al的介面增加一層TiN作為阻障層(barrier layer)(用來隔離Si與Al)

TiN造成MOS元件之歐姆式接觸能力降低,以導電性較好的TiSi2加於Si與TiN的介面

MOS元件的接觸金屬(contact metal)實際上是TiSi2 (下層) 、TiN (中層)、Al(上層) 三層結構

台灣師範大學機電科技學系 -67-

z 固化(curing): 加溫用來蒸除(evaporate)某些薄膜材料內的有機溶劑,以增 加薄膜的密度。

z 熱流動(flow): 將PSG(磷矽玻璃)與BPSG(硼磷矽玻璃)加熱至其玻璃轉換溫度 (glass transition temperature, Tg)以上(850~950℃, 20~40 min),使它們產生流動現 象,達到平坦化的目的。

熱製程 熱製程 (續 ( 續 ) )

半導體元件的積極度增加,需要多層金屬層,才能完成整個IC導線的連接。

多重金屬層的製作需要非常平坦的介電層(CMP發展的主因)。

SOG (Spin-on glass)是一種液態SiO

2,晶片旋塗SOG後可增加平坦性。為將SOG轉換成固態SiO2層,必須將晶片置於400~450℃的爐管,蒸除SOG內的溶劑

C. R. Yang, NTNU MT

基板 基板

薄膜 旋塗式玻璃

溝渠

(a) (b)

旋塗式玻璃 (spin-on glass; SOG) 是形成薄膜也是平坦化一種方式,如圖 將溶 於溶劑中的介電物質旋轉塗佈在需要平坦化的晶片上,使介電物質隨著溶劑 填入溝渠中,再經過高溫固化,形成近似二氧化矽的物質在晶片上,讓表面 輪廓比較平滑達到局部平坦化的目的,使後續的製程得以順利進行。

SOG SOG 的平坦化製程 的平坦化製程

台灣師範大學機電科技學系 -69-

離子摻雜(doping) 離子摻雜 (doping)

擴散法(diffusion) 擴散法 (diffusion)

擴散可分為兩個主要步驟,預置 (predeposition) 和趨入(drive-in),在預置時摻 雜物質經由氣體帶入爐管中,溫度通常大於 800 °C ,使定量的摻雜物質進入 晶片表面,趨入步驟則是藉由一定時間的高溫擴散,使摻雜物質重新擴散為所 需的濃度分佈曲線。

C. R. Yang, NTNU MT

氧化擴散高溫爐

氧化擴散高溫爐

台灣師範大學機電科技學系 -71-

離子植入 離子植入 (ion implantation) (ion implantation)

離子佈植是將經由高電壓加速的帶電原子或分子直接打入基材,最原始的目的是將欲摻雜 的離子打入晶片中,因為比擴散法更能將所需要的摻雜物質準確的打入且控制濃度分佈,

所以在積體電路中的應用很廣,例如製作 CMOS 電晶體中的源極 (source) 與汲極 (drain)

、 n 井與通道阻絕 (channel stop) 等。

z離子植入法可藉由控制離子束電流量與施加電壓,掌握摻雜的濃度與深度。

z離子植入法具良好的摻質縱向分佈控制,而熱擴散法離子層的分佈會產生橫向擴張現象。

而在微機電系統中最重要的應用就是在單晶矽上佈植入 p 型摻雜物質,利用氫氧化鉀對 p 型摻雜單晶矽的低蝕刻率來製作微機械結構,不過由於離子佈值機價格非常昂貴,而摻雜 大部分可以利用較便宜的擴散製程完成,所以若就價格、效益、及微機電系統的製程來考 量,離子佈值機的投資似乎值得商確。

C. R. Yang, NTNU MT

擴散摻雜

離子佈植是將所需的摻雜元素(如砷)電離成正離子,並施加高偏壓

,使其獲得一定的動能,以高速射入矽晶圓的技術。

離子植入 離子植入

Ion implantation

Ion implantation

台灣師範大學機電科技學系 -73-

離子植入系統的說明 離子植入系統的說明

先在反應室中加電壓使電子加速與氣體產碰撞而 產生電漿,亦即具有帶負電、正電或電中性的離 子與分子、原子團 (radicals) 等,接著藉由萃取電 極 (extraction electrode) 之高負電壓將帶正電離子 分離出,往解析磁場 (analyzing magnetic) 前進,

解析磁場會分離出真正需要的離子,以 BF3 所產 生的離子 BF2

+ 、 B++ 與 B+為例,在經過解析磁

場後只有一種離子被選擇出來進行佈植,然後進 入加速管 (acceleration tube) 中加速離子並聚焦(focusing) ,同時分離出電中性離子束 (neutral beam) ,最後帶電離子束進入掃瞄系統 (scanning system) 對晶片進行離子佈植,整個製程得在高真

空中進行,而且特別注意離子佈植製程不僅設備 複雜 昂貴, 而且充 滿毒氣 、高電壓、幅射與強 磁場。C. R. Yang, NTNU MT

Clean room

Sub fab

Basement Abatement equipment

Chemical blend &

dispense equipment Bulk gas

purifiers

Chillers Gas

bunkers

Bulk gas pad

Special gases Vacuum

pumps

無塵室 無塵室 (Clean room or FAB) (Clean room or FAB) 之構成 之構成

台灣師範大學機電科技學系 -75-

無塵實驗室與生產工廠 無塵實驗室與生產工廠

實現微/ 實現微 /奈米元件的場所 奈米元件的場所

C. R. Yang, NTNU MT

台灣師範大學機電科技學系 -77-

無塵室之構成 無塵室之構成 (續 ( 續 ) )

C. R. Yang, NTNU MT

2- 2 - 8 無塵室工作須知 8 無塵室工作須知( (自行研讀 自行研讀 ):重要! ) :重要!

台灣師範大學機電科技學系 -79-

C. R. Yang, NTNU MT

化學物處理注意事項

化學物處理注意事項

台灣師範大學機電科技學系 -81-

化學物處理注意事項

化學物處理注意事項 (續 ( 續 ) )

C. R. Yang, NTNU MT