大華科技大學

電機與電子工程系碩士班

碩士論文

爐管氮化矽均勻度改善之研究

Study on Improvement of

Uniformity of Silicon Nitride in

Furnace

研 究 生:張 治 文

指導教授:謝 振 中

爐管氮化矽均勻度改善之研究

Study on Improvement of Uniformity of Silicon Nitride

in Furnace

研 究 生:張治文

Student:Chih-Wen Chang

指導教授:謝振中

Advisor:Jenn-Jong Shieh

大華科技大學

電機與電子工程系碩士班

碩士論文

A ThesisSubmitted to Department of Electrical and Electronic Engineering College of Engineering and Design

Ta Hwa University of Science and Technology in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Electrical and Electronic Engineering July 2017

Hsinchu, Taiwan, Republic of China。

摘要

晶圓常常會因為人為處理的疏忽和機台異常或錯誤調整都會毀 損易碎的矽晶圓。常有錯誤的製程,導致有對準的錯誤造成微影步驟 出現問題,加上製程上伴隨而來的蝕刻或離子佈植、也會造成錯誤的 摻雜濃度、極差的均勻度,或在晶圓上的過量粒子等,也都會損毀矽 晶圓。當這些矽晶圓的毀損除會造成實用上的損失外,,並降低晶圓 良率。本研究利用改變爐管不同的設備條件,將實驗的設備調整水平 調整方向、歧管、水流量調整、抽風量調整來尋找出最佳的條件以改 善矽晶圓之均勻度以進一步提高晶圓良率。 關鍵字: 爐管、晶圓良率、矽晶圓、歧管、均勻度Abstract

Wafer is often caused by human handling of negligence and machine anomalies or error adjustments can damage fragile silicon wafers. Wrong process, resulting in a misplaced error that causes a problem with the lithography step, plus the process of etching or ion implantation, and also cause the wrong doping concentration, poor uniformity or excess particles on the wafer that will also damage the silicon wafer. When these silicon wafers will cause damage to the practical loss that is the general company does not want to see the problem. Therefore, the company will try every means to improve wafer yield.

This study uses different equipment conditions to change the furnace tube, adjust the direction of the equipment to adjust the direction of the equipment, manifold, water flow adjustment and ventilation adjustment to find the best conditions to improve the uniformity.

誌謝

本論文得以順利完成,最先要感謝指導教授謝振中博士。在謝振 中教授專業與耐心的教導下,除了學術研究上獲益良多,也學會了嚴 謹的做事態度。同時也感謝胡國英教授、謝飛虎教授在論文口試時, 所給予的寶貴意見與指導。 此外,感謝我的碩士班同學林振玉,在我的論文研究過程提供大 力的協助;其次要感謝我的女朋友林詠蓁,在我帶職進修期間,給予 最大的包容與支持。 最後要感謝我最愛的父母,在論文撰寫中給予的關心與支持,謹以 此論文獻給你們,謝謝你們。目錄

中文摘要···I 英文摘要···II 誌謝···III 目錄···IV 圖目錄···VI 表目錄···VIII 第一章 前言···1 1-1 研究背景與發展···1 1-2 研究動機與目的···1 1-3 論文架構···2 第二章 半導體製程介紹和均勻度介紹···3 2 - 1 前 言 · · · 3 2-2 製程介紹···6 2-2-1 熱氧化···6 2-2-2 薄膜··· 7 2-2-3 微影··· 13 2-2-4 蝕刻··· 14 2-2-5 擴散、離子植入···242-3 均勻度介紹···26 第三章 實驗機台介紹與分析···28 3-1 實驗機台介紹···28 3-2 實驗方法介紹···30 3-3 實驗設計之分析···31 第四章 實驗結果與討論···32 4-1 前言···32 4-2 實驗步驟···32 4-2-1 調整歧管(Manifold)···32 4-2-2 調整水流量(Up-Flange)···36 4-2-3 調整承載(Cap)水平···38 4-2-4 調整抽風壓力···41 4-3 實驗結果分析與討論···44 第五章 結論與未來研究方向···44 參考文獻···45

圖目錄

圖 2-1 晶圓之製造過程···3 圖 2-2 半導體產業結構上、中、下游完整製造流程···5 圖 2-3 氧化製程圖···6 圖 2-4 電子束蒸鍍示意圖···8 圖 2-5 濺鍍機原理圖···9 圖 2-6 化學氣相沉積原理···13 圖 2-7 微影示意圖···14 圖 2-8 底切顯示圖···17 圖 2-9 圖上初始晶圓;圖左乾蝕刻後的晶圓;圖右濕蝕刻後的晶圓 ···20 圖 2-1 不同蝕刻產生出來的蝕刻輪廓圖···23 圖 2-11 九點均勻度圖···27 圖 3-1 TEL Furnace(爐管)···29 圖 3-2 KE Furnace(爐管) ···29 圖 3-3 M/W 1~7 分析表···31 圖 4-1 M/W (a)歧管水平調整方向(b)歧管正視圖···32 圖 4-2 調整歧管示意圖···33 圖 4-3 (a) 調整歧管前 (b)調整歧管後···34圖 4-4 均勻度(M/W) 實驗改善後每週成效···35 圖 4-5 水帶走熱量示意圖···36 圖 4-6 均勻度(M/W) 實驗改善後每週成效···38 圖 4-7(a)水平儀(b)水平儀在承載上···38 圖 4-8 左圖為調整承載水平前;右圖為調整承載水平後···39 圖 4-9 均勻度 (M/W) 實驗改善後每週成效···40 圖 4-10 抽風口及進風口位置···41 圖 4-11 均勻度(M/W) 實驗改善後每週成效···43

表目錄

表 2-1 濕刻度參數及控制困難度表··· 16 表 2-2 擴散/離子植入比較···26 表 3-1 PU 控制晶圓片(M/W)改善前 Cp 值···30 表 4-1 調整歧管前後均勻度比較··· 34 表 4-2 PU 控制晶圓片(M/W)調整歧管後每週 Cp 值···35 表 4-3 調整水流量··· 36 表 4-4 PU-5A 調整水流量前後均勻度比較···37 表 4-5 PU 控制晶圓片(M/W)調整水流量後每週 Cp 值···37 表 4-6 調整 PU-3A 承載水平前後均勻度比較···40 表 4-7 控制晶圓片(M/W)調整承載水平後每週 Cp 值···40 表 4-8 調整抽風口壓力···42 表 4-9 PU-5A 抽風壓力調整前後均勻度比較···42 表 4-10 PU 控制晶圓片(M/W)調整抽風壓力後每週 Cp 值···42 表 4-11 實驗調整後整體的 Cp···43第一章 前言

1-1 研究背景與發展現況 電子技術的進步造就了現在目前資訊電腦產業的發展,更改變了現 在日常生活型態,甚至人類的思考模式、文化活動以及國家間之政治 與軍事的互動。電子技術中的主角就是半導體。這幾年來,隨著電子 科技、網路等相關技術的進步,以及全球電子市場消費水準的提昇, 個人電腦、多媒體、網路、手機相關設備等電子產品的需求量暴增, 帶動整個世界半導體產業的蓬勃發展,半導體業更成為維繫國家經濟 動脈的一個主力。基本上半導體製造為一垂直分工細密且高附加價值 的產業,其快速的成長也會帶動其他週邊產業的繁榮。 1-2 研究動機與目的 在現今半導體業中,隨者製程技術的日益進步,產品更趨近於輕薄 短小,消費者對產品品質的要求也越來越高;而製程的良率,是決定品 質高低與否的一項重要指標,所以提高品質的第一步,就是要提高製程 的良率著手。 晶圓良率(Wafer Yield)主要決定於晶圓的製程和處理。人為處理的 疏忽和設備突然異常或錯誤調整都會毀損易碎的矽晶圓。錯誤的製程, 諸如對準錯誤的微影步驟加上伴隨而來的蝕刻或離子佈植、錯誤的摻雜 濃度、極差的均勻度,或在晶圓上的過量粒子等,也都會損毀晶圓。 然而,文獻[1]提出了可改善半導體機械研磨平坦化方法,進而使 晶圓表面達到全面性的平坦化,文獻[2]提出了可改善半導體爐管製 程所遇到的微粒問題,都是為了要改善晶圓良率,提高均勻度,本論文以改善半導體爐管氮化矽均勻度主題,找出一個可改善晶圓均勻度之最 佳方法,提高產能,用 7 台機台的製程能力指標為依據,改善較差的均 勻度,提高晶圓良率。 1-3 研究架構 本論文共分成五章,第一章為前言,說明本研究之背景與發展現況、 研究動機與目的;第二章為半導體爐管均勻度對產品的重要性;第三章 為實驗設計與實現;第四章為實驗結果與討論;第五章為結論。

第二章 半導體製程介紹和均勻度介紹

2.1前言

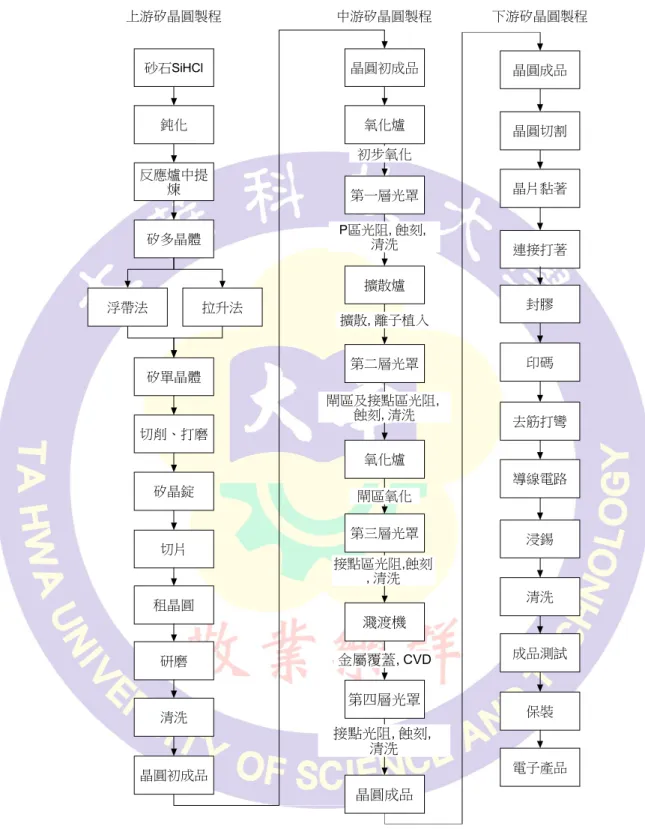

半導體工業的製程是在矽半導體上製造電子元件,包括微處理器、 動態記憶體、靜態記憶體…等,而電子元件是由精密且複雜的積體電路 所組成,積體電路(Integrated Circuit,簡稱 IC)。IC 的製造過程是將晶 片進行氧化層成長、物理氣相沉積(Physical Vapor Deposition)、化學氣 相沉積(Chemical Vapor Deposition)、微影(Lithography)及蝕刻(Etching) 等技術。每個製程都多達兩百至三百個步驟,程序相當多且複雜。隨著 電子資訊產品朝著輕薄短小化的方向發展,半導體製造的方法也向著高 密度及自動化生產的方向前進。而 IC 製造技術的發展趨勢,大多仍朝 著克服晶圓直徑變大,元件線幅縮小,製造步驟增加,製程步驟特殊化 以提供更好的產品特性等課題,將以上所造成的良率控制困難方向加以 改良。圖 2-1 為晶圓製造過程。 圖 2-1 晶圓之製造過程 半導體工業所使用之材料包含單一組成的半導體元素,如矽(Si)、鍺

(Ge)(屬化學週期表上第四族元素)及多成分組成的半導體含二至三種元 素,如鎵砷(GaAs)半導體是由第三族的鎵與第五族的砷所組成。在 1950 年代早期,鍺為主要半導體材料,但鍺製品在不甚高溫情況下,有高漏 失電流現象。因此,1960 年代起矽晶製品取代鍺成為半導體製造主要材 料。半導體產業結構可區分為材料加工製造、晶圓之積體電路製造(Wafer Fabrication)(中游)及晶圓切割、構裝(Wafer Package)等三大類完整製造 流程,如圖 2-2 所示。 其中材料加工製造是指從矽晶石原料提煉矽多晶體(Polycrystallines Silicon)直到晶圓(Wafer)產出,此為半導體之上游工業。此類矽晶片再經 過研磨加工及多次磊晶爐(Epitaxial Reactor)則可製成研磨晶圓成長成為 磊晶晶圓,其用途更為特殊,且附加價值極高。其次晶圓之體積電路製 造,則由上述各種規格晶圓,經由電路設計、光罩設計、蝕刻、擴散等 製程,生產各種用途之晶圓,此為中游工業。而晶圓切割、構裝業係將 製造完成的晶圓,切割成片狀的晶粒(Grain),再經焊接、電鍍、包裝及 測試後即為半導體成品。

圖 2-2 半導體產業結構上、中、下游完整製造流程 砂石SiHCl 鈍化 反應爐中提 煉 矽多晶體 浮帶法 拉升法 矽單晶體 切削、打磨 矽晶錠 切片 租晶圓 研磨 清洗 晶圓初成品 晶圓初成品 氧化爐 第一層光罩 擴散爐 第二層光罩 氧化爐 第三層光罩 濺渡機 第四層光罩 晶圓成品 晶圓成品 晶圓切割 晶片黏著 連接打著 封膠 印碼 去筋打彎 導線電路 浸錫 清洗 成品測試 保裝 電子產品 上游矽晶圓製程 中游矽晶圓製程 下游矽晶圓製程 初步氧化 P區光阻, 蝕刻, 清洗 擴散, 離子植入 閘區及接點區光阻, 蝕刻, 清洗 閘區氧化 接點區光阻,蝕刻 ,清洗 金屬覆蓋, CVD 接點光阻, 蝕刻, 清洗

2.2 製程介紹 以下本文將依序介紹熱氧化、薄膜、微影、蝕刻、擴散、離子植入之製 程。 2.2.1 熱氧化 當矽放在高溫氧化的環境中,表面是自然形成,產生矽本身的氧化 膜。但熱氧化對於污染的控制,必須嚴格要求,因為經常使用H -O 燃 燒法產生高純度的水蒸氣,並控制水蒸氣的濃度,來產生閘極氧化膜, 因此,此製程很容易造成環境汙染。值得一提的是閘極氧化膜的厚度非 常的薄,為了達到控制得宜,就必須好好調整氧化劑的供應量。 目前熱氧化處理的工具是高溫爐管,爐內溫度控制在 800-1000℃。矽晶 圓在爐內高溫環境下,晶圓表面會與通入爐管中之氧氣作用而形成二氧 化矽膜(SiO ),如圖 2-3 所示。 圖 2-3 氧化製程圖 氧化(場氧化層) 光阻旋塗 對準與曝光光罩-晶圓 曝光之光阻 光阻顯影 Oxide Etch 光阻線條 氧化 (閘極氧化層) 多晶矽沉積 多晶矽 光罩與蝕刻 離子植入 主動區域 氦化矽沉積 接觸窗蝕刻 金屬沉積及蝕刻

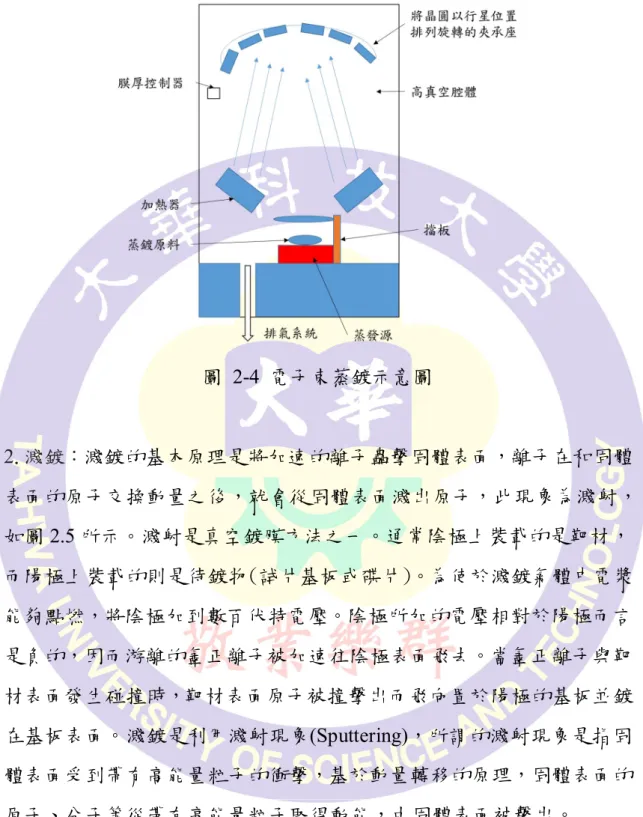

2.2.2 薄膜 薄膜沉積技術分為兩個方向:物理氣相沉積(PVD);化學氣相沈積(CVD) (一)物理氣相沉積 物理氣相沉積法是以物理機制來進行薄膜沉積製程技術,所謂的物 理機制就是物質的相變化,對欲沉積薄膜的材料原施加熱能或動能,始 知分解為單原子或原子聚合體,並結合或凝聚在矽晶圓表面,形成薄膜。 如蒸鍍(Evaporation)、濺鍍(Sputtering)。而這種過程無涉及化學反應, 因此所沉積的材料純度佳且品質穩定。 物理氣相沉積法主要的 PVD 技術如下: 1.蒸鍍:蒸鍍原理是在高真空腔體中,放入所要蒸鍍的材料,利用電熱 絲或電子束加熱升溫達到熔化、氣化溫度,使材料蒸發,到達並附著在 基板(晶圓)表面上的一種鍍膜技術。過程中,被鍍物的表面溫度對蒸鍍 所形成薄膜的特性有很重要的影響。基板需要適當的加熱,使得蒸鍍原 子可以在基板表面自由移動,如此才能形成均勻的薄膜。基板加熱至 150 ℃以上時,可使沉積膜與基板間形成良好的連結而不致剝落。如圖 2-4 所示。

圖 2-4 電子束蒸鍍示意圖 2.濺鍍:濺鍍的基本原理是將加速的離子轟擊固體表面,離子在和固體 表面的原子交換動量之後,就會從固體表面濺出原子,此現象為濺射, 如圖 2.5 所示。濺射是真空鍍膜方法之一。通常陰極上裝載的是靶材, 而陽極上裝載的則是待鍍物(試片基板或碟片)。為使於濺鍍氣體中電漿 能夠點燃,將陰極加到數百伏特電壓。陰極所加的電壓相對於陽極而言 是負的,因而游離的氬正離子被加速往陰極表面飛去。當氬正離子與靶 材表面發生碰撞時,靶材表面原子被撞擊出而飛向置於陽極的基板並鍍 在基板表面。濺鍍是利用濺射現象(Sputtering),所謂的濺射現象是指固 體表面受到帶有高能量粒子的衝擊,基於動量轉移的原理,固體表面的 原子、分子等從帶有高能量粒子取得動能,由固體表面被擊出。 濺鍍在高真空的環境下,反應室通入適當的氣體(大多使用氬氣 Ar), 並控制在適當的壓力下,反應室內的自由電子去撞擊 Ar 分子,造成 Ar

的解離,產生二次電子與 Ar 離子,Ar 離子受到靶材上負電位的影響, 加速去撞擊靶材,將靶材上的金屬給撞擊下來,並沉積在晶片表面上。 濺鍍的優點有薄膜沉積速率佳、精准成分控制佳、整體製造成本低、 純度高、低溫可形成薄膜,以及在製備合金和化合物薄膜的過程中可保 持原組成不變。相對的,階梯覆蓋率(Step Coverage)比較差(相較於 CVD)。 濺鍍本身受到濺射原子多方向與多角度散射的影響下,不易在非水平表 面下,得到連續且均勻覆蓋(Conformal)的薄膜。當製程線寬極小化的時 後,用傳統 PVD 鍍膜的方式就有其缺陷存在。且由於受到濺射原子多 元散射方向的影響,不易得到在接觸洞連續且均勻覆蓋的金屬膜,以至 於影響填洞或栓塞的能力。因此現在濺鍍技術的重點,莫不著重於改進 填洞時之階梯覆蓋率,以增加反擴散層等之厚度,以改善元件之電磁特 性,並簡化製造流程降低成本等。 圖 2-5 濺鍍機原理圖

(二)化學氣相沉積

張育唐(2012)定義化學氣相沉積法(Chemical Vapor Deposition, CVD), 是一種化學上常用的合成過程,其目標是生產高效能且高純度的一些化 學材料[7]。例如像是人工鑽石的合成,以及半導體業上的薄膜合成, 都是透過化學氣相沉積法來達到。而化學氣相沉積法製造鑽石的發現, 有效地提升了鑽石的產量與應用性。 李元堯(2012)指出化學氣相沉積是指利用熱能、電將放電或紫外線光 照射等形式的能源,使得氣態物質將晶圓(基底)暴露在一種或多種不 同的前趨物下,所發生之化學反應,並在該表面上產生沉積,形成穩定 固態膜的過程[10]。化學氣相沉積技術是使用半導體積體電路製程中 運作及廣泛的薄膜成長方法,如介電質、半導體、導體等薄膜材料,幾 乎都能用化學氣相沉積技術完成。 而典型的化學氣相沉積法,是將我們所使用的基底(Substrate),暴露 於欲合成之材料的前驅物蒸氣當中,常見的基底如矽、金屬或金屬化合 物;當前驅物蒸氣接觸到基底,便可能會發生不同的變化,譬如沉積、 分解等反應產生欲合成附著在基底上,當這些分子持續累積,便會得到 我們所想要的材料。例如像是在半導體產業上,我們將晶圓作為基底, 暴露在不同的蒸氣下,可以得到矽、二氧化矽、氮化矽(Si N ),甚至是 一些金屬的薄膜沉積。如圖 2.6 所示 化學氣相沉積法有相當多不同的種類,均在各領域被廣泛應用。我 們可以透過不同的指標來進行分類:利用氣壓的大小來分類,可以得到 常壓化學氣相沉積 (Atmosphere Pressure CVD, APCVD)、低壓化學氣相 沉 積 (Low Pressure CVD, LPCVD) 、 電 漿 增 強 式 化 學 氣 相 沈 積 法

等。在化學氣相沉積當中減低壓力,最主要的目的在將其他不相干的氣 體去除,以避免產生不必要的反應而得到雜質。畢竟化學氣相沉積其中 一個目的,就是要得到高純度的樣品。而傳統的化學氣相沉積法,必須 要在樣品能夠成為氣相,即樣品在該狀態下是氣態,或者具有一定的蒸 氣壓;然而許多高沸點的分子或是大分子,其蒸氣壓是相當 低,甚至 還有可能是固態。因此就產生了氣溶膠輔助氣相沉積(Aerosol Assisted CVD, AACVD)以及直接液體注入化學氣相沉積(Direct Liquid Injection CVD, DLICVD)。氣溶膠輔助氣相沉積是將樣品用超音波做成氣溶膠狀 的前驅物,使得液體狀的樣品也能夠沉降在基底當中;而直接液體注入 化學氣相沉積,則是將 液態樣品或固態樣品溶於溶劑之溶液利用注射 器噴出,再進行傳統氣相沉積反應。除此之外,例如透過電漿等不同的 產生氣態前驅物方法,也經常被拿來用在氣相沉積上。化學氣相沉積的 優點有大面積鍍膜的應用且有相當不錯的均整度、基板上不會有組成物 的顆粒沉積在表面上及對於活化能較高的區域有更高的選擇性。而此技 術的限制有部分反應氣體與前驅物可能有安全性問題,且易造成環境汙 染,還有部分高純度化合物的成本非常昂貴。 化學氣相沈積依照工作壓力及能源形式區分為: 1.常壓化學氣相沈積法(APCVD):顧名思義,就是在氣壓接近常壓下進 行 CVD 反應的一種沈積方式,此法的沈積速度極快,約為 600-1000 奈 米/分。APCVD 的操作壓力接近一大氣壓,氣壓分子間的碰撞頻率很高, 同質成核的 "氣相反應"容易發生,易產生微粒。在工業界的應用上, APCVD 的使用大都集中在對微粒的忍受能力較大的製程上,如保護層 (Passivation)。 2.低壓化學氣相沈積法(LPCVD):就是在進行薄膜沈積時,反應器內的氣

體壓力調降到大約 100torr 以下的一種化學氣相沈積反應。因為在低壓 下進行反應,LPCVD 法沈積的薄膜有較佳的步階覆蓋能力,但是氣體 分子間的碰撞頻率較低,使得 LPCVD 的薄膜沈積速度較 APCVD 慢。 3.電漿增強式化學氣相沈積法(PECVD):環繞爐管外圍的是一組用來對 爐管進行加熱的裝置,氣體從爐管前端送入爐管內,晶圓則置於石英晶 舟(Boat)上,放入爐管的適當位置,進行沈積。沈積反應所剩下來的 廢氣,則經由真空系統排出。一般而言,每次進行沈積的晶圓數量,可 以多達 120 片以上。LPCVD 爐管可分為水平式與直立式兩種。直立式 爐管的溫度控制與氣體的輸入設計比較複雜,但是使用樓板面小,因此 在應用上,已有取代水平式爐管的趨勢。 在 CVD 的反應中,氣體分子的分解須要足夠的激發能量。在電漿增強 化學氣相沈積法中,反應氣體在電磁場中獲得能量,各種化學反應在電 漿體中迅速地進行,從而在短時間內完成化學氣相沈積。PECVD 中的 電漿體屬於非平衡態。在此類的電漿體中,自由電子的絕對溫度通常比 平均氣體溫度高 1 到 2 個級次,這些高能電子撞擊反應物氣體分子,使 之激發並電離,產生化學性質很活潑的自由基團。另外離子撞擊底材表 面,產生更為活潑的表面結構,從而加快了化學反應。為了降低反應所 需的溫度,以達到調降製程熱能消耗的目的,PECVD 在 CVD 製程裡所 佔的份量,已逐漸成為主要的薄膜沈積工具之一,特別是用於 IC 晶圓 後段製程中的金屬與介電質膜的沈積。遠距電漿增強化學氣相沉積 4. 遠距離電漿增強化化學氣相沉積(RPECVD):遠距電漿增強化學氣 相沉積和 PECVD 技術很相近的技術。但晶圓不直接放在電漿放電的區 域,反而放在距離電漿遠一點的地方,晶圓遠離電漿區域可以讓製程溫

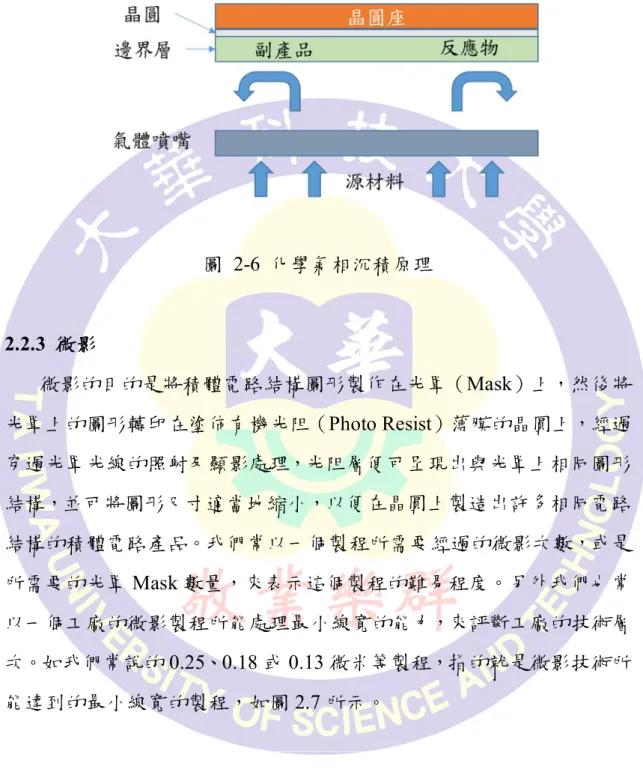

圖 2-6 化學氣相沉積原理 2.2.3 微影

微影的目的是將積體電路結構圖形製作在光罩(Mask)上,然後將 光罩上的圖形轉印在塗佈有機光阻(Photo Resist)薄膜的晶圓上,經過 穿過光罩光線的照射及顯影處理,光阻層便可呈現出與光罩上相同圖形 結構,並可將圖形尺寸適當地縮小,以便在晶圓上製造出許多相同電路 結構的積體電路產品。我們常以一個製程所需要經過的微影次數,或是 所需要的光罩 Mask 數量,來表示這個製程的難易程度。另外我們也常 以一個工廠的微影製程所能處理最小線寬的能力,來評斷工廠的技術層 次。如我們常說的 0.25、0.18 或 0.13 微米等製程,指的就是微影技術所 能達到的最小線寬的製程,如圖 2.7 所示。

圖 2-7 微影示意圖 2.2.4 蝕刻 蝕刻製程的功能,是要將進行微影製程前所沉積的薄膜,厚度約在 數千到數百 Å 之間,把沒有被光阻覆蓋及保護的部分,以化學反應或是 物理作用的方式加以去除,已完成轉移光罩圖案到薄膜上面的目的[ 12]。 蝕刻製程乃是將經過微影製程在表面定義出 IC 電路圖案的晶圓,以 化學腐蝕反應的方式,或物理撞擊的方式,或上述兩種方式的合成效果, 去除部份材質,留下 IC 電路結構。 蝕刻技術可分兩種,「濕蝕刻 (Wet Etching)」及「乾蝕刻(Dryetching)」, 濕蝕刻是使用化學溶液技術,使材料經由化學反應以達到蝕刻的目的, 而乾蝕刻則是以電漿蝕刻(Plasma Etching),電漿蝕刻中會使電漿中的離

子撞擊晶圓中晶片之表面,使晶片表面產生物理作用。也有以電漿中活 性自由基(Radical)與晶片表面原子間的化學反應。 一般蝕刻結構的形狀可分為均向性(Isotropic)與異向性(Anisotropic) 兩種,其蝕刻形成的形狀如圖所示。均向性蝕刻表示橫向和縱向之蝕刻 率相同,異向性蝕刻的橫向性蝕刻率則為 0。一般的蝕刻形狀介於此兩 種蝕刻類型之間。 蝕刻製程說明: 2.2.4.1 濕蝕刻 濕式蝕刻法利用化學溶液腐蝕晶圓上擬去除的材料,並在完成蝕刻 反應後,由溶液帶走腐蝕物。這種完全利用化學反應的方法來進行蝕刻 的技術有其先天上的缺點,也就是其蝕刻結構的形狀是各方向均勻的, 這樣會造成嚴重的側向腐蝕現象,顯著地限制了元件尺寸向微細化的發 展。 濕蝕刻是使晶片沉浸在適當的化學溶液中,或將化學溶液噴灑至晶 片上,經由容易與被蝕刻物的化學反應,來進行移除薄膜表面的原子, 以達到蝕刻的目的。 而當濕蝕刻進行時,溶液中的反應誤會先經由擴散作用,通過停滯 的邊界層(Boundary Layer),才能到達晶片表面,並與表面發生化學反應 及產生生成物。就濕蝕刻作用而言,對一種特定被時刻材料,通常可找 到相對的「蝕刻劑(Etchant)」,蝕刻劑的用處在於只會侵蝕你要消除的元 素,而對其他的材料並不會影響。因此濕蝕刻對不同材料有著相當高的 「選擇性 (Selectivity)」。然而除了結晶方向可能影響蝕刻速率外,由於 化學反應是不會對特定方向有任何偏好,因此,濕蝕刻是一種「等向性 蝕刻 (Isotropic Etching)」。

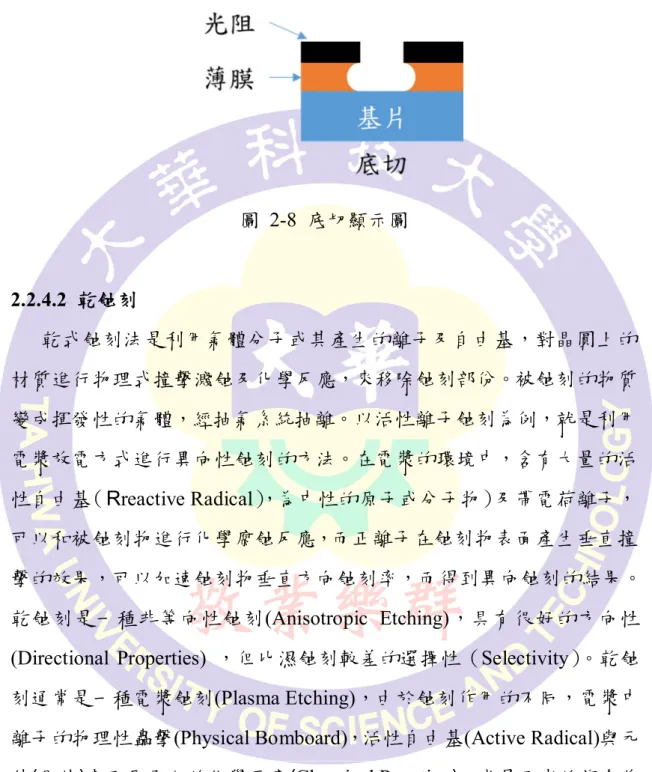

對等向性蝕刻來說,就像投下炸彈一般,炸出一個凹洞,而這個凹 洞是沒辦法去控制的,就會導致所謂的「底切 (Undercut)」現象,如圖 2-8 所示,使得圖形無法精確轉移至晶片。 表 2-1 說明濕刻度裡所使用的各種參數,加以解說,並顯示出控制之困 難點。 表 2-1 濕刻度參數 參數 解說 控制之困難度 濃度 溶液之濃度(如:用於蝕 刻氧化物之NH F:HF 的比例) 因為化學浴濃度持續在改變 故大部分參數均難以控制 時間 晶圓浸沒在濕式化學溶 液的時間 相當容易控制 溫度 化學溶液的溫度 相當容易控制 老化 溶液的老化 適切的控制具適中的困難 作業次數 經過一定作業次數後, 溶液必須予以更換,以 減少微粒及確保溶液強 度 相當容易控制

圖 2-8 底切顯示圖 2.2.4.2 乾蝕刻 乾式蝕刻法是利用氣體分子或其產生的離子及自由基,對晶圓上的 材質進行物理式撞擊濺蝕及化學反應,來移除蝕刻部份。被蝕刻的物質 變成揮發性的氣體,經抽氣系統抽離。以活性離子蝕刻為例,就是利用 電漿放電方式進行異向性蝕刻的方法。在電漿的環境中,含有大量的活 性自由基(Rreactive Radical),為中性的原子或分子物)及帶電荷離子, 可以和被蝕刻物進行化學腐蝕反應,而正離子在蝕刻物表面產生垂直撞 擊的效果,可以加速蝕刻物垂直方向蝕刻率,而得到異向蝕刻的結果。 乾蝕刻是一種非等向性蝕刻(Anisotropic Etching),具有很好的方向性

(Directional Properties) ,但比濕蝕刻較差的選擇性(Selectivity)。乾蝕

刻通常是一種電漿蝕刻(Plasma Etching),由於蝕刻作用的不同,電漿中 離子的物理性轟擊(Physical Bomboard),活性自由基(Active Radical)與元 件(晶片)表面原子內的化學反應(Chemical Reaction),或是兩者的複合作 用,可分為三大類:物理性蝕刻:濺擊蝕刻(Sputter Etching),離子束蝕 刻(Ion Beam Etching)。濺擊蝕刻(Sputter Etching)將惰性的氣體分子如氬

氣施以電壓,利用衍生的二次電子將氣體分子解離或激發成各種不同的 粒子,包括分子、原子團(Radical),電子、正離子等,;正離子被電極 板間的電場加速,即濺擊被蝕刻物,具有非常好的方向性(垂直方向), 較差的選擇性,因光阻亦被蝕刻,被擊出之物質為非揮發性,又沈積在 表面,困此在 VLSI 中很少被使用。化學性蝕刻:電漿蝕刻(Plasma Etching)利用電漿將蝕刻氣體解離產生帶電離子、分子、電子以及反應 性很強(即高活性)的原子團(中性基 Radical),此原子團與薄膜表面反 應形成揮發性產物,被真空幫浦抽走。電漿蝕刻類似濕蝕刻,利用化學 反應,具有等向性和覆蓋層下薄膜的底切(Under Cut)現象,由於電漿離 子和晶片表面的有效接觸面積比濕蝕刻溶液分子還大,因此蝕刻效率較 佳。電漿離子的濃度和能量是決定蝕刻速率的兩大要素,為了增加離子 的濃度,在乾式蝕刻系統設計了兩種輔助設備:(1)電子迴轉加速器 (Electron Cyclotron),(2)磁圈(Magnet Coil)。前者是利用 2.54GHz 的微 波來增加電子與氣體分子的碰撞機率;而後者則是在真空腔旁加入一個 與二次電子運動方向垂直的磁場,使得電子以螺旋狀的行徑來增加與氣 體分子的碰撞機率。

物理、化學複合蝕刻:反應性離子蝕刻(Reactive Ion Etching 簡稱 RIE) 最為各種反應器廣泛使用的方法,便是結合物理性的離子轟擊與化學反 應的蝕刻。此種方式兼具非等向性與高蝕刻選擇比等雙重優點,蝕刻的 進行主要靠化學反應來達成,以獲得高選擇比。加入離子轟擊的作用有 二:一是將被蝕刻材質表面的原子鍵結破壞,以加速反應速率。二是將 再沈積於被蝕刻表面的產物或聚合物(Polymer)打掉,以使被蝕刻表面能 再與蝕刻氣體接觸。而非等向性蝕刻的達成,則是靠再沈積的產物或聚

續進行,而在側壁上的沈積物,因未受離子轟擊而保留下來,阻隔了蝕 刻表面與反應氣體的接觸,使得側壁不受蝕刻,而獲得非等向性蝕刻。 應用乾式蝕刻主要須注意蝕刻速率,均勻度、選擇比、及蝕刻輪廓 等。蝕刻速率越快,則設備產能越快,有助於降低成本及提升競爭力。 蝕刻速率通常可藉由氣體種類、流量、電漿源及偏壓功率所控制,在其 他因素尚可接受的條件下,越快越好。均勻度是晶片上不同位置的蝕刻 率差異的一個指標,較佳的均勻度意謂著晶圓將有較佳的良率(Yield), 尤其當晶圓從 3 吋、4 吋發展到 12 吋,面積越大,均勻度的控制就 顯的更加重要。選擇比是蝕刻材料的蝕刻速率對遮罩或底層蝕刻速率的 比值,控制選擇比通常與氣體種類與比例、電漿或偏壓功率、甚至反應 溫度均有關係。至於蝕刻輪廓一般而言愈接近九十度越佳,除了少數特 例,如接觸窗或介層洞(Contact Window and Via Hole),為了讓後續金屬

濺鍍能有較佳的階梯覆蓋能力(Stepcoverage),而故意使其蝕刻輪廓小於

九十度。通常控制蝕刻輪廓可從氣體種類、比例、及偏壓功率來進行。 乾蝕刻通常以電漿來進行蝕刻,由於蝕刻作用不同,電漿中離子的 物理性轟擊(Physical Bomboard)、活性自由基(Active Radical )與元件表 面原子的化學反應或兩者的複合作用。其他的乾式蝕刻技術有:電子迴旋 共振(Electron Cyclotron Resonance,ECR)、磁場增強是反映、子蝕刻 (Magnetically Enhanced Reactive on Etch, MERIE)、感應耦合式電漿 (Transformer Coupled Plasma , TCP),磁場增強式反映離子蝕刻系統具有 高電將密度、低操作壓力、低離子能量可控制等優點,對於蝕刻製程中 能夠提供一般傳統蝕刻系統更高蝕刻速率與非等向性,來達成蝕刻後的 品質要求。

「非等向性蝕刻」,具有良好的方向性,但選擇性就比濕蝕刻來的差, 是因為乾蝕刻的蝕刻機制基本上為一種物理交互作用。因此,離子的撞 擊不但使被蝕刻的薄膜移除,也同時會移除光阻罩幕,沒有對單一材料 的「蝕刻劑」。 下圖左邊為非等向性之晶圓結果,也是乾蝕刻後的結果。而右邊的 不規則薄膜是等向性之晶圓結果,也是濕蝕刻所產生的結果,如圖 2-9 所示。 圖 2-9 圖上為初始晶圓;圖左下為乾蝕刻後的晶圓;圖右下為濕蝕刻 後的晶圓 2.2.4.3 蝕刻速率(Etching Rate) 蝕刻速率(d)是測量在蝕刻製程中薄膜被移除的速率有多快的一種 參數。

Etching Rate = ∆ (Å/ ) (2-1) ∆d = − (2-2) 為蝕刻前厚度 為蝕刻後厚度 (Å)為厚度改變量 t 為蝕刻時間 (min) 蝕刻時間相當重要的是在整個晶圓上會有一個均勻的蝕刻速率,會 有極高的重複性或好的晶圓對晶圓均勻性,一般定義成在蝕刻製成前後 之特定點厚度,並計算這些點蝕刻速率。 Uniformity = × × 100 (2-3) Emax:量測九個點中蝕刻速率最快之點 。 ERmin:量測九個點中蝕刻速率最慢之點 。 ERmean:九個點蝕刻率平均值。

蝕刻非均勻性 (Non-Uniformity, NU) 可由下列方程式計算 (稱 Max– Min 均勻性)

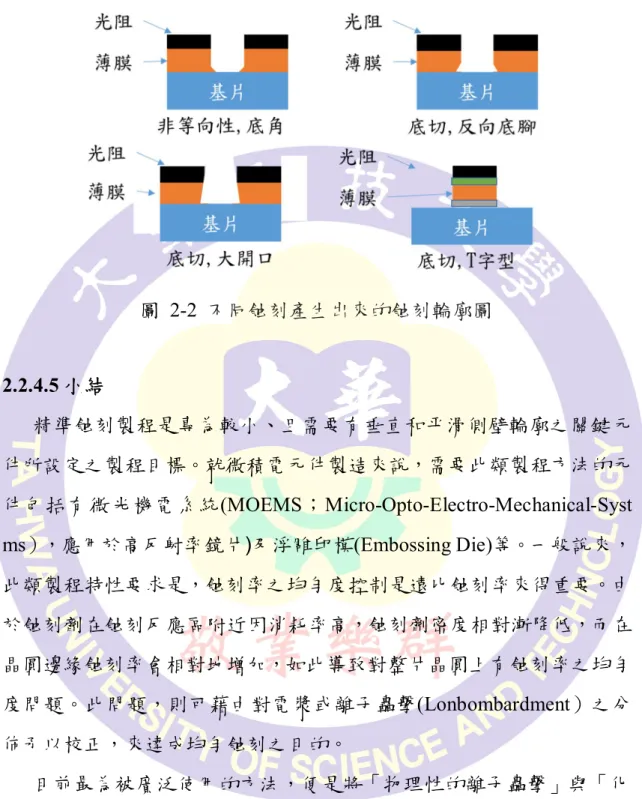

NU(%) = ( − )/(2 ) × 100% (2-4) 其中: Emax = 量測最大蝕刻速率 Emin = 量測最小蝕刻速率 Eave = 平均蝕刻速率 2.2.4.4 蝕刻輪廓 以下為不同蝕刻所產生出來的蝕刻輪廓,可以看到效果都是在改變 薄膜的形狀,而不同的形狀可製作出不同的 IC 晶片,前面兩個非等向 性及等向性,在前面有提過乾蝕刻會形成非等向性的輪廓,而濕蝕刻則 是形成等向性輪廓。而下面幾種不同的蝕刻輪廓,則是由電漿蝕刻或是 其他較特別的蝕刻才能形成。因此要控制蝕刻的方式才能做出使用者所 需要的蝕刻輪廓,如圖 2-10 所示。

圖 2-2 不同蝕刻產生出來的蝕刻輪廓圖 2.2.4.5 小結 精準蝕刻製程是專為較小、且需要有垂直和平滑側壁輪廓之關鍵元 件所設定之製程目標。就微積電元件製造來說,需要此類製程方法的元 件包括有微光機電系統(MOEMS;Micro-Opto-Electro-Mechanical-Syst ms),應用於高反射率鏡片)及浮雕印模(Embossing Die)等。一般說來, 此類製程特性要求是,蝕刻率之均勻度控制是遠比蝕刻率來得重要。由 於蝕刻劑在蝕刻反應區附近因消耗率高,蝕刻劑密度相對漸降低,而在 晶圓邊緣蝕刻率會相對地增加,如此導致對整片晶圓上有蝕刻率之均勻 度問題。此問題,則可藉由對電漿或離子轟擊(Lonbombardment)之分 佈予以校正,來達成均勻蝕刻之目的。 目前最為被廣泛使用的方法,便是將「物理性的離子轟擊」與「化 學反應」兩者結合的蝕刻。此種方法兼具非等向性的高蝕刻選擇比等雙 重優點。蝕刻的進行主要靠化學反應來達成,以獲得高選擇比。加入離 子轟擊後產生了兩種作用。一為將被蝕刻材質表面的原子鍵結破壞,以

加速反應速率。二是將在沉積於被蝕刻表面的產物或聚合物打掉,以使 被蝕刻表面能再與蝕刻氣體接觸。而非等向性時刻的達成,則是靠在沉 積的產物或聚合物,沉積在蝕刻圖形上,在表面的沉積物可為離子打掉, 故蝕刻可繼續進行。而在側壁上的沉積物,因為受離子轟擊而保留下來, 阻隔了蝕刻表面與反應氣體的接觸,使得側壁不受蝕刻,而獲得非等向 性蝕刻。 在應用任何蝕刻製程時,主要需注意蝕刻速率、均勻度、選擇比及 蝕刻輪廓等。蝕刻速率越快,則設備產能越快,有助於降低成本及提升 競爭力。蝕刻速率通常可藉由氣體種類、流量、電將源及偏壓功率所控 制,甚至反應溫度均有關係。在其他因素上可接受的條件下,越快越好。 至於蝕刻輪廓一般而言愈接近九十度越佳,除了少數特例,如接觸

窗或介層洞(Contact Window and Via Hole),為了使後續金屬濺鍍能有較 佳的階梯覆蓋能力(Step Coverage),而故意使其蝕刻輪廓小於九十度。 通常控制蝕刻輪廓可從氣體種類、比例、及偏壓功率來進行。 選擇比是蝕刻材料的蝕刻速率對遮罩或底層速率的比值,控制選擇比通 常與氣體種類與比例、電漿或偏壓功率、甚至反應溫度有關係。 2.2.5 擴散、離子植入 本區的製造過程都在高溫中進行,又稱為「高溫區」,利用高溫給 予物質能量而產生運動,因為本區的機台大都為一根根的爐管,所以也 有人稱為「爐管區」,每一根爐管都有不同的作用。 黃政平(2003)提到擴散與離子植入是用來控制半導體中雜質數量的 關鍵程序[14]。擴散製程中,是將不純物(Dopant)經由蝕刻過程產生

體,不純物主要有磷、砷及硼這三種,其來源包含固體(Bn、As O 及 P O )、液體(BBr 、AsCl 及 PoCl )及氣體(B H 、AsH 及 PH )來源。 擴散的製程步驟如下: 1. 預積(Predeposition) 首 先 在 攝氏 1050 度 時在 晶 圓 表 面 上 沉 積 出 一 層摻 雜 物 氧 化 層 (Dopant Oxide),如B O 或P O 。接著再以熱氧化製程來消耗掉殘餘的 摻物氣體,並且在矽晶圓上成長一層二氧化矽層來覆蓋摻物,以避免摻 雜物的向外擴散(Out-Diffusion)。 2. 驅入(Drive-In) 接著在氧氣環境下將高溫爐的溫度升至攝氏 1200 度,以提供足夠的 熱能讓摻雜物能快速地擴散到矽基片內。驅入時間則由所需的接面深度 來決定。 3. 摻雜的量測 監 測 摻 雜 過 程 時 最 常 用 到 的 量 測 工 具 就 是 四 點 探 針 (Four-Point Probe)。由於矽的電阻係數和摻物的濃度有關,因此測量矽表面的薄片 電阻就能夠提供摻雜物濃度的有用資料。相對於擴散方式,近來離子植 入的方式也逐漸被使用,離子植入是將離子化的不純物帶電粒子,以高 能量射入矽晶片中,但在離子植入過程中,那些高能量的摻物離子會對 靠近晶圓表面的矽晶體結構造成廣泛的破壞。為了符合元的規定就必須 利用退火(Annealing)將晶格的損傷修復,以使其恢復單晶結構並活化摻 雜物。離子植入的優點在於可精確的控制雜質的分佈與結構輪廓以及能 調整控制雜質的濃度,所以離子植入方法已經成為主流。兩種製程的比 較,如表 2-2 所示。

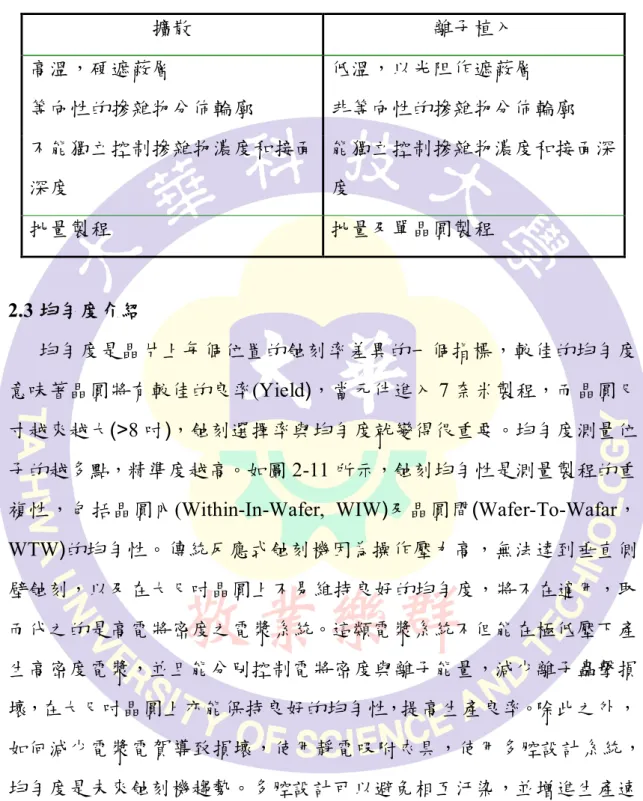

表 2-2 擴散/離子植入比較 擴散 離子植入 高溫,硬遮蔽層 低溫,以光阻作遮蔽層 等向性的摻雜物分佈輪廓 非等向性的摻雜物分佈輪廓 不能獨立控制摻雜物濃度和接面 深度 能獨立控制摻雜物濃度和接面深 度 批量製程 批量及單晶圓製程 2.3 均勻度介紹 均勻度是晶片上每個位置的蝕刻率差異的一個指標,較佳的均勻度 意味著晶圓將有較佳的良率(Yield),當元件進入 7 奈米製程,而晶圓尺 寸越來越大(>8 吋),蝕刻選擇率與均勻度就變得很重要。均勻度測量位 子的越多點,精準度越高。如圖 2-11 所示,蝕刻均勻性是測量製程的重 複性,包括晶圓內(Within-In-Wafer, WIW)及晶圓間(Wafer-To-Wafar, WTW)的均勻性。傳統反應式蝕刻機因為操作壓力高,無法達到垂直側 壁蝕刻,以及在大尺吋晶圓上不易維持良好的均勻度,將不在適用,取 而代之的是高電將密度之電漿系統。這類電漿系統不但能在極低壓下產 生高密度電漿,並且能分別控制電將密度與離子能量,減少離子轟擊損 壞,在大尺吋晶圓上亦能保持良好的均勻性,提高生產良率。除此之外, 如何減少電漿電賀導致損壞,使用靜電吸附夾具,使用多腔設計系統, 均勻度是未來蝕刻機趨勢。多腔設計可以避免相互汙染,並增進生產速 率。使用靜電吸附夾具可以降低粒子汙染,增進晶片冷卻效率,而減少 電漿導致損壞可使製程上的設計變得更單純,並提高元件的可靠性。

第三章 實驗機台介紹與分析

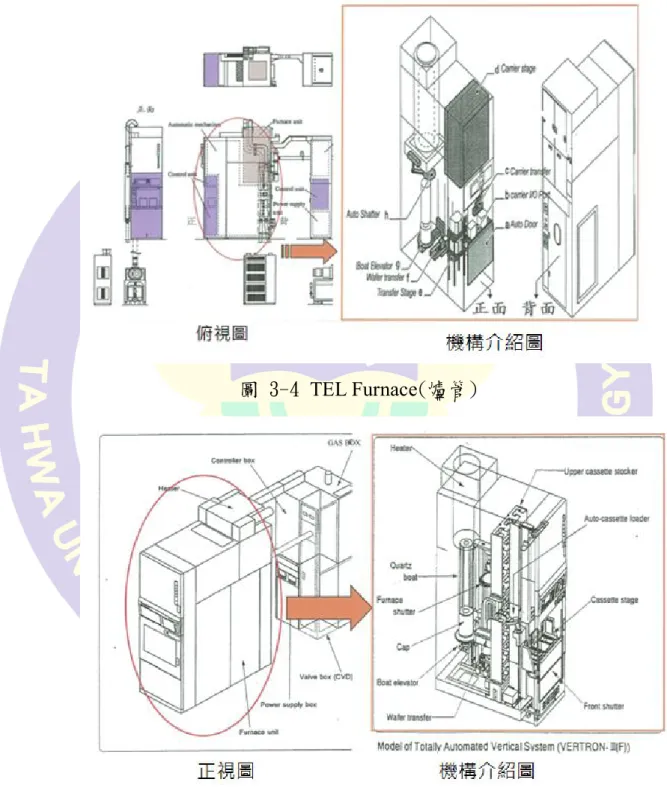

3.1 實驗機台介紹 前 第 二 章 已 經 說 明 有 關 LPVCD 的 低 壓 化 學 氣 相 沉 積 爐 管 (Low-Pressure CVD, LPCVD)。而後續的實驗我們使用下面所提到的設備 來設計這次的實驗。 低壓化學氣相沉積爐管,一般而又稱沉積爐管,會使用一種或多種 氣體在高溫低壓下反應,型成固態膜沉積於晶片上。爐管是利用強制通 風,中效爐與鋼熱交換器和多速風機。 這些爐管比以前的設計更為不 一樣。爐管的裝備有將吹入空氣通過熱交換器的燃燒式鼓風機,其可以 大大提高效率,同時允許熱交換器變小。這些爐管可能具有多種的風機, 可設計用於與中央空調系統配合使用。本次實驗的設備有兩個設備廠商一個為東京電子(Tokyo Election Lim ited, TEL)生產出來的機台,如圖 3-1 所示,另一個為日立國際電器 (Hitachi Kokusal Electric CO.,LTD, KE) 生產出來的機台,如圖 3-2 所示。 在加熱的 LPCVD 或氧化過程中,沉積極薄的晶體管柵極並圍繞這些結 構製造。還採用 ALD 技術進一步奈米擴散和深溝槽圖案。這些設備的 特點為超清潔,最先進的加熱元件技術,可以高速晶圓的在機台裡傳送, 以及吹出乾燥的淨化氣體技術。在於應用方面,用於自由基氧化(LPRO), 超薄閘電介質形成(氧化,氮化),LPCVD(支援 Poly,SiN,SiO / 乾的淨化氣體),可以生成 High-K 膜(AIO,HfO,ZrO)。

TEL 爐管設備:a.為自動門(Auto Door);b.載具的進出口(Carrier I/O Port);c.載具交換的地方(Carrier Transfer);d.載具存放區(Carrier Stage);

(Boat Elevator);h.自動放晶圓(Auto Shatter)

圖 3-4 TEL Furnace(爐管)

3.2 實驗方法介紹

本次實驗我們將調整設備的四種條件,如歧管(Manifold)水平位置、 承載(Cap)的水平調整、水流量調整(Up-Flang)及抽風量調整(進 風口及出風口)。再將使用製程最差的及最好的設備來比較,所以最後 挑出七台設備,編號分別為最好的製程設備為 PU-1、PU-2。最差的製 程設備為 PU-3A、PU-5A、PU-1B。 經過兩個月的觀察之下選擇出不同的機台等級,利用製程能力指標 (Cp)來比較各個設備的製程能力好壞。如表 3-1 所示。 = ( − )/(3 ∗ ) (3-1) USL 為規範上線 Avg 為平均值 Sigma 為標準差 表 3-1 PU 控制晶圓片(M/W)改善前 Cp 值

NO PU 1 week 2 week 3 week 4 week 5 week 6 week 7 week 8 week

1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96

由表 3-1 可看出最佳的為 PU-1A 和 PU-2A,最差的為 PU-3A、PU-5A 及 PU-1B。

3.3 實驗設計之分析 實驗前有最佳的設備兩組(PU-1A、PU-2A)來比對最差的設備三組 (PU-3A、5A、1B)。後續將各種的設備調整承載水平方向、歧管水平 方向、水流量調整、抽風量調整(抽風口、進風口)。來尋找出最佳的 條件。 我們利用圖 3-3 來分析,M/W 位置上方跟下方均勻度厚薄相反,判 斷可能與承載水平不佳所造成的。 圖 3-3 M/W 1~7 分析表 本文將會尋找實驗方法來調整這些相關的位置,最後來尋找最佳因 子外,後續章節將會將調整的因子做分析結果。

第四章 實驗結果與討論

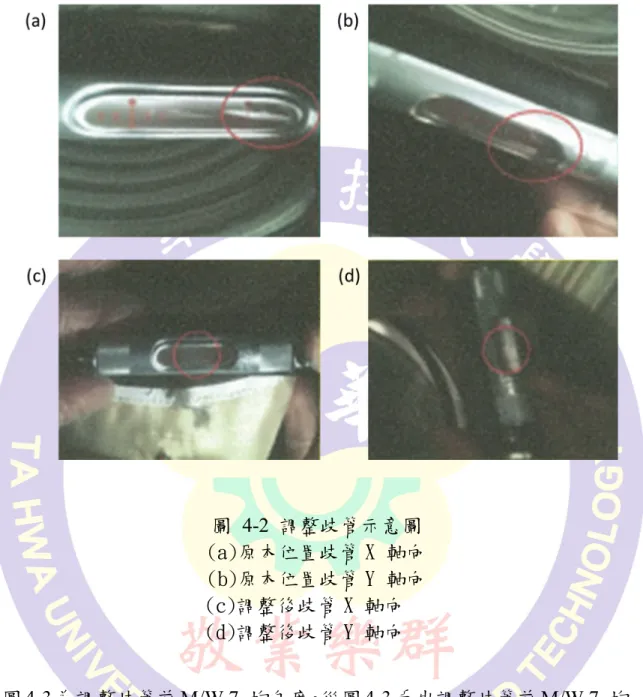

4.1 前言我們將針對 Cp 值較差的機台來做實驗,調整各種不同的參數來得 到不同結論。調整歧管水平位置、調整承載水平、水流量改善、抽風壓 力。 4.2 實驗步驟 我們將觀察實驗後的 7 台的每週 Cp 值,來看 Cp 值有沒有變化。 4.2.1 調整歧管 調整歧管的方法朝 9 點均勻度比較厚的方向去做調整,如圖 4-1 與圖 4-2 所示。 圖 4-1 (a)歧管水平調整方向(b)歧管正視圖

圖 4-2 調整歧管示意圖 (a)原本位置歧管 X 軸向 (b)原本位置歧管 Y 軸向 (c)調整後歧管 X 軸向 (d)調整後歧管 Y 軸向 圖 4-3 為調整歧管前 M/W 7 均勻度。從圖 4-3 看出調整歧管前 M/W 7 均 勻度 差了 120 Å(1596-1476=120), 調整歧管後均勻度變為 72 Å (1532-1460=72)。

圖 4-3 (a) 調整歧管前 (b)調整歧管後 表 4-1 為調整歧管前後均勻度比較。表 4-2 為 PU 控制晶圓片(M/W) 調整歧管後每週 Cp 值。由表 4-1 與 4-2 可知調整歧管後 M/W 1~7 均勻 度有變好且 PU-5A 有改善,由第 8 週的 0.5 提升到第 9 週的 1.12。圖 4-4 為其均勻度(M/W) 實驗改善後每週成效。 表 4-1 調整歧管前後均勻度比較 M/W1 M/W2 M/W3 M/W4 M/W5 M/W6 M/W7 Average PU-5A 調整歧管前 41.2 40.2 36.2 31.9 31.4 36.2 76.1 41.89 PU-5A 調整歧管後 40.8 31.3 28.7 26.9 27.8 28.4 63.5 35.34

表 4-2 PU 控制晶圓片(M/W)調整歧管後每週 Cp 值

No. PU 1 week 2 week 3 week 4 week 5 week 6 week 7 week 8 week 9 week 1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 1.84 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 1.68 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 0.98 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 1.12 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 0.85 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 1.74 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96 1.71 圖 4-4 均勻度(M/W) 實驗改善後每週成效 0% 20% 40% 60% 80% 100% 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

week

M/W均勻度CP

調整歧管水平位置

4.2.2 調整水流量 依照冷卻特性分析,發現溫度也會影響到產品,所以我們調整了水 的流量。水流量大小會影響溫度,如圖 4-5 所示,我們將使用編號 PU-5A 將水的流量調整為每一分鐘流 0.9 公升的水(0.9L/min)。而其他的設備調 整為每一分鐘流 0.5 公升的水(0.5L/min),如表 4-3 所示。 圖 4-5 水帶走熱量示意圖 表 4-3 調整水流量

PU-2A PU-3A PU-5A PU-1B PU-2B PU-6B

Repid(原始值) 4 5 5 5 4 5

Up-Flange 0.5L 0.5L 0.5L->0.9L 0.5L 0.5L 0.5L

Shutter(原始值) 1.3 1.1 1.2 1.4 1.3 1.4

表 4-4 為 PU-5A 調整水流量前後均勻度比較。表 4-5 為 PU 控制 晶圓片(M/W)調整水流量後每週 Cp 值。由表 4-4 與 4-5 可知調整調整水 流量後 M/W 1~7 均勻度有變好且 PU-5A 有改善,CP 值由第 9 週的 1.12 提升到第 10 週的 1.14。圖 4-6 為其均勻度(M/W) 實驗改善後每週成效。 表 4-4 PU-5A 調整水流量前後均勻度比較 PU-5A 水流量改善 M/W1 M/W2 M/W3 M/W4 M/W5 M/W6 M/W7 Average PU-5A Up-Flange 0.5L 54.3 39.1 38.6 38.1 35.7 43.7 76.8 46.61 PU-5A Up-Flange 0.9L 49.3 33.5 31.5 30.4 33.0 33.6 46.4 36.81 Unit:百分比% 表 4-5 PU 控制晶圓片(M/W)調整水流量後每週 Cp 值

No. PU 1 week 2 week 3 week 4 week 5 week 6 week 7 week 8 week 9 week 10 week 1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 1.84 1.87 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 1.68 1.71 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 0.98 1.14 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 1.12 1.14 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 0.85 1.68 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 1.74 1.75 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96 1.71 1.78

圖 4-6 均勻度(M/W) 實驗改善後每週成效 4.2.3 調整承載水平 此實驗用水平儀來調整承載水平方向,如圖 4-7。 圖 4-7(a)水平儀(b)水平儀在承載上 0% 20% 40% 60% 80% 100% 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

week

M/W均勻度CP調整歧管水平位置

調整水流量

圖 4-8 左圖為調整承載水平前後均勻度。從圖 4-8 看出調整承載水 平前 M/W 7 均勻度差了 101Å(1532-1431=101 Å),調整承載水平後均 勻度變為 56 Å(1036-980=56Å)。均勻度有變好。 圖 4-8 左圖為調整承載水平前;右圖為調整承載水平後 表 4-6 為調整 PU-3A 承載水平前後均勻度比較。表 4-7 為 PU 控制 晶圓片(M/W)調整承載水平後每週 Cp 值。由表 4-6 與 4-7 可知調整承載 水平後 M/W 1~7 均勻度有變好且 PU-3A 有改善,CP 值由第 10 週的 1.14 提升到第 11 週的 1.75。圖 4-9 為其均勻度(M/W) 實驗改善後每週成效。

表 4-6 調整 PU-3A 承載水平前後均勻度比較 PU-3A CAP M/W1 M/W2 M/W3 M/W4 M/W5 M/W6 M/W7 Average 調整前 46.8 41.4 48.8 44.2 39.9 43.0 75.4 48.50 調整後 43.2 38.8 44.5 39.7 37.8 40.4 57.0 43.06 Unit: 百分比% 表 4-7 PU 控制晶圓片(M/W)調整承載水平後每週 Cp 值

No. PU 1 week 2 week 3 week 4 week 5 week 6 week 7 week 8 week 9 week 10 week 11 week 1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 1.84 1.87 2.17 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 1.68 1.71 1.67 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 0.98 1.14 1.75 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 1.12 1.14 1.24 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 0.85 1.68 1.68 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 1.74 1.75 2.01 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96 1.71 1.78 1.71 0% 20% 40% 60% 80% 100% 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

week

M/W均勻度CP

調整歧管水平位置

調整水流量

調整承載水平位置

4.2.4 抽風壓力 利用抽風或進風的壓力來改善均勻度。先進行快速冷卻後,將 PU-5A 此設備機台抽風壓力從負的調整成正的。首先將了解再設備的抽風口及 進風口的位置,如圖 4-10 所示。 圖 4-10 抽風口及進風口位置 首先調整 PU-5A 的設備進風壓力及抽風的壓力,我們將抽風口壓 力從-420PSI 調整為 190PSI,進風口壓力從-0.1 調整為 0,如表 4-8 所示。 表 4-9 為 PU-5A 抽風壓力調整前後均勻度比較。表 4-10 為 PU 控制 晶圓片(M/W)調整抽風壓力後每週 Cp 值。由表 4-9 與 4-10 可知調整承 載水平後 M/W 1~7 均勻度有變好且 PU-3A 有改善,CP 值由第 11 週的 1.24 提升到第 12 週的 1.34。圖 4-11 為其均勻度(M/W) 實驗改善後每週 成效。

表 4-8 調整抽風口壓力

PU-2A PU-3A PU-5A PU-1B PU-2B PU-6B

進風壓力(PSI) 0 0.1 -0.1->0 0 0.2 0 抽風壓力(PSI) -158.1 -346.8 -420.4->190 -387.1 -152.5 -158.1 表 4-9 PU-5A 抽風壓力調整前後均勻度比較 PU-5A M/W1 M/W2 M/W3 M/W4 M/W5 M/W6 M/W7 Average 抽風壓力調整前 39.4 33.2 29.6 29.8 28.2 29.8 66.6 36.66 抽風壓力調整後 26.9 27 27.2 21.9 23 25.1 45.1 28.03 Unit:百分比% 表 4-10 PU 控制晶圓片(M/W)調整抽風壓力後每週 Cp 值

No. PU 1week 2week 3week 4week 5week 6week 7week 8week 9week 10week 11week 12week 1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 1.84 1.87 2.17 2.06 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 1.68 1.71 1.67 2.23 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 0.98 1.14 1.75 1.71 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 1.12 1.14 1.24 1.34 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 0.85 1.68 1.68 1.69 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 1.74 1.75 2.01 1.83 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96 1.71 1.78 1.71 1.85

圖 4-11 均勻度(M/W) 實驗改善後每週成效 4.3 實驗結果分析與討論 本實驗調整不同的參數也有所不同的改善,雖然改善不同的位置有 不同的改良。最後都是以好的方向前進。表示不管是溫度、位置…等。 這些因子都會反應到數據上,如表 4-11 所示。 表 4-11 實驗調整後整體的 Cp No. PU 1 week 2 week 3 week 4 week 5 week 6 week 7 week 8 week 9 week 10 week 11 week 12 week 13 week 14 week 15 week 16 week 1 PU-1A 2.05 2.27 1.72 2.05 2.02 2.02 2.37 1.77 1.84 1.87 2.17 2.06 2.86 2.57 3.13 2.9 2 PU-2A 2.12 2.42 2.71 3.26 3.11 3.11 1.72 2.19 1.68 1.71 1.67 2.23 1.78 1.85 2.01 2.56 3 PU-3A 0.7 0.59 0.8 0.76 0.78 0.55 0.87 0.47 0.98 1.14 1.75 1.71 1.72 1.84 2.38 2.08 4 PU-5A 0.88 0.78 0.96 0.88 0.72 0.82 0.9 0.5 1.12 1.14 1.24 1.34 1.34 1.7 1.78 1.72 5 PU-1B 0.74 0.68 0.7 1.19 0.64 1.29 1.14 1.19 0.85 1.68 1.68 1.69 1.69 1.73 2.07 1.79 6 PU-2B 1.71 1.75 1.68 1.82 1.73 1.73 1.75 1.71 1.74 1.75 2.01 1.83 1.83 1.75 2.37 2.09 7 PU-6B 1.91 1.70 1.71 1.75 1.68 1.71 1.81 1.96 1.71 1.78 1.71 1.85 1.99 2.55 2.42 3.06 0% 20% 40% 60% 80% 100% 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

week

M/W均勻度CP

調整歧管水平位置 調整水流量 調整承載水平位置 調整抽風壓力第五章 結論與未來研究方向

5.1 結論 實驗設計與產品均勻度改善間有著密不可分的關係,對均勻度改善 人員而言,實驗設計可以讓改善人員在規劃實驗時所花費之人力和時間 成本最小,且能夠精確的找出解決製程問題的最佳配方,讓產品均勻度 能夠改善。本研究以新竹科學園區一家公司所產生之均勻度改善為研究 個案,利用四個實驗設計方法來規劃提升了均勻度。 由本研究之結果可知,本論文所提之設計規劃可提升爐管氮化矽品 質(均勻度由第一週的 1.44 提升至第十六週的 2.31)外,並可降低製程人 員調機之人力及減少調機錯誤的風險(沉積的時間和溫度)。 5.2 未來研究方向 本論文未來可以繼續研究的方向有下列幾點: 1. 本 論 文 這 次 實 驗 的 設 備 廠 商 只 提 到 如 何 改 善 設 備 日 立 國 際 電 器 (Hitachu Kokusal Electric CO.,LTD, KE)均勻度,沒有提到如何改善另一 個機型設備東京電子(Tokyo Electron Limited,TEL)均勻度,後續研究者可 就此方向做研究探討。參考文獻

[1] 康家榕,2010,運用 Fuzzy C-means 與均勻化法解決半導體化學機械 研磨平坦化問題,國立清華大學工業工程與工程管理學系碩士論文。 [2] 唐福連,2016,半導體爐管製程中微粒與缺陷之探討,逢甲大學工業 工程與系統管理學系碩士論文。 [3] http://blog.ylsh.ilc.edu.tw/geo/modules/newbb/dl_attachment.php?attachi d=1276007959&post_id=101 [4] http://www2.nsysu.edu.tw/IEE/lou/elec/web/process/semi.htm,半導體製 作流程。 [5] 吳忠義,正修科技大學教學卓越計畫,半導體元件與製程模擬實習。 [6] 李明修,2000,濕式清洗製程改善快閃記憶體金屬佈線與通道連接電 阻降低研究,國立交通大學工學院半導體材料與製程設備學程碩士論 文。[7] 張 育 唐 , 2012 , 化 學 氣 相 沉 積 法 (Chemical Vapor Deposition) , http://highscope.ch.ntu.edu.tw/wordpress/?p=40948。 [8] http://140.123.5.6/coleng/uploads/02%20VLSI_technology.pdf。 [9] 張 文 澤 , 2016 , 熱 氧 化 製 程 , http://www.ccut.edu.tw/teachers/wentse/downloads/fabrication06.ppt。 [10] 李 元 堯 , 2012 , 半 導 體 製 程 技 術 , http://tdc.csu.edu.tw/home01.aspx?ID=$3001&IDK=2&EXEC=D&DAT

=760。 [11] 楊 雲 凱 , 2014 , 物 理 氣 相 沉 積 (PVD) 介 紹 , http://www.ndl.narl.org.tw/docs/publication/22_4/pdf/E5.pdf。 [12] 莊達人,VLSI 製造技術,高立圖書有限公司,民國 102 年 8 月。 [13] http://www.sharecourse.net/sharecourse/upload/course/181/8aea1adee7 3ee3db9d7af9ac624bdeac.pdf。 [14] 黃政平,2003,台灣半導體製程技術現況與趨勢之研究-以技術地 圖探討,國立臺北大學企業管理學系碩士論文。

![圖 2-7 微影示意圖 2.2.4 蝕刻 蝕刻製程的功能,是要將進行微影製程前所沉積的薄膜,厚度約在 數千到數百 Å 之間,把沒有被光阻覆蓋及保護的部分,以化學反應或是 物理作用的方式加以去除,已完成轉移光罩圖案到薄膜上面的目的[ 12] 。 蝕刻製程乃是將經過微影製程在表面定義出 IC 電路圖案的晶圓,以 化學腐蝕反應的方式,或物理撞擊的方式,或上述兩種方式的合成效果, 去除部份材質,留下 IC 電路結構。 蝕刻技術可分兩種, 「濕蝕刻 (Wet Etching](https://thumb-ap.123doks.com/thumbv2/9libinfo/7270678.69482/25.892.126.770.174.1001/及保護罩圖案到薄膜上面目的蝕刻製程乃是過微去除部份材質留下.webp)