國 立 交 通 大 學

機 械 工 程 學 系

碩士論文

利用 CMOS-MEMS 技術製作低電壓驅動微機械邏輯閘

Using CMOS-MEMS Technology to Fabricate

the Low Voltage MEMS Logic Gate

研 究 生: 林廷儒

指導教授: 陳宗麟 博士

利用 CMOS-MEMS 技術製作

低電壓驅動微機械邏輯閘

學生:林廷儒 指導教授:陳宗麟 博士

國立交通大學機械工程學系 碩士班

摘要

本實驗室先前研發微機械邏輯閘(MEMS logic gate),其特點在於可利用單 一機械結構實現 NAND 閘和 NOR 閘的功能。為了和現有電路進行整合,本研究 預計使用 CMOS-MEMS 製程來製作此一邏輯閘。先前研究受限於製程問題及設 計未臻完善,使得製作出的元件存在無法懸浮、無法實現金屬-金屬接觸功能、 驅動電壓過高、等問題。本研究針對上述問題,修改後製程與元件設計,提出解 決方式。 本研究所使用的製程為 TSMC 0.35μm 2P4M,該製程提供的導體層包括: 鋁、鎢、雜質參雜的多晶矽、氮化鈦。在研究各材料特性與製程整合可行性後, 本研究選用具高熔點、高硬度的氮化鈦來實現低阻抗的接觸(contact)性能規格。 然而定義氮化鈦並非 2P4M 製程的標準步驟,因此如何定義氮化鈦的尺寸與位置, 以及如何蝕刻鋁而保留氮化鈦成為本研究的重點之一。 由於必須與現有電路整合以及提高元件的生命週期(life cycles),元件的操 作電壓設定在 5V 以下。元件的操作電壓和元件的剛性及驅動力直接相關。為了 避免元件因接觸而產生粘著問題(adhesion problem),元件的剛性不宜設計過低,

因此驅動力的估算必須儘可能準確。本元件的驅動力來自於上下電極、0.6µm 空 隙、1µm 二氧化矽所構成的靜電力。傳統的靜電力估算方式直接簡化二氧化矽層 所造成的影響,進而造成較保守的靜電力估算。本研究重新推導相關的公式,估 算雙層介電材料的靜電力。 本研究藉由量測先前設計/製作的微機電邏輯閘,獲得相關數據,進而重新 設計製程與元件尺寸。所完成的新的微機電邏輯閘設計尺寸約 250µm x 230µm, 共振頻率 11kHz,輸入/輸出訊號 (0V, 5V)。目前已完成相關的設計、數值模 擬、元件佈局。

Using CMOS-MEMS Technology to Fabricate

the Low Voltage MEMS Logic Gate

Student: Ting-Ju Lin Advisor: Dr. Tsung-Lin Chen

Department of Mechanical Engineering

National Chiao Tung University

Abstract

In our previous study, we proposed a novel MEMS logic gate that can implement the NOR gate and NAND gate function on the same mechanical structure. In order to promote this MEMS device, this research aims to fabricate the design using foundry-provided CMOS-MEMS process. After experimenting on our first design, we found that the old design suffer from release problem, contact problem, and high actuation voltage problems, and etc. In this research, we proposed a new post-fabrication process and new design, aiming to solve above problems.

The intended CMOS-MES process is TSMC 0.35μm 2P4M, which contains conducting layers including aluminum, tungsten, doped polysilicon, and titanium nitride. After examining the mechanical/ electrical properties and process integrity of each layer, we choose titanium nitride to realize the functionality of low-resistance contact. However, patterning the titanium nitride layer is not a standard service provided by the foundry. Therefore, patterning titanium nitride and etching aluminum while preserving titanium nitride become key issues in this research.

In order to integrate the proposed MEMS device with existing IC circuits and to extend the life cycles of the MEMS device, the MEMS gate should operate below 5Volts. The operating voltage is determined by the actuation force and stiffness of the

device. Since the device stiffness cannot be too soft for the sake of adhesion problem, the actuation force should be carefully estimated. In this design, the actuation force comes from the electrostatic force, which involves a 0.6µm air gap and 1µm silicon dioxide between the top and bottom electrodes. The conventional approach neglecting the 1µm silicon dioxide layer results in a conservative estimate of electrostatic force. In this research, we derive the equations for the electrostatic force with composite dielectric materials, to estimate the electrostatic force more precisely.

In this research, we conducted several experiments on the previously designed devices. Using those experimental data, we modified the post-fabrication process and redesign the device dimensions to meet the performance specifications. Currently, the new device has the footprint of 250µm x 230µm, operating voltages (0V, 5V), resonant frequency of 11kHz. The work of performance simulation and design layout has also been completed.

致謝

首先誠摯的感謝指導教授 陳宗麟博士,指導了我不管是學術上的知識、如 何有邏輯的循序漸進,將一件事完成,最令我敬佩的是,老師那豐富的經驗和對 研究嚴謹的態度,每當我遇到困難時,老師總能提供正確的方向和建議,讓我獲 益良多,也使得我的研究生涯更加順利。 再來要謝謝實驗室的學長張正暘、吳健彰,提供了很多寶貴的意見和經驗分 享,讓我在研究過程中更為順利,也謝謝一起努力的同學子成、睿群、博詮和冠 豪,在實驗室生活的點點滴滴,令人難忘,當然也要謝謝學弟們的陪伴,讓研究 生活增添了許多樂趣。 最後,要謝謝我的父親 林景森先生與母親 陳素雲女士,感謝他們提供很好 的環境讓我念書,讓我沒有後顧之憂,在此獻上最誠摯的感謝。目錄

中文摘要 ··· I 英文摘要 ··· III 致謝 ··· V 目錄 ··· VI 圖目錄 ··· VIII 表目錄 ··· XI 第一章 緒論 ··· - 1 - 1.1 文獻回顧··· - 1 - 1.1.1 邏輯閘··· 1 1.1.2 接觸金屬··· 4 1.2 研究動機··· 7 1.3 本文架構··· 7 -第二章 基本介紹 ··· - 8 - 2.1 微機電系統··· 8 2.2 邏輯閘介紹··· 8 2.3 微機電邏輯閘··· 9 2.4 金屬金屬接觸 ··· 10 2.5 TiN 簡介 ··· 10 -2.6 TSMC 0.35μm 2P4M CMOS-MEMS 介紹 ··· - 11 - 2.7 Silox VapoxIII 介紹 ··· 12 -第三章 邏輯閘結構 ··· - 13 -3.1 雙層式微機電邏輯閘··· 13 3.2 邏輯閘尺寸··· 14 3.3 作動原理··· 15 -第四章 製程步驟與實驗結果 ··· - 17 - 4.1 製程步驟··· 17 4.2 實驗結果··· 21 4.2.1 使用 BOE 之實驗結果··· 21 4.2.2 使用 Silox VapoxIII 之實驗結果 ··· 21 -第五章 新尺寸設計 ··· - 28 - 5.1 設計目的··· 28 5.2 雙層介電質靜電力公式推導··· 29 5.3 Serpentine Spring 介紹 ··· 32 5.4 彈簧尺寸··· 33 5.5 模擬結果··· 34 5.6 元件設計··· 40 5.7 layout 圖··· 48 -第六章 結論與未來方向 ··· - 49 - 6.1 結論··· 49 6.2 未來方向··· 49 -參考文獻 ··· - 50 -

圖目錄

圖 1. S.W LEE 等人提出的邏輯單元 ··· 1 圖 2. 輸入/輸出關係圖 ··· 1 圖 3. HIRATA 等人所提出的微機械邏輯閘 ··· 2 圖 4. RHESA, NATHANAEL 等人所提出平板式微機械開關結構··· 3 圖 5. JAESEOK, JEON 等人提出的翹翹板式微機械開關示意圖 ··· 3 圖 6. 鎢受到 BOE 蝕刻之 SEM 圖 ··· 5 圖 7. 凸塊結構製作流程圖 ··· 6 -圖8. TSMC 0.35ΜM 2P4M 的標準 CMOS 製程··· - 11 - 圖 9. 鋁金屬層與 VIA 的詳細圖 ··· 12 圖 10. 雙層式微機電邏輯閘示意圖 ··· 13 圖 11. 邏輯閘上下電極示意圖 ··· 14 圖 12(A). 上視圖 ··· 18 圖 12(B). 剖面圖 ··· 19 圖 12(C). PAD 光罩圖形 ··· 19 圖 12(D). RLS 光罩圖形 ··· 19 圖 12(E). FHD5 濕蝕刻釋放元件 ··· 20 圖 12(F). RIE 去除 TIN ··· 20 圖 12(G). BOE 濕蝕刻 ··· 20 圖 13. FHD5 濕蝕刻後 OM 圖 ··· 22圖 14. 鋁濕蝕刻後晶片 EDS 分析圖 ··· 22 圖 15. RIE 後邏輯閘之 OM 圖 ··· 23 圖 16. RIE 後 TESTKEY 之 OM 圖 ··· 23 -圖 17. SIO2濕蝕刻後邏輯閘之 OM 圖 ··· 23 圖 18. 邏輯閘去掉上電極示意圖 ··· 24 圖 19. 邏輯閘 LAYOUT 圖··· 25 圖 20. 量測結果圖 ··· 26 圖 21. 蝕刻孔圖 ··· 27 圖 22. 邏輯閘側視圖 ··· 27 圖 23. 雙層介電質示意圖 ··· 29 圖 24. SERPENTINE SPRING 示意圖 ··· 32 圖 25. 彈簧示意圖 ··· 33 圖 26. 彈簧側視圖 ··· 33 圖 27. 電極配置示意圖 ··· 35 圖 28. ANSYS 模擬平板 Y 方向位移量圖(I) ··· 36 圖 29. ANSYS 模擬平板 Y 方向位移量圖(II)··· 36 圖 30. ANSYS 模擬平板 Y 方向位移量圖(III) ··· 37 圖 31. 新設計共振頻率圖(第一模態) ··· 37 圖 32. 新設計共振頻率圖(第二模態) ··· 38 -圖 33. M-Ɵ 關係圖(樑寬=5UM) ··· - 38 - 圖 34. 平板旋轉示意圖 ··· 39

圖 35. 鋁(METAL2)蝕刻速率 TESTKEY ··· 40 圖 36. TIN 蝕刻 TESTKEY ··· 41 圖 37. SIO2 蝕刻速率 TESTKEY ··· 42 圖 38. TIN 導電性 TESTKEY ··· 43 圖 39. OXIDE 寬度示意圖 ··· 43 圖 40(A). 製程流程(M1,2,3)1 ··· 44 圖 40(B). 製程流程(M1,2,3)2 ··· 44 圖 40(C). 製程流程(M1,2,3)3 ··· 45 圖 40(D). 製程流程(M1,2,3)4 ··· 45 圖 41(A). 製程流程(M1)1 ··· 46 圖 41(B). 製程流程(M2)2 ··· 46 圖 41(C). 製程流程(M1)3 ··· 47 圖 41(D). 製程流程(M1)4 ··· 47 圖 42. 新設計 LAYOUT 圖··· 48

-表目錄

表 1. 不同驅動電極和支撐樑之尺寸 ··· 2 表 2. 有潛力作為開關接觸的金屬 ··· 4 表 3. 不同製程參數下的 TIN 薄膜電阻率 ··· 5 表 4. 基本邏輯閘的輸入/輸出關係與符號 ··· 9 表 5(A). FHD5 濕蝕刻參數表 ··· 21 表 5(B). RIE 機台實驗參數 ··· 21 表 5(C). SILOX VAPOXIII 濕蝕刻參數 ··· 21 表 6. 彈簧受靜電力時各方向之最大彎曲量 ··· 35-第一章

緒論

1.1 文獻回顧

文獻回顧分成兩部分,第一部分先介紹各種不同設計邏輯閘之功能性,第二 部分則針對開關常見問題:金屬-金屬接觸問題,做初步的探討。1.1.1 邏輯閘

圖 1. S.W Lee 等人提出的邏輯單元 圖 2. 輸入/輸出關係圖此為 S.W Lee 等人提出的 MOS-like 元件[1],藉由輸入訊號給 source 和 gate,產 生靜電力造成 drain 輸出,結果如圖 2。圖 1(b)之改良是為了避免 source 接觸到 gate 並且改善圖 1(a)需要大面積 gate 才能產生足夠靜電力矩使懸臂樑吸附。

圖 3. Hirata 等人所提出的微機械邏輯閘 表 1. 不同驅動電極和支撐樑之尺寸 圖 3 為 Hirata 等人所設計的微機械邏輯閘[2],由兩個固定驅動電極、兩個 固定接觸電極、兩個可移動式驅動電極和一個可移動式接觸電極組成,在 S3 條 件下,需要左右電極都給驅動電壓 30V,開關才有電壓輸出,此即為 AND 閘, 在 S5 條件下,只需要有一邊驅動電壓為 30V,開關就有電壓輸出,此即為 OR 閘,此微機械邏輯閘利用兩組不同面積大小的驅動電極,來達到 AND 閘或 OR 閘的邏輯功能(並非同一個元件同時達到兩種邏輯功能)。

圖 4. Rhesa, Nathanael 等人所提出平板式微機械開關結構 Rhesa, Nathanael 等人提出平板式微機械開關的結構設計[3],和先前研究的 不同點在於,他增加了一組 body 的電極,用來控制開關。在”開”狀態時,因為 body 和 gate 之間的靜電力,導致開關導通。 圖 5. Jaeseok, Jeon 等人提出的翹翹板式微機械開關示意圖 Jaeseok, Jeon 等人提出的翹翹板式微機械開關的結構設計[4],他固定下電極 的電壓,調整上電極電壓來造成翹翹板的作動,和一般單邊的邏輯閘相比,翹翹 板式回復力矩不僅是靠彈簧,也藉由另一邊之靜電力,可以避免黏附現象。

1.1.2 接觸金屬

根據 A. Tazzoli 等人的文獻[5]指出,接觸金屬之可靠性會影響開關的機械特 性和電性,若可靠性差,容易發生接觸金屬表面氧化或是多次接觸後造成接觸金 屬變形等等的問題,導致所設計之元件失效。為了解決接觸金屬的問題,H. Kam 等人提出[6]在接觸金屬上在沉積一層 0.25Å 的二氧化鈦介電薄膜,可有效的減 緩微電銲的現象,改善接觸金屬的問題。本論文則是希望找到一種可靠性高的材 料,來解決此問題。 表 2. 有潛力作為開關接觸的金屬 根據 Qing MA 等人的文獻[7],他提供了幾個有潛力作為接觸金屬的金屬特 性分析,由表可得知 AuNi5、Rh 和 Au 相比有較高的硬度,更適合做為接觸金屬, 但考慮到製程的便利性,所以本文不採用。圖 6. 鎢受到 BOE 蝕刻之 SEM 圖 本實驗室先前之研究[8]是用鎢(tungsten)當作接觸金屬,但是由於金屬鈦蝕 刻液也會蝕刻鎢,導致接觸金屬被破壞,無法導通。 表 3. 不同製程參數下的 TiN 薄膜電阻率 常見金屬電阻率(*10 - 4Ω‧cm) : Ag:0.01586 Cu:0.0678 Au:0.024 Al:0.026548 Ni:0.0684 Ti:0.42

雖然 TiN 的電阻率會隨著形狀等等的性質而改變,但是依據 K. Lal 等人的 文獻[9]指出,他利用不同的參數製作 TiN 薄膜,並量測其電阻率,根據 TiN 的 電阻率和常見金屬電阻率相比,雖然電阻率高了十倍,但仍有作為接觸金屬的可 能性。 圖 7. 凸塊結構製作流程圖 實驗室先前之研究[8],做了 dimple 設計,除了限制平板之旋轉角度外,也 避免上下驅動電極相互接觸,造成吸附電壓無窮大而使邏輯功能失效。

1.2 研究動機

研究學長製作的微機電邏輯閘[8]的結果後,發現使用 CMOS-MEMS 的標準 製程,其主要的問題來自於金屬與金屬接觸的部分。金屬-金屬接觸,不但需要 具有導電性,也要考慮其硬度等材料性質,才能滿足微機電邏輯閘的要求,並同 時具有較長的壽命,故解決金屬接觸問題是必要的。 CMOS-MEMS 製程部分,問題來自於 Ti 蝕刻液會有效蝕刻掉 Ti 金屬與 TiN, 但同時也把欲當作接觸金屬的 via:W 給蝕刻掉,如果直接讓鋁金屬層外露當作 接觸金屬,則會有氧化的問題,本論文提出另一種想法,將原本欲蝕刻掉的 TiN 做為接觸金屬,TiN 有著高熔點、高硬度、高溫化學穩定性、優良導熱性、導電 性等等, 其中的導電性是我們所要的,加上 TiN 是本身就在 CMOS-MEMS 標 準製程中就有的,如果可以直接使用,除了減少後續額外的製程,更可以增加良 率。 不同於 MOS-like 開關,藉由串聯、並聯達到邏輯功能,我們希望以單一機 械結構,達到 NAND 和 NOR 的邏輯功能,如此一來可以提升此邏輯閘之泛用性。 本設計希望與市面上的電路商品整合,所以採用 TSMC 0.35um 2P4M CMOS-MEMS 製程來製作。1.3 本文架構

本論文共包含六個章節,第一章為緒論,內容包括文獻回顧與研究動機。第 二章則將使用到的材料、製程和蝕刻液作簡單介紹。第三章介紹雙層式微機電邏 輯閘、設計之邏輯閘尺寸和其作動方式。第四章則分成兩部分,第一部分為使用 BOE 之製程步驟和結果,第二部分則是使用 silox vapoxIII 之實驗結果。第五章 對先前設計做修改,提出了一個新設計,並呈現其模擬結果。最後一章為結論與 未來方向。第二章

基本介紹

2.1 微機電系統

微機電,顧名思義,就是指微小的機器。這概念最早是由物理學家費曼博士 (Richard Phillips Feynman)提到,於 1978 年,「微機器(Micromachines)」一詞出現 於國際學術研討會之中。之後 1989 年,於美國鹽湖城的一場研討會中,「微機電 系統(MEMS, Micro-electro-mechanical systems)」這名詞被具體提出。

微機電系統技術起源於對半導體製程技術,當半導體製程技術日漸成熟,微 機電系統也開始蓬勃發展,將原本用於微電子產業的半導體技術,拿來製作微米 級的機械結構。演變至今,微機電從學術到進產業界,並大量的用於生活中。 微機電主要分為三種:微結構、微感測器和微致動器。微結構是靜態式作用, 如微透鏡、微齒輪、微流道、微噴嘴等等;微感測器則是用來量測物理量或化學 亮,如加速度計、流速計、壓力計、化學感測器、熱感測器等;微致動器則是將 輸入能源,通常是電訊號,轉化成運動輸出,如梳狀致動器、微馬達、微幫浦等。

2.2 邏輯閘介紹

邏輯閘,是一種擁有布林邏輯運算功能的電子元件,構成數位電路的基本邏 輯閘包括下列六種:AND、OR、NOT、NAND、NOR、XOR,其真值表(true table) 與邏輯符號分別列於表 4 中:表 4. 基本邏輯閘的輸入/輸出關係與符號

其中,上述六種邏輯運算又可用 AND 閘、OR 閘、NOT 閘三種組合而成, 而這三種又可以用 NAND 閘跟 NOR 閘組合而成,故 NAND 閘跟 NOR 閘被稱為 通用型邏輯閘,只要能做出 NAND 閘跟 NOR 閘兩種邏輯閘,即可組成各種邏輯 電路。

2.3 微機電邏輯閘

微機電邏輯閘,結合了微機械開關的優點:低耗能、高絕緣性、批次製造, 與 IC 邏輯閘的布林代數運算功能,可直接取代傳統邏輯線路中,某些部分的 IC 邏輯閘。 微機電邏輯閘的概念最早在 1999 年由 A. Hirata 等人[2]提出,他們利用懸浮 結構搭配兩組不同面積大小的驅動電極,達到了 AND 閘跟 OR 閘的邏輯功能。 之後有人以仿造 MOS 的功能設計機械電晶體,可實現類似 PMOS 或 NMOS 的 開關功能,但若要達到 NOR 閘或 NAND 閘的邏輯功能,則要四個以上元件串、 並聯才能達成,此作法會增加佈局面積、製程複雜度等等問題。2.4 金屬-金屬接觸

不管是在微機電邏輯閘中,或者是一般的電阻式微機電開關中,金屬與金屬 的接觸是一個非常重要的問題,常常也會是一個元件能否運作的關鍵因素。

由於微機電把機械微小的緣故,不論是金屬導線,亦或是結構上面用以接觸 的金屬,都變得非常的小,許多本來一般機械上不會被考慮的因素也要被納入考 量,像是金屬與金屬接觸的粘黏(adhesion)、凡得瓦力(Van Der Waals force)、氧 化、表面粗糙度,都會直接影響一個微機電邏輯閘、微機電開關的可靠度。 在一個微機電邏輯閘和電阻式微機電開關中,做為接觸點的金屬通常要承受 不斷的接觸、分開,不斷的開關會造成金屬表面粗糙度下降,長期下來,金屬表 面會變得光滑,而產生極大的凡得瓦力,使得金屬與金屬間產生黏著現象,因而 損壞。另外還有電流通過產生的熱和微電銲現象,都會使得接觸用的金屬可靠度 下降。另外的問題則是氧化問題,幾乎全部的金屬暴露於空氣中都會氧化,常用 於 CMOS 製程中的鋁活性較大,一暴露於空氣中就馬上氧化,而造成元件的損 壞。

2.5 TiN 簡介

氮化鈦(TiN)屬於一種陶瓷材料,高熔點、高硬度、高溫化學穩定性及優良 的導熱性能、導電性能、耐磨耗性、抗腐蝕性,通常將其鍍於鈦合金、不銹鋼、 碳化鎢和鋁合金表面,以強化基材表面特性,由於具有金色的金屬光澤,也常被 應用於珠寶、汽車等裝飾用途,此外,氮化鈦的無毒性與生物相容性,也使它被 用於醫療生物方面。 CMOS-MEMS 標準製程中的 TiN 其原本目的是作為障礙擴散層,防止鋁金 屬層往氧化矽層擴散,如果能將其使用在 MEMS 開關中金屬與金屬接觸的部分, 不僅不用額外增加製程蝕刻掉 TiN 層與 Ti 層,也可以藉由 TiN 優越的特性:高 熔點、高硬度、導電性、耐磨性,有效且同時的解決金屬與金屬接觸時所遇到的 種種問題。2.6 TSMC 0.35μm 2P4M CMOS-MEMS 介紹

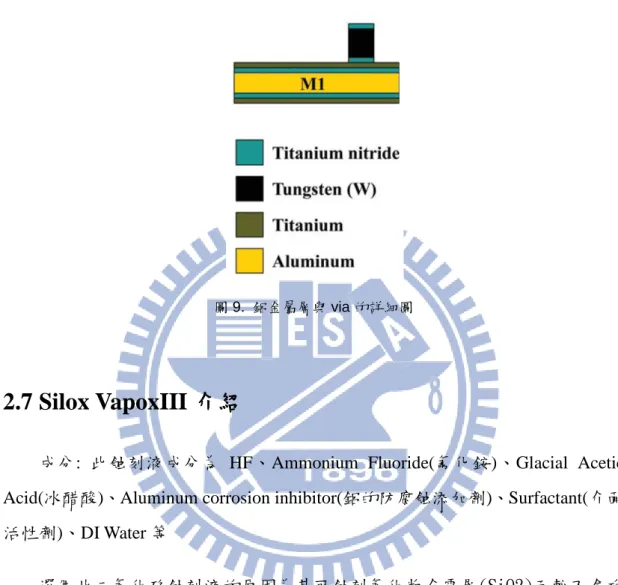

一般來說,製作微機電元件的方式可分為兩種:一種是自行設計製程步驟及 製程參數,優點是自主性高,可針對欲設計的 MEMS 元件設計出一套最佳的製 作程序,缺點是較為耗時,且設計者需具備相當的製程經驗;另一種方法則為借 助積體電路代工廠,使用代工廠所提供的標準化製程方式,再搭配「後製程處理 程序」(post-CMOS process)來完成 MEMS 的製作,優點是 MEMS 與 IC 電路易 整合,以及縮短元件製作時程,但是缺點是設計者必須牽就現有的製程參數與製 程步驟,在許多的限制下設計所要的微機電元件。 圖 8 是台灣積體電路製造公司所提供的 0.35μm 2P4M 製程,如圖所示,製 程中有兩層多晶矽(polysilicon)(紅、綠)、四層鋁(Aluminum)金屬(黃)、及金屬與 金屬之間的氧化矽(silicon oxide),做為絕緣層之用,圖中的黑色部分,則是為了 讓不同層的金屬彼此間能具有電性傳輸功能,而蝕刻出來的通道(via),其材料為 鎢(Tungsten)。 圖 8. TSMC 0.35μm 2P4M 的標準 CMOS 製程

若更詳細的做細部研究,可發現在金屬層的上下,皆包覆著一層氮化鈦 (Titanium nitride, TiN)及金屬鈦(Titanium),如圖 9。而用於通道的鎢上下也各有 一層氮化鈦。

圖 9. 鋁金屬層與 via 的詳細圖

2.7 Silox VapoxIII 介紹

成分: 此蝕刻液成分為 HF、Ammonium Fluoride(氟化銨)、Glacial Acetic Acid(冰醋酸)、Aluminum corrosion inhibitor(鋁的防腐蝕添加劑)、Surfactant(介面 活性劑)、DI Water 等 選用此二氧化矽蝕刻液的原因為其可蝕刻氧化物介電層(SiO2)而較不會攻 擊鋁,和原本使用的 BOE 蝕刻液相比,其對於 SiO2 和 Al 的選擇比更好,能更輕 易的掌握濕蝕刻的時間。蝕刻速率約為每分鐘 960 Å[10][11]。 先前學長使用的二氧化矽蝕刻液為 BOE,他對二氧化矽和鋁都有不錯的蝕刻 效果,因此在蝕刻二氧化矽的時候,若蝕刻時間過長,則很容易蝕刻到鋁,導致 電極的破壞,蝕刻時間太短,又無法將欲蝕刻的二氧化矽確實蝕刻完整,在換成 Silox VapoxIII 之後,可以輕易的改善這個問題。

第三章

邏輯閘結構

3.1 雙層式微機電邏輯閘

如圖 10,此雙層式微機電邏輯閘的構造,懸浮結構是由一個平板結構,被 兩側細長的懸臂樑所支撐著,平板受到下方底電極(灰色)的靜電力所吸引,因而 進行扭轉,支撐的懸臂樑則扮演著彈簧的角色,提供恢復力讓平板在不受力時回 到水平狀態。 圖 10. 雙層式微機電邏輯閘示意圖 圖 10 為一個 NOR 閘,其邏輯功能來自於平板兩側帶著不同的電位(Vcc+, Vcc-),以及下方底電極的面積不同所完成。底電極分成 A 與 B,就是輸入端, 當輸入訊號都是 1 時,平板順時鐘旋轉,輸出 0,反之則輸出 1。但是當輸入訊 號分別為 1 和 0 時,順時鐘與逆時鐘都會有靜電力產生,但由於底電極面積不相 同,因此兩邊的靜電力亦不相同,平板仍然會旋轉,以此圖為例,結果皆會順時 鐘旋轉,終將輸出 0 的訊號,故為 NOR 閘。若將上電極平板的電極交換,變成 Vcc-和 Vcc+,則此元件將變成一個 NAND 閘,故只需要一種設計,藉由改變其電極分配,即可同時實現 NOR 閘跟 NAND 閘,再經由串並聯,實現出全部共六 種的邏輯閘。

3.2 邏輯閘尺寸

圖 11. 邏輯閘上下電極示意圖 圖 11 為邏輯閘上下電極示意圖,其尺寸如上圖所示,結構包含[metal-1(紅 色), metal-3(淺藍色), metal-4(橘色)],紅色和淺藍色重疊的面積,即為上下電極能 產生靜電力的有效面積。 根據矩形樑扭轉公式[12]: Ф=𝑻𝑻𝑮𝑮 (3.1)得知 k=𝑮𝑮 𝑻= 31∗109∗0.312∗15∗1.63∗10−24 90∗10−6 =6.6*10−9 所以此邏輯閘的 torsional stiffness 即為 2k=1.32*10−8。 (懸浮結構由兩根彈簧支撐) Ф:旋轉角度 T:扭矩 G:剪力模數 J:慣性轉矩 L:懸臂樑長度

3.3 作動原理

假設上下各有一塊金屬平板,間距 d,上金屬平板給電壓 V 伏特,下金 屬平板給 0 伏特,A 為上下金屬平板投影之重疊面積,Ɛ 為介電常數,根據靜電 力公式: F=Ɛ𝐀(𝐕𝟐) 𝟐(𝒅𝟐) (3.2) 金屬平板會互相吸引,其產生吸引力的位置和上電極平板中間的距離,即為 其力矩的施力臂。 又懸臂樑根據其材料、尺寸,也可以得到其回復力矩,根據矩形樑的扭 轉公式: Ф=𝑻𝑻𝑮𝑮 (3.3) J=βdt3 (3.4)若已知旋轉角度Ф,懸臂樑長度 L,剪力模數 G,慣性轉矩 J 的話,則可得 知其回復力矩 T。

因此,在特定的旋轉角度下,比較其施力矩和回復力矩的大小,即可知 旋轉平板是否可以順利作動。

第四章

製程步驟與實驗結果

4.1 製程步驟

利用 CMOS-MEMS 標準製程技術來製作,使用 TiN 當作接觸金屬的狀況。 有幾點在佈局時必須考慮進去。

(1) 採用 metal-2 層的鋁金屬當犧牲層, metal-2 亦是後製程 RIE 時的阻擋層, 保護矽基板不受蝕刻攻擊,所以須利用佈局設計來保護 metal-1 下方的矽 基板不受到蝕刻攻擊。

(2) 懸浮結構部分必須同時擁有兩個不同的電位,因此需要包含絕緣的設計, 不僅是分隔懸浮部分 metal-3 的電位,也要能同時分開 metal-2 上下兩層 的 TiN 電位,才可以使元件擁有邏輯功能。

(3) 當 metal-2 被蝕刻掉後,金屬與金屬接觸的角色將由 metal-2 上下的 TiN 來扮演。

後製程部分先使用濕蝕刻液將 metal-2 去除,在送交交大奈米中心進行 HDP-RIE 高密度活性離子蝕刻將不需要的 TiN 去除,最後再利用 BOE 濕蝕刻去 掉 metal-2 中間用來絕緣的氧化矽,至此製程全部完成,以下將對製程詳加解說。

(a) 上視圖:圖 12(a)為利用 TSMC 2P4M CMOS-MEMS 標準製程所製作完 成的元件上視圖,此處只畫出 metal-3,其餘省略,左右兩邊分別是兩塊 不同電位的電極,分別在接觸底電極後輸出兩個不同的訊號(1 跟 0),由 導線經由兩懸臂樑接到輸入端。

(b) 剖面圖:圖 12(b)為經過 TSMC 2P4M CMOS-MEMS 標準製程製作完成 的元件剖面圖,metal-2 同時為犧牲層跟保護層,而 metal-4 則為懸浮結

構之保護層,保護懸浮結構的絕緣不被 RIE 所蝕刻,metal-1 為底電極, 外側兩塊為輸出,而內側兩塊不同大小的底電極即為使整個元件擁有邏 輯功能的重要部分,metal-3 則是懸浮結構中帶電部分,左右兩邊分別為 不同的電極。

(c) Pad 光罩圖形:如圖 12(c),為了要去除 metal-4 層上方的保護層(passivation layer),採用 CIC 所提供的 Pad 光罩,以利後面製程的蝕刻。

(d) RLS 光罩圖形:如圖 12(d),此步驟是利用 CIC 所提供的 RLS 光罩,針 對氧化矽層做非等向性的垂直蝕刻,定義出元件的幾何形狀及蝕刻孔大 小,並使 metal-2 裸露出來,方便之後的鋁金屬蝕刻。此時的 metal-4 及 metal-2 皆是蝕刻阻擋層,保護下方的基底和氧化矽懸浮結構。

(e) 濕蝕刻釋放元件:如圖 12(e),利用等向性的濕蝕刻將 metal-2 及 metal-4 完全去除,使元件能夠懸浮。在去除犧牲層的同時,要確保 TiN 及氧化 矽結構不受到侵蝕,故蝕刻液的選擇是非常重要的。 (f) 如圖 12(f),使用交大奈米中心 HDP-RIE 將部分 TiN 除去。 (g) BOE 濕蝕刻:如圖 12(g),將最後殘留於 metal-2 層中間部分的絕緣氧化 矽蝕刻掉。由於大部分的犧牲層上下皆有 TiN 保護著,故不會受到攻擊, 唯有中間裸露出來的二氧化矽會被蝕刻,使元件完全懸浮,到此製程結 束,元件也算是完成了。 圖 12(a). 上視圖

圖 12(b). 剖面圖 圖 12(c). Pad 光罩圖形 圖 12(d). RLS 光罩圖形 SiO2 SiO2 Wafer

圖 12(e). FHD-5 濕蝕刻釋放元件 圖 12(f). RIE 去除 TiN 圖 12(g). BOE 濕蝕刻 利用 TSMC 所提供的 CMOS-MEMS 標準製程來製作微機電邏輯閘,前半段 是採用代工完成,只需要注意佈局設計即可,然後元件成功與否,後製程才是關 鍵,蝕刻液的選擇、蝕刻時間長短,都會直接的影響結果。之後將介紹所使用的 蝕刻參數。

4.2 實驗結果

4.2.1 使用 BOE 之實驗結果

做完所有製程步驟後,將邏輯閘做電性測試,無法量到電性[13],原因為 BOE 對於二氧化矽和鋁的蝕刻選擇比不高,當 BOE 濕蝕刻時間過長,會導致電極被 蝕刻掉;當 BOE 濕蝕刻時間過短,中間殘留 SiO2,結構無完全懸浮。故欲知 BOE 濕蝕刻適當時間相當困難。於是我們將 BOE 蝕刻液換成先前所介紹的 Silox VapoxIII 蝕刻液來解決此問 題。

4.2.2 使用 Silox VapoxIII 之實驗結果

蝕刻參數&邏輯閘 OM 圖

表 5(a). FHD-5 濕蝕刻參數表 浸泡溶液 浸泡時間 FHD-5 20min DI water 5min IPA 5min 表 5(b). RIE 機台實驗參數 ICP Power 400 W Bias Power 100 W P 10 mTorr BCl3 35 sccm Cl2 35 sccm Time 3 min 表 5(c). Silox VapoxIII 濕蝕刻參數 浸泡溶液 浸泡時間Silox VapoxIII : DI water (1:4) 10min DI water 5min

上述表格為經過多次實驗之後,所得到較佳的蝕刻參數。濕蝕刻過後之晶片, 都要都要先泡 DI water 清洗,再泡 IPA,利用 IPA 的疏水性避免懸浮結構吸附在 下電極,導致元件失效。

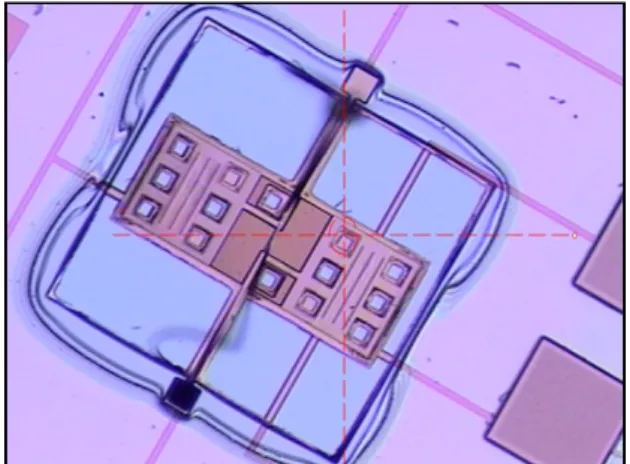

依照先前所提到的製程步驟和蝕刻參數,得到以下的實驗結果,和先前製程 步驟唯一不同的地方是,將二氧化矽蝕刻液 BOE 換成 Silox VapoxIII,來改善二 氧化矽和鋁的蝕刻選擇比問題。 下面將分別介紹做完每步製程步驟後所拍之 OM 圖。 圖 13. FHD-5 濕蝕刻後 OM 圖 上圖為進行完鋁濕蝕刻,周圍的地方都還留有 TiN,尚未除去,故不是透明 的,看不到下方 metal-1 之導線。 圖 14. 鋁濕蝕刻後晶片 EDS 分析圖

圖 15. RIE 後邏輯閘之 OM 圖

圖 16. RIE 後 testkey 之 OM 圖

透過所設計的 testkey 得知,TiN 確實有被蝕刻,testkey 將會在稍後作介紹。

電性測試

到此元件即完成所有的製程步驟,接下來進行電性測試。 為了確認下電極能否順利傳導電性,於是做了以下測試: 1.將製程完成的晶片,用探針將懸浮結構挑掉或是利用膠帶黏住上電極,將 其撕掉。(或者利用因為蝕刻太久,導致上電極漂走的元件。) 2.如此一來,下電極原本被遮蔽的 TiN 即露出。 3.利用三用電表+探針座+探針的組合,將探針下到圖中所標示的 1 和 2,即 可確定電訊號能否順利傳導。 圖 18. 邏輯閘去掉上電極示意圖 藉由這個測試,可以確定下電極的部分,其電性可順利的從結構導通到所連 接的 Pad 上。也證實了所使用的 TiN 是具有導電性的。完整結構的晶片測試:

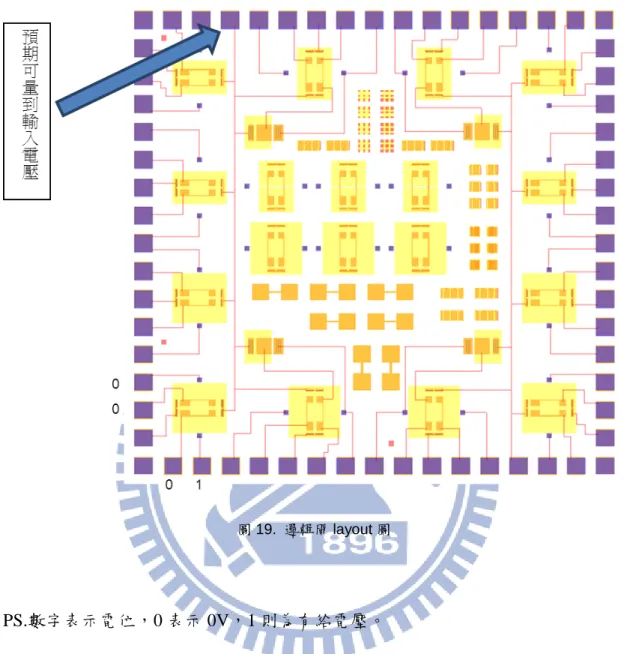

圖 19. 邏輯閘 layout 圖

PS.數字表示電位,0 表示 0V,1 則為有給電壓。

圖 19 為 layout 圖(結構包含 metal-1, metal-2),在各個電極所對應的 bonding pad 給電壓,即可測試邏輯閘是否順利作動、是否有邏輯功能。

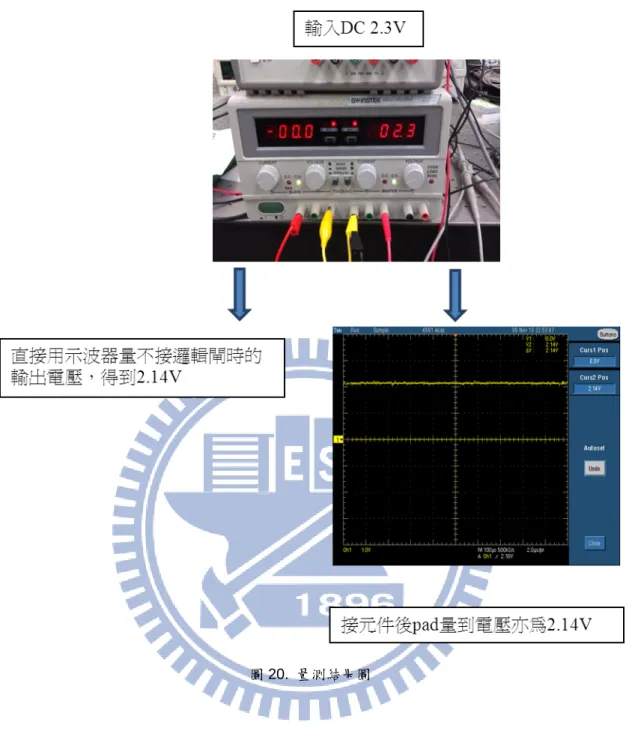

圖 20. 量測結果圖

但是實際上,即使輸入電壓給 0.1V,示波器上仍可以量到 0.1V,表示並不 是因為邏輯閘作動而導通,可能是有地方短路所造成的。

推測原因: 圖 21. 蝕刻孔圖 圖 22. 邏輯閘側視圖 由圖 21 可看出,標示出來的地方沒有蝕刻孔,表示此處鋁蝕刻液比較不容 易到達,因此推測此處鋁沒有蝕刻乾淨(即圖 22 綠色標示部分),尚有 metal-2 金 屬鋁殘留,而導致上電極的電壓因為短路傳到下電極而傳出去,並不是因為邏輯 閘作動而順利傳送電壓。

第五章

新尺寸設計

5.1 設計目的

為了改善先前短路的問題,增加四個蝕刻孔,以確保 metal-2 被蝕刻完全。 另外將懸臂樑式的彈簧,改成 serpentine spring 的形式,欲達到驅動電壓 5V 的目 標且節省佈局面積,最後,設計四種 testkey 來檢視製程步驟是否成功,也可以 得到蝕刻液的側向蝕刻率。5.2 雙層介電質靜電力公式推導

圖 23. 雙層介電質示意圖 為了要計算出所設計之邏輯閘尺寸在 5V 驅動下是否能如預期作動,所以做 了下列推導[14],此數學模型和一般靜電力公式不同的地方有兩點,第一點為平 行電容板中間之介電層並非只有空氣,還包含二氧化矽層,第二點就是不同平行 電容板位置有不同的靜電力、靜電力矩,將其列入考慮,才能計算出在特定位置 之靜電力、靜電力矩是否達到要求。 根據作動原理,為了要得到在特定驅動電壓下平板旋轉角度與靜電力矩的關 係,做了以下之推導: 根據平行電容板公式 𝑪 = 𝜺 ∗𝑨𝒅 (5.1) A為上下平板垂直投影重疊面積。 d為上下平板間距。 再根據電容串聯公式 𝑪 = 𝑪𝟏∗𝑪𝟐 𝑪𝟏+𝑪𝟐 (5.2)所以 𝒅𝑪𝟏 = 𝜺𝟏∗𝒅𝑨𝒉 = 𝒉𝜺𝟏𝟏−𝒙∗𝒔𝒊𝒏𝜽∗𝒘∗𝒅𝒙 =𝜺𝒉𝟏𝟏∗𝒘∗𝒅𝒙−𝒙∗𝜽 (5.3) 𝒅𝑪𝟐= 𝜺𝟐∗𝒅𝑨𝒉 =𝜺𝟐∗𝒘∗𝒅𝒙𝒉𝟐 (5.4) 串聯之後得到[15] 𝒅𝑪 = 𝜺𝟐∗𝒘∗𝒅𝒙 𝒉𝟐+𝜺𝟐𝜺𝟏∗(𝒉𝟏−𝒙∗𝜽) (5.5) 儲存在平行電容板的能量為 𝒅𝑼 =𝟏𝟐∗ 𝑽𝟐∗ 𝒅𝑪 =𝟏 𝟐∗ 𝑽𝟐∗ 𝜺𝟐∗𝒘∗𝒅𝒙 𝒉𝟐+𝜺𝟐𝜺𝟏∗(𝒉𝟏−𝒙∗𝜽) (5.6) 電極所受的力表示為 𝒅𝑭 =𝒅𝑼𝒅𝒙 =𝟏𝟐∗ 𝑽𝟐∗ 𝜺𝟐∗𝒘∗𝒅𝒙 [𝒉𝟐+𝜺𝟐𝜺𝟏∗(𝒉𝟏−𝒙∗𝜽)]𝟐 (5.7) 所以可以得到力矩為 𝑴 = ∫ 𝒙 ∗ 𝒅𝑭 =𝟏𝟐∗ 𝑽𝟐∗ ∫ 𝜺𝟐∗𝒘∗𝒙∗𝒅𝒙 [𝒉𝟐+𝜺𝟐𝜺𝟏∗(𝒉𝟏−𝒙∗𝜽)]𝟐 𝑩 𝑨 𝑩 𝑨 (5.8) 此 A、B 為距離平板中心之長度,如示意圖上所標, 經過變數變換 𝑴 = � 𝒙 ∗ 𝒅𝑭 =𝟏𝟐 ∗ 𝑽𝟐∗ � 𝜺𝟐∗ 𝒘 ∗ 𝒙 ∗ 𝒅𝒙 [𝒉𝟐+ 𝜺𝜺𝟐𝟏∗ (𝒉𝟏− 𝒙 ∗ 𝜽)]𝟐 𝑩 𝑨 𝑩 𝑨 =𝟏𝟐 ∗ 𝑽𝟐∗ � 𝒄 ∗ 𝒙 (𝒅 − 𝒆 ∗ 𝒙)𝟐 𝑩 𝑨 𝒅𝒙

=𝟏𝟐 ∗ 𝑽𝟐∗ 𝒄 ∗ � 𝒙 (𝒅 − 𝒆 ∗ 𝒙)𝟐 𝑩 𝑨 𝒅𝒙 = 𝟏𝟐 ∗ 𝑽𝟐∗ 𝒄 ∗−𝟏 𝒆 ∗ � −𝒆 ∗ 𝒙 (𝒅 − 𝒆 ∗ 𝒙)𝟐 𝑩 𝑨 𝒅𝒙 = 𝟏 𝟐 ∗ 𝑽𝟐∗ 𝒄 ∗ −𝟏 𝒆 ∗ � ( 𝒅 − 𝒆 ∗ 𝒙 (𝒅 − 𝒆 ∗ 𝒙)𝟐 𝑩 𝑨 − 𝒅 (𝒅 − 𝒆 ∗ 𝒙)𝟐)𝒅𝒙 =𝟏𝟐 ∗ 𝑽𝟐∗ 𝒄 ∗−𝟏 𝒆 ∗ � ( 𝟏 (𝒅 − 𝒆 ∗ 𝒙) 𝑩 𝑨 − 𝒅 (𝒅 − 𝒆 ∗ 𝒙)𝟐)𝒅𝒙 = 𝟏𝟐 ∗ 𝑽𝟐∗ [𝒄 𝒆𝟐∗ 𝒍𝒏(𝒅 − 𝒆 ∗ 𝒙) + 𝒄 ∗ 𝒅 𝒆 ∗ 𝟏 𝒆 ∗ (𝒅 − 𝒆 ∗ 𝒙)] 𝑩 𝑨 最後得到力矩為 𝐌 =𝐕𝟐∗𝛆𝟐∗𝐰∗�𝐡𝟐+ 𝛆𝟐 𝛆𝟏∗𝐡𝟏� 𝟐∗𝛆𝟐𝛆𝟏∗𝛉 ∗ 𝐁−𝐀 �𝐡𝟐+𝛆𝟐𝛆𝟏∗𝐡𝟏−𝛆𝟐𝛆𝟏∗𝛉∗𝐀�∗(𝐡𝟐+𝛆𝟐𝛆𝟏∗𝐡𝟏−𝛆𝟐𝛆𝟏∗𝛉∗𝐁) + 𝛆𝟐∗𝐰∗𝐕𝟐 𝟐∗�𝛆𝟐𝛆𝟏∗𝛉�𝟐∗ 𝐥𝐧 𝐡𝟐+𝛆𝟐𝛆𝟏∗𝐡𝟏−𝛆𝟐𝛆𝟏∗𝛉∗𝐁 𝐡𝟐+𝛆𝟐𝛆𝟏∗𝐡𝟏−𝛆𝟐𝛆𝟏∗𝛉∗𝐀 (5.9) 有了此數學模型,便可以在 matlab 中作圖,當電壓固定時,便可以得到𝐌– 𝛉 的關係圖,意思就是說,當給定一個電壓時,可以知道上電極平板要旋轉到某個 特定角度,需要多少力矩。比較上電極平板所受力矩和支撐彈簧的回復力矩,就 可以得知邏輯閘是否成功作動。

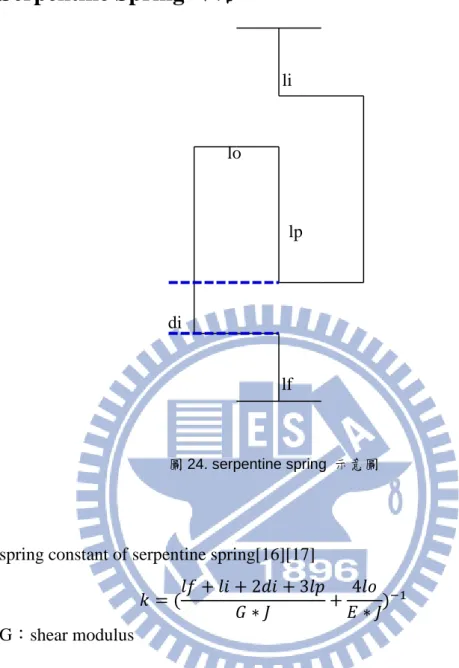

5.3 Serpentine Spring 介紹

圖 24. serpentine spring 示意圖

spring constant of serpentine spring[16][17]

(5.10) G:shear modulus

J:polar moments of inertia with respect to the beam E:Young’s modulus 懸臂樑的 torsional stiffness 跟其尺寸有關係(越細、越薄、越長其 k 值都越小), 由於在製程中的厚度被限制住了,能改變的只有寬度和長度,若要達到 5V 驅動 電壓所需的 k 值,懸臂樑會很長,所以採用 serpentine spring 的彈簧,他的優點 是能在不改變厚度的情況下,增加其組數來降低 k 值,也可以減小佈局面積,但 是必須注意的是,若是使用太多組,會造成過長而導致其他方向彎曲。 li lf lp lo di 𝑘 = (𝑙𝑓 + 𝑙𝑖 + 2𝑑𝑖 + 3𝑙𝑝𝐺 ∗ 𝐽 +𝐸 ∗ 𝐽)4𝑙𝑜 −1

5.4 彈簧尺寸

圖 25. 彈簧示意圖 圖 26. 彈簧側視圖 圖 25 為彈簧上視圖,它標示了各分段的長度,圖 26 則為彈簧的剖面圖,根 據先前提到的式子(5.10)的公式,再利用先前導出的數學模型得到k = 6.5 ∗ 10−10, 由於邏輯閘是由兩個 serpentine spring 支撐,所以總共的 k 為1.3 ∗ 10−9。值得一 提的是,由於製程步驟會進行二氧化矽濕蝕刻,為了確保蝕刻後之彈簧寬度為 5um,所以設計 Metal-3 和下方的鎢為二氧化矽之蝕刻終點。開關黏附現象之探討

開關使用低扭轉剛度之彈簧,可能會產生黏附現象,根據 Jack Yaung 之文獻 [18],他提出三種造成接觸金屬黏附的力(毛細力、凡德瓦力、氫鍵力),我們則 著重於凡德瓦力的計算,雖然無法精準的確定本設計邏輯閘之接觸面積大小為何, 但是經粗算後,凡德瓦力所產生的力矩和彈簧的回覆力矩差個 4 個 order,表示 凡德瓦力產生的影響很微小。計算式如下: Fv = 𝐻∗𝐴𝑐 6∗π∗𝑑3∗ 𝑧0 (𝑑+𝑧0) (5.11) H:Hamaker constant AC:contact aread:distance between two surfaces Z0:20nm 本設計之 TiN 之 H 為 15.73*10-20, AC 為(5*10-6)*(90*10-6) ,d 為 0.4*10-6 , 計 算 後 可 得 所 產 生 之 凡 德 瓦 力 Fv=2.93*10-12 N , 產 生 之 力 矩 =F*125*10-6=3.66*10-16N*m 和平板旋轉 0.4um 之回復力=4.68*10-12N*m 相比差 了 4 個 order,所以不會產生黏附現象。

5.5 模擬結果

彈簧 X、Y、Z 方向位移:

此設計之彈簧,欲作動之狀態為旋轉,不希望其在 X、Y 和 Z 方向有彎曲, 所以模擬了在三種給電壓情況下,彈簧 X、Y、Z 方向之彎曲。 為了避免彈簧 X、Y、Z 方向彎曲量過大,所以作了以下模擬。 在不同的給電壓狀態下模擬彈簧各方向之最大位移量。Type I 為 Vcc+給 5V,Vcc-給 0V,A、B 皆為 0V 的情況 Type II 為 Vcc+給 5V,Vcc-給 0V,A 給 5V,B 給 0V 的情況 Type III 為 Vcc+給 5V,Vcc-給 0V,A、B 皆為 5V 的情況

由表 6 可得知,彈簧受到靜電力時各方向之彎曲量皆很小,不會影響其旋轉 作動,需要特別注意的是彈簧的 Y 方向變形量,用以確保上電極平板不會因為 彈簧 Y 方向的彎曲大於上下電極間隙,因而碰觸到下電極,導致短路的情形發 生。 圖 27. 電極配置示意圖 表 6. 彈簧受靜電力時各方向之最大彎曲量 X 方向 Y 方向 Z 方向 Type I 0.012571 0.1047 0.001815 Type II 0.004251 0.0718 0.001249 Type III 0.004378 0.0490 0.000826 單位:um

討論平板旋轉所造成平板末端 Y 方向位移:

由圖 28、29、30 得知,在特定一組電壓的狀態下,上電極平板的 Y 方向位 移皆大於 0.4um,表示上電極可以順利的接觸到下電極而將電壓傳輸出去。 TypeI 為上電極左邊給 5V、右邊給 0V,下電極皆為 0V 的情況。 圖 28. ANSYS 模擬平板 Y 方向位移量圖(I) TypeII 則為上電極左邊給 5V、右邊給 0V,下電極皆為上面給 5V、下面給 0V 的情況。 圖 29. ANSYS 模擬平板 Y 方向位移量圖(II)TypeIII 則為上電極左邊給 5V、右邊給 0V,下電極皆為 5V 的情況。 圖 30. ANSYS 模擬平板 Y 方向位移量圖(III) 將上述設計的彈簧和平板畫入 ANSYS 中,固定兩彈簧末端,找到我們要的 振動模態(1st mode),得到共振頻率:11413.1Hz,此邏輯閘之操作頻率,必須低 於第一共振模態,避免上電極平板尚未接觸到下電極就被拉回。也要避免操作在 其他模態之共振頻率上(我們所要的振型為第一模態,故沒有此問題)。 圖 31. 新設計共振頻率圖(第一模態)

第二模態之共振頻率為 37279.7Hz。 圖 32. 新設計共振頻率圖(第二模態) 圖 33. M-Ɵ 關係圖(樑寬=5um) 在驅動電壓 5V 的條件下,上電極由於受到靜電力產生的力矩而轉動,圖 33、 34 為 moment-theta 圖,在三種給電壓的情況下,平板所受的力矩和旋轉角度的 黑色: (A,B)=(5V,5V) 紅色: (A,B)=(0V,0V) 綠色: (A,B)=(5V,0V) or (0V,5V) 藍色:彈簧彈性力矩

關係圖,由圖可知,在我們設定的移動範圍內(3.2 ∗ 10−3 rad),彈簧的回復力矩 皆小於上電極平板所受力矩,表示平板可以順利旋轉直到接觸下電極,電訊號因 此可以順利傳導出去。 圖 34. 平板旋轉示意圖 詳細來看,以圖 34 為例,Vcc+=5V,Vcc-=0V,分成三個下電極狀態(靜電扭 矩為正,平板順時針旋轉,靜電扭矩為負,平板逆時針旋轉;彈簧回復力矩為正, 平板逆時針旋轉,彈簧回復力矩為負,平板順時針旋轉): 1. 下電極電壓為(A,B)=(5V,5V)時,當平板在-4*10-3rad 時所受之靜電扭 矩為正(順)且彈簧回復扭矩為負(順),故平板會朝順時針方向旋轉, 當旋轉角度大於 0 時,靜電扭矩(順)為正且大於彈簧回復扭矩(逆), 所以平板會順時針旋轉直至碰到下電極。 2. 下電極電壓為(A,B)=(0V,0V)時,當平板在 4*10-3rad 時所受之靜電扭 矩為負(逆)且彈簧回復扭矩為正(逆),故平板會朝逆時針方向旋轉, 當旋轉角度小於 0 時,靜電扭矩為負(逆)且其值大於彈簧回復力矩 (順),所以平板會逆時針旋轉直至碰到下電極。 3. 下電極電壓為(A,B)=(5V,0V) or (0V,5V)時,當平板在-4*10-3rad 時所 受之靜電扭矩約為 0(X),彈簧回復扭矩為負(順),故平板會朝順時 針方向旋轉,當旋轉角度大於 0 時,靜電扭矩(順)大於彈簧回復力 矩(逆),所以平板會順時針旋轉直至碰到下電極。

5.6 元件設計

Testkey

針對每步製程步驟,設計一組 testkey 用以確保製程結果無誤。鋁(Metal-2)蝕刻速率 testkey:

設計了 5,10,15,20,25,30,35,40,45,50um 的蝕刻距離(雙向蝕刻),新設計邏輯 閘的兩蝕刻孔間距為 30um。 設計目的:除了可以確認 Metal-2 有沒有蝕刻乾淨之外,經由不同尺寸的 testkey,也可以得到鋁的側蝕速率。 圖 35. 鋁(Metal-2)蝕刻速率 testkeyTiN 蝕刻 testkey:

設計目的:做完 HDP-RIE 後,確認 TiN 有無確實被蝕刻掉。

圖 36. TiN 蝕刻 testkey

SiO2 蝕刻速率 testkey:

設計了 0.5,1,2,3um 的蝕刻距離(雙向蝕刻),新設計邏輯閘的兩 Metal-2 中間 oxide 尺寸為 1um 和 2um。

設計目的:用來量測 SiO2 的側蝕速率,藉以得知實際上蝕刻了幾 um 的 SiO2, 除 了 確 定 邏 輯 閘 是 否 有 懸 浮 之 外 , 也 避 免 過 蝕 而 影 響 懸 臂 樑 的 torsional Stiffness。

圖 37. SiO2 蝕刻速率 testkey

TiN 導電性 testkey:

設計目的:此結構等同 TiN 的 testkey,用來測試 TiN 的導電性,元件這麼大 的原因是為了方便探針接觸。

P.S 製程做完 FHD-5 濕蝕刻、HDP-RIE 之前就要量測。否則下一步 HDP-RIE 就會將 TiN 蝕刻掉。

圖 38. TiN 導電性 testkey

結構設計:

1.oxide 寬度設計

圖 39. Oxide 寬度示意圖

Metal-2 中間絕緣的 oxide,設計成兩種尺寸,分別為 1um 和 2um。

設計目的:因為先前的設計有短路的問題,所以設計兩種不同寬度來確保左 右電極絕緣。

2.bonding pad 結構設計

設計目的:先前之 bonding pad(包含 Metal-1,2,3)已確定可以導通,但是將 bonding pad 簡化成 Metal-1,不僅僅可以使設計更為精簡,也能降低電路的電阻。 a. bonding pad(包含 Metal-1,2,3)

圖 40(a). 製程流程(M1,2,3)-1

圖 40(c). 製程流程(M1,2,3)-3

b. bonding pad(Metal-1)

圖 41(a). 製程流程(M1)-1

圖 41(c). 製程流程(M1)-3

5.7 layout 圖

圖 42. 新設計 Layout 圖

紅色範圍:鋁蝕刻 testkey 藍色範圍:SiO2 蝕刻 testkey 綠色範圍:TiN 蝕刻 testkey

棕色範圍:TiN 導通 testkey(用來下探針確保 TiN 能導電,所以設計的比較 大)

第六章 結論與未來方向

6.1 結論

由電性實驗結果得知,經由本論文所採用之製程和蝕刻參數製作,用來作為 接觸金屬之 TiN 薄膜有留下,且具有導電性。 本論文藉由推導雙層介電質之靜電力矩,將數學模型導入 matlab 模擬上電 極平板施力矩和懸臂樑回復力矩的關係,設計出一個 K=6.5*10-10 N*m/rad 之彈簧, 藉由低扭轉剛度和 1.6um 的上下電極間距,來達到 5V 驅動之目標。 將所設計的邏輯閘藉由套裝軟體 ANSYS 模擬得到其共振頻率為 11413.1Hz、 平板旋轉時的 Y 方向位移最小量 0.7421um(大於 gap=0.4um)、受到靜電力時上 電極平板 Y 方向的最大彎曲量 0.1047um(小於 gap=0.4um),藉以確定邏輯閘具有 NAND、NOR 閘功能,可以順利作動。本論文設計之邏輯閘尺寸約 250µm x 230µm, 輸入/輸出訊號 (0V, 5V)。目前已完成相關的設計、數值模擬、元件佈局。6.2 未來方向

1. ANSYS 模擬的部分,限制平板的位移,並以暫態分析模擬其作動。 2.完成邏輯閘之後製程,量測其特性是否符合當初所設計。 3.將 testkey 之蝕刻寬度對應蝕刻時間,可得到蝕刻液之蝕刻速率圖。參考文獻

[1] S. W. Lee, R. Johnstone, and A. M. Parameswaran, “MEMS mechanical logic units: design and fabrication with micragem and polymumps," in Electrical and Computer Engineering, 2005. Canadian Conference on, 2005, pp. 1513-1516. [2] A. Hirata, K. Machida, H. Kyuragi, and M. Maeda, "A electrostatic

micromechanical switch for logic operation in multichip modules on Si," Sensors and Actuators A: Physical, vol. 80, no. 2, pp. 119-125, 2000.

[3] R. Nathanael, V. Pott, Hei Kam, Jaeseok Jeon, E. Alon, and T.-J. K. Liu,"Four-Terminal-Relay Body-Biasing Schemes for Complementary Logic Circuits,"IEEE Electron Device Letters, vol. 31, no. 8, pp. 890-892, Aug. 2010. [4] J. Jeon, V. Pott, H. Kam, R. Nathanael, E. Alon, and T.-J. King Liu, “Seesaw

Relay Logic and Memory Circuits,” Journal of Microelectromechanical Systems, vol. 19, no. 4, pp. 1012-1014, Aug. 2010.

[5] A. Tazzoli, V. Peretti, R. Gaddi, A. Gnudi, E. Zanoni, G. Meneghesso, “ RELIABILITY ISSUES IN RF-MEMS SWITCHES SUBMITTED TO CYCLING AND ESD TEST," IEEE 06CH37728 44th Annual International Reliability Physics Symposium, San Jose, 2006.

[6] H. Kam, V. Pott, R. Nathanael, J. Jeon, E. Alon, and T. J. K. Liu, ”Design and reliability of a micro-relay technology for zero-standby-power digital logic applications,” in Electron Devices Meeting (IEDM), 2009 IEEE International, 2009, pp. 1-4.

[7] Qing Ma, Quan Tran, Tsung-Kuan A. Chou, John Heck, Hanan Bar, Rishi Kant and Valluri Rao Intel Corporation, Santa Clara, CA 95054, "Metal contact reliability of RF MEMS switches."

[8] Chun-Yin Tsai, 2011, "Design, Fabricate, and Test CMOS Process-Compatible MEMS Logic Gates" PhD dissertation.

[9] K. Lal, A.K. Meikap, S.K. Chattopadhyay, S.K. Chatterjee, M. Ghosh, K. Baba, R. Hatada, "Electrical resistivity of titanium nitride thin films prepared by ion beam-assisted deposition", Physica B 307 (2001) 150–157.

[10] 許中勇, "利用殘餘應力研製 CMOS 製程相容之射頻微型開關." 國立台北科 技大學碩士論文,2006。

[11] Ching-Liang Dai, "A maskless wet etching silicon dioxide post-CMOS process and its application", Microelectronic Engineering 83 (2006) 2543–2550.

[12] ROY R. CRAIG, JR., "MECHANICS OF MATERIALS, Second Edition," JOHN WILEY & SONS, INC.

[13] 吳承懋, "利用 CMOS-MEMS 與化鎳浸金技術製作 MEMS 邏輯閘", 碩士論 文, 2013.

[14] Wei-Ting Kuo, "MEMS Logic Gate," masters dissertation,2005.

[15] S. Boisseau, G. Despesse and B. Ahmed Seddik,“Electrostatic Conversion for Vibration Energy Harvesting," Ch5.

[16] J. You, M. Packirisamy and I. Stiharu, "Modeling of Torsional Micromirrors with springs made of Multiple Rotational Serpentine Elements", NSTI-Nanotech 2006, Vol. 3, 2006.

[17] Bai Y H, Yeow J T W, Constantinou P, Damaskinos S and Wilson B C 2010 A 2-D micromachined SOI MEMS mirror with sidewall electrodes for biomedical imaging IEEE/ASME Trans. Mechatronics 15 501–10.

[18] Jack Yaung, “NEM Relay Scaling for Ultra-low Power Digital Logic”, Electrical Engineering and Computer Sciences University of California at Berkeley, Technical Report No. UCB/EECS-2014-90.

![圖 3. Hirata 等人所提出的微機械邏輯閘 表 1. 不同驅動電極和支撐樑之尺寸 圖 3 為 Hirata 等人所設計的微機械邏輯閘[2],由兩個固定驅動電極、兩個 固定接觸電極、兩個可移動式驅動電極和一個可移動式接觸電極組成,在 S3 條 件下,需要左右電極都給驅動電壓 30V,開關才有電壓輸出,此即為 AND 閘, 在 S5 條件下,只需要有一邊驅動電壓為 30V,開關就有電壓輸出,此即為 OR 閘,此微機械邏輯閘利用兩組不同面積大小的驅動電極,來達到 AND 閘或 OR 閘的邏輯功能(並](https://thumb-ap.123doks.com/thumbv2/9libinfo/8235893.171159/14.892.246.635.226.745/和一個可移動式需要電極都給驅動電壓V開關有一邊驅動電兩組不同.webp)

![圖 4. Rhesa, Nathanael 等人所提出平板式微機械開關結構 Rhesa, Nathanael 等人提出平板式微機械開關的結構設計[3],和先前研究的 不同點在於,他增加了一組 body 的電極,用來控制開關。在”開”狀態時,因為 body 和 gate 之間的靜電力,導致開關導通。 圖 5](https://thumb-ap.123doks.com/thumbv2/9libinfo/8235893.171159/15.892.148.749.118.355/先前研究不同點在於他增加了一組電極用來時因和之間靜電力導.webp)

![圖 6. 鎢受到 BOE 蝕刻之 SEM 圖 本實驗室先前之研究[8]是用鎢(tungsten)當作接觸金屬,但是由於金屬鈦蝕 刻液也會蝕刻鎢,導致接觸金屬被破壞,無法導通。 表 3](https://thumb-ap.123doks.com/thumbv2/9libinfo/8235893.171159/17.892.151.748.105.346/鎢受到本實驗當作接觸金屬但是由於金屬鈦蝕刻液也會致接觸金屬被.webp)