電子工程學系 電子研究所碩士班

碩 士 論 文

1.8V、10 位元、每秒 100 百萬次取樣 CMOS

導管式類比數位轉換器

A 1.8V 10-Bit 100MS/s CMOS Pipeline

Analog-to-Digital Converter

研 究 生:張家華

指導教授:陳巍仁

1.8V 、10 位元、每秒 100 百萬次取樣 CMOS

導管式類比數位轉換器

A 1.8V 10-Bit 100MS/s CMOS Pipeline

Analog-to-Digital Converter

研 究 生: 張家華 Student:Chia-Hua Chang

指導教授: 陳巍仁 Adviser:Wei-Zen Chen

國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

A Thesis

Submitted to Department of Electronics Engineering

College of Electrical Engineering and Computer Science

National Chiao-Tung University in partial Fulfillment of

the Requirements for the Degree of

Master of Science

in

Electrical Engineering

October 2004

Hsin-Chu, Taiwan, Republic of China

1.8V、10 位元、每秒 100 百萬次取樣 CMOS

導管式類比數位轉換器

學生:張家華 指導教授:陳巍仁

國立交通大學電子工程學系 電子研究所碩士班

摘要

隨著製程技術的進步,超大型積體電路系統可以用更小的晶片面積達到更高 的運算速度。在現行的通訊系統中,訊號將先透過一個類比數位轉換器將接收到 的類比訊號量化,以供後級的數位電路執行更複雜的訊號處理;為提昇整體系統 之性能,類比數位轉換器往往和龐大的數位訊號處理系統整合在單一顆晶片上。 伴隨著電晶體尺寸的縮小,系統晶片的供應電壓也隨之下降。因此,低電壓類比 數位轉換器將伴演愈形重要的角色。 本論文中的主要目標為設計一個操作在 1.8V DC 之下、10 位元、每秒 100 百萬次取樣導管式類比數位轉換器。其採用每級 1.5-bit 解析度的架構,以提高 整體類比數位轉換器的運算速度。同時結合數位校正技術以增加比較器的偏移電 壓容忍度,而不須要前級預先放大器,進而節省功率的耗費。在取樣並保持電路 的設計上,其採用翻轉迴授(Flip-Around)架構,使得電路在保持模式時可具有最 大的回授因子,減小運算放大器所須的頻寬需求及功率消耗;此外,為了因應低 電源電壓的操作,本設計利用升壓技術(bootstrapping technique)以控制前級取樣 開關,進而減低因低電壓操作時對取樣保持電路線性度的影響。 整個類比數位轉換器原型晶片以 TSMC 0.18µm CMOS 製程製作,晶片面積 為 3.2mm2;當輸入為 2.0V pp的差動訊號且在 100MHz 的轉換速度(conversion rate) 之下,此類比數位轉換器達到 65dB 訊號雜訊動態範圍(SNDR),微分型非線性誤 差(DNL)和積分型非線性誤差(INL)皆小於 0.2LSB,其電源供應為 1.8V 的單電 壓,功率消耗為 88mW。A 1.8V 10-Bit 100MS/s CMOS Pipeline

Analog-to-Digital Converter

Student:Chia-Hua Chang Adviser:Wei-Zen Chen

Department of Electronics Engineering

National Chiao-Tung University

Abstract

The rapid developments of IC technology have made it possible to realize a VLSI system chip with higher operating speed in a smaller feature size. In a modern communication system, input signal is quantized by an analog-to-digital data converter for the following complicated signal-processing in the digital domain. In the current IC design trend, analog to digital data converters and the sophisticated digital circuits are integrated on a single chip for higher performance. As the operating voltage is scaled down along with the shrinkage of device size, a low voltage ADC is demanding and would play an important role in the future.

The objective goal of this thesis is to realize an 1.8 V, 10-bit, 100MS/s pipelined analog to digital data converter. An 1.5-bit/stage architecture is adopted for higher operating speed. Cooperating with digital error correcting technique, it tolerates higher comparator’s input offset voltage and no preamplifier is needed, thus lowers the total power dissipation. In addition, a flip-around sample and hold architecture in the front-stage is utilized for a maximum feedback factor, so as to relax OP’s gain-bandwidth requirement and reduce power dissipation. Furthermore, to operate under a supply voltage as low as 1.8 V, voltage bootstrapping technique is adopted for controlling the switches in the front-stage. It can reduce the impacts of linearity degradation due to the limitation of low supply voltage.

The ADC prototype is fabricated in TSMC 0.18µm CMOS process, and it occupies an chip area of 3.2mm2. With an 2.0Vpp differential input signal, the analog-to-digital converter manifests a SNDR up to 65dB at 100 MHz conversion rate. The DNL and INL are both less than 0.2LSB. Operating under a 1.8V supply, total power consumption is 88mW.

誌謝

隨著這本碩士論文的完成,我在交大兩年的研究生生涯也將告一段落;非常 感謝我的指導教授陳巍仁博士兩年來耐心的教導,讓我能夠順利完成碩士學業。 老師嚴謹的研究態度,深深影響著我,使我在研究的路上獲益良多,而 307 實驗 室更提供了寶貴且完備的軟硬體資源,讓我得以順利的進行研究;感謝國家晶片 設計中心提供先進的半導體製程,使我有機會實現並驗證我所設計的電路。除此 之外,更要感謝吳介琮教授、李泰成教授、黃柏鈞教授擔任我的口試委員,給予 我寶貴的經驗,讓這本論文更加充實。 另一方面,在這兩年的求學途中,感謝所有 307 實驗室的成員,因為有你們 的陪伴與協助,這本論文才得以順利完成。感謝徐建昌博士、李瑞梅、翟芸、黃 鈞正、范啟威、范振麟、廖以義、虞繼堯、王文傑、羅仁鴻、劉嘉俊等學長姐在 課業上的指導與幫助,透過與你們的切磋討論,讓我對電路設計的觀念與方法更 清楚更紮實;感謝郭建良、陳世倫、蘇烜毅學長在生活上的提攜照顧,謝謝你們 給我的鼓勵與支持;感謝王騰毅、曾偉信、邱偉茗、黃洪濤、林大新、甘瑞銘、 李宗霖、黃冠勝諸位同學,和我一起努力奮鬥,我永遠不會忘記你們這群戰友; 也謝謝王志賢學弟在我寫論文時間所給予的協助,謝謝你們! 最後我要致上最深的感謝給我的父母,感謝你們對我一直以來的照顧;感謝 哥哥姐姐們的支持與諒解,我才能專心的求學;還有默默陪伴著我的女友小佩, 感謝妳在我沮喪的時候給我支持與鼓勵。因為你們,才讓我能心無旁鶩的完成學 業,衷心感謝你們對我所付出的一切,僅以此論文獻給你們,希望能與你們一起 分享這份喜悅與光榮。目錄

表目錄

圖目錄

第一章 緒論 1

1.1 研究動機 1

1.2 論文組織 4

第二章 高速類比數位轉換器架構 5

2.1 類比數位轉換器基本原理 5

2.2 類比數位轉換器架構介紹與比較 9

第三章 取樣並保持電路設計 14

3.1 簡介 15

3.2 取樣並保持電路基本原理 15

3.3 取樣並保持電架構介紹與比較 19

3.4 取樣並保持電路設計 26

3.4.1 取樣網路分析與設計 30

3.4.2 開關增壓技術 30

3.4.3 運算放大器 34

3.4.4 共模迴授電路 38

3.4.5 時脈產生器 40

3.5 取樣並保持電路製作 41

3.5.1 電路量測 43

3.5.2 量測結果 45

3.5.3 討論 48

第四章 類比數位轉換器系統與電路設計 50

4.1 數位校正技術 51

4.2 每級 1.5 位元架構 55

4.3 區塊電路設計 56

4.3.1 比較器電路 56

4.3.2 編碼器電路 57

4.3.3 減法器與乘法器電路 58

4.4 類比數位轉換器製作 59

4.4.1 電路佈局 61

4.4.2 電路模擬結果 64

第五章 結論 66

表目錄

表 1.1 SIA 技術趨勢圖………1 表 3.1 閉迴路取樣並保持電路比較………...25 表 3.2 雙級運算放大器模擬………...38 表 3.3 儀器型號與規格………...42 表 3.4 取樣並保持電路效能總結...47 表 4.1 各級運算放大器功率消耗比較………...55 表 4.2 編碼器轉換表………...57 表 4.3 類比數位轉換器效能總結………...65圖目錄

圖1.1 類比數位轉換器應用範疇...2 圖1.2 應用範圍 vs. ADC架構與規...3 圖1.3 ADC架構 vs. 解析度與取樣...3 圖2.1 類比數位轉換器在電路系統中所伴演的角...5 圖2.2 SNR vs. 輸入訊號功率...7 圖2.3 類比數位轉換器非線性度示意圖...8 圖2.4 快閃式類比數位轉換器架構...9 圖2.5 半域轉換類比數位轉換器架構...10 圖2.6 雙步驟類比數位轉換器架構...11 圖2.7 管線化類比數位轉換器架構...12 圖2.8 平行管線化類比數位轉換器架構...13 圖3.1 取樣並保持電路功能圖...15 圖3.2 取樣並保持電路架構圖...16 圖3.3 取樣並保持電路行為示意圖...16 圖3.4 電荷注入效應...17 圖3.5 取樣並保持電路非線性示意圖...18 圖3.6 取樣點非線性...19 圖3.7 開迴路形式取樣並保持電路架構...20 圖3.8 閉迴路形式取樣並保持電路架構...20 圖3.9 (a) Type 1取樣並保持電路 (b) 取樣模式 (c) 保持模式...21 圖3.10 (a) Type 2取樣並保持電路 (b) 取樣模式 (c) 保持模式...22 圖3.11 (a) Type 3取樣並保持電路 (b) 取樣模式 (c) 保持模式...24 圖3.12 Flip-Around架構取樣並保持電路...26 圖3.13 (a) 量化器轉移特性曲線 (b) 量化誤差示意圖...27 圖3.14 RC電路熱雜訊示意圖...28 圖3.15 解析度和SNR vs. 取樣電容關係圖...29 圖3.16 取樣網路示意圖...30 圖3.17 電晶體開關電導係數與輸入電壓間的關係圖...31 圖3.18 電晶體導通阻抗對輸入輸出訊號所造成的影響…...32 圖3.19 開關增壓電路...33 圖3.20 開關增壓電路模擬...33 圖3.21 摺疊堆積式與望遠鏡式運算放大器...36 圖3.22 雙級(Two-Stage)運算放大器...37圖3.23 雙級運算放大器模擬...37 圖3.24 連續時間型共模迴授電路...38 圖3.25 動態式共模迴授電路...39 圖3.26 時脈產生器...40 圖3.27 時脈產生器波形...40 圖3.28 底板取樣技術...41 圖3.29 量測印刷電路板圖...42 圖3.30 取樣並保持電路晶片圖(1087µm X 910µm)...43 圖3.31 量測印刷電路板圖...44 圖3.32 量測環境照相圖...44 圖3.33 輸入訊號頻率2MHz、取樣頻率100MHz,時域量測圖...45 圖3.34 輸入訊號頻率2MHz、取樣頻率100MHz,頻域量測圖...45 圖3.35 輸入訊號頻率50.038MHz、取樣頻率100MHz,頻域量測圖...46 圖3.36 SFDR量測值 vs. 輸入訊號頻率 @ 100MHz取樣頻率,1.8Vp-p... 46 圖3.37 考量磅線電感影響的佈局後模擬圖...48 圖3.38. 利用Hspice模擬實際量測情形...49 圖4.1 每級2-bit ADC 輸入對輸出的轉換曲線…...51 圖4.2 比較器抵補電壓造成輸出溢位...51 圖4.3 放大器抵補電壓造成輸出溢位...52 圖4.4 放大器增益誤差造成輸出溢位...52 圖4.5 修正過後的轉換曲線圖...53 圖4.6 每級1.5位元轉換曲線圖…...53 圖4.7 數位校正電路架構圖...54 圖4.8 每級1.5位元管線式類以數位轉換器...55 圖4.9 比較器電路圖...56 圖4.10 編碼器電路圖...57 圖4.11 減法器與乘法器電路圖...58 圖4.12 電容不匹配 vs. 類比數位轉換器線性度...59 圖4.13 類比數位轉換器佈局圖...60 圖4.14 類比數位轉換器佈局方塊圖...61 圖4.15 MDAC時域分析圖...61 圖4.16 ADC時域分析圖...62

圖4.17 ADC佈局後模擬圖(fin=1MHz Sinusoidal Wave,fs=100MHz,Vp-p=1.5V) ...62

圖4.18 ADC佈局後模擬圖(fin=49MHz Sinusoidal Wave,fs=100MHz, Vp-p=1.5V)...63

圖4.20 ADC SNDR vs. Input Frequency @ 75°C...64 圖4.21 ADC DNL 佈局後模擬(Code Density=20,Input

Range=-0.75Vref~0.75Vref)...64 圖4.22 ADC INL 佈局後模擬(Code Density=20,Input

第一章

緒論

1.1 相關研究發展現況與研究動機

在現今十倍速的時代,隨著極大型積體電路的製程不斷地向下縮小尺寸,單 位晶片面積所含的電晶體數目也跟著不斷的遽增;電路設計可以達到高速、低功 率消耗以及低成本等優點。其中極大型積體電路快速發展並大幅增加電路系統中 數位運算和訊號處理的能力,加上數位電路的高精確度以及相較於類比電路較不 易受到雜訊、操作電壓和製程等變動的影響等優點,使其在電路積體化的過程中 伴演主要的角色,在整體電路系統中所占的比重也有越來越多的驅勢(表 1.1)。 然而,即使數位電路擁有這麼多的優點,但無論如何最終仍須要和自然環境有溝 通、互動,而在自然環境的訊號都是以類比的型式存在,舉凡高頻的射頻電波; 或較低頻的聲頻訊號,均為連續時間的類比訊號。因此,在類比訊號與數位處理 之間,資料的轉換以及重建性能的優劣便成為影響整個電路系統設計上最重要的 瓶頸。所以,無論是設計多麼完美的類比電路或是數位電路都必須搭配良好的資 料轉換電路才能完全發揮其功能。 表 1.1 SIA 技術趨勢圖除此之外,也由於極大型積體電路的製程不斷地向下縮小尺寸,閘極氧化層 亦不斷地變薄。此時若操作電壓仍維持與尺寸縮小前相同,將會導致垂直和水平 電場過大,前者會造成閘極氧化層可靠度(Reliability)的問題,後者會產生熱載 子效應(Hot Carrier Effect)的問題。所以隨著製程的縮小,電路的操作電壓勢必 也要跟著降低。又因為考慮到漏電流的影響,元件的臨界電壓並沒有等比例的隨 著製成尺寸縮小而下降,這樣對於數位電路而言有著正面的優點,其中最直接的 就是大幅地降低了電路的功率消耗;但是這樣一來卻會使得一向重視電晶體工作 區間的類比電路面臨極大的挑戰。

類 比 數 位 轉 換 器 的 應 用 範 圍 非 常 廣 泛 , 舉 凡 無 線 網 路 系 統 (wireless communication system)、個人行動電話(cellar phone)、數位影音系統(digital video system)、高速數據機(high speed modem)和乙太網路系統(Ethernet system)等(圖 1.1),都屬於類比數位轉換器應用的範疇。

圖 1.1 類比數位轉換器應用範疇

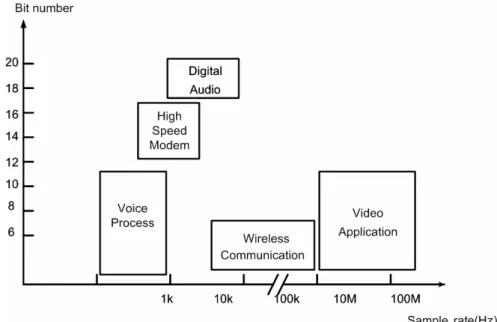

由其應用範圍的不同,造成類比數位轉換器具有各式各樣不同的規格須求, 也因此衍生出許多不同的電路架構,如圖 1.2 所示:

圖 1.2 應用範圍 vs. ADC 架構與規格 以及各種架構的解析度對取樣頻率之分佈圖,如圖 1.3 所示:

圖 1.3 ADC 架構 vs. 解析度與取樣頻率

在本論文中我們主要目標是設計一個操作在 1.8V DC 之下,10 位元、每秒 100 萬次取樣導管式類比數位轉換器。採用每級 1.5-bit 解析度的架構提高整個類

比數位轉換器的運算速度,並結合數位校正技術增加對比較器的偏移電壓容忍 度,使得每一級的比較器有 250mV 的誤差容忍度而不須要前級放大器,節省因 前級放大器所耗費的功率。在取樣並保持電路的設計上是採用 Flip-Around 的架 構來設計,使得電路在保持模式時可以有最大的回授因子,減小運算放大器所須 的功率消耗;為了因應低電源電壓的操作,利用開關升壓技術(bootstrapping technique)減低前端取樣並保持電路因低電壓操作對其線性度的影響。整個類比 數位轉換器原型晶片透過 TSMC 以 0.18µm CMOS 製程製作,佔據 3.2mm2的晶 片面積;當輸出為 2.0Vpp在 100MHz 的轉換速度(conversion rate)之下,此類比 數位轉換器達到 65dB 訊號雜訊動態範圍(SNDR),微分型非線性誤差(DNL)和 積分型非線性誤差(INL)皆小於 0.2LSB,其電源供應為 1.8V 的單電壓消耗 88mW。

1.2 論文組織

本篇論文之內容架構如下: 在論文的第一章中,首先簡述類比數位轉換器之重要性與低電壓設計的必然 趨勢,並對此一類比數位轉換器的研究動機和設計重點做初步的說明。 在論文的第二章中,我們將對傳統的類比數位轉換器架構做一說明並分析其 相關特性以及硬體上的須求度。 在論文的第三章,我們將對類比數位轉換器前端的取樣並保持電路的設計做 詳細的說明,首先概述取樣並保持電路的基本工作原理,並針對幾種不同架構的 取樣並保持電路做分析與比較,接著會介紹我們所採用的 Flip-around 架構的取 樣並保持電路及其附屬電路(開關增壓電路,運算放大器、連續與非連續時間的 共模回授電路和時脈產生器)等電路設計,最後提到針對取樣並保持電路的下線 量測結果。 在論文的第四章中,我們將詳細的介紹本論文所設計的類比數位轉換器。包 含了數位校正機制的考量、類比數位轉換器的附屬電路(比較器、減法器、數位 類比轉換器)設計,並有相對應的模擬結果驗證設計性能。 在論文的第五章中,我們將對這篇論文做個總結,並討論後續的研究與建議。第二章

高速類比數位轉換器架構

本章首先會針對類比數位轉換器的基本操作原理做一個概念式的說明,並詳 細介紹其相關的特性參數及參數定義,透過這些公認的參數來評估類比數位轉換 器的效能,同時對於類比數位轉換器設計的重要關鍵有初步的體認;接著再對幾 種常見的類比數位轉換器架構做初步的分析與比較,進而決定適合本論文所預期 達到目標的電路架構。 2.1 類比數位轉換器基本原理 2.2 類比數位轉換器架構介紹與比較2.1 類比數位轉換器基本原理

近年來隨著積體電路技術的快速發展,數位信號處理技術也日趨成熟;數位 電路的高精確度、低成本、抗雜訊、易儲存等優點,使其成為電路系統中信號處 理的主流,然而在實際應用上由於自然界的信號多以類比信號的形式為主,為了 能夠將自然界的類比訊號利用數位電路來處理,因此,類比數位轉換器儼然成為 關鍵的橋樑角色,如圖 2.1。 圖 2.1 類比數位轉換器在電路系統中所伴演的角色而為了描述類比數位轉換器之特性,我們必須先對於公認且基本的參數有一 定的認識,以便用來界定一個類比數位轉換器的效能,以下將分別對於動態特 性、靜態特性等列舉介紹[1][2]: 動態特性: 解析度(Resolution): 解析度是用來描述類比數位轉換器將類比的輸入訊號量化為數位的輸 出訊號時所能夠轉換的位元數,對於固定的輸入訊號範圍而言,解析度亦可 以代表其所能夠數位化的最小電壓值。 取樣頻率(Sampling Rate): 取樣頻率是用來描述類比數位轉換器每秒可取樣輸入訊號的次數,單位 為赫之(Hz)。透過奈奎斯特(Nyquist)定理可知取樣頻率必須大於最高輸入 頻率的兩倍以上。

輸入訊號範圍(Input Signal Range):

輸入訊號範圍是用來說明類比數位轉換器所能接受輸入端最大的電壓 範圍。因為輸入訊號範圍的大小會決定在類比數位轉換器中的參考電壓值, 所以輸入訊號範圍是必須要有明確規定的。

無寄生動態範圍(Spurious-Free Dynamic Range,SFDR):

SFDR 是指輸出端主訊號功率和最大諧波功率的比值,單位是 dB。 ] [ _ 10 ] [ ( log 20 RMS MAX HD RMS A fin A SFDR=

全諧波失真(Total Harmonic Distortion,THD):

THD 是指輸出端主訊號功率和所有諧波功率總和的比值,單位是 dB。 5 . 0 2 ] [ _ 2 ] [ 3 _ 2 ] [ 2 _ 10 } ... { ] [ ( log 20 RMS N HD RMS HD RMS HD RMS A A A fin A THD + + + = 訊號對雜訊比(Signal-to-Noise Ratio,SNR): SNR 是指輸出端主訊號和所有雜訊(不包含諧波失真)功率的比值,單 位是 dB。

76 . 1 02 . 6 ( log 20 ] [ _ ] [ 10 = + = N A A SNR RMS Noise Total RMS Signal

訊號對雜訊及失真比(Signal-to-Noise and Distortion Ratio,SNDR): SNDR 是指輸出端主訊號功率和所有雜訊功率以及所有諧波功率的比 值,單位是 dB。SNDR 代表雜訊和諧波對於訊號的影響程度,通常也以此 決定等效位元數目。 ] [ _ ] [ _ ] [ 10( log 20 RMS HD Total RMS Noise Total RMS Signal A A A SNDR + =

等效位元數目(Effective Number of Bits,ENOB):

類比數位轉換器輸出端的輸出訊號通常包含了訊號以及其他的雜訊和 諧波,因此類比數位轉換器真正能轉換的位元數並不完全等於其解析度,於 是採用等效位元數目來定義類比數位轉換器真正能轉換的位元數。 02 . 6 76 . 1 − = SNDRpeak ENOB 動態範圍(Dynamic Range): 動態範圍是指最大的正弦波輸入功率和當 SNR=0 時的正弦波輸入功率 的比值。通常當輸入訊號功率微弱時,SNR 值將會被雜訊所限制,隨著輸 入訊號功率的增加,訊號的諧波功率也跟著增加,漸漸地 SNR 值將被諧波 所限制,如圖 2.2 所示。 圖 2.2 SNR vs. 輸入訊號功率

靜態特性: 圖 2.3 類比數位轉換器非線性度示意圖 偏移誤差(Offset error): 圖 2.3 中直線 AB 與縱軸的交點與原點的距離即為偏移誤差大小。 增益誤差(Gain error): 圖 2.3 中直線 AB 的斜率與理想值(通常為 1)的誤差即為增益誤差大小。 微分型非線性度(Differential Non-Linearity,DNL): 圖 2.3 中兩個連續的數位輸出碼轉換點之間(C、D)相對於理想值(1 個 LSB)在水平軸方向上的最大距離即為其微分型非線性度大小。 積分型非線性度(Integral Non-Linearity,INL): 圖 2.3 中輸出輸入特性曲線和 AB 兩點所連成的直線間在垂直軸上的最 大距離即為其積分型非線性度大小。

2.2 類比數位轉換器架構介紹與比較

2.2.1 快閃式架構:

快閃式架構的類比數位轉換器是目前最快速最簡單的類以數位轉換器架構 [3],如圖 2.4 所示: 圖 2.4 快閃式類比數位轉換器架構 在快閃式(flash)類比數位轉換器中,類比的輸入訊號直接由轉換器的輸入端 輸入, 透過整個比較器陣列比出相對應的位階大小,而整個比較器陣列的參考 電壓準位由電阻分壓所決定;每一個輸入訊號只須經過一個時脈週期就可以被轉 換完成,所以通常快閃式類比數位轉換器很容易可以操作在較高的速度。舉例來 說,由於快閃式類比數位轉換器的輸入是採平行的方式輸入到各個比較器,因此 一個 N 位元解析度的快閃式類比數位轉換器就須要 2N -1 個比較器以及足以產生 出 2N -1 個參考電壓的電阻串列,這樣一來,一旦我們想要得到更高的解析度, 比較器的數目就會呈 2 的冪次方急速成長,造成硬體成本的提高。雖然快閃式類

比數位轉換器的架構簡單又擁有高速操作的優點,但其同時也有著許多的限制與 缺點:首先由於快閃式類比數位轉換器所須要的比較器數目會隨著其解析度的提 高而急速劇增,造成過大的晶片面積,大大提高製作成本;除此之外大量的硬體 須求也使得消耗功率跟著往上激增,再者由於輸入端並聯大量的比較器,導致前 端的取樣電路有很大的輸出負載,在高速的操作頻率之下,輸入端就必須有很大 的輸入驅動電流才足以使電路正常工作。另一方面,限制整個類比數位轉換器精 準度還有兩個問題:第一,決定參考電壓的電阻串列很可能因為彼此間的不夠單 一性而造成參考準位的不準確,當解析度須求越高時這個影響就會越嚴重。第 二,因製程飄移所造成比較器的偏移電壓亦會影響整個類比數位轉換器的輸出結 果。例如,對一個類比輸入為 2V 而言,若要達到 10 位元的解析度,則每個位 階的差異僅僅只有 2mV,無論是 bipolar 或是 CMOS 製程的比較器都很難達到這 樣的要求。綜合以上的限制與缺點,一般而言,快閃式類比數位轉換器的準確度 往往不會超過 8 位元。

2.2.2 半域轉換架構:

圖 2.5 半域轉換類比數位轉換器架構圖 2.5 所示為半域轉換(subrange)架構的類比數位轉換器架構圖。為了改善快 閃式類比數位轉換器須要過多的比較器所產生的限制,衍生出了半域轉換架構的 類比數位轉換器;一個半域轉換架構的類比數位轉換器包含了 2N個電阻,2N/2 -1 個比較器,以及伴隨在每個電阻旁的切換開關。首先取樣電路對輸入訊號作取樣 並將取樣值交給第一組量化器(coarse comparator)作量化,並輸出表示 MSB 的幾 個位元;而第一組量化器的比較準位則是由 2N個電阻中的 2N/2個階段所決定。 接下來再經由先前輸出的 MSB 位元透過切換開關來定義第二組量化器(fine comparator)的比較準位,剩下的 LSB 位元將會被比較決定出來。 半域轉換架構減少了電路所須的比較器個數,不過卻也增加了許多的切換開 關,對於輸入端來說也造成了相當大的負載,依然無法將精準度做到太高。

2.2.3 雙步驟架構:

圖 2.6 雙步驟類比數位轉換器架構 圖 2.6 所示為雙步驟(two-step)架構的類比數位轉換器架構圖[4][5][6]。類似 於半域轉換架構的精神,將原本快閃式架構中每筆資料只須一個時脈週期來處理 延長為兩個時脈週期,減少一半的比較器數量。一個雙步驟架構的類比數位轉換 器包含了一個取樣並保持電路、兩組量化器、數位類比轉換器、減法器和乘法器。 首先,取樣電路對輸入訊號作取樣並交給第一組量化器作量化,第一組量化器的 輸出碼字決定了數位類比轉換器的輸出,再透過減法器得到數位類比轉換器的輸 出以及取樣值的差值,這個剩餘值(residue)將會被乘法器放大回原本的比較範 圍,以供給第二組的量化器作量化。2.2.4 多階管線化架構:

圖 2.7 管線化類比數位轉換器架構 圖 2.7 所示為管線化架構的類比數位轉換器架構圖。每一個轉換位階包含了 取樣電路、N 位元的量化器、以及乘法器和減法器,其轉換機制相同於雙步驟的 架構,差別僅在於管線化架構將整個轉換過程細切成更多級,每級前端都有取樣 電路對上一級的剩餘值作取樣。而每一級的數位輸出將會因延遲時間的不同經過 不同的延遲暫存器,接著再利用數位校正電路將各級的數位輸出碼字合併為一個 碼字輸出,改善了雙步驟架構產出率(throughput rate)太低的問題,同時提高電路 中各級比較的偏移電壓容忍度,在花費合理的晶片面積和功率之下,較容易達到 高速、高精準度的須求[7][8]。2.2.5 平行管線化架構:

圖 2.8 平行管線化類比數位轉換器架構 圖 2.8 所示為平行管線化架構的類比數位轉換器架構圖。為了更進一步提升 管線化架構類比數位轉換器的操作速度,於是提出了平行管線化架構,利用分時 多工的想法來實現,換句話來說,理論上每增加一組的電路硬體,就可以使轉換 速度提高一倍。不過在實際的設計上,平行管線化架構仍有其主要的限制:第一, 不同通道間的時序不一致(timing mismatch)會使得取樣點有偏差,造成頻譜上的 響應受影響,在高精確度的應用時,這個影響就會更嚴重,而且時序的不一致是 不能避免的,因為時脈的分佈對各個通道而言本來就很難完全對稱。第二,各通 道間的剩餘值放大器增益不一致(gain mismatch)將會產生固定型式的雜訊,減低 電路的精準度[10][11]。第三章

取樣並保持電路設計

本章首先會針對取樣並保持電路的基本操作原理做一個概念式的說明,並詳 細介紹其相關的特性參數及參數定義,透過這些公認的參數來評估取樣並保持電 路的效能,同時對於取樣並保持電路設計的重要關鍵有初步的體認;接著再對幾 種常見的取樣並保持電路架構做初步的分析與比較,進而決定適合本論文所預期 達到目標的電路架構。 除此之外,本章也將針對取樣並保持電路的設計流程做清楚的說明,包含其 細部電路的電路架構圖以及電腦模擬結果,最後再附上取樣並保持電路的量測結 果。 3.1 簡介 3.2 取樣並保持電路基本原理 3.3 取樣並保持電路架構介紹與比較 3.4 取樣並保持電路設計 3.4.1 取樣網路分析與設計 3.4.2 開關增壓技術 3.4.3 運算放大器 3.4.4 共模回授電路 3.4.5 時脈產生器 3.5 取樣並保持電路製作 3.5.1 電路量測 3.5.2 量測結果 3.5.3 討論3.1 簡介

在類比數位轉換器的設計中,取樣並保持電路扮演一個非常重要的角色,因 為取樣並保持電路通常置於類比數位轉換器的最前端直接與輸入訊號接觸,因此 取樣並保持電路主導了整個類比數位轉換器的取樣速度和精確度等基本性能。 取樣並保持電路最主要的兩項功能:首先對輸入訊號的電壓大小作取樣,接 著將取樣到的訊號儲存其電壓值後傳給下一級電路。另一方面,由於全差動(Fully Differential)的架構具有較大的動態範圍(Dynamic Range)以及較好的雜訊免疫 度,諸如電荷注入效應(Charge Injection Effect)、電源電壓雜訊(Power Supply Noise)、時脈反饋效應(Clock Feedthrough Effect)等之消除,因此絕大部份的類比 數位轉換器以及取樣並保持電路均採用全差動的形式。 我們所設計的全差動取樣並保持電路主要是作為高速類比數位轉換器的前 端電路,在電源電壓 1.8V 時,時脈速度 100MHz,解析度為 10 位元,輸出信號 振幅 2Vp-p。3.2 取樣並保持電路基本原理

圖 3.1 取樣並保持電路功能圖 圖 3.1 表示一個取樣並保持電路的基本工作原理,為了能針對不斷變化的輸 入訊號作取樣,所以一個取樣並保持電路最基本會包含一個儲存能量的元件和一 個能控制訊號進出的開關。而具有儲存特性的電子元件不外乎是電感和電容,在 實際應用上儲存電壓在電容上又比儲存電流在電感上容易的多,因此幾乎所有的 取樣並保持電路都是使用電容來作儲能元件。整個取樣並保持電路的動作主要分為兩個部份:分別是取樣模式(Sample Mode)和保持模式(Hold Mode)。在取樣模式時,輸入訊號經過開啟的閘門開關對 電容 Ch 充電,並使的輸出追隨輸入而變化;而在保持模式時,閘門開關關閉, 取樣電容 Ch 因為電荷的積聚而保持在開關即將關上前的電壓準位,如此一來, 便對輸入訊號完成取樣及保持的動作。在實際的電路應用當中,由於取樣電容 Ch 所儲存的電荷往往會因為後級電路寄生電容的彼此耦合而使得電荷流失造成 取樣到的輸入電壓產生變化;所以整個取樣並保持電路前後往往會加上緩衝器以 隔絕前後電路對儲存在電容中電荷的影響,讓儲存的電荷不至於流失而影響電壓 的準確取樣,如圖 3.2。 圖 3.2 取樣並保持電路架構圖 為了正確及有效的對取樣並保持電路的特性及性能有所定義和規範,我們必 須先對於公認且基本的參數有一定的認識,以便用來界定一個取樣並保持電路的 效能[2][12]: 圖 3.3 取樣並保持電路行為示意圖

確認時間(Acquisition time,Tacq):

如圖 3.3 所示,確認時間是指當取樣並保持電路接收到取樣指令後;其 輸出點的擺幅為最大時(full-scale)從開始直到穩定(即使有一段固定差值)所 需要的時間。確認時間通常由輸入及輸出兩組緩衝器的回覆(recovery delay) 時間、開關 S 的開啟阻抗(turn-on resistance)、及 Ch 所決定。

穩定時間(Hold Settling Time,Ths):

如圖 3.3 所示,穩定時間是指當取樣並保持電路接收到保持指令後;開 始逐漸穩定至一電壓值所需的時間,而當最後穩定時仍會有一段誤差量。穩 定時間通常是由取樣電路後半段的緩衝器的穩定時間所決定。 衰退率(Droop Rate): 如圖 3.3 所示,在保持模式時,理論上所有的電荷儲存在電容 Ch 上; 當電荷透過某些寄生路徑流失時;取樣電壓也會發生偏移。而這一些漏電行 為往往和電路的輸出級緩衝器偏壓電流及電容 Ch 有關。 基底誤差(Pedestal Error): 在取樣電路進入保持狀態時,所儲存的電壓和理想電壓的誤差量;通常 這一項誤差由電晶體開關 S 在關閉時,其電荷注入效應對電容 Ch 所構成。 如圖 3.4 所示,當電晶體關閉時,存在電晶體通道內的電荷 Qch 將會有部份 注入到取樣電容 Ch 中,影響取樣到的輸入電壓值。 圖 3.4 電荷注入效應

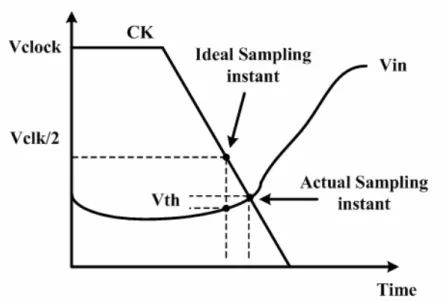

非線性誤差(Nonlinearity Error): 相似於類比數位轉換器的 INL/DNL,非線性誤差所定義的為取樣電路 輸入輸出及其理想上所對應構成的直線最大的誤差量,如圖 3.5 中所示。非 線性誤差通常來自於輸入輸出緩衝器的非線性,電晶體開關 S 對於電容 Ch 的電荷注入效應(charge-injection)的非線性,即隨著輸入電壓不同對於會有 不同開關 S 的開啟阻抗(turn-on resistance)。 增益誤差(Gain error): 圖 3.5 中直線 AB 的斜率和理想轉換曲線斜率(通常為一)的差異。 圖 3.5 取樣並保持電路非線性示意圖 保持模式反饋(Hold-mode feedthrough): 由於電晶體開關 S 本身具有寄生的電容(Cgs 或 Cgd);即使當電晶體關 閉時,輸入信號仍然會透過寄生電容對電容 Ch 所儲存的電荷造成影響,進 而使取樣到的輸入電壓產生偏移。 動態範圍(Dynamic Range): 在一定的準確度下(容許的保持電壓誤差量),取樣電路可以取樣到最大 的和最小的信號功率上的比值。 間隙抖動(Aperture Jitter): 在 Hold 動作應該開始執行的時候,因為電晶體開關的非理想因素(Vt 的存在),使得真正關閉的時間點與理想之間有所誤差,而這一段誤差時間 往往是隨機的,如圖 3.6。

圖 3.6 取樣點非線性 訊號雜訊比(Signal-to-Noise Ratio,SNR):

SNR 是指輸出端上信號功率和整個雜訊功率(不含諧波功率)的比值,通 常量測信號為弦波。SNR 的限制通常是由前後兩組緩衝器及電晶體開關 S 的間隙抖動所決定。

無寄生動態範圍(Spurious-Free Dynamic Range,SFDR):

SFDR 是指輸出端主訊號功率和最大諧波功率的比值,單位是 dB。

訊號雜訊及失真比(Signal-to-Noise and Distortion Ratio,SNDR):

SNDR 是指輸出端上信號功率和整個雜訊功率及諧波項功率總和的比 值,通常量測信號為弦波。SNDR 的限制通常是由前後兩組緩衝器及其非線 性因素和電晶體開關 S 的電荷注入效應(charge-injection)所決定。

3.3 取樣並保持電路架構介紹與比較

取樣並保持電路的架構主要可以分為兩大類,開迴路形式和閉迴路形式。圖 3.7 所示為最簡單的一種開迴路形式的取樣並保持電路,其主要包含了一個控制 輸入訊號進出的開關、一個儲存取樣電壓的取樣電容以及一個運算放大器,其中 運算放大器被接成單一增益緩衝器(Unity-Gain Buffer)的形式。當電晶體開關打開 時,電路處於取樣模式,輸入訊號立刻對取樣電容 Ch 充電。當電晶體開關關閉 時,電路處於保持模式,輸入訊號停止對取樣電容充電,此時取樣電容上所儲存 的電壓值保持定值,其電容兩端的跨壓等於電晶體開關剛剛關上時的輸入訊號大 小,完成取樣並保持的動作。這種形式的取樣並保持電路其取樣速度完全取決於 電晶體開關的導通電阻與取樣電容的乘積大小,所以開迴路形式的取樣並保持電路很容易可以操作在很高的速度,不過由於電晶體開關並非完全理想,所以電晶 體開關的導通電阻變化以及關閉時所產生的電荷注入效應,都會嚴重影響到電路 的精準度,這個現象在低電壓電源的操作下影響更是巨大,所以開迴路形式的取 樣並保持電路的精準度一般沒有閉迴路形式來的高。 圖 3.7 開迴路形式取樣並保持電路架構 圖 3.8 所示為最簡單的一種閉迴路形式的取樣並保持電路,採用閉迴路形式 的主要目的,不外乎就是希望能夠減少上述開迴路形式中非理想電晶體開關所造 成的誤差。當電晶體開關打開時,電路處於取樣模式,輸入訊號透過一個轉導放 大器將輸入電壓轉成電流對取樣電容 Ch 充電。當電晶體開關關閉時,電路處於 保持模式,輸入訊號停止對取樣電容充電,此時被接成單一增益緩衝器的運算放 大器會將取樣電容的左端鎖在運算放大器的共模輸入電壓準位,讓取樣電容所儲 存的電荷不致於流失,而取樣電容兩端的跨壓會等於電晶體開關剛剛關上時的輸 入訊號大小,完成取樣並保持的動作。在閉迴路的架構中,電晶體開關關閉的時 間以及關閉時的電荷注入量均與輸入訊號無關,不影響電路的線性度,不過這樣 的電荷注入還是會使得輸出有一偏移電壓存在。 圖 3.8 閉迴路形式取樣並保持電路架構

圖 3.9 (a) Type 1 取樣並保持電路 (b) 取樣模式 (c) 保持模式 以下將介紹三種基本的閉迴路形式取樣並保持電路架構,它們都具有對運算 放大器作抵補電壓(offset voltage)儲存的功能。圖 3.9 所示為第一種形式的取樣並 保持電路架構;當 CLK 為高電位 CLKb 為低電位時,電路處於取樣模式(s),電 路的輸出在歸零(Autozero)的狀態,而運算放大器的輸出及輸入點分別接到其輸 出和輸入的共模電壓上;此時取樣電容 Cs 儲存了輸入訊號(input)和輸入共模電 壓間的電壓差值,同時,由於運算放大器正負相接,可以將抵補電壓一起儲存到 取樣電容中:

[ ]

[ ]

os input Cs out V s V V Autozero v s V − = =0 ,( ) 當 CLK 為低電位 CLKb 為高電位時,電路處於保持模式(h),運算放大器被接成 負迴授的形式成為單一增益緩衝器,藉此將剛剛儲存在取樣電容中的電荷鎖在運 算放大器的兩端;透過運算放大器虛擬接地(Virtual Short)的特性將剛才儲存的抵 補電壓抵銷,而不會反映在最後的輸出值上。[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

A h V s V A h V V V s V V V h V A h V V V V V h V out input out os os input cs out out os cs out − = − + − = + = = − + = − − − ) ( ) ( ) ( 由上面的式子我們可以發現,因抵補電壓所產生的誤差項已經被消除掉,而所剩 下的誤差項為運算放大器本身的增益誤差(Gain Error)所造成。 圖 3.10 (a) Type 2 取樣並保持電路 (b) 取樣模式 (c) 保持模式 圖 3.10 所示為第二種形式的取樣並保持電路架構;當 CLK 為高電位 CLKb 為低電位時,電路處於取樣模式(s),電路的輸出在歸零(Autozero)的狀態,而運 算放大器的輸出及輸入點分別接到其輸出和輸入的共模電壓上;此時取樣電容 Cs 儲存了輸入訊號(input)和輸入共模電壓間的電壓差值,同時,由於運算放大器 正負相接,可以將抵補電壓一起儲存到取樣電容中:[ ]

[ ]

os input Cs out V V V s V V Autozero v s V − = − = =0 ,( )當 CLK 為低電位 CLKb 為高電位時,電路處於保持模式(h):

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[

(

[ ]

)

(

[ ]

)

]

[ ]

[ ]

(

[ ]

[ ]

)

[ ]

[ ]

[ ]

A h V C C s V C C h V V h V s V C C s V h V V s V h V C Q Q Cf Q s V h V A h V V h V h V h V h V V V h V out f s input f s os input f s Cf out os input s Cs Cf Cf Cs Cf out os Cf out Cs out ) 1 ( 0 + − = + − + + = − − − − = ∆ − = ∆ ∆ + = − = − = + = − − − − − − 第二種形式取樣並保持電路的工作原理即是利用電荷守恆原理,在 Cs 左端原本 儲存了(Vinput * Cs)的感應電荷;Cs 右端也儲存了相等量的負電荷;在保持模式 中,左端的電荷會被接地;右邊的電荷則會跑到 Cf 的左端,而 Cf 的右端此時也 會感應相對等的電荷量而電壓(Vout)相位剛好跟原本的 Cs 左側的輸入電壓相 同;若 Cs 和 Cf 的電容值不同;則 Vout 會根據電荷守恆的原理反映出 Cs/Cf 的 電壓。這種形式的電路結構仍然可以將抵補電壓(offset voltage)儲存並抵銷;Vout 輸出最後的誤差項將是運算放大器本身的增益誤差(Gain error)。圖 3.11 (a) Type 3 取樣並保持電路 (b) 取樣模式 (c) 保持模式 圖 3.11 所示為第三種形式的取樣並保持電路架構;當 CLK 為高電位 CLKb 為低電位時,電路處於取樣模式(s),電路的輸出在歸零(Autozero)的狀態,而運 算放大器的輸出及輸入點分別接到其輸出和輸入的共模電壓上;此時取樣電容 Cs 以及迴授電容 Cf 都儲存了輸入訊號(input)和輸入共模電壓間的電壓差值,同 時,由於運算放大器正負相接,可以將抵補電壓一起儲存到取樣電容和迴授電容 中:

[ ]

[ ]

[ ]

Cf os input Cs out V V s V s V Autozero v s V = − = =0 ,( )當 CLK 為低電位 CLKb 為高電位時,電路處於保持模式(h):

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[ ]

[

(

[ ]

)

(

[ ]

)

]

[ ]

[ ]

(

[ ]

[ ]

)

[ ]

[ ]

[ ]

A h V C C s V C C h V V h V s V C C s V h V V s V h V C Q Q C Q s V h V A h V V h V h V h V h V out f s input f s os input f s Cf out os input s Cs Cf f Cf Cf Cf out os Cf out ) 1 ( ) 1 ( 0 + − + = + − + + = − − − − = ∆ − = ∆ ∆ + = − = + = − − − − − 第三種形式和第二種形式的取樣並保持電路的工作原理都是利用電荷守恆原 理。唯一的差別是在取樣模式時,迴授電容 Cf 也同時對輸入訊號作取樣,這樣 一來,最後的 Vout 值也會多出一倍出來。Type1 Type2 Type3

閉迴路低頻 增益 1 f s C C ) 1 ( f s C C + 低頻增益誤 差 A h Vout[ ] ) 1 ( f s C C + A h Vout[ ] ) 1 ( f s C C + A h Vout[ ] 迴授因子 (β) ( s g) s C C C + ( ) g f s f C C C C + + ( s f g) f C C C C + + 時間常數 .(w/h Cg) gm CL f L s s f L f C gm C C C C C C × + + f L s s f L f C gm C C C C C C × + + 時間常數 .(w/o Cg) s L s s g g L C gm C C C C C C × + + f g s L g s f L f C gm C C C C C C C C × + + + + ( ) ( ) f g s L g s f L f C gm C C C C C C C C × + + + + ( ) ( ) 熱雜訊(w/o Cg) Cs KT s C KT f s C C KT + 表3.1 閉迴路取樣並保持電路比較 表3.1中gm以及Cg分別代表運算放大器的轉移電導和輸入端的雜散電容, 而CL為負載電容。從表中我們可以發現,Type1的迴授因子最大(趨近於1),因 此如果想要能夠操作在較高的頻率下,Type1是最好的選擇;又因為作為管線式 類比數位轉換器前端的取樣並保持電路並不須要對輸入訊號作放大,所以我們所 設計的取樣並保持電路會採用可以操作在較高取樣頻率的Type1架構。而Type2

和 Type3 均具有放大輸入訊號的功能;可以藉由調整電容值來決定電路的增益, 其中 Type3 因為對迴授電容有預先充電的動作,所以其電路速度又略比 Type2 來 的快,此一技巧可以應用於之後管線式類比數位轉換器的增益級中。

這三種架構的取樣並保持電路在取樣模式時,運算放大器的輸出都會處於歸 零的狀態,也就是說在保持模式時,運算放大器須要對負載電容從共模電壓開始 充電;不過,若考慮到當電路操作在奈奎斯特取樣頻率(Nyquist Sampling Rate) 時,這樣預先歸零的動作可以減低運算放大器迴轉率(Slew Rate)的須求。

3.4 取樣並保持電路設計

圖 3.12 Flip-Around 架構取樣並保持電路 本論文的取樣並保持電路是採用上述 Type1 的 Flip-Around 架構所設計(圖 3.12),使用全差動的形式來提高電路對雜訊的免疫度,如電源電壓雜訊、電荷注 入效應、時脈反饋效應等,整個電路包含一對開關增壓電路、一對取樣電容、一 個全差動運算放大器以及數個電晶體開關。整個取樣並保持電路在保持模式的轉 移函數可以寫成下式: in s ip o V C C A V =[1− 1 (1+ )]× 式中 A 為運算放大器的低頻增益,Cip為運算放大器輸入點上所看到的寄生電容 大小,Cs為取樣電容大小;現在我們可以推算出因運算放大器有限的低頻增益所 導致的增益誤差 ε,以及電路的迴授因子:) 2 . 3 ( 1 ) 1 . 3 ( ) 1 ( 1 ≈ + = × + = ip s s in s ip C C C V C C A β ε 接下我們首先針對電路的訊號雜訊比(SNR)做初步的分析;雜訊的方面我們主要 考量到兩個比較重要的成份:量化誤差(Quantization Noise)和熱雜訊(Thermal Noise)。 圖 3.13 (a) 量化器轉移特性曲線 (b) 量化誤差示意圖 圖 3.13(a)表示輸入訊號經過量化器量化後的轉移特性曲線,而圖 3.13(b)顯 示輸入訊號經量化器後產生的量化誤差,假設量化誤差為均勻分佈(Uniformly Distributed),我們可以將量化誤差的功率大小表示成下式:

12

1

2 2 2 2 , LSB T/ T/ Q rms QV

dt

V

T

V

=

=

∫

− (3.3)圖 3.14 RC 電路熱雜訊示意圖 ) 4 . 3 ( 4 1 4 4 1 2 1 2 2 C KT RC KTR V RC RC B o n = × = = × = π π 圖 3.14 為 RC 電路中熱雜訊的示意圖,而上式中 Bn為雜訊頻寬(Noise Bandwidth),式(3.4)用來表示熱雜訊的功率大小。 綜合式(3.3)(3.4)來計算取樣並保持電路的 SNR 值: ) 5 . 3 ( 12 ) 2 / 2 ( 2 log 10 12 2 log 10 2 2 2 2 + = + = + = C KT V V V V 熱雜訊功率 量化雜訊功率 訊號功率 SNR N FS FS LSB FS σ 式(3.5)中 VFS代表輸入訊號的最大振幅(Full Swing),N 代表電路的解析度,σ 2 為熱雜訊功率,K 和 T 分別代表絕對溫度和波茲曼常數(Boltzmann’s Constant)。 接下來將式(3.5)透過 Matlab 軟體作分析可以得到下圖 3.14。

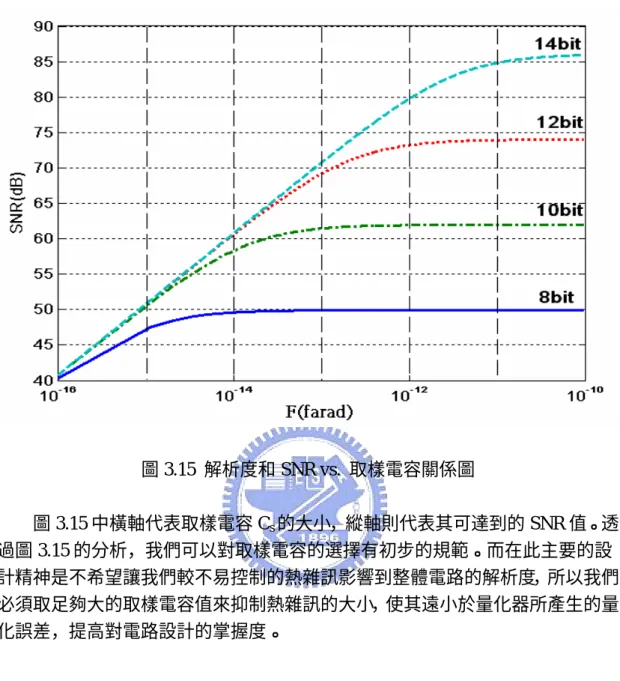

圖 3.15 解析度和 SNR vs. 取樣電容關係圖 圖 3.15 中橫軸代表取樣電容 Cs的大小,縱軸則代表其可達到的 SNR 值。透 過圖 3.15 的分析,我們可以對取樣電容的選擇有初步的規範。而在此主要的設 計精神是不希望讓我們較不易控制的熱雜訊影響到整體電路的解析度,所以我們 必須取足夠大的取樣電容值來抑制熱雜訊的大小,使其遠小於量化器所產生的量 化誤差,提高對電路設計的掌握度。

3.4.1 取樣網路分析與設計:

圖 3.16 取樣網路示意圖 當取樣並保持電路處於取樣模式時,如圖 3.16。其前端取樣網路包含一對取 樣電容(Cs1和 Cs2),四個電晶體開關;考慮取樣電容取樣到的電壓值的穩定精確 度(Settling Accuracy)必須高於 0.5LSB,我們可以得知取樣網路中 RC 的時間常數 須求: 2 ln ) 1 ( 2 1 2 1 2 / 1 + ≤ ≤ − N f LSB e s s f s s τ τ 式中 τs為取樣網路中的 RC 時間常數,N 為解析度,fs是取樣頻率。以 100MHz 的取樣頻率為例,如果要達到 10 位元的解析度,則取樣網路的 RC 時間常數必 須要小於 0.65 nsec。3.4.2 開關增壓技術:

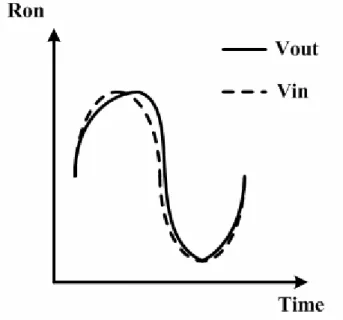

在基本的切換式電容(Switch-Capacitance)電路中,由於電晶體開關在開啟時 並非理想的阻抗為零,而是存在一定的阻抗值;而這個阻抗值的大小會隨著輸入訊號的大小而作變化,其中,NMOS 電晶體開關的阻抗隨著輸入訊號變大而增 大;而 PMOS 電晶體開關的阻抗隨著輸入訊號的變大而減小;因此在電晶體開 關的設計方面,我們有以下幾點的考量:我們首先針對電晶體開關的電導係數與 輸入電壓間的關係開始分析,圖 3.17 顯示出電晶體開關的電導係數對輸入訊號 隨著電源電壓下降所產生的變化,其中我們假設電晶體開關的電導系數為一個線 性模型來作圖。 圖 3.17 電晶體開關電導係數與輸入電壓間的關係圖 由圖 3.17 可以發現隨著供應電源電壓的下降,電晶體開關已經很難只用一 個 NMOS 或是一個 PMOS 來實現,甚至就連 CMOS 開關都面臨到很大的難題; 然而在電晶體開關的設計上,不僅僅只是要求能做到”導通”與”關閉”這兩個功 能,其導通阻抗的變化更是一個重要的考量,隨著導通阻抗的變化,輸入訊號經 過取樣網路後得到的取樣訊號也會跟著變化,如圖 3.18,產生與輸入訊號相關的 誤差項,這個誤差將使得電路的線性度下降。然而對於講求線性度的取樣並保持 電路而言,在低電源電壓操作下,因電晶體開關導通電阻的變化所產生的非線性 將會更加的嚴重。

圖 3.18 電晶體導通阻抗對輸入輸出訊號所造成的影響 除此之外,電晶體開關在關閉時所造成的電荷注入效應(Charge Injection Effect),在高解析度的取樣並保持電路設計中,也是一個重要的參數。我們可以 將電晶體開關在導通時積存在通道內的電荷量(Qch)寫成下面的式: ) ( GS TH ox ch WLC V V Q = − 當電晶體開關關閉時,原本積存在通道中的電荷 Qch將會分別注入到電晶體的源 極和汲極,造成取樣電容的取樣電壓值產生誤差。如果通道內積存的電荷量 Qch 和輸入訊號無關而且維持一個定值,那我們可以視其為一個偏移電壓(Offset) 源,並不會對取樣並保持電路的線性度造成影響;不過,事實上 Qch不只不是一 個定值還跟輸入訊號彼此相關,於是這樣一個和輸入訊號相關的誤差將會造成取 樣並保持電路的諧波失真,惡化電路的線性度與整體的精準度。 綜合上面的考量,我們希望設計出一種電晶體開關,其適用於低電源電壓操 作,並且在輸入訊號變動範圍內的導通阻抗以及導通時積存在通道中的電荷量維 持一個常數;為了達到這樣的目的,已經有很多相關的研究被發表[13][14][15]。

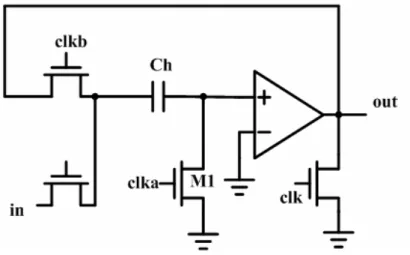

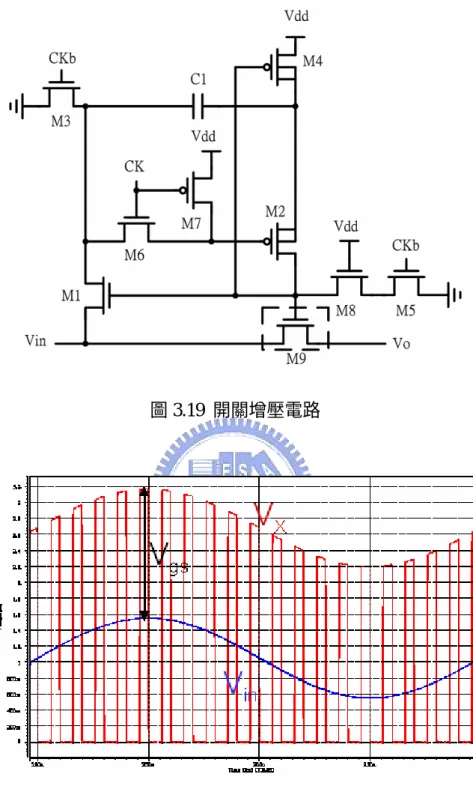

圖 3.19 開關增壓電路 圖 3.20 開關增壓電路模擬 圖 3.19 所示為本論文所採用的開關增壓電路架構,而圖 3.20 為電路經 Hspice 模擬的結果。 在圖 3.19 中,當 CK 為低電位 CKb 為高電位時電路處於保持模式,M9 關 閉阻隔輸入訊號,同時 M4 和 M3 導通,並將 Vdd 的壓差存於 C1 的兩端,等到 CK 為高電位 CKb 為低電位時電路處於取樣模式,M6 導通致使 M2 導通,接著

M1 被導通並使 M9 的閘極和源級的壓差保持在 Vdd 附近的一個定值,於是 M9 被導通使電路對輸入訊號作取樣。在開關增壓電路設計中,我們必須考慮到電路 的可靠度,也就是必須確保電晶體的跨壓不可高於 Vdd,避免因跨壓過大造成電 晶體有被擊穿或崩潰的危險,圖中 M8 就是用來緩和 M5 的 Vds,確保電路的可 靠度。透過開關增壓電路,M9 的 Vgs-Vth 將趨近於一個常數,其導通阻抗也跟 著唯持在一個定值;於是與輸入相關的電荷注入效應和取樣誤差就會大大的減小 並可以視為共模上的雜訊而予以消除,提升取樣並保持電路的線性度。

3.4.3 運算放大器:

無論是在取樣並保持電路或是類比數位轉換器中,電路的速度和精確度主要 都取決於運算放大器的表現;其單一增益頻寬和迴轉率決定電路的操作速度、低 頻增益決定了電路的增益誤差、輸出端的最大擺幅決定電路的訊號動態範圍,所 以對於運算放大器架構的選擇與其細部電路的設計,將嚴重影響整體電路的效 能,以下為我們設計上的要點和須求: (a) 低頻增益: 在運算放大器低頻增益的考量上,我們必須確保整體電路的增益誤差小 於 0.5LSB;假設運算放大器輸入端上的寄生電容(Cip)大小為 0.15pF,利用 式(3.2)我們可以求出電路的迴授因子,再透過式(3.1)來計算運算放大器所須 的低頻增益: dB A LSB C C A V s ip i 5 . 68 2 1 ) 1 ( ≥ ⇒ ≤ + (b) 迴轉率: 在運算放大器迴轉率的考量上,由於我們所採用的取樣並保持電路有歸 零(Autozero)的動作,所以輸出最大改變率只有 Vp-p的一半,式中 CL為後級 的負載電容。在此我們必須考慮到非重疊時脈(Non-Overlap Clock)對實際可 用的取樣時間及保持時間的影響,我們預估 1/4 的保持時間給電路作為迴轉 時間。s V SR period overlap non T T C V SR Slew Slew L p p µ / 500 ) ( 2 1 4 1 2 1 ≥ ⇒ − × = × = − (c) 單一增益頻寬: 假設整個運算放大器是一個簡單的單極點系統,要使得穩定時的精準度 (Settling Accuracy) 達到 10 位元: MHz f f LSB e t t set T set set 480 2 1 2 1 ≥ ⇒ = ≤ = − πβ τ ε τ 式中 ε 代表電路穩定時的誤差量,β 代表電路的迴授因子,在此我們預估 3/4 的保持時間給電路做穩定(Settling)的動作。 (d) 輸出擺幅: 在切換式電容電路中輸出信號的動態範圍並不能使運算放大器脫離飽 和區而操作,否則將會使增益誤差急遽增大;使電路失去原該有精確度,並 產生失真(Distortion)的現象。這也就是為什麼切換式電容電路在低電壓製程 會面臨設計瓶頸的原因。

(e) 運算放大器架構: 圖 3.21 摺疊堆積式與望遠鏡式運算放大器 圖 3.21 中是最基本的兩種運算放大器的架構;左邊的摺疊疊積式 (Folded-Cascode)運算放大器的輸入信號由 M17 和 M18 輸入,因此此一架構 的增益約是

( )

2 17 ro gm ,其中 ro 是 out+或 out-點的輸出阻抗;而信號經過的 路徑在 M7 和 M8 的汲極(drain)端會產生一非主極點(non-dominant pole)而影 響單一增益頻寬,非主極點的時間常數是 M7 和 M8 汲極端的 RC 乘積值; 而右邊的望遠鏡式運算放大器增益約是 2 1(ro) gm ,其中 ro 是 out+或 out-點的 輸出阻抗;非主極點位置在 M3 和 M4 的源極(source)端。將兩種電路架構比 較,增益相差並不多,而非主極點的位置則因望遠鏡式架構中的 M3 和 M4 為 NMOS 而有較小的寄生電容和較大的轉導,所以可以得到較佳的頻率響 應;在消耗功率上望遠鏡式架構中的源極耦合對(source-couple-pair)與增益 級(gain-stage)共用電流源;電流再利用(Current-reuse)的設計使其消耗較少功 率;在輸出擺幅上摺疊疊積可以有較大的輸出擺幅;而望遠鏡式架構因串疊 較多的電晶體,輸出擺幅上有較多的限制。舉例而言,如下圖如果輸出的動 態範圍要達到 2Vp-p,單端的動態範圍要有 1V;則 M4、M6、M3、M5 的 Vds 就必須大於 500mv+Vdsat 才不至於使運算放大器脫離飽和區操作!圖 3.22 雙級(Two-Stage)運算放大器 然而在低電源電壓的操作條件之下,又要有足夠的輸出擺幅,前述的兩種架 構並不是相當適合。為了克服這樣的問題,於是我們採用雙級(Two-Stage)運算放 大器的架構(圖 3.22)[18],先利用第一級望遠鏡式放大器提供高電壓增益,再由 第二級放大器提供足夠大的輸出擺幅。與前述兩種架構的運算放大器相較,雙級 運算放大器在架構上明顯較為複雜,電路在操作速度上的表現也沒有前面兩種架 構來的好,除此之外,還必須做頻率補償來確保電路的穩定度(Stability),雖然有 這些設計上的難處,不過雙級運算放大器架構卻可以達到我們低電源電壓、高輸 出擺幅的須求。下圖 3.23 和表 3.2 為雙級運算放大器模擬結果! 圖 3.23 雙級運算放大器模擬

TT FF FS SF SS DC Gain 82dB 71.2dB 74.8dB 83.2dB 79dB PM 77 ° 83 ° 80 ° 76 ° 75 ° ft 805MHz 724MHz 758MHz 794MHz 758MHz Power 8.12 mW 8 .01 mW 8.23 mW 8.08 mW 8.32 mW 表 3.2 雙級運算放大器模擬

3.4.4 共模迴授電路:

在全差動運算放大器的設計中,共模迴授電路用來掐住運算放大器的共模電 壓,使運算放大器的擺幅能有一相同的基準點;在上述雙級運算放大器中的第一 級放大器,由於其輸出的擺幅並不大,我們可以採用連續時間型迴授共模電路(圖 3.24),減小對放大器的負載效應;而第二級放大器由於其輸出擺幅極大,連續時 間型共模迴授電路因其會脫離飽和區操作所以並不適用,須要採用動態式迴授共 模電路(圖 3.25)。 圖 3.24 連續時間型共模迴授電路圖 3.24 所示為一連續時間型共模迴授電路,第一級放大器的輸出分別輸入 MB3 和 MB6,而 MB7 和 MB8 為一固定電流源,Vcmo1 為參考的共模電壓值; 當第一級放大器的共模電壓向上升,則流經 MB2 的電流會增大,流經 MB1 的電 流會減小,使得共模迴授電路的輸出 Vct 電壓上升並控制第一級放大器 PMOS 電流源的電流變小,最後第一級放大器的輸出電壓跟著下降,如此一來,構成一 個負迴授網路,把第一級放大器輸出的共模電壓掐在參考電壓準位上。 圖 3.25 動態式共模迴授電路 圖 3.25 所示為一動態式共模迴授電路,當 clk1 為低電位 clk2 為高電位時 S5~S8 開啟,CB3 和 CB4 被充電到 Vcmo 和 CMFB2 的差值,而此時取樣電路處 於保持模式(Hold-mode);下一時刻 clk1 為高電位 clk2 為低電位時 S1~S4 開啟, 適才儲存於 CB3 和 CB4 的電荷會和 CB1 和 CB2 上的電荷作平均的動作,如果 Vout1 和 Vout2 的共模電壓有所偏移的話,壓差會耦合到 M9 的閘極上而透過運 算放大器的電流源迴授至輸出點 Vout1 和 Vout2 作校正;但對差動信號而言,正 負電荷會在 M9 的閘極抵銷而不會對共模電壓有影響。

3.4.5 時脈產生器:

圖 3.26 時脈產生器 在切換式電容電路中;電晶體的開關控制均由內部的時脈產生器所產生,由 於設計的取樣並保持電路是依賴電荷存在電容中來擷取資料,因此我們必須將取 樣模式和保持模式的時脈隔開,如下圖 3.27,以避免電荷流失。在各式各樣的取 樣並保持電路中,我們常常會發現有一組會被先關閉的開關;如圖 3.28。因為如 果 M1 關閉的時間是 clk1 的話,其關閉時的電荷注入效應會影響原本存在 Ch 右 側的電荷;但如果我們讓 M1 關閉,雖然關閉時的電荷仍會注入 C1 電容右側, 但因為輸入端的電晶體仍未關閉 Ch 左側仍被充電;基於電荷守恆原理,Ch 右側 需存在一等值電荷,因此剛才 M1 關閉時的電荷注入效應便不會影響最後所儲存 的電荷,此種技巧稱為底板取樣(Bottom-Plate Sampling)。 圖 3.27 時脈產生器波形圖 3.28 底板取樣技術

3.5 取樣並保持電路製作:

在取樣保持電路的佈局當中,我們把整個電路分為四個主要的區塊,分別是 運算放大器、電容陣列、電晶體開關、及時脈產生器。我們將各個區域分別隔開; 並用保護環(guard-ring)包圍,電容是使用 MIM 形式。而時脈產生器被隔離在晶 片的左上方以避免雜訊耦合到運算放大器。由於整體電路需要很多的 DC 直流電 壓,因此我們在空位擺上穩壓電容藉以穩定參考電壓。而供應類比電路的電壓源 和數位電路的電壓源分開以避免雜訊耦合效應。 考量到將來取樣並保持電路的實際量測,我們將相同的兩個取樣並保持電路 做在同一個晶片上,第一個取樣並保持電路的操作頻率為第二個取樣並保持電路 的兩倍;透過第二個取樣並保持電路對第一個取樣並保持電路的輸出作取樣,經 由這樣重複取樣(Resample)的方式來量測[16],如圖 3.29,這樣的做法可以減低 對量測儀器速度上的須求,除此之外,由於第二個取樣並保持電路操作在較慢的 速度,相對上也可以有比第一個取樣並保持電路有較大的驅動能力,減低因量測 儀器負載所造成的影響。圖 3.29 量測印刷電路板圖 Pulse Generator Spectrum Analyzer Oscilloscope Active Probe Function Generator Model Agilent 81110A R&S FSIQ26 TDS754D TK P6246 R&S SMIQ06B MAX Freq 165MHz 26.5GHz 500MHz 1GHz 6.4GHz MIN Freq --- 20Hz --- --- 300KHz Appendix --- --- 2GS/s CL<1pF --- 表 3.3 儀器型號與規格

3.5.1 電路量測:

整個取樣並保持電路晶片製作是採用裸晶的方式(圖 3.30)並未加以封裝,而 由於是採用 0.18μm 製程技術製造,所以電路有加上 ESD 保護電路。在量測上 我們將晶片透過磅線(Bonding Wire)和印刷電路板(PCB)連接(圖 3.31),為了減低 因為磅線電感所造成的電壓抖動,除了晶片內部的穩壓電容外,在印刷電路板上 我們也對各個電壓源加上足夠大的穩壓電容。 圖 3.30 取樣並保持電路晶片圖(1087μm X 910μm)圖 3.31 量測印刷電路板圖

3.5.2 量測結果:

圖 3.33 輸入訊號頻率 2MHz、取樣頻率 100MHz,時域量測圖

圖 3.35 輸入訊號頻率 50.038MHz、取樣頻率 100MHz,頻域量測圖

1996 [20] 2001 JSSC [21] 2003 VLSI [22] This work Sample Rate 100 MHz 75 MHz 100 MHz 100 MHz SFDR at Nyquist Rate 68 dB 85 dB 80 dB 47.19 dB Differential Input 2 Vpp 2 Vpp 1.8 Vpp 1.8 Vpp Power Consumption 140 mW 100 mW 33 mW 10.8 mW DC Gain of Opamp 76 dB 80 dB 63 dB 82 dB

Opamp Type Super Cascode Folded Cascode Telescopic Two-Stage

Supply Voltage 5 V 3 V 2.5 V 1.8 V

Technology 1µm CMOS 0.35µm CMOS 0.25µm CMOS 0.18µm CMOS

FOM 1.51 11.23 25.64 17.61 *FOM fs Power N / ) 2 ( × = 表 3.4 取樣並保持電路效能總結

3.5.3 討論:

透過量測我們發現量測所得的結果和電腦模擬所得的結果並不相同。考量到 Vdd、Gnd 和輸出端磅線電感的影響所作的佈局後模擬,在輸入頻率 2MHz 正弦波、 100MHz 取樣頻率之下,電路的 SFDR 可以有 68dB,如圖 3.37;而時際量測值卻 只有 46dB 左右,如圖 3.34。 圖 3.37 考量磅線電感影響的佈局後模擬圖 這樣的誤差有幾個可能的原因:電源電壓的抖動、製程的漂移、PCB 板上的 不匹配、訊號源或時脈產生器不夠精準等,經過實驗可以確定這些都不是致命的 原因。我們在此提出兩個最可能的原因: 第一,在本論文所設計的取樣並保持電路有作歸零(Autozero)的動作,這樣 的動作使得輸出訊號猶如被一個脈波訊號調變(Modulate),經過這樣調變的動 作,很多不在奈奎斯特(Nyquist)頻率內的雜訊或諧波項又會被調變進來,使得 在我們使用的頻帶內的雜訊和諧波增大。 第二,由於透過 Hspice 來模擬電路線性度是取特定點(實際應用時下級 MDAC 取樣的值)來做 FFT 運算,電路的 glitch 以及未穩定前的電壓值並不會有任何影 響,可是對於頻譜分析儀而言,這些 glitch 以及未穩定前的雜訊都會被計算進 來,勢必會使得量測到的效能大打折扣。 針對前兩點我們讓 Hspice 的動作能和實際量測時更一致,在一個輸出週期 內取 32768 點作 FFT 分析,不再只取到特定時間點的值,這樣一來我們可以得到下圖 3.38。 圖 3.38 利用 Hspice 模擬實際量測情形 上圖的輸入訊號、取樣頻率都與量測時相同,我們可以看到模擬的 SFDR 值跟實 際量測幾乎一樣,足以驗證我們的推測! 另一方面,考慮到取樣並保持電路在類比數位轉換器中實際的應用面,電路 的 glitch 和未穩定前的值並不應該算進電路的真實效能內,因為在類比數位轉換 器中,我們重視的是 MDAC 對取樣並保持電路取樣的那個時間點的電壓值而 已,所以本電路真正的效能並沒有完全量測出來,有可能必須借助一高解析度的 ADC 來協助量測,才能有較佳的結果!

第四章

類比數位轉換器系統與電路設計

本章首先會對數位校正技術(Digital Error Correction)做一個介紹,接下來針 對管線式類比數位轉換器各級解析度的選擇做一說明,選擇適合的各級解析度以 利於達到我們所預期的效能規格。除此之外,本章也將針對類比數位轉換器的設 計流程做清楚的說明,包含其細部電路的電路架構圖以及電腦模擬結果。 4.1 數位校正技術 4.2 每級 1.5 位元架構 4.3 區塊電路設計 4.3.1 比較器電路 4.3.2 編碼器電路 4.3.3 減法器與乘法器電路 4.4 類比數位轉換器製作 4.4.1 電路佈局 4.4.2 電路模擬結果

![圖 3.22 雙級(Two-Stage)運算放大器 然而在低電源電壓的操作條件之下,又要有足夠的輸出擺幅,前述的兩種架 構並不是相當適合。為了克服這樣的問題,於是我們採用雙級(Two-Stage)運算放 大器的架構(圖 3.22)[18],先利用第一級望遠鏡式放大器提供高電壓增益,再由 第二級放大器提供足夠大的輸出擺幅。與前述兩種架構的運算放大器相較,雙級 運算放大器在架構上明顯較為複雜,電路在操作速度上的表現也沒有前面兩種架 構來的好,除此之外,還必須做頻率補償來確保電路的穩定度(Stability)](https://thumb-ap.123doks.com/thumbv2/9libinfo/7490805.115068/49.892.280.611.128.467/第一級夠大輸出擺幅與前述兩種架構的運算放大器相較雙運算放大Stability.webp)