互補式金氧半溫度感測電路以及能帶隙參考電壓源

全文

(2) 互補式金氧半溫度感測電路以及能帶隙參考電壓源 CMOS Temperature Sensor and Bandgap Voltage Reference. 研 究 生:楊宙穎. Student:Julian Yang. 指導教授:謝太烱教授. Advisor:Prof. Tai-Chiung Hsieh. 國 立 交 通 大 學 電 子 物 理 研 究 所 碩 士 論 文. A Thesis Submitted to Institute and Department of Electrophysics College of Science National Chiao Tung University In partial Fulfillment of the Requirements For the Degree of Master in Electrophysics. July 2004 Hsinchu, Taiwan, Republic of China. 中 華 民 國 九 十 三 年 七 月.

(3) 互補式金氧半溫度感測電路以及 能帶隙參考電壓源 研究生:楊宙穎 指導教授:謝太烱教授 國立交通大學 電子物理研究所碩士班 摘要 一個數位輸出的溫度感測系統包括了前端的溫度感測電路、參考電 壓源,和後端的類比數位轉換器。本文探討溫度感測系統前端部分的設 計,以 ADS 做電路模擬。藉由 CMOS 製程中的雙載子接面電晶體,利 用其 VEB 電壓對溫度變化的特性,來完成溫度感測電路、參考電壓源, 電路模擬是使用 TSMC 公司的 CMOS 0.25um 1P5M 的標準製程參數。在 -25℃~125℃的溫度範圍內,模擬顯示所設計的電路有正比於溫度的感 測電壓,其隨溫度的變化率為 3.6mV/℃。參考電壓( Vref )為 1.21V,溫度 係數為 8.3ppm/℃。 另外提出一型電路的設計具有參考電壓 Vref = a1VEB1 + a2VEB 2 的形 式。將雙載子接面電晶體的 VEB 電壓對溫度做二階泰勒級數展開,再以 a2 = 1, a2 = −0.79 的線性組合來完成溫度的二階補償。以電流模式的電路. 架構達到 VEB 電壓的線性組合,使用 TSMC 0.18um 標準製程參數,模擬 結果可達到當 VDD=1.8V 時,從-40℃到 125℃的溫度範圍,參考電壓為 255mV,溫度係數為 7.8 ppm/℃,消耗的電流為 408uA,消耗的功率為 0.73mW(在 25℃)。 I.

(4) CMOS Temperature Sensor and Bandgap Voltage Reference Student:Julian Yang. Advisor:Prof. Tai-Chiung Hsieh. Institute and Department of Electro-physics National Chiao-Tung University. Abstract A temperature sensing system with digital output consists of a front part and a rear part. The front part includes temperature sensor and bandgap voltage reference. The rear part is an analog to digital converter (ADC). In CMOS technology, the BJT device is used as the basic temperature sensor. The base-emitter voltage (VEB) can be approximated as a linear function of temperature. By using it, temperature sensor and bandgap voltage reference can be accomplished. The simulation of the front part using a standard TSMC 0.25um 1P5M CMOS process is presented in the thesis. The designed PTAT (Proportional To Absolute Temperature) circuit has an output voltage in proportion to absolute temperature with 3.6mV / ℃. The reference voltage (Vref) is 1.21V with an effective temperature coefficient of 8.3 ppm/℃ from -25℃~125℃. Further more, A new type of bandgap voltage reference, in the form of Vref = a1VEB1 + a2VEB 2 , is proposed. We expand VEB(T) into Taylor series. After II.

(5) second-order compensation with one scaling factor a1 =1 and a2 =-0.79, we will get a third-order temperature dependency of bandgap voltage reference. With current mode topology, the circuits design achieves a second-order compensation of VEB. It is simulated with the models of standard TSMC 0.18um 1P6M process. From simulation, the output voltage is 255mV with an effective temperature coefficient of 7.8 ppm/℃ for the temperature range -40℃~125℃. Total current consumption is about 408uA and power consumption is about 0.73mW at 25℃ for this proposed circuit.. III.

(6) 致謝 有幸能夠留在交大繼續讀研究所,經過兩年多的努力,終於順利完 成碩士學業。 從小時候帶我到長大的奶奶,在一年級上學期的期末考週前逝世 了,身為長孫的我只能在有期末考的當天回來新竹考試,不過還是彌補 不了「樹欲靜而風不止、子欲養而親不待」的遺憾,僅以此論文紀念我 的阿嬤。在這兩年中,首先感謝生育我的父母和阿公,在生活上照顧的 無微不至讓我無後顧之憂,適時的開導啟發我走向正確的方向,感謝家 人無怨無悔的支持。 在研究課題上,感謝指導教授謝太烱老師的教誨與悉心指導,沒有 他的不厭其煩的指引與協助,本論文不可能完成。再來要感謝郭立民和 趙靜軒學長在電路模擬與 layout 的指導,使我的疑義得到解決。 感謝實驗室同窗黃賢生常常和我一起討論我的電路,幫我解決很多 難題,還有林伯洋、鄒善強、吳柏霖同學和龔俊穎學弟在生活中和課業 上相互勉勵。感謝女友薇嵐在最後一段日子的體諒、關懷和鼓勵。最後 感謝皓棠、萬信、璟輝、照慶、子昭在我遇到困難或低潮時,給予支持。. 楊宙穎 2004. 夏 於新竹. IV.

(7) 目錄索引 中文摘要. Ⅰ. 英文摘要. Ⅱ. 致謝. Ⅳ. 目錄索引. Ⅴ. 圖索引. Ⅶ. 表格索引. Ⅸ. 第一章. 序論 …………………………………………………………………… 1. 1-1. 背景簡介………………………………………………………………………1. 1-2. 動機……………………………………………………………………………2. 1-3. 感測器設計原理………………………………………………………………5. 1-4. 論文架構………………………………………………………………………6. 第二章. 基本溫度感測電路與能帶隙參考電壓源 …………………….7. 2-1. 傳統溫度感測電路的回顧……………………………………………………7. 2-2. 傳統能帶隙參考電壓源的回顧……………………………………………10. 2-3. 模擬結果……………………………………………………………………13. 第三章. 新型能帶隙參考電壓源 …………………………………………15. 3-1. 理論基礎…………………………………………………………………15. 3-2. 電路實現……………………………………………………………………20. V.

(8) 3-2-1. 運算放大器(OP-AM)………………………………………………20. 3-2-2. PTAT…………………………………………………………………24. 3-2-3. CTAT…………………………………………………………………28. 3-2-4. 用電流模式(current mode)來執行 VBE ( PTAT ) − 0.79VBE (CTAT ) …30. 3-2-5. 啟動電路 start-up……………………………………………………32. 第四章. 總結與未來展望……………………………………………………36. 4-1. 總結…………………………………………………………………………36. 4-2. 未來展望……………………………………………………………………38. 參考文獻…………………………………………………………………………39. VI.

(9) 圖索引 圖 1. 1. 電子式溫度感測器分類圖………………………………………………1. 圖 1. 2. 溫度感測系統……………………………………………………………3. 圖 1. 3. 感測器示意圖 ……………………………………………………………4. 圖 1. 4. 橫向雙載子接面電晶體剖面圖…………………………………………5. 圖 1. 5. 縱向雙載子接面電晶體剖面圖…………………………………………5. 圖 2. 1. ∆VBE ………………………………………………………………………8. 圖 2. 2. ∆VBE 跨壓在 R1…………………………………………………………8. 圖 2. 3. PTAT 電流………………………………………………………………9. 圖 2. 4. PTAT 電壓………………………………………………………………10. 圖 2. 5. 能帶隙參考電壓源原理………………………………………………11. 圖 2. 6. 溫度感測電路與參考電壓源……………………………………………12. 圖 2. 7. 佈局圖……………………………………………………………………12. 圖 2. 8. PTAT 電流………………………………………………………………13. 圖 2. 9. PTAT 電壓(R2=50K) ……………………………………………………14. 圖 2. 10 參考電壓對溫度關係圖…………………………………………………14 圖. 3. 1 BJT…………………………………………………………………………15 圖. 3. 2. ……………………………………………………………………………18. 圖 3. 3 (a) n 型輸入差動對(b) p 型輸入差動對…………………………………21 圖 3. 4. 採用的雙級組態運算放大器電路圖……………………………………22. 圖 3. 5. 增益對頻率響應圖………………………………………………………23. 圖 3. 6 相位邊際值 phase margin…………………………………………………23 圖 3. 7. PSRR……………………………………………………………………24. 圖 3. 8. PTAT 電壓的產生………………………………………………………25. VII.

(10) 圖 3. 9. ∆VBE 跨壓在 R1…………………………………………………………25. 圖 3. 10. PTAT 電流………………………………………………………………25. 圖 3. 11. PTAT 電流………………………………………………………………26. 圖 3. 12. ∆VBE 對溫度變化的模擬…………………………………………………27. 圖 3. 13. ∆VBE 與溫度關係的模擬圖………………………………………………27. 圖 3. 14. PTAT 電流的模擬圖……………………………………………………28. 圖 3. 15. CTAT 電流………………………………………………………………29. 圖 3. 16 PTAT 與 VBE / R2 …………………………………………………………29 圖 3. 17. CTAT 電流與溫度的模擬圖……………………………………………29. 圖 3. 18 用電流模式來執行 VBE ( PTAT ) − 0.79VBE (CTAT ) ………………………30 圖 3. 19 Vref 模擬結果……………………………………………………………31 圖 3. 20 Vref 與供應電壓的關係圖………………………………………………32 圖 3. 21. 啟動電路…………………………………………………………………33. 圖 3. 22 啟動電流與 Vp 的關係圖………………………………………………33 圖 3. 23. 暫態模擬(a)(b) …………………………………………………………34. 圖 3. 25. 完整電路圖………………………………………………………………35. 圖 4. 1. (a)參考電壓的溫度誤差(MAPLE 模擬) ………………………………37 (b)電路設計之參考電壓(PSPICE) ……………………………………37. VIII.

(11) 表格索引 表 3. 1. 不同運算放大器架構的效能比較………………………………………20. 表 4. 1. 相關論文的比較…………………………………………………………37. IX.

(12) 第一章 緒論. 1.1 背景簡介 在我們的日常生活中,溫度扮演著極重要的角色,自十八世紀工業革命以 來,科技與工業的發展對是否能夠掌握溫度有絕對的關係。 一開始,溫度只是個相對的概念,很燙或很冰,後來我們定義水的三相點 為 0℃,水的沸點為 100℃,以此為參照點,其它的度數測量水的體積,然後在 這兩個基準溫度的體積間做 "線性" 內插,得其溫度。隨著物理的進展,由 Kelvin 提出絕對溫度的定義,是由卡諾定理來的這是由可逆熱機的(最佳)效率定出來 的,因為這效率與物質無關,所以溫度才能是個用諸天下皆準的物理量。 不過在一般日常生活中或是工業上,使用溫度計(溫度感測器)來獲得溫 度還是比較方便經濟。像水銀溫度計的水銀體積,對溫度的變化雖然不是線性, 但在量測室內溫度,這樣的誤差在容忍的範圍內,精確度也算足夠了。而工業用 或是日常電器用品則需要電子式溫度感測器,而電子式溫度感測器依量測可分類 為圖 1.1 所示。. 圖 1. 1 電子式溫度感測器分類圖. 非接觸式通常採用紅外線(熱輻射)技術量測溫度,可以不接觸到待測物, -1-.

(13) 即能擷取到待測物表面溫度的特性,可用來量測無法接觸的高溫物體,或像之前 SARS 流行,拿來量測體溫可以避免與病人接觸,比較衛生,不易造成病菌傳染。 工業界為了低價、低功率、體積小,而使用接觸式的微型溫度感測電路, 熱電偶是最多人使用的,它簡單而且溫度範圍廣,它是由兩種不同材質的金屬或 合金組合成探頭(如 K 型探頭:鉻/鎳合金) ,不同溫度,金屬之間會產生不同電 壓差(電動勢),再依據電壓大小來判斷被測物之溫度,熱電偶的感測溫度範圍 廣,美中不足的是不能微縮到積體電路中。 隨著工業與科技的進展,自動控制為現代人帶來很多好處,而感測器是自 動控制的關鍵核心,感測器不僅有溫度感測器,還包括壓力感測器、光感測器、 磁性感測、生物化學感測器[1],然而不是半導體型態的感測器不能夠微縮到現代 的電子產品中,如此會導致成本的提高。而我們考慮到積體電路微縮的越來越 小,例如:個人電腦的核心-中央處理器(CPU) ,從幾年前的 0.35um 製程一直微 縮到現在的 90 奈米製程。die 的尺寸雖然變小,但是操作頻率越快,晶片也愈來 愈燙,散熱鰭片跟風扇都必須更要求,熱(溫度)成為晶片最大的殺手。如果晶 片有內建溫度感測器電路來偵測晶片溫度過高,因而暫停整個系統的工作,或是 降低工作時脈,則可以避免晶片過熱燒毀。在日常生活中也可以應用的非常廣 泛,從空調、冰箱、烤箱等家電產品到電腦、電子設備,還有自動化生產設備, 精密儀器等。所以溫度感測系統的研究和科技息息相關、密不可分,探討溫度感 測器實在是刻不容緩。. 1.2 動機 一個溫度感測系統的設計包括了前端的溫度感測電路和一個參考電壓源, 比較兩個的輸出電壓大小之後,就可以得知系統所處的溫度,也可以在後端加上 一個類比數位轉換器(A/D converter)來得到數位訊號,如圖. 1. 2 所示。而我們 希望對前端類比的部分,也就是溫度感測電路與參考電壓源,做些探討以及改進。. -2-.

(14) 圖 1. 2 溫度感測系統. 所以本文是打算用台積電 CMOS 製程來製作一個積體化的溫度感測器電路的前 端。 此外,溫度感測器電路前端所含的能帶隙參考電壓源,也是廣泛的應用於 類比與數位電路中,如:動態隨機處理記憶體(DRAM)與快閃記憶體(Flash Memory),因為能帶隙參考電壓源可以提供一個穩定的電壓,不隨溫度、供應電 壓、以及製程的變化而改變電壓值,使得輕薄短小、便於攜帶的個人電子產品在 上山下海的惡劣環境下,都可以正常的工作。 例如:首當其衝的就是在類比電路中很常見的偏壓電流(bias current)、偏 壓電壓(bias voltage) ,這些參考電壓源或參考電流源的直流狀態會隨著供應電壓 (supply) 、製程參數、壓力的不同,有小小的變動,而對溫度的不同,就有比較 大的變化,不過對於溫度的影響,有比較明確的探討與定義。這些環境變數往往 影響電路是否能夠正常工作或是表現得不如預期,例如:差動放大對的偏壓電流 是從參考電流源鏡射(mirror)而來的,參考電流源隨溫度、供應電壓一變,電 壓增益也跟著變動。在快閃式記憶體裡,抹除和寫入的動作需要一個高電壓來執 行,為了得到一個精準的高電壓,必須先有一個參考電壓電路來產生基準點,高 電壓為這個參考電壓的 N 倍,電壓太高則放電,電壓太低則充電。 基於以上工業和日常家電對溫度感測器與參考電壓源的需求,再加上 SARS 爆發流行,造成對溫度感測器懷有很大的憧憬,於是開始了這個研究。 -3-.

(15) 1.3 感測器設計原理 基本上,所有的感測系統都是透過轉換子或稱為感測器(sensor)把物理量 的變化轉換成我們比較好量測的變化量(如感測元件的體積、發射電磁波波長、 電阻或電壓等形式),比較一個不會隨著變化的參照點,最好能夠再以一轉換電 路和放大電路轉換成比較好量測的電壓輸出(類比輸出) ,其方塊圖如圖 1. 3 所 示。若要再得到數位輸出,就要在後端接一個類比數位轉換器。. 圖 1. 3 感測器示意圖. 在互補式金氧半導體製程(CMOS)下,有三種電路元件可以被使用來當作 溫度感測器(sensor):[2] 1.金氧半場效電晶體(MOSFET)操作在次導通區(sub-threshold region); 2.橫向雙載子接面電晶體(lateral BJT)操作在順向主動區(forward active); 3.縱向雙載子接面電晶體(vertical BJT)操作在順向主動區。 其中第 2.3 項為寄生元件(因為在 BiCMOS 製程下,才有雙載子接面電晶體)。 都利用雙載子接面電晶體的基極-射極電壓 VBE ,在順向主動區工作, VBE 幾乎是 溫度的線性函數,以此來當作溫度感測元件,而第 1 項將 MOSFET 操作在次導 通區時,( I D ≅. VGS W kT I D 0 exp( ) ; VGS < VTH + n ,1 < n < 3 ),類似雙載子接 L n(kT / q ) q. 面電晶體的操作在順向主動區。 但 Vittoz 在[3]中提到 MOSFET 操作在弱反轉區,可以用來做溫度感測,然 而因為製程的變異,MOSFET 導通電壓 VTH 變動範圍很大,導通電壓影響溫度參 -4-.

(16) 數劇烈,因此良率很低。而寄生的橫向雙載子接面電晶體則因為從基版(substrate) 漏出的電流太大(相對於縱向雙載子接面電晶體來說)[4],可能到達射極電流 (emitter current)的 50%,而且漏電流很難控制和預估,所以寄生的縱向雙載子 接面電晶體為我們溫度感測元件的最佳選擇。. 圖 1.4 橫向雙載子接面電晶體剖面圖. 圖 1.5 縱向雙載子接面電晶體剖面圖. -5-.

(17) 1.4 論文架構 本篇論文分為四章,分別敘述如下: . 第一章為緒論. . 第二章則對基本的溫度感測器以及參考電壓源的原理做介紹,並且針對設計 考量的條件和效能做討論。. . 第三章是新型態的參考電壓源,主要是探討雙載子接面電晶體的 VBE 與溫度 的關係,利用兩個 VBE 做線性組合,達到溫度的二階補償,設計出一個低溫 度係數的參考電壓源。. . 第四章則是結論,並對溫度感測器的展望以及努力方向作一說明。. -6-.

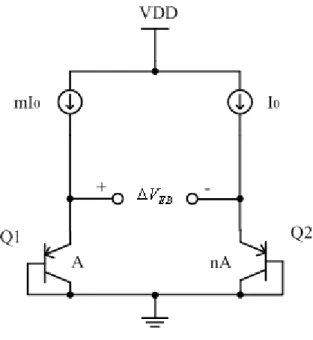

(18) 第二章 基本溫度感測電路與能帶隙參考電壓源. 2.1 傳統溫度感測電路的回顧 我們在 1.3 節中提到:在 CMOS 製程下,比較適合我們採用的溫度感測元 件--縱向雙載子接面電晶體,而我們利用兩個雙載子接面電晶體操作於不同的電 流密度下,其基極--射極電壓的差值( ∆VEB )與絕對溫度成正比[5]。 如果兩個不同的電晶體( Is1 =. 1 Is2 ),均偏壓於相同的集極電流 n. ( Ic1 = Ic2 = I 0 ),如圖 2.1 操作在在順向主動區,我們可以用(2.1) (2.2)來描述雙 載子元件. Ic1 = Is1e. VBE1 VT. Ic2 = Is2 e. VBE 2 VT. (2.1). = nIs1e. VBE 2 VT. (2.2). 其中 VT 為 thermal voltage, VT = 因為 Ic1 = Ic2 = I 0 ⇒ Is1e. VBE1 VT. kT 。 q. = nIs1e. 所以 ∆VBE = VBE1 − VBE 2 = VT ln(n) =. VBE 2 VT. kT ln(n) q. (2.3). 由此可知 ∆VBE 為一正溫度係數的電壓,且正比於絕對溫度(Proportional To. Absolute Temperature ,PTAT)。 在此要注意的是,雖然均偏壓於相同的集極電流( Ic1 = Ic2 = I 0 ) ,但是流入 兩個不同大小的電晶體( Is1 =. 1 Is2 ) ,造成電流密度的不同,使得產生正比於絕 n. 對溫度的 ∆VBE 。這個結果與兩個相同大小的電晶體( Is1 = Is2 ),偏壓於不同集. -7-.

(19) 極電流( Ic1 =. 1 Ic2 ),同樣也是可以得到(2.3)。 n. 圖 2.1 ∆VBE. 想得到 ∆VBE ,於是在 Q2 上串聯一個電阻 R1,如圖 2.2。若能使 V1=V2,則 可得: ∆VBE 跨在 R1 上,流經電阻的 PTAT 電流等於 I = 鏡取出這個 PTAT 電流。如圖 2.2 所示。. 圖 2.2 ∆VBE 跨壓在 R1. -8-. kT / q ln(n) ,再透過電流 R1.

(20) 圖 2.3 PTAT 電流. 要能得到 PTAT 電路,在選擇 R1 上必須使得 V1=V2(圖 2.2 中)。或者使用 一個操作放大器(op-amp),由於開路電壓增益很大,透過迴授,輸入端幾乎虛 短路(virtual short) ,也可以使 V1=V2,如圖 3.11,不過這部分將在後面做說明。 如圖 2.3 為我們的 PTAT 電路。因為 NPN 電晶體的 VBE 對溫度變化大,所以 我們使用 NPN 電晶體。採用電流鏡取出經過電阻的 PTAT 電流後,將 PTAT 電 流導入 Rptat ,就可以得到 PTAT 電壓( Rptat=50K=30R1 ),如圖 2.4。. -9-.

(21) 圖 2.4 PTAT 電壓. 2.2 傳統能帶隙參考電壓源的回顧 由[6]可知. ∂VEB VT Ic V Eg = ln − (4 + m) T − 2 VT ∂T T Is T kT =. (2.4). VEB − (4 + m)VT − Eg / q T. 假設 VEB =750mV,. ∂VEB ∂T. (2.5). 750 − 1200 = −1.5 mV / K 300. 以上的估算可知, VEB 為一負溫度係數的電壓。. - 10 -.

(22) 我們有了正溫度係數的電壓 ∆VEB ,也有了負溫度係數的電壓 VEB ,將這兩個電 壓來做溫度的補償,將可以得到一個不隨溫度變化的參考電壓。 令 Vref=VEB + M • ∆VEB. (2.6). 可以補償得到一階溫度補償的能帶隙參考電壓源,而 Vref 經過溫度的一階補 償,所以對溫度作圖,應該可以得出一個二次的溫度函數。. 圖 2.5 能帶隙參考電壓源原理. - 11 -.

(23) 圖 2.6 溫度感測電路與參考電壓源. 圖 2.7 佈局圖. - 12 -.

(24) 2-3 模擬結果 圖 2.6 為我們模擬的電路,採用 TSMC 0.25um 1P5M 製程參數。 溫度感測電路方面,PTAT 電流對溫度的變化為 0.07 uA/℃,PTAT 電壓對 溫度的變化為 3.6mV/℃。 從圖 2.10 的模擬結果可以看出 Vref 約為 1.21V。等效溫度係數的定義公式 [7],TCF (eff ) =. 1 VMAX − VMIN ( ) Vout TMAX − TMIN. (2.6). 求出我們的參考電壓溫度係數為 8.3ppm/℃。. 36 34. Iptat ,uA. 32 30 28 26 24 22 -40. -20. 0. 20. 40. 60. 80. temp (℃). 圖 2.8 PTAT 電流. - 13 -. 100. 120. 140.

(25) 1.8 1.7. Vptat, V. 1.6 1.5 1.4 1.3 1.2 1.1 -40. -20. 0. 20. 40. 60. 80. 100. 120. 140. 120. 140. temp (℃). 圖 2.9 PTAT 電壓(R2=50K). 1.2110. Vref ,V. 1.2105. 1.2100 1.2095. 1.2090 -40. -20. 0. 20. 40. 60. 80. temp (℃). 圖 2.10 參考電壓對溫度關係圖. - 14 -. 100.

(26) 第三章 新型能帶隙參考電壓源. 3-1 理論基礎 本節將從理論面探討一個新型能階差參考電壓源的可行性,以及瞭解此參 考電壓源的二階溫度補償工作原理。首先,我們要了解溫度感測元件中的雙載子 接面電晶體隨溫度變化的物理特性,我們從[7]( p.11)中可得:. 圖.3.1 BJT. Ic = Is ⋅ e. Is = qA. VEB VT. Dn ni 2 D n2 = qA n i W • NA QB. 其中 Ic = 集極電流 (A) ,VBE = 基極到射極電壓 (V). VT =. kT ,k=1.38 • 10-23 (J/K) ,q=1.6 • 10-19 (C) ,T為絕對溫度 (K) q. A = 射極的截面積 W = 基極的寬度, N A = 基極的參雜濃度. QB = 每單位射極面積的基極參雜原子數. Dn = 平均電子擴散常數 ni = Si 的本質載子濃度 Is 的典型值為 10−14 ~ 10−16 ( A) - 15 -. (3.1) (3.2).

(27) 由 Einstein relation: un = (. q kT ) Dn ⇒ Dn = un kT q. (3.3). un = 電子平均遷移率 所以(3. 2)式可以改寫為 Is =. A kT • un (T )ni 2 WQB. (3.4). 再由[7] (p.382)可得(3.5) , (3.6) ,(3.7). un (T ) ~ u0T m. 3. ni (T ) ~ T e. −. (3.5). Eg kT. (3.6) −. Eg kT. 由(3.1)式:可得 VEB =VT ln. Ic Is. 所以把(3.4) ⇒ Is = bT. m+4. e. (3.7). (3.8). 再把 VEB 跟溫度有關的參數萃取出來,將(3.7)式代入(3.8)中得到. VEB (T ) =. kT Ic k Eg ln − (4 + m)T ln T + q b q q. (3.9). Eg 的能帶隙也會隨絕對溫度改變 ∵VG (T ) =. Eg (T ) q. ∴VEB (T ) =. kT Ic k ln − (4 + m)T ln T + VG (T ) q b q. (3.10). 令m + 4 =η. VEB (T ) =. kT Ic k ln − (η )T ln T + VG (T ) q b q. (3.11). 假設 Ic=a • Tθ. θ = 0 ⇒ Ic 為不隨溫度變化的定電流(Constant to Absolute Temperature ,CTAT) θ = 1 ⇒ Ic 為一次線性正比於溫度的電流(Propose to Absolute Temperature ,PTAT). - 16 -.

(28) 所以(3.11) ⇒ VEB (T ) =. kT a k ln − (η − θ )T ln T + VG (T ) q b q. (3.12). a b 這兩個數很難得到,我們用 VEB (Tr ) 在 T = Tr 時,VEB (Tr ) = 所以 ln. kTr a k ln − (η − θ )Tr ln Tr + VG (Tr ) q b q. ⎤ a q ⎡ k VEB (Tr ) + (η − θ )Tr ln Tr − VG (Tr ) ⎥ = ⎢ b kTr ⎣ q ⎦. (3.13) (3.14). 將(3.14)代入(3.12)把 a b 消掉可得. VEB (T ) =. ⎤ k T ⎡ k VEB (Tr ) + (η − θ )Tr ln Tr − VG (Tr ) ⎥ − (η − θ )T ln T + VG (T ) ⎢ Tr ⎣ q ⎦ q. 從新整理一下: VEB (T ) = VG (T ) − [VG (Tr ) − VEB (Tr ) ]. T kT T − (η − θ ) ln Tr q Tr. (3.15). 此時,VEB 對溫度的函數關係式就得出了,因為我們想做出一個二階溫度補 償的參考電壓源,所以我們要找出 VEB (T ) 對絕對溫度的一次項及二次項係數,想 辦法補償掉最主要也是造成溫度變化最大的這兩個係數,那麼補償完的 VEB (T ) 只 剩溫度的三次項係數,也就幾乎不隨溫度變動,即可成為一個不隨溫度變化的參 考電壓源。接下來,我們對 VEB (T ) 在 T = Tr 附近做泰勒展開(展到二次項即可)。 泰勒級數展開式: f ( x) = f ( x0 ) + f '( x0 )( x − x0 ) +. 1 f ''( x0 )( x − x0 ) 2 + ...... 2!. (3.16). (3.15)式每一項分別各自展開:. ⎡ ∂VG 1 ∂ 2VG 2⎤ |T =Tr (T − Tr ) + | VEB (T ) = ⎢VG (Tr ) + T − Tr ) ⎥ 2 T =Tr ( 2 ∂T ∂T ⎣ ⎦ V (Tr ) − VG (Tr ) 0 ⎧ ⎫ + ⎨[VEB (Tr ) − VG (Tr ) ] + EB (T − Tr ) + (T − Tr ) 2 ⎬ 2! Tr ⎩ ⎭ 2 ⎧⎪ kTr T − Tr ) ⎫⎪ ⎤ ( Tr ⎡ k Tr k k -⎨ (η − θ ) ln + ⎢ (η − θ ) ln + (η − θ ) ⎥ (T − Tr ) + (η − θ ) ⎬ Tr 2q Tr ⎣ q Tr q ⎦ ⎪⎩ q ⎪⎭. 合併後得到:. ⎡ ⎤ T − Tr ∂V kTr ⇒ VEB (T ) = VEB (Tr ) + ⎢VEB (Tr ) − VG (Tr ) + G |T =Tr •Tr − ) (η − θ )⎥ ( q ∂T ⎣ ⎦ Tr (3.17) ⎤ T − Tr 2 kTr 1 ⎡ 2 ∂ 2VG + ⎢Tr |T =Tr − (η − θ ) ⎥ ( ) ∂T 2 2⎣ q ⎦ Tr - 17 -.

(29) 令 VEB (T ) = VEB (Tr ) + [VEB (Tr ) − VG '] ( 則其中 VG ' = VG (Tr ) − B2 (θ ) =. T − Tr T − Tr 2 ) + B2 (θ )( ) Tr Tr. ∂VG kTr |T =Tr •Tr + (η − θ ) q ∂T. (3.18) (3.19). ⎤ kT 1 ⎡ 2 ∂ 2VG − r (η − θ ) ⎥ | ⎢Tr 2 T =Tr q ∂T 2⎣ ⎦. (3.20). 假設如 圖.3.2(a) 所示,兩個 VEB (不同形式的 Ic 流入 BJT 造成的)線性組合成 一個不隨溫度變化的參考電壓源,. vref (T ) = a1VEB (T ) + a2VEB (T ). (3.21). 如圖.3.2(a),將 A1 歸一化後,亦可以得到一個不隨溫度變化參考電壓源,只是電 壓值不一樣大而已,所以我們可以去除考慮 A1 的影響,僅剩 a2 一個因子。 令 Vref (T ) = VEB1 (T ) + a2VEB 2 (T ) . (3.22). 圖.3.2(a). ∂Vref (T ). 圖 3.2(b). ∂VEB1 (T ) ∂V (T ) + a2 EB 2 =0 ∂T ∂T ∂T 1 2(T-Tr) [ B2 (θ1 ) + a2 B2 (θ 2 )] = 0 ⇒ [VEB1 (Tr ) − VG1 '+ a2VEB 2 (Tr ) − a2VG 2 '] + Tr 2 Tr. 則. =. (3.23) (3.24). (3.24)式 為一個 T 的一次方程式(C․T+D=0),所有的 T 都要滿足,唯一的條件 就是 C= 0,D= 0,所以得到下列兩個條件:. - 18 -.

(30) VEB 2 (Tr ) − VG1 '+ a2VEB 2 (Tr ) − a2VG 2 ' = 0. (3.25). B2 (θ1 ) + a2 B2 (θ 2 ) = 0. (3.26). 由(3.26)式可得: B2 (θ1 ) = −a2 B2 (θ 2 ) 或 a2 = −. B2 (θ1 ) B2 (θ 2 ). (3.27). ∂ 2VG |T =Tr 這個數值,來計算 B2 (θ1 ) B2 (θ 2 ) 這兩個不同型態 VBE 的二 (3.20)式中需要 ∂T 2 次項溫度係數。 我們採用[8]的 VG 的溫度模型: VG (T ) = VG 0 −. αT 2 T +β. (3.28). 其中 VG 0 為 0 K 時的 Silicon 能帶隙電壓( 1.17 eV ), α = 4.73 ×10−4 , β = 636 ∂ 2VG ∂ 2 αT 2 2α 4α T 2α T 2 = = − + ( ) ∂T 2 ∂T 2 T + β T + β (T + β ) 2 (T + β )3. (3.29). ∂ 2VG |T =300 K = −4.67 ×10−7 ∂T 2 B2 (θ ) =. ⎤ 1 kT 1 ⎡ 2 ∂ 2VG − r (η − θ ) ⎥ = [−4.2 × 10−2 − 0.0259 × (3.2 − θ )] | ⎢Tr 2 T =Tr ∂T q 2⎣ ⎦ 2. (3.30). B2 (1) = −0.049, B2 (0) = −0.062 由(3.27) ⇒ a2 = −0.79. 接下來,我們就可以從(3.18) ,(3.22)得到:. T − Tr T − Tr 2 ) + B2 (θ1 )( ) Tr Tr T − Tr T − Tr 2 ⎤ ⎡ ) + B2 (θ 2 )( ) ⎥ − a2 ⎢VEB 2 (Tr ) + [VEB 2 (Tr ) − VG 2 '] ( Tr Tr ⎣ ⎦. Vref = VEB1 (Tr ) + [VEB1 (Tr ) − VG1 '] (. =VEB1 (Tr ) − a2VEB 2 (Tr ). (3.31). 再由(3.25)知: VEB1 (Tr ) + a2VEB 2 (Tr ) = VG1 '+ a2VG 2 '. ∴Vref = VG1 '+ a2VG 2 '. (3.32). 約略估計 Vref ≈ 0.21 • VG (Tr ). (3.33). - 19 -.

(31) = 246mV. 從推導的過程中,我們可以發現用 Ic = PTAT 的 VEB1 (T ) ,減去 Ic = CTAT 的. 0.79 • VEB 2 (T ) ,即可得到一個參考電壓源 Vref ≈ 0.21 • VG (Tr ) ,由於做了二階的溫 度補償,所得到的 Vref 對溫度作圖應該是三次的曲線。. 3-2 電路實現 要完成上述理論的電路,我們需要利用到幾個子電路:運算放大器 (OP-AMP)、PTAT、CTAT、啟動電路(Start-up),將分別在底下一一介紹,模 擬參數皆是採用 TSMC 0.18um 製程、VDD = 1.8V 的模型來模擬。. 3-2-1 運算放大器(OP-AM). 伸縮組態. (Telescopic) 折疊串接組態. (Folded Cascode) 雙級組態. (two-stage) 增益拉高組態 (Gain boosted). 增益. 輸出擺幅. (Gain). (Output Swing) (Speed). 速度. 功率消耗 雜訊. (Power). (Noise). 中. 中. 最高. 低. 低. 中. 中. 高. 中. 中. 高. 最高. 低. 中. 低. 高. 中. 中. 高. 中. 表 3.1 不同運算放大器架構的效能比較. 為了設計出符合我們所需求的運算放大器,必須在各種不同架構中選取一 個效能比較合適的(如 表 3.1) ,因為我們的電路不是工作在高頻段,僅需考慮 DC 直流狀態或低頻段,所以速度要求不高,而且雙級架構的增益以及輸出擺幅 - 20 -.

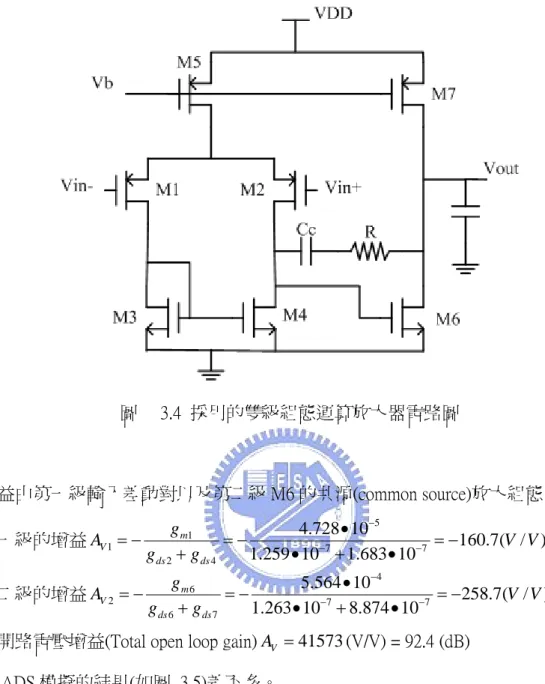

(32) 都很高,綜合各種效能的取捨(trade-off),最終我們選擇雙級架構來實現運算放大 器。 運算放大器的輸入端,幾乎都是連接到 VEB ,也就是 diode-connected 的 PNP BJT,考慮到 VEB 對溫度的變化,從最高 0.91V(-40℃)到最低 0.53V(125℃), 所以輸入共模範圍(ICMR ,input common mode range)一定要涵蓋這一段區間。 如圖 3.3(a) n 型輸入差動對(input differential pair)最低輸入電壓至少要. VDS ( sat ) + VGS = 0.2 + 0.45 (VTH _ n ) = 0.65(Volt ) ,所以只能採用 p 型輸入差動對,而 p 型輸入差動對最高輸入電壓為. VDD − VDS ( sat ) − VGS = 1.8 − 0.2 − 0.5 (VTH _ P ) = 1.1(Volt ) ,如圖 3.4 為我們運算放大 器的電路圖,而最低輸入電壓為. GND + Vov 3 + VTH 3 − VTH 1 = 0 + 0.07 + 0.45 − 0.5 = 0.02(Volt ) 所以我們採用的雙級組態運算放大器涵蓋住 VBE 對溫度的變動範圍。. 圖 3.3(a) n 型輸入差動對 圖 3.3(b) p 型輸入差動對. - 21 -.

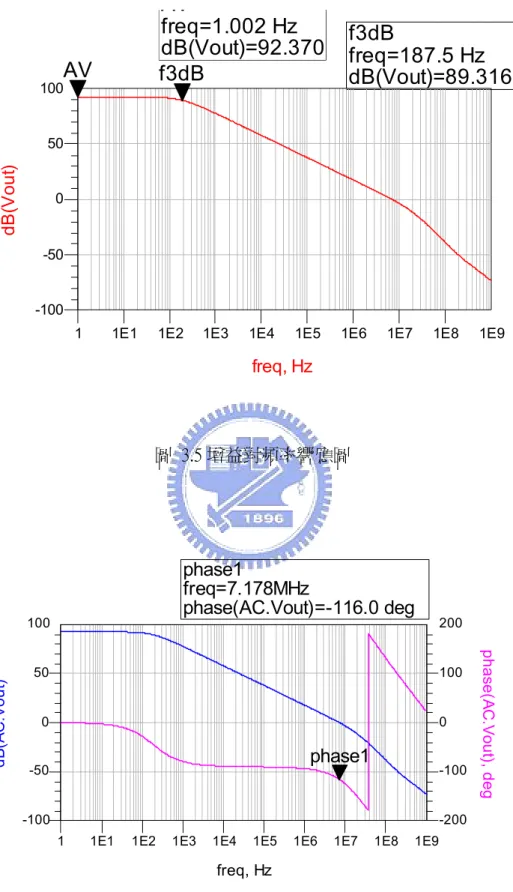

(33) 圖 3.4 採用的雙級組態運算放大器電路圖. 增益由第一級輸入差動對以及第二級 M6 的共源(common source)放大組態。 第一級的增益 AV 1 = −. g m1 4.728 • 10−5 =− = −160.7(V / V ) g ds 2 + g ds 4 1.259 • 10−7 + 1.683 • 10−7. 第二級的增益 AV 2 = −. gm6 5.564 • 10−4 =− = −258.7(V / V ) g ds 6 + g ds 7 1.263 • 10−7 + 8.874 • 10−7. 總開路電壓增益(Total open loop gain) AV = 41573 (V/V) = 92.4 (dB) 與 ADS 模擬的結果(如圖 3.5)差不多。 相位邊際值(Phase margin)接近 65°,如圖 3.6 所示。 PSRR(power supply rejection ratio)為 102dB. - 22 -.

(34) AV freq=1.002 Hz dB(Vout)=92.370 f3dB. AV. 100. f3dB freq=187.5 Hz dB(Vout)=89.316. dB(Vout). 50. 0. -50. -100 1. 1E1. 1E2. 1E3. 1E4. 1E5. 1E6. 1E7. 1E8. 1E9. freq, Hz. 圖 3.5 增益對頻率響應圖. phase1 freq=7.178MHz phase(AC.Vout)=-116.0 deg. 50. 200. 100. 0. 0. phase1. -50. -100. -100. -200 1. 1E1. 1E2. 1E3. 1E4. 1E5. 1E6. 1E7. freq, Hz. 圖 3.6 相位邊際值 phase margin. - 23 -. 1E8. 1E9. phase(AC.Vout), deg. dB(AC.Vout). 100.

(35) PSRR dB(AC.VDD/AC.Vo). 120 100 80 60 40 20 1. 1E1. 1E2. 1E3. 1E4. 1E5. 1E6. 1E7. 1E8. 1E9. freq, Hz. 圖 3.7 PSRR. 3-2-2 PTAT 在前一章提到,我們採用 P 型的寄生縱向雙載子電晶體(vertical PNP)來當 作溫度感測元件,我們已經知道電晶體在主動區(forward-active)工作時,. VEB 是負的溫度係數 ,但是在 1964 年,[6]如果兩個雙載子電晶體通入不同的電 流密度之下,其 ∆VEB 和絕對溫度成正比。以圖 3.8 為例,. Ic1 = Is1e. VEB1 VT. 同理, Ic2 = Is2 e. (3.34) VEB 2 VT. = nIs1e VEB1. VEB 2 VT. (3.35) VEB 2. 因為 Ic1 = mIc2 ⇒ Is1e VT = mnIs1e VT 所以 ∆VEB = VEB1 − VEB 2 = VT ln(mn) =. kT ln(mn) q. (3.36). k 因此, VEB 的差異與絕對溫度成正比。而且它的正溫度係數 ln(mn) ,為一個與 q 溫度無關的恆定值,只跟 m ,n 這兩個比例常數有關。. - 24 -.

(36) 圖 3.8 PTAT 電壓的產生 要變成實際可以利用的電路,首先必須如圖 3.9 所示,必須確保 V1=V2,方 法為加入前一節所設計的運算放大器,將 V1 ,V2 分別接到負正輸入端,經過迴 授後,幾乎可以視為虛短路(virtual short) 。另一個方法為在電流鏡電流源(mI0 ,I0) 下,再串接一個電流鏡,串接的電流鏡則可以視為一個簡單的放大電路(如圖 3.10),不過在此不贅述。. VDD. m. :. 1 M5 M2. M1. m. :. 1 M4. M3. PTAT電流 R1. Q2. Q1 A. 圖 3.9 ∆VEB 跨壓在 R1. nA. 圖 3.10 PTAT 電流. - 25 -.

(37) 確 保 V1 = V2 後 , 跟 絕 對 溫 度 成 正 比 的 ∆VEB 會 跨 在 電 阻 R1 上 , 則. R1 I = ∆VEB = I=. kT ln(mn) , 所 以 可 以 得 到 一 個 與 絕 對 溫 度 成 正 比 的 電 流 q. kT / q ln(mn) ,再透過電流鏡取出這個 PTAT 電流。如圖 3.11 所示,為我們的 R1. PTAT 最終電路圖。 模擬的結果: VEB 和 ∆VEB 對溫度的變化如圖 3.11 和圖 3.12,由於 R1 也有溫 度係數,R1 對溫度的變化會造成 PTAT 電流輸出很大的影響,所以我們以 poly 電阻(負溫度係數)跟 diffusion 電阻(正溫度係數)的串聯來當 R1,使得 R1 的 溫度係數變化較小。 從圖 3.14 可看出,PTAT 電流幾乎等於 aT,也就是通過(0uA ,0K)的原點。 雖然溫度係數 a=+0.028uA/℃,但是只要加大 M3 的通道寬度(width)即可加大電流 與溫度的斜率 a,有了這個 PTAT,只要量測到 PTAT 電流,即可知道環境的絕 對溫度。. 圖 3.11 PTAT 電流 - 26 -.

(38) 1.0. Vbe2, V Vbe1, V. 0.9 0.8 0.7 0.6 0.5 -40. -20. 0. 20. 40. 60. 80. 100. 120. 140. temp ℃. 圖 3.12. VEB 對溫度變化的模擬. Veb1-Veb2 Vbe1-Vbe2 ,V. 0.14 0.13 0.12 0.11 0.10 0.09 0.08 0.07 -40. -20. 0. 20. 40. 60. temp. 80. 100. ℃. 圖 3.13 ∆VEB 與溫度關係的模擬圖. - 27 -. 120. 140.

(39) I_Probe1.i, uA PTAT 電流. 12 11 10 9 8 7 6 5 4 3 2 1 0 140 120. 80. 40. 0. -40. -80. -120. -160. -200. -240. -280. temp ℃. 圖 3.14 PTAT 電流的模擬圖. 3-2-3 CTAT(constant to absolute temperature) 利用上述求得之正溫度係數的電流(PTAT),再設計一個負溫度係數的電流 來補償,就可以發展出具有零溫度係數的電流(CTAT),從上一節的圖 3.12 可 以得到 VEB 是負溫度係數的電壓,再跨壓在一個零溫度係數的電阻 R2 上(零溫 度係數的電阻我們依然使用正溫度係數的 diffusion 電阻和負溫度係數的 poly 電阻 來串聯而成),就可以得到一個負溫度係數的電流 把 PTAT 電流. VEB 。 R2. kT / q V ln(mn) 加上負溫度係數的電流 EB ,補償可得一個 R1 R2. CTAT,電路圖如圖 3.15,使用 ADS 模擬結果如圖 3.16 和圖 3.17。. - 28 -.

(40) 圖 3.15 CTAT 電流. I_Probe4.i, uA I_Probe3.i, uA. PTAT temp=-22.000 I_Probe3.i=7.705uA 13 12 11 10 9 8 7 6 5 4 3 2 1 0. IVbe temp=121.000 I_Probe4.i=8.195uA IVbe. PTAT. -40. -20. 0. 20. 40. 60. temp. 80. ℃. 圖 3.16 PTAT 與 VEB / R2. - 29 -. 100. 120. 140.

(41) 20.4. CTAT 電流 I_Probe1.i, uA. 20.2 20.0 19.8 19.6 19.4 -40. -20. 0. 20. 40. 60. 80. 100. 120. 140. temp ℃. 圖 3.17 CTAT 電流與溫度的模擬圖. 3-2-4 用電流模式(current mode)來執行 VEB ( PTAT ) − 0.79VEB (CTAT ) 做出 PTAT 以及 CTAT 之後,可以開始完成我們想驗證理論的電路,如圖 3.18 所示,PTAT 電流流入 Q1 產生 VEB1,CTAT 電流流入 Q3 產生 VEB 3 ,利用運算 放大器將 VEB1 轉換成電流. V VEB1 ,同理 VEB 3 轉換成電流 EB 3 。 R3 R4. 圖 3.18 用電流模式來執行 VBE ( PTAT ) − 0.79VBE (CTAT ) - 30 -.

(42) 從 M9 的源極流出 ,所以 Vref = (. V VEB1 ,從 M14 的汲極流入 EB 3 ,電流相減流入 R5 R3 R4. VEB1 VEB 3 − ) • R5 R3 R4. (3.37). 令 R3 = R5 = 0.79 R4 ,則可以實現 Vref = VEB1 − 0.79VEB 3 其中 R3 , R4 , R5 的溫度係數與 Vref 無關,電阻的溫度特性不會影響到我們的參考 電壓。. m3 temp=85.0000 Vout=255.24mV. m1 temp=-40.0000 m1 Vout=255.38mV. 255.4. 255.3. Vref, mV. m4 temp=125.0000 m3 Vout=255.12mV. m2 temp=6.0000 Vout=255.05mV. 255.2. m4 m2. 255.1. 255.0 -40. -20. 0. 20. 40. 60. 80. 100. 120. 140. temp ℃. 圖 3.19 Vref 模擬結果 從模擬結果可以看出 Vref 約為 255.1mV。等效溫度係數的定義公式[7] pp.321,. TCF (eff ) =. 1 VMAX − VMIN ( ) Vout TMAX − TMIN. 我們的參考電壓溫度係數為 7.8ppm/℃,而充飽的精密電池溫度係數大約為 ±30 ppm/℃. - 31 -.

(43) 3-2-5. 啟動電路 start-up. 在電路圖 3.18 中,輸出電壓和供應電壓的相關係極低(圖 3.20)。此電路可能 需要一個啟動電路(start-up) ,因為 VX 、VY 可能等於零,而且運算放大器的輸入 差動對會關閉,輸出端會是 VDD,也就是 M1、M2 的閘極變成 VDD,電流全部 關閉成為另一個穩定態,所以我們加入一個啟動機制(圖 3.21)。. 257.5. Vref, mV. 257.0 VDD=2.200 V. 256.5 256.0. VDD=2.000. 255.5. VDD=1.900. 255.0. VDD=1.800 VDD=1.750. 254.5 -40. -20. 0. 20. 40. 60. temp. 80. 100. 120. 140. ℃. 圖 3.20 Vref 與供應電壓的關係圖. 假設整個電路都在關閉的狀態下,M1、M2 的閘極電壓 Vp 為 VDD 也就是 V High,經過一個反相器變成 Low,Vq = low 打開 M18 的啟動電流,於是啟動 Q1,. VBE1 是運算放大器的負輸入端,所以運算放大器的輸出端就降下來,M1、M2 也 被打開,整個電路就可以在預想的工作點工作。 在預想的工作點下,Vp = 1.1V,而起動電路必須在完成任務之後關掉 M18 的啟動電流,以免影響原來的電路,所以反向器底下再串疊兩個 MOS 電晶體來 增加位準,使得反向器在 Vp =Low(1.45V)時,Vq 電壓反轉成 High(1.8V), 關掉 M18 的電流,模擬如圖 3.22。 - 32 -.

(44) 圖 3.21 啟動電路. M18電流, uA. 15. 10. 5. 0 0.9. 1.0. 1.1. 1.2. 1.3. 1.4. 1.5. 1.6. 1.7. Vp, V. 圖 3.22 啟動電流與 Vp 的關係圖 - 33 -. 1.8.

(45) 暫態模擬,將 VDD 在時間 T = 50 nsec 打開,上升時間(rise time)為 1 usec 如圖 3.23(b),可以得到圖 3.23(a): Vref 的暫態響應。. 300. Vref, mV. 250 200 150 100 50 0 0.0. 0.2. 0.4. 0.6. 0.8. 1.0. 1.2. 1.4. 1.6. 1.8. 2.0. time, usec. 圖 3.23 暫態模擬(a). 2.0. VDD, V. 1.5. 1.0. 0.5. 0.0 0.0. 0.2. 0.4. 0.6. 0.8. 1.0. 1.2. time, usec. 圖 3.23 暫態模擬(b). - 34 -. 1.4. 1.6. 1.8. 2.0.

(46) - 35 -. 圖 3.25 完整電路圖.

(47) 第四章 總結與未來展望. 4-1 總結 我們從半導體物理理論著手,探討出雙載子接面電晶體基極與射極間的電 壓差與溫度的關係,並且對溫度做二次泰勒級數展開,找出 VEB (T ) 對絕對溫度的 一次項及二次項係數,最後再以 a2 = −0.79 的線性組合補償 PTAT 偏壓的 VEB (T ) 與. CTAT 偏壓的 VEB (T ) ,一次項及二次項的溫度係數補償掉後,得到一個與溫度呈 三次方關係的參考電壓。 再者,採用 TSMC 0.18um 1P6M 的製程參數來模擬、驗證我們的理論。首 先設計了一個 PTAT 電流,以及 CTAT 電流,分別偏壓在 VEB1 、VEB 2 ,再將 VEB1 、. VEB 2 轉換成電流模式,執行以 a2 = −0.79 的比例補償,從模擬結果可以看到我們 設計的參考電壓為一個三次曲線,當 VDD=1.8V 時,從-40℃到 125℃的溫度範圍, 溫度係數為 7.8 ppm/℃,消耗的電流為 408uA,消耗的功率為 0.73mW(在 25℃)。 參考文獻[9]在 2001 年提到兩種不同偏壓的 VEB 之和來達到溫度的二階補 償,經過數學模擬軟體計算後,得到 a1 = 0.8286549, a2 = −0.6523162 ,參考電壓 為 200mV,從 0℃~100℃的溫度係數為 0.09ppm/℃,後來用商用的雙載子接面電 晶體 MAT-01,實驗得到 a1 = 0.62569090, a2 = −0.45360053 ,得到參考電壓為 200mV,從 20℃~100℃的溫度係數為 0.092ppm/℃,不過算是物性上面的研究, 沒有電路的設計。 在參考文獻[10]於 2002 年提出類似的會議論文, a2 算出為-0.8089,再把電 流與溫度的函數輸入 MAPLE,模擬得到溫度係數為 0.8ppm/℃的參考電壓源 Vref= 217.46 mV,如圖 4.1(a),而且提出一電路,在 DIMES03 製程下,用 PSPICE - 36 -.

(48) 模擬得到一個 Vref = 225mV 的參考電壓源,溫度係數等於 3ppm/℃(如圖 4.1.b), 發現比 MAPLE 模擬的結果還差,而且是溫度的二次曲線,作者認為是 PSPICE 的能帶隙(bandgap energy)模型不同,以及電阻的溫度效應所引起的。. 圖 4.1(a)參考電壓的溫度誤差(MAPLE 模擬). (b)電路設計之參考電壓(PSPICE). R, Amador, A. Azarkan, A.; Polanco, A. Nagy, van Staveren, A.; M. Alvarez Fruett, F.. 本文. year. 2001. 2002. 2004. 線性組合(a1,a2). (0.82,-0.65) (0.63,-0.45)*. (1,-0.81). (1,-0.79). 參考電壓 Vref. 200mV. 217mV 225mV*. 255mV. 溫度係數 Tc(eff). 0.09ppm/℃ 0.09ppm/℃*. 0.8ppm /℃ 3ppm /℃. 7.8 ppm /℃. 溫度範圍(℃). 0~100 (20~100)*. (0~120). (-40~125). 註. calculation MAT-01* No circuit. MAPLE PSPICE* 二階溫度函數*. 表 4.1 相關論文的比較. 本文第三章新型的參考電壓源所耗的電流和功率雖然過大,但是創新的架 構算是比較有貢獻的地方。另外,要排除電阻的溫度係數造成的影響,以及 CTAT 不夠完美,否則可能無法到達如表 4.1 所列論文數值計算出的 0.8ppm/℃或是 0.092ppm/℃。. - 37 -.

(49) 4-2 未來展望 一個溫度感測系統的設計包括了前端的溫度感測電路和一個參考電壓源, 和後端的類比數位轉換器。我們已經完成溫度感測系統前端的模擬,未來將以本 篇論文架構作為基礎,再加上後端的類比數位轉換器,完成一個數位輸出的溫度 感測系統。未來也希望透過國家晶片中心的資源,將模擬的結果實現,以證實本 論文的理論。 除了後端可以加上類比數位轉換器外,也可以利用此設計經驗,希望在參 考電壓源上再做最佳化,或往溫度的三階補償邁進,使參考電壓源對溫度更不靈 敏。更精準的參考電壓源在可攜性電子產品的電路或類比數位轉換器是非常迫切 需要的,在日常生活中可以應用的非常廣泛,從空調、變頻式冷氣、冰箱、烤箱、 電子溫度計等家電產品到電腦、電子設備等,均需要數位溫度感測功能讓人類監 看,雖然目前都是白金做的熱電偶來做溫度感測器,不過這些家電裡面幾乎都有 單晶片,如果加溫度感測電路進去晶片內,可使得產品更有競爭力。 也期望本文的電路在未來可以把線路簡化,將功率降低,以期有一天可以 在市面上的產品可以看到它的蹤跡。. - 38 -.

(50) 參考文獻 1.. S. M. Sze, “Classification and terminology of sensors”; Semiconductor Sensors, edited by S. M. Sze, John Wiley & Sons, Inc., pp. 1-15, 1994.. 2.. A. Bakker, J.H. Huijsing, ” Micropower CMOS temperature sensor with digital output,” IEEE Journal of Solid-State Circuits, vol. 31 , Issue: 7 , pp. 933 937, July 1996.. 3.. E.A. Vittoz, O. Neyroud,“A low-voltage CMOS bandgap reference,” IEEE. Journal of Solid-State Circuits, vol. 14 , Issue: 3 , pp.573 - 579 , Jun 1979. 4.. E.A. Vittoz, “MOS transistors operated in the lateral bipolar mode and their application in CMOS technology,” IEEE Journal of Solid-State Circuits, vol. 18 , Issue: 3 , pp.273 – 279, Jun 1983.. 5.. D. Hibiber, ‘A New Semiconductor Voltage Standard,” ISSCC Dig. of Tech.. Papers, pp 32-33, Feb. 1964. 6.. Behzad Razavi, “Design of Analog CMOS Integrated Circuits” McGraw-Hill, 2001.. 7.. Gray, Hurst, Lewis and Meyer, Analysis and Design of Analog Integrated. Circuits, John Wiley & Sons, Inc., 2001 8.. S. M. Sze, Semiconductor devices, physics and technology, John Wiley & Sons, Inc., 1985. 9.. R, Amador, A. Polanco, A. Nagy, M. Alvarez; "Design methods of low-voltage curvature-corrected bipolar bandgap references based on the sum of base-emitter voltages," Archives of the VII Workshop IBERCHIP; Montevideo, Uruguay; March, 2001. 10. A. Azarkan, A. van Staveren, F. Fruett, ”A low-noise bandgap reference voltage. - 39 -.

(51) source with curvature correction,” IEEE International Symposium on Circuits. and Systems, Volume: 3, Pages:III-205 - III-208 vol.3 , May 2002 11. TSMC 0.18µm mixed signal 1P6M salicide 1.8V/3.3V RF spice models, Taiwan. Semiconductor Manufacturing Co. Ltd. 12. J.H. Huijsing, Analog circuit design:low-noise, low-power, low-voltage;. mixed-mode design with CAD tools; voltage, current and time references, Kluwer Academic Publishers, 1996. 13. Andrea Boni, Member, IEEE, ”Op-amps and Startup Circuitsfor CMOS Bandgap. References with Near 1-V Supply”, IEEE Journal of Solid-State Circuits, vol. 37, no. 10, October 2002. 14. A.J. Annema, “Low-power bandgap references featuring DTMOSTs,” IEEE. Journal of Solid-State Circuits, vol. 34, pp. 949-955, July 1999. 15. Shu-Yuan Chin, Chung-Yu Wu, “A New Type of Curvature-compensated CMOS. Bandgap Voltage Reference ”, VLSITSA, 1991. 16. S. L. Lin and C.A.T. Salama, “A Vbe(T) model with application to bandgap. reference design,” IEEE Journal of Solid-State Circuits, vol. SC-20, pp. 1283-1285, Dec 1985. 17. B. S. Song and P. R. Gray, “A Precision curvature-compensated CMOS bandgap. reference,” IEEE Journal of Solid-State Circuits, vol. SC-18, pp. 634-943, Dec 1983. - 40 -.

(52)

數據

![圖 2.4 PTAT 電壓 2.2 傳統能帶隙參考電壓源的回顧 由[6]可知 ln (4 ) 2EBTT TVVIcVEgmV T T Is T kT∂=− +−∂ (2.4) V EB (4 m V) T Eg q/ T− + −=](https://thumb-ap.123doks.com/thumbv2/9libinfo/8063637.163088/21.892.215.683.118.733/PTAT電壓傳統能帶隙電壓源的回顧可知∂=−+−∂V+−=.webp)

相關文件

1997 年 IEEE ELECTRONICS LETTERS 曾有學者 A.Motamed 、 C.Hwang 以及 M.Imail 提出一篇 CMOS Exponential Current-to-Voltage Converter[7],主要 是利用

Abstract - A 0.18 μm CMOS low noise amplifier using RC- feedback topology is proposed with optimized matching, gain, noise, linearity and area for UWB applications.. Good

Hogg (1982), “A State-of-the-art Survey of Dispatching Rules for Manufacturing Job Shop Operation,” International Journal of Production Research, Vol.. Gardiner (1997), “A

等溫電漿應用於電弧熔鍊(Arc Refinement)、電漿融射(Plasma Spraying)及感應偶合電漿分光儀(Inductively Coupled Plasma Optical

第二章是介紹 MEMS 加工製程,包括體型微加工、面型微加工、LIGA、微 放電加工(Micro-EDM)、積體電路相容製造技術 CMOS MEMS 製程等。製作微 加速度感測器。本研究是選用台積電 0.35μm

Sugii, “Junction profile engineering with a novel multiple laser spike annealing scheme for 45-nm node high performance and low leakage CMOS technology,” in IEDM

First we explain how to implement CMOS current-mode quadratic circuits and design the proposed circuit in the way of multiple corrections.. We use the best

The proposed circuit is based on CMOS Current-Mode Quadratic Function Circuits, its W/L ratio and construction could be adjusted by the relative error that the users