國 立 交 通 大 學

電控工程研究所

碩 士 論 文

0.5-V 低電壓類比前端積體電路應用於生醫訊號紀錄

0.5-V Low Voltage Analog Front-End IC for Biomedical

Signal Recording

研 究 生:楊澤勝

0.5-V 低電壓類比前端積體電路應用於生醫訊號紀錄

0.5-V Low Voltage Analog Front-End IC for Biomedical

Signal Recording

研 究 生:楊澤勝 Student : Tze-Zheng Yang

指導教授:蘇朝琴 教授 Advisor : Chau-Chin Su

國 立 交 通 大 學

電控工程研究所

碩士論文

A ThesisSubmitted to Institute of Electrical Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical Control Engineering

July 2012

Hsinchu, Taiwan, Republic of China

0.5-V 低電壓類比前端積體電路應用於生醫訊號紀錄

研究生 : 楊澤勝 指導教授 : 蘇朝琴 教授

國立交通大學電控工程研究所

摘 要

隨著現代醫學的發達,可攜帶的生醫訊號量測裝置的需求越來越大。我們希望病人 可以攜帶輕巧的監控裝置並可長時間的監控。本研究提出一個 0.5-V 低電壓,可程式化的 CMOS 類比前端積體電路應用在生醫訊號測量。我們的設計能夠處理心電圖,肌電圖, 以及腦波訊號,並且利用差動放大、chopper-stabilized 與交流回授電路技巧阻隔電極片 的直流偏移,共模雜訊,以及 1/f 雜訊。類比前端放大電路的 input-referred noise floor 為 36 以及 3.26 的 noise-efficient factor (NEF)。另外,可程式化放大器的電壓增 益可以透過數位介面控制,實現上容易與 DSP 整合。總功率消耗是 4.21μW (不包含偏 壓電路)。所提出的電路架構將被實現在 UMC CMOS 90 nm 的製程,其晶片面積為 0.75mm X 0.66mm (不包含 PAD)Hz nV

0.5-V Low Voltage Analog Front-End IC for Biomedical

Signal Recording

Student: Tze-Zheng Yang

Advisor: Chau-Chin Su

Institute of Electrical Control Engineering

National Chiao Tung University

Abstract

In this thesis, a 0.5-V low voltage programmable CMOS analog front-end IC for

biomedical signal acquisition is presented. The design deals with Electrocardiogram (ECG),

Electromyogram (EMG), and Electroencephalogram (EEG) signals, while reject DEO

(Differential Electrode Offset), common-mode disturbance and solve flicker noise by

differential circuits and chopper-stabilized technique with an AC feedback circuit. The analog

front-end circuits achieve 36 input-referred noise floor and the noise-efficient factor

(NEF) of 3.26. The programmable gain amplifier (PGA) sets voltage gain with digital

interface, which could be integrated with DSP easily. The total power consumption is 4.21μW

(biasing circuits are excluded). The chip is realized in UMC 1P9M 90nm CMOS process. The

active die area is 0.75mm X 0.66mm.

Index Terms – Bio-potential amplifier, Chopper-stabilized amplifier, Low-voltage circuits, Programmable gain amplifier.

Hz nV

誌謝

首先最感謝的人就是我的指導老師:蘇朝琴教授,感謝老師三年來能夠教導我做研 究的方法,當我遇到瓶頸時,能夠適當的指引我方向,讓我能夠完成本篇論文,未來在 職場上,我會將所學到的態度與方法加以運用。 接著我要感謝的是實驗室的博班學長們,感謝煜輝學長不辭辛勞的帶領生醫計畫, 並指導我實作的經驗,同時也感謝盈杰學長一直幫忙生醫計畫,以及教導許多量測晶片 上的技巧,最後要感謝庭佑學長幫忙督促生醫計畫的進度以及在我下線時幫忙佈局,也 很謝謝學長每次都抽空來維護實驗室的工作站,謝謝實驗室博班學長的指導。 很感謝實驗室碩班學長: 于昇、哲瑋、鈞藝、博祥、群育、修銘、泓瑋,不論在學 業以及生活上都帶給我很大的啟發與樂趣。感謝碩班一起奮鬥的夥伴: 璟伊、弘宇、順 煜、昶志,大家一起尬學術的那段日子,實在難忘,也祝你們未來都能發光發熱。最後 要感謝實驗室的開心果學弟學妹們: 紅豆、馬克、加藤哲、阿 Mon 以及碩一學弟學妹: 怡 婷、勇志、可卿、可謙、皓鈞、子軒、政隆,謝謝你們為枯燥的實驗室生活帶來了歡笑。 家人方面我最感謝的是我父母,謝謝他們一直不辭辛勞的工作,讓我可以無後顧之 憂的讀研究所,並且在我低潮時鼓勵我,同時也要感謝我的親哥哥以及表哥表姊們謝謝 你們帶領我走向電機之路,陪伴我成長到今天。也要謝謝我的大學同學和高中同學,這 三年大家互相成長進步。 最後我要跟過世的外婆說一聲 ,我們約好的事已經踏出一大步了,希望您會一直 在我心中,看我達成約定的那一天。 本論文僅獻給阿嬤、阿姨、嘉文目錄

摘 要 ... i

Abstract ... ii

目錄 ... iv

圖目錄 ... vii

表目錄 ... x

第一章 ... 1

緒論 ... 1

1.1 動機 ... 1 1.2 系統簡介 ... 4 1.3 論文結構 ... 4第二章 ... 5

動態偏移消除技術 ... 5

2.1 介紹 ... 5 2.2 雜訊 ... 6 熱雜訊 ... 6 閃爍雜訊 ... 8 2.3 動態偏移消除技術 ... 9(DYNAMIC OFFSET CANCELLATION TECHNIQUE) ... 9

自動歸零放大器(Auto – Zero Amplifier) ... 10

2.4 交流耦合截波穩定放大器(交流回授) ... 17 2.5 總結 ... 19

第三章 ... 20

0.5-V 類比前端積體電路設計(一) ... 20

3.1 類比前端電路設計 ... 20 3.2 儀表放大器 ... 22 3.3 可程式化增益放大器 ... 36 3.4 系統模擬結果與佈局 ... 40 3.5 規格比較 ... 50第四章 ... 51

0.5-V 類比前端積體電路設計(二) ... 51

4.1 介紹 ... 51 4.2 類比前端電路與規格 ... 52 4.3 儀表放大器 ... 52 4.4 可程式化增益放大器 ... 56 4.5 系統模擬結果與佈局 ... 58第五章 ... 66

量測結果 ... 66

5.1 量測 PCB 考量 ... 66 5.2 量測晶片環境設定 ... 68 5.3 量測結果與討論 ... 69結論 ... 80

6.1 結果與討論 ... 80

6.2 未來展望 ... 81

圖目錄

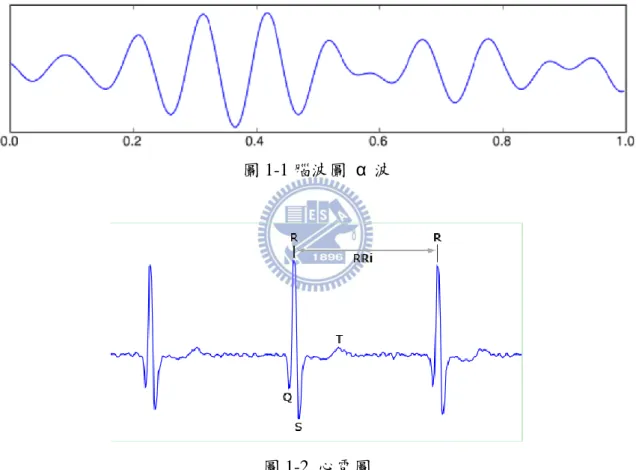

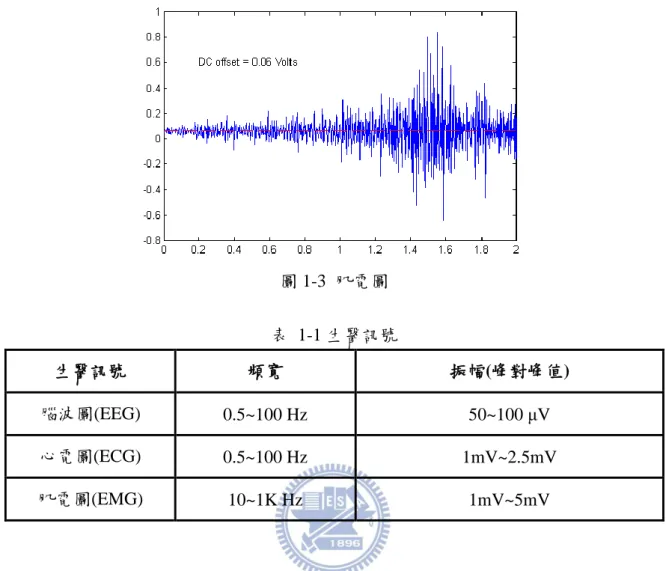

圖 1-1 腦波圖 α 波 ... 2 圖 1-2 心電圖 ... 2 圖 1-3 肌電圖 ... 3 圖 1-4 傳統生醫訊號前端感測電路系統 ... 4 圖 2-1 熱雜訊時域圖 ... 6 圖 2-2 熱雜訊功率密度頻譜圖 ... 6 圖 2-3(a) 電壓源的電阻熱雜訊模型 (b) 電流源的電阻熱雜訊模型 ... 7 圖 2-4 電晶體熱雜訊模型 ... 7 圖 2-5 電晶體雜訊模型,包含熱雜訊和閃爍雜訊 ... 8 圖 2-6 電晶體的雜訊功率頻譜 ... 9 圖 2-7 自動歸零放大器 ... 11 圖 2-8 自動歸零技術觀念 ... 11 圖 2-9 自動歸零對熱雜訊頻譜功率圖 ... 12 圖 2-10 歸零對閃爍雜訊功率頻譜圖 ... 12 圖 2-11 截波訊號示意圖 ... 13 圖 2-12 直流訊號經過截波調變時域圖 ... 13 圖 2-13 截波調變流程圖 ... 14 圖 2-14 截波調變對閃爍雜訊功率頻譜圖 ... 14 圖 2-15 截波調變時域圖(非理想) ... 15 圖 2-16 電荷注入產生圖 圖 2-17 電荷注入對訊號影響圖... 15 圖 2-18 突波經過截波調變圖 ... 16 圖 2-19 交流耦合截波穩定放大器(交流回授)圖 ... 18 圖 3-1 生醫訊號感測類比前端電路 ... 20 圖 3-2 N 型電晶體截波開關 ... 22 圖 3-3 交流耦合回授儀表放大器 ... 24 圖 3-4 放大器增益和相位模擬圖 ... 26 圖 3-5 放大器迴轉率模擬圖 ... 27 圖 3-6 儀表放大器內部運算放大器 ... 27 圖 3-7 開關共模回授電路 ... 28 圖 3-8 連續時間共模回授電路 ... 29 圖 3-9 非重疊時脈產生器 ... 30 圖 3-11 拔靴式電路 ... 31 圖 3-12 拔靴式電路操作原理(VDD ~ VSS) ... 32 圖 3-13 拔靴式電路操作原理(VSS ~ VDD) ... 32 圖 3-14 拔靴式電路輸出電壓模擬圖 ... 33圖 3-16 截波開關電導模擬圖(有拔靴式電路) ... 34 圖 3-17 Gm-C 濾波器 ... 35 圖 3-18 全差動電流鏡放大器 ... 35 圖 3-19 可程式化增益放大器圖 ... 36 圖 3-20 開迴路增益放大器圖 ... 37 圖 3-21 開迴路放大器增益與相位圖 ... 38 圖 3-22 放大器迴轉率模擬圖 ... 38 圖 3-23 疊接電晶體示意圖 ... 40 圖 3-24 類比前端電路 FFT 模擬圖 ... 40 圖 3-25 類比前端電路增益頻寬模擬圖 ... 41 圖 3-26 前端電路雜訊截波比較圖 ... 42 圖 3-27 前端電路雜訊模擬圖 ... 42 圖 3-28 共模拒斥比模擬圖 ... 43 圖 3-29 共模增益示意圖 ... 44 圖 3-30 實際放大器負電阻示意圖 ... 44 圖 3-31 共模拒斥比蒙地卡羅模擬圖 ... 45 圖 3-32 類比前端電路晶片佈局圖 ... 45 圖 3-33 心電圖訊號模擬圖 ... 49 圖 4-1 類比前端電路架構圖 ... 52 圖 4-2 儀表放大器電路圖 ... 52 圖 4-3 儀表放大器內部運算放大器圖 ... 53 圖 4-4 非重疊時脈產生器和拔靴式電路圖 ... 55 圖 4-5 Gm-C 濾波器內部放大器圖 ... 56 圖 4-6 可程式化增益放大器圖 ... 57 圖 4-7 類比前端電路 FFT 模擬圖 ... 58 圖 4-8 針對肌電圖和心電圖的增益頻寬圖 ... 59 圖 4-9 針對腦波圖的增益頻寬圖 ... 59 圖 4-10 前端電路雜訊模擬圖 ... 60 圖 4-11 共模拒斥比模擬圖 ... 61 圖 4-12 類比前端電路晶片佈局圖 ... 62 圖 4-13 心電圖訊號模擬圖 ... 65 圖 5-1 類比前端電路晶片打線圖 ... 67 圖 5-2 濾波電容電感圖 ... 67 圖 5-3 量測環境設定圖 ... 68 圖 5-4 輸入訊號量測圖 ... 69 圖 5-5 輸出訊號(000)量測圖 ... 69 圖 5-6 輸出訊號(100)量測圖 ... 70 圖 5-7 輸出訊號(101)量測圖 ... 70

圖 5-8 輸出訊號(110)量測圖 ... 71 圖 5-9 輸出訊號(111)量測圖 ... 71 圖 5-10 輸出訊號(000)量測圖 ... 72 圖 5-11 輸出訊號(100)量測圖 ... 72 圖 5-12 輸出訊號(101)量測圖 ... 73 圖 5-13 輸出訊號(110)量測圖 ... 73 圖 5-14 輸出訊號(111)量測圖 ... 74 圖 5-15 ECG 輸入訊號量測圖(頻寬 1KHz) ... 74 圖 5-16 ECG 輸出訊號(000)量測圖(頻寬 1KHz) ... 75 圖 5-17 ECG 輸出訊號(100)量測圖(頻寬 1KHz) ... 75 圖 5-18 ECG 輸出訊號(101)量測圖(頻寬 1KHz) ... 76 圖 5-19 ECG 輸出訊號(110)量測圖(頻寬 1KHz) ... 76 圖 5-20 ECG 輸出訊號(111)量測圖(頻寬 1KHz) ... 77

表目錄

表 1-1 生醫訊號 ... 3 表 3-1 類比前端電路規格 ... 21 表 3-3 放大器增益頻寬的製程角落模擬表 ... 26 表 3-4 放大器迴轉率的製程角落模擬表 ... 27 表 3-5 放大器增益頻寬的製程角落模擬表 ... 38 表 3-6 放大器迴轉率的製程角落模擬表 ... 39 表 3-7 總諧波失真表 ... 41 表 3-8 生醫訊號增益表 ... 41 表 3-9 前端電路雜訊模擬表 ... 42 表 3-10 生醫訊號雜訊總值表 ... 43 表 3-11 共模拒斥比模擬表 ... 43 表 3-12 類比前端電路功率消耗表 ... 46 表 3-13 類比前端電路規格總結表 ... 47 表 3-14 類比前端電路規格比較表 ... 50 表 4-1 放大器規格表 ... 54 表 4-2 可程式增益放大器增益表 ... 57 表 4-3 總諧波失真表 ... 58 表 4-4 生醫訊號增益表 ... 60 表 4-5 前端電路雜訊模擬表 ... 60 表 4-6 共模拒斥比模擬表 ... 61 表 4-7 生醫訊號雜訊總值表 ... 61 表 4-8 功率消耗表 ... 62 表 4-9 類比前端電路規格總結表 ... 63 表 5-1 可程式化增益放大器量測表 ... 77 表 5-2 可程式化增益放大器功率模擬表……… ..78 表 5-3 類比前端電路量測規格比較表……… ..79第一章

緒論

1.1 動機

由於現今CMOS技術、通信和低功耗電路設計技術的突飛猛進,為可攜式生物醫療 設備行業帶來了不小的改變。生醫訊號的讀取系統已經可以由傳統分離元件組成的系統 轉而由單一晶片所取代。一般來說,生醫訊號的振幅從幾微伏特到幾毫伏特都有,為了 處理這些信號,必須設計低輸入雜訊和可程式化增益來適應如此高動態範圍的訊號。更 進一步考慮減輕病人必須長時間忍受儀器所帶來的不舒服,於是,現今的生醫系統就朝 向小體積、輕量化、可攜式來發展。以電路技術而言就必須朝向低雜訊、低功率、低電 壓並且以電池供應電壓的系統為設計考量。 一般來說量測生醫訊號時,會使用兩片生理電極片固定在量測部位,再經由電極片 將生醫訊號讀取到前端電路系統做處理。通常生醫訊號大多為低頻率的小訊號,但是外 界或是電路的雜訊都比生醫訊號要來的大,所以一個前端電路其中要做的重要工作就是 必須抑制這些雜訊。而大部分最主要要探討的可以分為三個部分。第一個為閃爍雜訊。 由於電子在電晶體內流動的時候,根據能量的狀態容易陷入或被閘極和基極交界的自由 鍵所釋放,使得汲極電流會因為閃爍雜訊而受到影響,由於生醫訊號具有相當低頻的成 分,這也意味著閃爍雜訊會在低頻時加入到生醫訊號,導致輸出訊號失真。第二個所要 討論的雜訊存在於電源線,電源線存在著50/60 Hz 的訊號並且很容易耦合到人的身體, 這在人的生醫訊號上可以視為一個共模雜訊,在低電壓的電路裡影響更是重大,通常電擺幅較小的生醫訊號,電源線雜訊將不可以忽視。第三個是由於兩個電極貼片所產生的 不同 DC準位,稱作差動電極偏移電壓(Differential Electrode Offset, DEO)。就傳統的氯 化鋁電極而言,差動電極偏移電壓擺幅可高達50mV並隨著時間變化,這在生醫系統上 是 必 須 要 處 理 的 。 表 1-1 為 生 醫 訊 號 的 一 般 規 格 。 其 中 包 含 了 圖 1-1 的 腦 波 圖 (Electroencephalogram, EEG),圖1-2的心電圖(Electrocardiogram, ECG),圖1-3的肌電圖

(Electromyogram, EMG)。

圖 1-1 腦波圖 α 波

圖 1-3 肌電圖 表 1-1 生醫訊號 生醫訊號 頻寬 振幅(峰對峰值) 腦波圖(EEG) 0.5~100 Hz 50~100 μV 心電圖(ECG) 0.5~100 Hz 1mV~2.5mV 肌電圖(EMG) 10~1K Hz 1mV~5mV 以上這些規格都是針對低頻生醫訊號。而閃爍雜訊、共模雜訊、差動電極偏移電壓 (DEO),則是偵測生醫訊號時最主要需要考量的。在一般生醫訊號處理的過程中,傳統 的方式是使用一個擁有高共模拒斥比(CMRR)的儀表放大器來避免閃爍雜訊和抑制共模 雜訊。對差動電極偏移電壓(DEO)而言,則是提高電壓或是使用雙電壓源來增加訊號的 擺幅空間。根據功率消耗定理,功率的消耗是跟電壓成正比的,所以使用傳統的設計方 式將是一個會消耗大量功率的方式,若要達成現今生醫技術所要求的低耗能裝置,上述 的方法是不可行的。圖1-4為一個傳統生醫訊號前端感測電路系統。通常是使用兩個電 極片黏在身體的表面,進而將生醫訊號傳送給前端電路。通常系統內會包含儀表放大器 來做第一次的訊號放大,並且將不要的訊號藉由濾波器來濾除,接著將濾出的訊號送到 數位類比轉換器去轉換成數位訊號,讓數位訊號系統去做訊號處理。

IA Filter ADC DSP 圖 1-4 傳統生醫訊號前端感測電路系統

1.2 系統簡介

在上節裡提到了傳統前端電路對於共模雜訊和差動電極偏移電壓(DEO)的解決辦 法,但此作法並不適用於現今強調低功耗的可攜式生醫系統。要實現低功耗的系統,第 一個最有效的方式便是降低系統供應電壓,但這也意味著雜訊所佔訊號的比例也越來越 大,所以現代為了符合可攜式生醫訊號系統的趨勢,低雜訊、低電壓的生醫系統便是非 常重要,也是現今類比積體電路設計的一大挑戰。在本篇研究中,我們實現了一個0.5V 的低電壓類比生醫前端電路晶片,此前端電路提供了66 dB的放大倍率,由一個交流耦 合的儀表放大器和可程式化增益放大器所組成。此電路的總消耗功率大概為4.21μW。1.3 論文結構

本論文內容分成五個章節。第一章為緒論,簡介發展現況、研究動機以及論文結構。 第二章會介紹動態偏移電壓消除的基本觀念與技巧。並且比較自動歸零放大器和截波放 大器。此外,本章節還會介紹現今動態偏移電壓消除技巧和使用交流回授技巧的截波穩 定放大器。第三章節則是介紹 0.5V 類比前端電路系統(一)及模擬結果。第四章節為設計 0.5V 類比前端電路系統(二)及模擬結果。第五章節為 0.5V 類比前端電路的晶片量測與 討論,第六章為總結。第二章

動態偏移消除技術

(

Dynamic Offset Cancellation Technique

)

2.1 介紹

在生醫系統裡類比前端電路最為重要的就是處理雜訊這件事,因為生醫訊號大多振 幅都很小,往往一個雜訊就會使得訊號消失,所以認清雜訊的種類與處理方式,將是非 常的重要。動態偏移消除技術(Dynamic Offset Cancellation Technique)[8]為處理雜訊常見 的技術,本章節將會詳細介紹動態偏移消除技術的原理以及它對各種類型雜訊的影響。 一開始 2.2 節會先介紹一些存在於生醫系統的雜訊種類以及來源。2.3 節將會介紹基本的

2.2 雜訊

在類比電路設計中,雜訊最主要可以分為兩種:半導體電路雜訊和環境雜訊。半導體 電路雜訊可以分為閃爍雜訊和熱雜訊。環境雜訊可以分為電源端雜訊和電晶體基板耦合 雜訊。本章節主要討論的是半導體電路雜訊。熱雜訊

因為熱雜訊的雜訊功率頻譜在一極寬的頻寬下為定值,所以通常又稱作白色雜 訊。熱雜訊的來源最主要是由於電子在導體中隨機的運動所產生的。經研究顯示熱雜訊 與絕對溫度成正比。圖 2-1 為熱雜訊在時域的波形圖。圖 2-2 則是熱雜訊在單邊頻譜下 的功率密度圖。 圖 2-1 熱雜訊時域圖 S(f) f(frequency) 圖 2-2 熱雜訊功率密度頻譜圖熱雜訊在不同的導體有不同的雜訊模型。對一個電阻而言,就可以當作是電阻上並 聯電壓源或是串聯電流源。圖 2-3 為電阻的熱雜訊模型。針對電壓源形式的熱雜訊可以 表示如式(2.1)。 2 ( ) 4 R S f kTR (2.1) 其中 k 代表波茲曼常數, 23 1.38 10 J k K ,T 為絕對溫度,R 為電阻。 對電晶體而言,電流流過的通道即是產生熱雜訊的來源。可以表示成式(2.2) 2( ) 4 d I f kT gm (2.2) 而γ為一個常數值。通常長通道電晶體的 23。模型上可以看成一個電流源並聯於電 晶體的飽和區通道上,如圖 2-4。 2 ( ) 4 R V f kTR noiseless R noiseless R IR2( ) 4f kT R/ 圖 2-3(a) 電壓源的電阻熱雜訊模型 (b) 電流源的電阻熱雜訊模型 2 ( ) 4 d I f kT gm 圖 2-4 電晶體熱雜訊模型

閃爍雜訊

由於在越低頻的頻率範圍內,電子被晶格捕捉或釋放的現象增加。所以閃爍雜訊的 頻譜密度通常是跟頻率成反比,也因為這個原因,閃爍雜訊也稱作“ 1/f noise ”。在 電晶體中,閃爍雜訊是非常重要的雜訊來源,尤其是在低頻率範圍時,電子更容易被存 在閘極和基極之間的自由鍵所捕捉或釋放。而這個現象將會影響汲極所產生的電流,如 圖 2-5 可以視作一個電壓源串聯在閘極,並且由式(2.3)可知,電晶體的尺寸越大,閃爍 雜訊越小,所以在低雜訊的電路設計上,電晶體的尺寸都會滿大的。由於 P 型電晶體的 通道與閘極的二氧化矽距離比 N 型電晶體來的遠,所以閃爍雜訊較 N 型電晶體來的小。 2 ( ) 4 d I f kT gm 2 1 ( ) n ox K V f C WL f 圖 2-5 電晶體雜訊模型,包含熱雜訊和閃爍雜訊 2( ) 1 n ox K V f C WL f (2.3) 式中Cox代表閘極的單位面積電容,W 和 L 分別代表電晶體的寬度和通道長度,K 是一 個由製程決定的參數,通常數值的等級在10 V F25 2 。2 20 logVn c f f(log scale)

1/f corner

Thermal

圖 2-6 電晶體的雜訊功率頻譜 因此可以得知電晶體的總雜訊可以表示成 2( ) 1+4kT 2 1 3 n ox K V f C WL f gm (2.4) 圖 2-6 為電晶體的雜訊功率頻譜。在閃爍雜訊和熱雜訊的交界處,有一個頻率稱作“交 界頻率”。它發生在當閃爍雜訊功率等於熱雜訊功率的時候。式子可以表示成 1 2 1 4kT 3 ox K C WL f gm (2.5) 則雜訊的交界頻率即可寫成 3 8kT c ox K f gm C WL (2.6)2.3 動態偏移消除技術

(Dynamic Offset Cancellation Technique)

現今許多生醫晶片所要處理的訊號通常在毫伏特的等級。不幸的是,在互補式金屬

氧化半導體技術下,電晶體的雜訊和偏移電壓也是在毫伏特以上的等級,這也意味著訊 號非常容易受到干擾,因此許多消除電晶體雜訊和偏移電壓的技術便發展出來。最主要

異或是光罩錯誤造成電晶體產生誤差而產生的偏移電壓。根據誤差模型式(2.7),臨界值 電壓是跟電晶體的尺寸成反比。其中AVt為誤差參數(mV

m)。而電晶體的雜訊可以由 式(2.3)得知,增大尺寸也是一個解決的方法。 2 ( Vt) A Vt W L (2.7) 第二個方法為使用雷射來調整電路消除偏移電壓,不過這需要額外的測試裝置,會 增加額外的成本。第三,則是使用動態偏移消除技術。最後一個是大多數人使用的方法, 因為它具有長時間的穩定性且花費不貴。接下來將要介紹其中兩種動態偏移消除技術: 自動歸零和截波技術。在此由於系統訊號為低頻,所以這裏所說的雜訊是以閃爍雜訊為 主,而偏移電壓為直流電壓值,所以也與閃爍雜訊歸類為低頻雜訊。自動歸零放大器(Auto – Zero Amplifier)

圖 2-7 為一個自動歸零放大器。主要可以分為兩個操作模式:自動歸零模式和訊號放 大模式。在自動歸零模式時(

1),放大器會對偏移電壓取樣並且將它儲存在電容上。 當穩定後偏移電壓存在電容上的量為: . 1 os A V A 在訊號放大模式時(

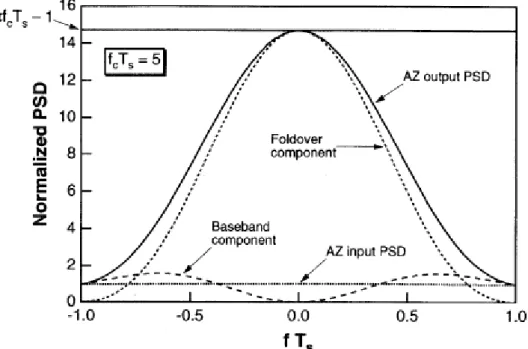

0),放大器將會 正常輸出被放大的訊號。由於閃爍雜訊和偏移電壓都為低頻的雜訊,所以在訊號放大模 式時,閃爍雜訊和偏移電壓會和上一個時間被儲存在電容上的雜訊相減,最後可得輸入 總雜訊變為: 1 1 os V A .可以從公式得知,低頻雜訊成分經過自動歸零放大器之後,其大 小值可以被放大器的增益有效的抑制。 A Vos Vi Vo 圖 2-7 自動歸零放大器 Sample&Hold Vn,i Vn,o 圖 2-8 自動歸零技術觀念 自動歸零的基本觀念如圖 2-8。圖 2-8 的雜訊轉導方程式為式(2.8),其中H f( )為取樣電 路的轉移方程式。 , ( ) , ( ) (1 ( )) n o n i v f v f H f (2.8) 且 ( ) sin ( ) H f c f (2.9) 可以由上式得知(1H f( ))為一個高通方程式,意味著低頻的雜訊(如偏移電壓、1/f 雜訊) 將會被衰減。這個特性同時也造成了缺點,會使得高頻的雜訊疊回低頻域。也就是說對 閃爍雜訊而言,自動歸零是有幫助的,但是對於熱雜訊而言,它在高頻區域的部分將會 疊回低頻域,造成低頻域的熱雜訊增加。如圖 2-9 為自動歸零對熱雜訊影響的頻譜功率 圖,由此圖得到雜訊經過自動歸零之後反而增加,其中 fc為系統的頻寬,Ts為取樣週 期。圖 2-10 為對閃爍雜訊影響的頻譜功率圖, fk為交界頻率[8]。

圖 2-9 自動歸零對熱雜訊頻譜功率圖

截波穩定放大器(Chopper-Stabilized Amplifier)

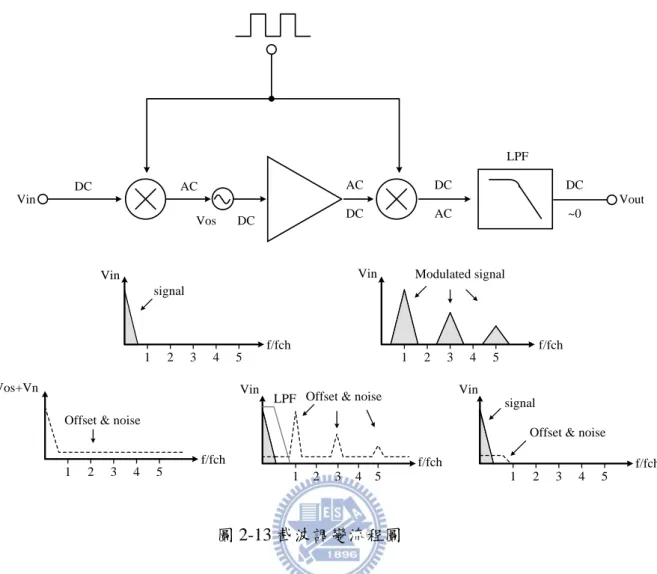

訊號經過截波所提供的頻率調變功能,會將低頻率的訊號移往高頻率,高頻率的信 號移往低頻率。如圖 2-11 為截波訊號的示意圖。在頻域方面,截波先將低頻訊號移往 高頻,接著低頻雜訊(如閃爍雜訊、熱雜訊)也經由系統加入調變過的訊號內,再經過一 次截波,原本高頻的訊號經調變回到低頻,低頻雜訊調變到高頻,如此將使得雜訊與訊 號分開,最後再經過一個低通濾波器把雜訊濾除,如圖 2-13 所示。圖 2-12 表示訊號V tin( ) 經過m t( )調變之後,會把V tin( )調變到閃爍雜訊不在的高頻區域去。 m(t) t Vin(t) m(t) Vc(t) 圖 2-11 截波訊號示意圖 m(t) t Vin(t) +Vin T/2 T Vin(t) +Vin -Vin T/2 T t 圖 2-12 直流訊號經過截波調變時域圖Vin DC AC Vos DC AC DC DC AC DC ~0 Vout LPF Vin f/fch 1 2 3 4 5 signal Vin f/fch 1 2 3 4 5 Modulated signal f/fch 1 2 3 4 5 Vos+Vn

Offset & noise

Vin f/fch 1 2 3 4 5 Vin f/fch 1 2 3 4 5

Offset & noise

LPF signal

Offset & noise

圖 2-13 截波調變流程圖

圖 2-13 為截波穩定放大器的系統流程圖,假設截波頻率遠高於交界頻率且放大器 為理想,則閃爍頻率經過截波穩定放大器之後會被完全的移除。圖 2-14 為閃爍雜訊經 過截波調變後的功率頻譜圖。

上述分析時域信號經過截波調變之後為一方波,這裡是假設直流輸入信號和無限寬 的系統頻寬。實際電路裡,系統通常為放大器,而放大器的頻寬是有限的,這也造成訊 號經過截波調變後需要穩定的時間。圖 2-15 為實際有限系統頻寬的波形圖,可以與圖 2-12 作比較。由圖 2-15 可以看出經過兩次調變的訊號,其直流訊號因為放大器有限頻 寬的關係,輸出值會比理想上還要低。由於放大器頻寬造成輸出值的誤差可以表示成式 (2.10)。Aid表示為理想的放大器倍率,Anonid為非理想的放大倍率,f3dB 1,fch 1T。 (1 4 ) nonid id A A T (2.10) 由於截波調變是經由電晶體開關來達成,因為電晶體開關在切換時,開關的閘極電 壓經由電晶體兩端寄生的電容耦合到訊號,這個問題稱為“電荷注入”,使得訊號會有 多餘的電壓產生,造成錯誤(如圖 2-16、2-17) 。 t ideal actual ideal actual Vin(t) +Vin -Vin T/2 T t m(t) T/2 T -Aid .Vin +Anonid .Vin +Aid .Vin Vin(t) 圖 2-15 截波調變時域圖(非理想) n n channel p MOS s Q V C Vs Cs Vout

clk Input spikes Demodulated spikes DC level m(t) m(t) 圖 2-18 突波經過截波調變圖 由於電荷注入效應,造成輸入訊號經過截波調變後會造成突波,而此突波經過再次 截波調變和低通濾波器後,會產生多餘的偏移電壓(如圖 2-18)。而此偏移電壓的量可以 由式 2.11 來表示。其中 fch是截波頻率,Vspike為突波振幅, 為穩定時間常數。 2 . spike ch spike Offset f V (2.11) 為了讓因為突波而造成的偏移電壓減小,勢必要降低截波頻率和縮小時間常數,但 是要付出的代價就是閃爍雜訊的增加和功率消耗量上升,在現今低功率電路的設計上, 這將是設計者所面臨的一大挑戰。

2.4 交流耦合截波穩定放大器(交流回授)

先前介紹的自動歸零和傳統截波穩定放大器,最主要的功能是用來濾除低頻的雜 訊,但是以下有二個問題是量測生醫訊號將會發生的,光靠上述的電路技巧將無法處理。 第一個問題就是量測生理訊號時所使用的電極片,電極片在人體身上時,所產生共模電 壓將會不同,這會造成前端電路無法運作。根據文獻[16],使用軌對軌放大器,來滿足 電極片共模電壓的變化範圍,但這也意味著需要有兩個電源來滿足軌對軌放大器。針對 這個問題,現今解決的方法就是輸入級使用交流耦合,使用電容將輸入訊號的直流電壓 隔絕,以免放大器受到干擾。第二個問題電極片差動偏移電壓(DEO),以傳統使用鋁來 做為電極片而言,差動偏移電壓隨著時間改變大概可到 50mV ,由於截波穩定放大器是 一個直流耦合系統,差動偏移電壓的出現將會使得放大器輸出飽和,所以在訊號輸入放 大器之前,須要有高通濾波器來處理差動偏移電壓。解決差動偏移電壓的問題,可以使 用被動元件作為高通濾波器或是使用差動差別放大器(differential difference amplifier), 而前者會降低訊號對雜訊比(signal-to-noise ratio),後者則是會付出功率消耗上升的結 果。以下所提出的交流回授方法,將不會有上述如此嚴重的代價。 圖 2-19 為交流耦合截波穩定放大器,其中包含了一個閉迴路的截波穩定放大器、 低通濾波器,還有一個交流回授電路。當輸入訊號進入系統之前,會先被截波調變一次, 此時訊號被調變到高頻區,接著電路內的閃爍雜訊和熱雜訊就會加入,訊號和雜訊會再 次被截波調變,此時低頻雜訊就會到高頻區去,訊號會回到原本的頻域,若訊號本身含 有差動偏移電壓,則放大器輸出將會飽和,當下交流回授電路便會發揮功用。放大器的 飽和輸出將會經過 Gm-C 濾波器,將輸出飽和訊號的直流成份積存在大電容,並且回授 到截波穩定放大器內,以消除電極片所造成的差動偏移電壓,使截波穩定放大器回到正 常運作區域。A Gm-C -1/K fch fch fch Vs Vnoise Vo fch : 圖 2-19 交流耦合截波穩定放大器(交流回授)圖 式 2.12 為交流穩定截波放大器(交流回授)的系統轉移方程式, ( ) 1 1 ( ) ( ) 1 1 o HP s LP V s H s A s V s s (2.12) 其中1/ K為系統回授因子,則輸出偏移電壓對輸入偏移電壓的轉移方程式為式 2.13,式 2.14 為輸出雜訊在功率頻譜所表示的式子。 , , 1 offset out offset in V A A V K (2.13) 2 2 , 2 , 2 1 ( ) ( ) ( )

noise out chop noise in chop n n odd S f A f n f S f n f n

(2.14) 從上述可以看出此系統具有帶通的特性,可以阻擋低頻的雜訊(閃爍雜訊、偏移電 壓),也有避免高頻雜訊干擾的功能。2.5 總結

在本節討論了應用於生醫前端電路的技術,自動歸零雖然可以減少閃爍雜訊,但是 卻會增加了熱雜訊的成份,截波放大器雖然對閃爍雜訊有效,但是卻受限於放大器的頻 寬,和輸入訊號的偏移電壓影響。最後所提出的交流耦合截波穩定放大器不只可以解決 雜訊,其中的交流回授對於偏移電壓和共模電壓變化都能有效的抑制,在現今設計中, 交流耦合運用於截波穩定放大器中,將是個不錯的設計方向。第三章

0.5-V 類比前端積體電路設計(一)

3.1 類比前端電路設計

圖 3-1 為本章所要設計的生醫訊號感測類比前端電路。我們使用 Kendall H99SG 電 極片來連接身體與感測電路。生醫訊號會先經過儀表放大器來濾除雜訊(閃爍雜訊、共 模雜訊)。為了確保放大倍率足夠,還會再經過可程式化增益放大器,來提供完整的輸 出訊號。最後會經過一個類比數位轉換器,以提供數位訊號給數位系統做分析。此外根 據表 1-1 針對腦波訊號,由於它的振幅相對於心跳、肌肉訊號比較小,所以光靠儀表放 大器和可程式化增益放大器是不夠的,因此本系統提供了專門給腦波訊號放大的路徑。 我們使用了數位介面,可以讓使用者選擇現在要量測那些訊號,若是腦波訊號,系統在 感測訊號時,會在介面中加入一個放大器,作為補償放大倍率的功用。 IA PGA ADC Preamp Digital control Gain Mode 圖 3-1 生醫訊號感測類比前端電路設計規格

為了使前端電路具有長時間使用的特性,整體電路的供應電壓選擇工作在 0.5V,而 如此低電壓下便會產生許多電路設計上的難度。此外要讓系統使用時間超過一年,功率 消耗訂定在 5μW 以下。在如此低電壓的系統下工作,輸出訊號的失真程度也是一個重 要的考量。為了使輸出訊號到數位類比轉換器時,能夠有良好的資料轉換率,系統放大 倍率則是越大越好。在實際使用電路時,都會存在著 50/60 Hz 的雜訊,而在低電壓系統 影響更是劇烈,所以擁有良好共模拒斥比(Common mode rejection ratio)將是非常重要的 規 格 。 根 據 國 際 臨 床 神 經 生 理 學 聯 合 會 (International Federation of Clinical Neurophysiology),共模拒斥比最好大於 110 dB。總諧波失真(Total harmonic distortion)比例要小於 1%。另一項規格為動態放大操作範圍,它的定義為最大輸入訊號在總諧波 失真小於 1%的情形下的放大倍率。而總相對輸入雜訊(input-referred noise)關係到訊號對 雜訊比(signal to noise ratio),以一個十位元的數位類比轉換器來說,總相對輸入雜訊要 小於1μVrms。表 3-1 為本系統的規格表。 表 3-1 類比前端電路規格 Spec. Value Supply voltage 0.5 V Gain >40 dB CMRR >110 dB THD <1 % Dynamic range >60 dB

Input – referred noise 1μVrms (0.5Hz ~ 100Hz)

Bandwidth 1kHz

3.2 儀表放大器

本節裡將針對交流耦合穩定截波放大器來討論。有關此系統的方塊圖和轉移函數在 圖 2-19 和式 2.12。此系統包含了一個全差動的運算轉導放大器,低通濾波器,N 型電 晶體截波電路(圖 3-2)和一個外掛電容。在使用 N 型電晶體截波電路時,所要注意的就 是開關導通的電阻值是否跟得上截波的頻率,在低電壓操作時,用一般的數位電路無法 達成,因此在本系統將會使用到升壓電路來導通切換開關。整個系統的回授路徑可以分 為兩個,一個為訊號放大的路徑,另一個為抵銷差動電極偏移電壓。圖 3-3 為儀表放大 器的電路簡圖。 此系統的轉移方程式為 1 1 ( ) ( ) ( ) 1 1 1 i o i f i f h p HP LP o f C s v s H s v s C C C C C s s A C (3.1) 其中低通頻率為 f LP t i C C (3.2) 高通頻率為 hp m i HP ext fb f C G C C C C (3.3)

中頻段為訊號範圍,其放大倍率為 i f C C ,而消除差動電極偏移電壓的迴路放大倍 率為 h f C C 。接下來就是有關整個電容值的設計,假設運算放大器的熱雜訊為 2 ni v ,則 整個回授迴路的相對輸入雜訊為 2 2 2 , i h f p ni cl ni i C C C C v v C (3.4) 從式 3.4 來看,減少熱雜訊的方法就是要加大輸入電容,減少回授電容,這中間存 在著面積與電路效能好壞的考量。大的輸入電容號的面積大,但是抗雜訊效果好,回授 電容太小,會使得抗差動電極偏移電壓的能力下降,這都是設計者需要注意的。接著從 表 3-2 可以看出放大訊號到輸出最大範圍可以分為兩個例子,第一個是針對心電圖和肌 電圖,放大倍率範圍為 26 ~ 40 dB,第二個是針對腦波圖,範圍為 60 ~ 66 dB。在本設 計中,儀表放大器將會負責第一個例子,它的放大倍率將有兩種: 26 dB 或是 32 dB,剩 下的放大倍率將由預先放大器和可程式化增益放大器來處理。 表 3-2 生醫訊號放大倍率 生醫訊號 頻寬 振幅(峰對峰值) 放大倍率 腦波圖(EEG) 0.5~100 Hz 50~100 μV 60~66 dB 心電圖(ECG) 0.5~100 Hz 1mV~2.5mV 32~40 dB 肌電圖(EMG) 10~1K Hz 1mV~5mV 26~40 dB 為了要達到放大倍率,並考慮 1 op cl op A A A ,輸入電容Ci為 30 pF 和 9 pF,為了減 少寄生電容的效應,回授電容Cf 設計為 0.29 pF,差動電極偏移電壓回授電容為 1 pF。 在差動電極偏移電壓發生時,其直流成份會先經過截波調變到高頻,此時運算放大器會 視為訊號將其放大,在低電壓的環境下,輸出訊號很容易就產生飽和現象,再經過第二

偏移電壓成分儲存在Cext上,穩定狀態時,Cext上的偏移電壓為 DEO i h C V C ,接著在經 由截波調變回授到輸入端,與輸入偏移電壓相減。 -+ + -+ + -Gm Vipc Vinc Ci3 Ci1 Ci2 Ci4 Cf1 Cf2 Ch2 Ch1 Cext Vonc Vopc 圖 3-3 交流耦合回授儀表放大器

運算放大器

本系統中運算放大器的設計是極為重要的一環,在低電壓低雜訊的要求下,儀表放 大器身為系統的第一級電路,對於雜訊必須要有適當的抵抗能力,因此我們採用了架構 較為簡單的電流鏡放大器(如圖 3-4),避免因為電晶體太多產生的雜訊而影響訊號。在設 計運算放大器有幾個需要注意的規格:放大倍率、頻寬、電晶體雜訊、共模拒斥比、迴轉 率。對運算放大器而言,開迴路放大倍率則是越大越好,這樣會減少閉迴路增益因為非 理想效應導致增益下降。

1 5 5 7 3 3 1 || o m m o o m m f A g g r r g g (3.5) 1 m c L g f C (3.6) 在此設計上需特別注意的就是負電阻 3 1 m f g 的尺寸設計,在運用上可以分為數位設 計和類比設計,此處是用來放大小訊號的用途,所以不可以當作數位來設計,否則訊號 將會發散。類比設計則是讓 3 3 1 m m f g g 成為一個極小正電阻,來放大小訊號。頻寬方面, 在截波頻率調變下,訊號會被調變到以截波頻率為中心頻的頻帶,所以閉迴路的 3 dB 頻( ) / c ch sig f f f 。作為第一級的放大器,雜訊的抑制是很重要的,式 3.7 和式 3.8 為電 流鏡放大器在熱雜訊和閃爍雜訊上的表現 ,由兩式可以得知輸入級的設計,對雜訊的 抑制很有關係,因此這一對電晶體設計上採用的是 P 型輸入對,因為在低頻的閃爍雜訊 裡,P 型電晶體擁有較少閃爍雜訊,同時為了提高gm值,輸入對將會操作在次臨界區, 並增大電晶體的尺寸。共模拒斥比的高低對放大器也是非常重要,它也是產生偏移電壓 的來源,在電路上除了因為輸入級不匹配造成偏移電壓之外,另一個原因就是電晶體 Mb,它負責電路的電流來源,在小訊號分析上,理想是視為一個交流地,但實際上會 因為它的有限阻抗產生電流,使得輸出產生偏移電壓,在此設計上,則是增加 Mb 的阻 抗,來減小交流電流的產生。 3 3 2 , 2 1 1 16 1 3 m m f n in thermal m m g g V KT f g g (3.7) 2 2 3 2 3 , ker 1 1 3 3 1 3 3 1 1 1 m 1 m f n in flic ox m f f m g g K V f f C W L W L g W L g (3.8) 在設計心電圖時,可以發現在 Q、R、S 波這段區域的波形頻率是不同於其他區段 的波形,設計上就必須要確保放大器能夠跟得上訊號,迴轉率的高低,是為了要判斷放 大器在訊號瞬間變化時能否跟得上,針對心電圖,我們可以從[7]得知,Q、R、S 波大 概佔全部波型的五十分之一,且已知 ECG 的波形大概為 0.5 Hz ~150 Hz ,可以算出 0.75 (mV ) SR s 。

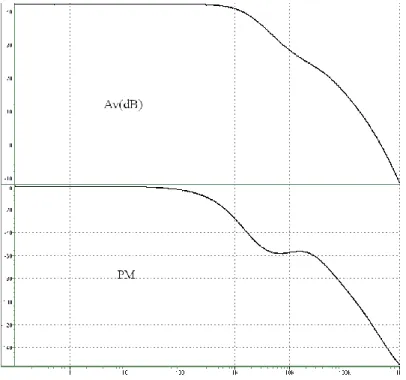

圖 3-4 放大器增益和相位模擬圖 表 3-2 放大器增益頻寬的製程角落模擬表 TT FF FS SF SS Av(dB) 42.0 39.7 41.9 41.7 42.4 PM 47.2 56.1 48.6 46.8 46.2 fc (Hz) 474k 445k 512k 419k 492k

圖 3-5 放大器迴轉率模擬圖 表 3-3 放大器迴轉率的製程角落模擬表 mV s TT FF FS SF SS SR 39.7 40.1 41.7 36.5 42.0 Mb Mp1 Mp2 Mn3 Mf3 Mf4 Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vopp Vonn Vfb

共模電壓回授電路

由於差動電路的共模輸出電壓沒有定義,設計上需要有一個回授電路來定義差動電 路的共模準位,此電路的作用就是當共模準位因為製程飄移、輸入訊號不對稱等原因偏 移時,利用負回授到原本電路,將偏移的共模電壓修正。一般共模電壓回授電路有兩種, 第一種是屬於離散時間的回授,利用開關將電容預先儲存的電荷量,以電荷守恆的觀 念,將共模電壓慢慢修正,其優點是輸出共模電壓的偏移量範圍並不會影響電路回授的 機制,而且消耗功率極低,缺點是開關在切換時,會造成輸出訊號雜訊變大,並且作為 電荷平衡的電容也會造成輸出負載變大(如圖 3-7)。第二種是在連續時間下回授(如圖 3-8),其優點就是產生的雜訊對輸出影響小,缺點是對於共模偏移電壓有一定的操作範 圍,所消耗的功率也比開關來的大。由於本系統操作在 0.5-V 低電壓下,所以輸出操作 範圍也有限,對雜訊的要求也就更為重要,所以最後共模電壓回授電路是採用連續時間 操作的電路。 Vopp Vonn Vfb Vcm Vcm Vb C1 C1 C2 C2 1 2 1 2 1 2 圖 3-7 開關共模回授電路 連續時間回授電路是先用電晶體做成的電阻將兩端輸出共模準位偵測出來,這裡要 注意的是當作輸入電阻的兩端其值不能太小,否則放大器的輸出阻抗將會受到影響,導 致放大器增益下降,所以作為電阻的電晶體為長通道的 P 型電晶體。將輸出共模準位偵 測出來後,接著在與 Vcm 做比較,再藉由負回授將共模電壓修正。為了使偏移電壓能夠被抑制良好,負回授的增益必須越大越好,為了增加回授電路的增益,將輸入及操作 在次臨界區,提高輸入級的轉導值,並且為了提高 Mp0、Mp1 的負載值,將電路放入了 負電阻 Mp00、Mp11,使其增益從式 3.9 變為式 3.10。同樣的,負電阻的設計必須為類 比方式,即是 Mp00、Mp11 的電晶體尺寸必須小於 Mp0、Mp1。而通常會在輸入電阻處 並聯電容,電容的用途是提供零點,增加回授電路的頻寬及相位。 , . mi v cmfb mp g A g (3.9) * , . mi v cmfb mp mpf g A g g (3.10) Vopp Vonn Vcm Vb2 Vfb Mta Mip Min Mp0 Mp00 Mp11 Mp1 圖 3-8 連續時間共模回授電路

非重疊時脈產生器

在使用截波技術時,是由兩對開關所組成,並由時脈產生器來驅動開關,但是必須 要注意的是要使用兩個不重疊相位的時脈來驅動,避免訊號的相位錯誤。因此所需要的 就是一個非重疊時脈產生器,內部皆為基本的數位電路,利用正反器的延遲時間,來產 生兩個不同相位輸出的時脈(如圖 3-9)。Clk

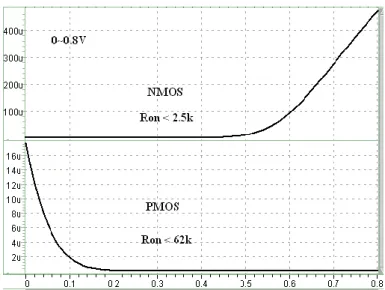

圖 3-9 非重疊時脈產生器 圖 3-10 非重疊時脈產生器時序模擬圖時脈拔靴式電路

截波電路即是使用開關來完成,也就是使電晶體操作在三極管區(Triode region),如 同電阻(式 3.11)。當操作在低電壓的環境下時,會因為電晶體的臨界電壓(Threshold voltage)及閘級電壓太小的關係,使得電晶體電阻變大,造成訊號調變時產生失真的現 象。如果靠電晶體的尺寸加大來減小電阻值會產生寄生電容過大,造成電荷注入(Charge injection)現象加劇的結果。 1 . ( ) on ox g in th R W C V V V L (3.11)先進製程下電晶體的非理想效應會使得當電晶體的Vgs 0時,電晶體還會有不小的電 流,這個現象也會使調變的結果變差。為了解決電晶體電阻及漏電流的問題,我們使用 了拔靴式(Bootstrapped)電路,如圖 3-11。M1、M4 負責升降壓電容的充放電,C1、C2 為升降壓電容,M2 及 M3 為開關。理想上輸出電壓 Clk_bo 會產生 2VDD ~ -VDD 的電 壓擺幅,2VDD 可以使得截波調變的電晶體電阻值很小,使訊號能在週期內穩定,-VDD 則是能讓開關的漏電流變小,減少訊號失真。由於輸出雙倍電壓會受到輸出節點的寄生 電容影響,所以實際上的電壓應該如式 3.12。由 3.12 式可知要提高雙倍電壓的值, bo para C C 是必要的條件。 _ bo 2 bo para C Clk bo VDD C C (3.12) Clk Clk_bo Cbo1 Cbo2 M1 M2 M3 M4 圖 3-11 拔靴式電路 圖 3-12 和圖 3-13 為拔靴式電路操作圖。圖 3-12 為當輸入訊號 Clk 由 VDD 變為 VSS 時,儲存在電容 Cbo1 的電壓 VDD 會使得 Va 的電壓從 VDD 變為 2VDD,此時 M2 將 會導通將將 Va 上的電壓傳導到 Clk_bo,而 Clk_bo 將會導通 M4 使得 Cbo1 的電壓降到

當 Clk 由 VSS 變為 VDD 時,儲存在電容 Cbo2 的電壓 VDD 會使得 Vb 的電壓從 VSS 變為-VDD,此時 M3 將會導通將將 Vb 上的電壓傳導到 Clk_bo,而 Clk_bo 將會導通 M4 使得 Cbo1 的電壓升到 VDD。在這個週期下,Cbo2 的功用是用來升壓,Cbo1 則是

重置本身的電壓。 Clk Clk_bo Cbo1 Cbo2 M2 Va M4 VDD VSS VDD VSS VDD VSS Vb 2VDD VDD 圖 3-12 拔靴式電路操作原理(VDD ~ VSS) Clk Clk_bo Cbo1 Cbo2 M1 M3 Va Vb VDD VSS VDD VSS VDD VSS VSS -VDD

圖 3-14 拔靴式電路輸出電壓模擬圖

圖 3-15 和圖 3-16 為開關在不同電壓下輸出的電導值,可以由兩圖比較出使用拔靴

式電路後,電晶體的電阻值將會明顯的變小。

圖 3-16 截波開關電導模擬圖(有拔靴式電路)

Gm-C 濾波器

由於 Gm-C 濾波器是用來濾出輸入差動電極偏移電壓的直流值,並加以回授並消 除,所以它必須要有極低頻的頻寬的,至少要小於 0.5Hz。為了製造出低頻的高通極點, 需要的是

F 等級的電容量,在此為一個外掛電容(如圖 3-17)。使用全差動的電流鏡有 幾個好處,第一個是這個電路的主極點是在第二級輸出級,加上外掛電容,其主極點頻 率將會非常的小,以確保系統的穩定。第二個就是全差動的架構消除差動電極偏移電壓 的能力比單端電路要好。此濾波器的用途是讓偏移電壓直流值濾出,所以在設計上線性 度並不重要,最主要的考量就是頻寬要夠小,否則一般的低頻生醫訊號也會被濾出,回 授到電路去,這樣將會使得輸出訊號失真。在電晶體的設計上,可以從式 3.14 和式 3.15 得知,為了使輸出的低頻雜訊能夠小,輸入級也是採用 P 型電晶體, 並操作在次臨界 區,增加電晶體的尺寸。1 m u ext g f C (3.13) 2 3 , 2 1 1 16 1 3 m n in thermal m m g V KT f g g (3.14) 2 2 3 , ker 1 1 3 3 1 1 1 m n in flic ox m g K V f f C W L W L g (3.15)

-+

+

-Gm Cext Vi-Vo+ Vo-Vi+ 圖 3-17 Gm-C 濾波器 Mb Mp1 Mp2 Mn3 Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vopp Vonn Vfb3.3 可程式化增益放大器

由於三種生醫訊號的振幅各不相同,所以在最後放大階段時,必須要有適當的增益 調整,來使得生醫訊號放大的更加完整,因此就需要可程式化增益放大器。圖 3-19 為 可程式化增益放大器。其中包含了一個全差動電流鏡放大鏡和電容回授。在輸入訊號到 放大器的輸入端形成了一個非常低頻的高通路徑,最後再由放大器的輸出端構成了一個 低通路徑,使整個增益放大器能夠阻擋儀表放大器來的直流偏移電壓,又可以抑制高頻 來的雜訊。整個電路的直流增益為 i f C C ,並且可用數位控制訊號來控制輸入電容,使得 整體閉迴路增益能夠變化。 1 1 ( ) 1 1 par i i v i L f o par f f m s R C C A s C C C s s A R C C G (3.16) Vin Vip Cf1 Cf2 Cp Cn Cp1 Cn1 Vop Von 圖 3-19 可程式化增益放大器圖運算放大器

運用在可程式化增益放大器的放大器,最主要就是要能夠提供準確的放大增益,並 且讓訊號能夠通過,比較重要的是由於生醫訊號都有著低頻的成分,必須要讓這些低頻成分通過,從式 3.16 可以看出運算放大器的增益越大,高通極點的頻率將會越小,而所 需電容量也可減小。由於增益放大器的回授因子並沒有如儀表放大器來的大,所以此電 路的頻寬並不是主要的限制,設計上是以放大器的增益和雜訊抑制為主,輸入級採用 P 型電晶體來抑制閃爍雜訊,並操作在次臨界區以提高轉導值(如式 3.17)。一些基本的式 子都與儀表放大器一樣,差別就是輸出級的阻抗,在這裡設計得比儀表放大器還大,犧 牲頻寬來換取放大器的開迴路增益。同樣地,差動電路也是需要共模電壓回授電路,此 處電路使用的共模電壓回授電路如同圖 3-8。

0 1 5 5 7 3 3 1 || m m o o m m f A g g r r g g (3.17) 1 m c L g f C (3.18) 3 3 2 , 2 1 1 16 1 3 m m f n in thermal m m g g V KT f g g (3.19) 2 2 3 2 3 , ker 1 1 3 3 1 3 3 1 1 1 m 1 m f n in flic ox m f f m g g K V f f C W L W L g W L g (3.20) Mb Mp1 Mp2 Mn3Mf3 Mf4Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vfb Vopp Vonn圖 3-21 開迴路放大器增益與相位圖 表 3-4 放大器增益頻寬的製程角落模擬表 TT FF FS SF SS Av(dB) 48.4 43.1 48.9 46.6 49.6 PM 84.0 86.0 84.2 84.2 84.1 fc(Hz) 38.9k 32.7k 41.3k 34.5k 40.4k 圖 3-22 放大器迴轉率模擬圖

表 3-5 放大器迴轉率的製程角落模擬表 mV s TT FF FS SF SS SR 3.0 2.9 3.3 2.6 3.3

預先放大器

在量測三種生醫訊號時,可以從表 3-2 發現,腦波訊號跟其他生醫訊號比起來 ,其振幅明顯比較小,在測量時,如果只有儀表放大器和可程式化增益放大器的話,放 大倍率是不夠的。因此在這個狀況下,需要在其中加入一級預先放大器,以提高整體訊 號的放大倍率,其電路如圖 3-18。設計上不使用負電阻,以達到適當的放大倍率,由於 預先放大器也是訊號必經的路徑,所以在雜訊的考量上也如同,儀表放大器及增益放大 器一樣重要。 1. m c L g f C (3.21)放大器設計原理

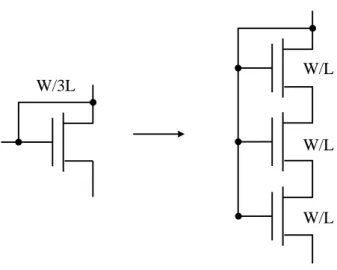

在上述設計各個不同規格的運算放大器,如圖 3-6、3-18、3-20,可以發現使用了很 多電晶體疊接的方式,如圖 3-23。這裡採用電晶體的原因主要有三個,第一個原因就是 在設計上電晶體的邊界電壓(threshold voltage)會隨著通道長度增加而變化,但是在此製 程下當長度太大時,N 型電晶體的邊界電壓會變為負的值,這在電晶體設計上是會造成 放大器誤動作,因此採用疊接的方式來使得每顆電晶體的通道長度在適當的範圍,避免 邊界電壓進入負的範圍,同時確保整個電晶體的通道長度夠大,以增加輸出阻抗。第二 個原因就是避免邊界電壓隨著通道長度增加而產生大變化。電晶體參數在各個製程漂移 下往往會產生不同的電流、阻抗,在這裡疊接電晶體所扮演的角色就是避免大的通道長 度來影響邊界電壓,減少影響電晶體參數的原因。第三個則是布局上的考量,借由將一 個長通道的電晶體拆成多個小通道長度的電晶體,使得佈局上可採用對稱的方式減小電減小寄生電容,使得頻寬避免受到寄生電容的影響太大。 W/3L W/L W/L W/L 圖 3-23 疊接電晶體示意圖

3.4 系統模擬結果與佈局

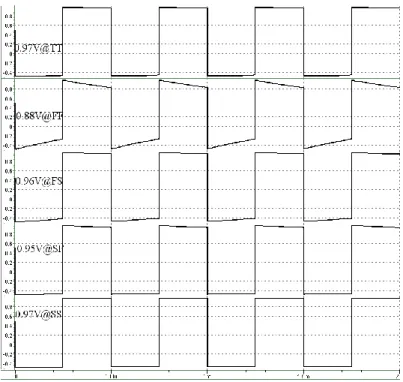

本節將會討論類比前端電路系統在實際心電圖輸入的模擬結果,如圖 3-33。 前端電路除了要負責放大生醫訊號之外,同時訊號的失真程度與否,也是非常重要的,也就是總諧波失真(Total Harmonic Distortion)。圖 3-24 為輸入訊號 100Hz、1mVpp 的弦波,輸出訊號的 FFT 頻譜圖。

表 3-6 總諧波失真表 TT FF FS SF SS THD (%) 0.031 0.048 0.017 0.084 0.14 圖 3-25 為本系統的增益頻寬模擬圖,訊號放大範圍為 0.5Hz~1kHz。基本上分為兩 種情形,針對腦波圖,系統的放大增益可以達到 66 dB ,振幅較大的心電圖和肌電圖, 則使用較小的放大增益。圖 3-26 為比較系統電路有無截波對雜訊的影響,圖 3-27 為截 波前端電路的雜訊模擬圖,在截波頻率為 4kHz 時,雜訊密度為 36.6 nV Hz,2kHz 時 為 50.7 nV Hz。表 3-9 為雜訊密度在製程角落的值。 圖 3-25 類比前端電路增益頻寬模擬圖 表 3-7 生醫訊號增益表 Signal Av (dB) EEG 59.4、64.6 ECG、EMG 29.5、34.7、41.7

100m 1 10 100 1k 0.0 5.0x10-5 1.0x10-4 1.5x10-4 2.0x10-4 2.5x10-4 3.0x10-4 V/ sq rt (H z)(V/ sq rt (H z)) frequency(Hz)

afe with chopper afe no choppper 圖 3-26 前端電路雜訊截波比較圖 100m 1 10 100 1k 3.5x10-8 4.0x10-8 4.5x10-8 5.0x10-8 5.5x10-8 6.0x10-8 6.5x10-8 7.0x10-8 7.5x10-8 V/ sq rt (H z)(V/ sq rt (H z)) frequency(Hz) chopper_2kHz chopper_4kHz 圖 3-27 前端電路雜訊模擬圖 表 3-8 前端電路雜訊模擬表 Noise Density (nV Hz) TT FF FS SF SS 4k 36.6 34.7 39.8 37.0 48.4 2k 50.7 51.3 45.7 47.5 52.6

表 3-9 生醫訊號雜訊總值表 Signal BW(Hz) IRN (μVrms) EEG 0.5~100 0.36 ECG 0.5~100 0.36 EMG 10~1000 1.59 由於輸入訊號的偏移電壓常常因為 60Hz 雜訊而發生改變,進而影響的內部前端電 路,因此身為前端電路的第一級必需要有抵抗的能力,圖 3-28 為儀表放大器的共模拒 斥比模擬圖,可以看到在 60Hz 時,其值是大於 110 dB。 此類比前端電路是採用 UMC 90nm 製程,圖 3-32 為本電路的晶片佈局圖。總面積 為 0.96 x 0.94 2 mm ,電路面積為 0.75 x 0.66 2 mm 。系統的規格總結為表 3-13。 圖 3-28 共模拒斥比模擬圖 表 3-10 共模拒斥比模擬表 TT FF FS SF SS CMRR (dB) 194 197 192 195 184

從圖 3-31 可以看出,加入製程漂移參數後,前端電路的 CMRR 值大概落在 80~90 dB 之間,與沒加入製程誤差的模擬值有很大的差距,圖 3-29 為放大器在共模模式下的示 意圖,由此圖可以推得式(3.21)、式(3.22),可以看出 CMRR 的值與放大器所看到的主動 負載有很大的關係,當在設計負電阻時,為了使放大器的交流增益變大,設計上讓負電 阻與正電阻值接近,以減小看到的負載阻抗,但這對共模增益而言卻是不好的選擇,因 為製程漂移而導致負載增加,這個結果將會使得 CMRR 下降。 2 1 2 L cm m b R A g R (3.21) 2 m b L L g R CMRR R R (3.22) Vic Rb RL RL+ΔRL Vic Rb RL/2 圖 3-29 共模增益示意圖 Mb Mp1 Mp2 Mn3 Mf3 Mf4 Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vopp Vonn Vfb Mn3 Mf3 Mf4 Mn4 圖 3-30 實際放大器負電阻示意圖

0 20 40 60 80 100 120 140 160 180 200 0 100 200 300 400 500 N u mb e r CMRR (dB) AFE_CMRR SIGMA=3 TEMP=27 NUMBER=1000 圖 3-31 共模拒斥比蒙地卡羅模擬圖

CLK

PGA cap

PGA cap

IA cap

IA cap

IA cap

IA cap

PGA cap

PGA cap

IA

PRE

PGA

圖 3-32 類比前端電路晶片佈局圖表 3-11 類比前端電路功率消耗表 Power(μ W) BIAS 0.68 IA 2.16 PGA 0.62 PREA 1.43 Total 4.89 Total(no bias) 4.21

表 3-12 類比前端電路規格總結表

Spec. Value Unit

Supply Voltage 0.5 V Supply Current 8.42 μ A Power 4.21 μ W Gain 26~66 dB NEF 3.26/2.77 Input-referred Noise Density(0.5~1kHz) 36.6/50.7 (4k/2k) nV Hz THD <0.1 % CMRR(60Hz) >110 dB

High Pass -3 dB frequency 0.5 Hz

Low Pass -3 dB frequency 1k Hz

AFE SFDR 70.2 dB Chip size 0.96 x 0.94 2 mm Core area 0.75 x 0.66 2 mm Technology 90 nm

NEF: Noise Efficient Factor

, 2 4 tot ni rms T I NEF V V kT BW

3.5 規格比較

整個類比前端電路的規格比較表如下所示。整個電路所消耗的電流量為 8.42μ A, 輸入相對雜訊為 0.36μ Vrms (100Hz),電路面積為 0.49mm2。 表 3-13 類比前端電路規格比較表 Spec. Tim Denison, JSSC 07[11] R.F. Yazicioglu, JSSC 07[9] R.F. Yazicioglu, JSSC 08[10] X.Zou Y.Lian JSSC 09[14] L.Yan, H.Jun Yoo JSSC 10[15] This work Supply Voltage 1.8~3.3V 3V 3V 1V 3V 0.5V Supply Current 1.0μ A 11.1μ A 3.6μ A 337 nA 1.66μ A 8.42μ A Power 1.455mW 33.3μ W 10.8μ W 0.33μ W 5μ W 4.21μ W Gain 41~50.5 dB 51~67dB 72~81dB 45~60dB 58~70dB 26~66 dB NEF 4.6 4.7 4.3 3.26 3.1 3.26/2.77 Dynamic Range 50.5 dB 67 dB 81 dB 60 dB 60 dB 66 dB Input-referred Noise RMS 0.95μ V (100Hz) 0.57μ V (100Hz) 0.59μ V (100Hz) 1.16μ V (100Hz) 0.51μ V (100Hz) 0.36μ V (100Hz) High Pass -3 dB frequency 0.05 Hz 0.5 Hz, 10 Hz 0.5 Hz, 4.5m Hz, 0.5 Hz, 0.5 Hz Low Pass -3 dB frequency 180 Hz >150 Hz 675 Hz 292 Hz 625 Hz 1 kHz Core area NA 1.95 2 mm 17.55 2 mm (8-channel) 1 2 mm 2.6 2 mm 0.49 2 mm Technology 0.8 μ m 0.5 μ m 0.5 μ m 0.35 μ m 0.18 μ m 90 nm第四章

0.5-V 類比前端積體電路設計(二)

4.1 介紹

前一章節裡介紹了一個運用於 0.5-V 系統的類比前端電路。本章節要介紹另一種系 統架構的類比前端電路,最後進而比較這兩種架構在 0.5-V 下的優缺點。4.2 節為本電 路簡介。再來 4.3 節為電路的設計與模擬,及 4.4 節為晶片的佈局與規格。4.2 類比前端電路與規格

本章節所提出的類比電路系統架構如下圖 4-1 所示。基本上和第三章的架構差不多, 差別在於內部電路與放大倍率的不同。而系統規格的要求為操作在 0.5V 電壓下,各項 規格要求就如同表 3-1。 IA PGA ADC Preamp 26 dB -6 dB~18 dB 32 dB 圖 4-1 類比前端電路架構圖4.3 儀表放大器

本節將會說明使用的儀表放大器。圖 4-2 為所使用的儀表放大器,內含有兩組截波 調變開關、運算放大器、低通濾波器及一個外掛電容。和第三章不同處為此儀表放大器 並沒有可變增益的功能,其餘的功能就跟第三章的一樣。 -+ + - Vipc Vinc -+ + -Gm Vonc Vopc Cext Ci1 Ci2 Cf1 Cf2 Ch1 Ch2 圖 4-2 儀表放大器電路圖運算放大器

用於儀表放大器的電路如圖 4-3,式 4.1 為此電路的開迴路增益,在這裡跟第三章 不同的是 Mn3b、Mn4b,這裡當作負載來使用,減少 Mn3 和 Mn4 的電流,增加其轉導 值。雜訊考量方面跟第三章的設計是一樣的,這裡也是針對輸入級來改善,採用 P 型電 晶體並操作在次臨界區,以增加轉導值和低雜訊的效果。表 4-1 為此放大器的一些基本 規格。

1 5 5 7 3 || m o m o o m g A g r r g (4.1) 1 m c L g f C (4.2) 2 3 3 , 2 1 1 16 1 3 m m b n in thermal m m g g V KT f g g (4.3) 2 2 2 3 3 , ker 1 1 3 3 1 3 3 1 1 1 m 1 m b n in flic ox m b b m g g K V f f C W L W L g W L g (4.4) Mb Mp1 Mp2 Mn3 Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vopp Vonn Vfb Mn3b Mn4b Vb2 圖 4-3 儀表放大器內部運算放大器圖表 4-1 放大器規格表 TT FF FS SF SS Av(dB) 42.2 38.3 41.1 43.1 43.2 PM 83.1 77.6 79.8 78.5 89.2 fc(kHz) 245 208 275 185 305 SR(mV ) s 10.9 9.5 17.9 6.3 20.7

共模電壓回授電路

由於第四章所提出的類比前端電路也是全差動的型式,故也是需要共模回授電壓電 路來定義共模電壓,如圖 3-8 所示。在這裡要注意的是由於回授路徑的不同,在設計上 要使共模負回授路徑穩定,詳細情形如同第三章所述。非重疊時脈產生器和拔靴式電路

在低壓操作截波調變開關時,需要兩個相位的時脈來驅動開關,且由於在低電壓操 作,開關的電阻值也是設計的重點。因此就需要非重疊時脈產生器和拔靴式電路來解決 開關調變的問題。基本操作原理就如同 3.3 節所述。圖 4-4 為使用的電路架構。Clk

Non-overlapped Clock generator

Ph Phb M1 M3 M5 M2 M4 M6 圖 4-4 非重疊時脈產生器和拔靴式電路圖

Gm-C 濾波器

此濾波器的功能是能夠濾出因為電極片所造成的偏移電壓,並經過截波調變後,將 因為電極片所造成的偏移電壓經由負回授回授到輸入節點,藉此抵消輸入直流偏壓。這 裡採用的運算放大器,也是屬於電流鏡放大器,在這裡不使用增加增益的方式來設計運 算放大器,因為本放大器最主要是要濾出直流偏壓值,不需要太高的增益。圖 4-5 為內 部電流鏡放大器。Mb Mp1 Mp2 Mn3 Mn4 Mp7 Mn5 Mp8 Mn6 Vin Vip Vb1 Vfb Vopp Vonn Vfb 圖 4-5 Gm-C 濾波器內部放大器圖

4.4 可程式化增益放大器

在本節將要介紹可程式化增益放大器,在第三章已經介紹過它的基本原理。本節將 要強調它與第三章不同的地方。最主要的差別是在於此增益放大器可以選擇的增益範圍 較多以及內部電路的不同。運用於增益放大器的電路如圖 4-6,為了增加開迴路的增益, 同樣地,使用了增益增強的電流鏡放大器。由 3.16 式可以知道閉迴路的高通極點是由放 大器的開迴路增益和電容所決定的,當使用此架構時,缺點就是電容量會太大,而且會 使得儀表放大器的負載增加,減少頻寬。預先放大器

在測量生醫訊號時,腦波的振幅是屬於較小的,如果要放大到跟心電圖和肌電圖一 樣的大小時,需要有多一級的放大器,此預先放大器就是為了腦波圖而存在的。如圖 4-5 所示。表 4-2 可程式增益放大器增益表 Code Av(dB) 000 -6 100 0 101 6 110 12 111 18 -+ + -Vipp Vinn Cf1 Cf2 Cp Cn Cp1 Cp2 Cp3 Cp4 Cn1 Cn2 Cn3 Cn4 Vopp Vonn 圖 4-6 可程式化增益放大器圖

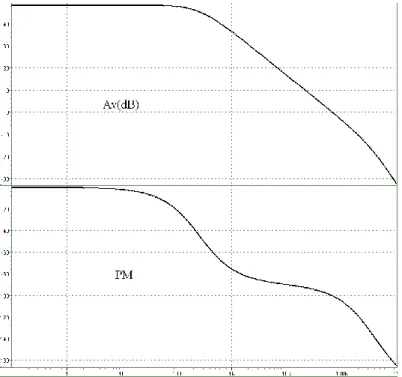

4.5 系統模擬結果與佈局

在這節將會討論本系統的模擬結果,包括心電圖訊號、系統頻寬以及雜訊的影響。 圖 4-7 為輸出訊號端的 FFT 頻譜圖,輸入訊號為 100Hz、1mVpp 的弦波,由此可以 看出輸出訊號的失真程度。 圖 4-7 類比前端電路 FFT 模擬圖 表 4-3 總諧波失真表 TT FF FS SF SS THD(%) 0.04 0.16 0.02 0.12 0.19圖 4-8、4-9 是本架構的增益頻寬模擬圖,中頻帶為 0.5Hz~1kHz。基本上也是分為 兩個情形來放大訊號,跟第三章較不同的是,由於可程式化增益放大器的變動增益範圍 較大,所以整體的增益範圍較廣。最大增益為 78 dB,最小增益達 28 dB。 圖 4-11 代表著抑制 60Hz 雜訊的能力,一般的電路規格在 60Hz 時,共模拒斥比要 大於 110 dB。 圖 4-8 針對肌電圖和心電圖的增益頻寬圖 圖 4-9 針對腦波圖的增益頻寬圖