國

立

交

通

大

學

機械工程學系

碩

士

論

文

CMOS製程相容之熱驅動、壓阻式微感測振盪器設計

與製作

A CMOS micromachined resonant sensor with thermal actuation and

piezoresistive sensing

研究生:王俊傑

指導教授:陳宗麟 教授

中 華 民 國 九 十 八 年 十 月

CMOS製程相容之熱驅動、壓阻式微感測振盪器設計與製作

A CMOS micromachined resonant sensor with thermal actuation and

piezoresistive sensing

研 究 生:王俊傑 Student:Chun-Chieh Wang 指導教授:陳宗麟 Advisor:Tsung-Lin Cheng 國 立 交 通 大 學 機 械 工 程 學 系 碩 士 論 文 A ThesisSubmitted to Department of Mechanical Engineering College of Mechanical Engineering

National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of Master in

Mechanical Engineering

October 2009

Hsinchu, Taiwan, Republic of China

CMOS製程相容之熱驅動、壓阻式微感測振盪器設計與製作 學生:王俊傑 指導教授:陳宗麟 國立交通大學機械工程學系﹙研究所﹚碩士班 摘 要 本論文藉由CMOS製程,設計製做出以電熱驅動之微振盪器,並以壓阻 材料作為感測元件,此結構可藉著吸附預量測物質,改變結構的共振頻, 經由壓阻材料的電阻值將質量變化轉換為電訊號,計算所吸附物質的重 量。此元件可應用於量測氣體與流體中物質含量,在生醫工程領域,可依 吸附材料不同感測物質或細胞之密度。 為設計出高效能之微振盪器,研究中使用電熱轉換來驅動元件,並對 於驅動端經由有限元素模擬將尺寸及形狀作最佳化設計。另外,藉由研究 CMOS製程中壓阻材料-polysilicon的壓阻性質,了解影響壓組材料特性的各 種因素,並建立其物理模型。將結果應用於提升感測性能的穩定性與準確 度。為使元件有良好的穩定度與高感測效能,以橋樑式結構作為元件的形 狀(如下圖),此設計可將電熱驅動與感測元件分開,避免溫度改變壓阻材料 之特性,且維持感測元件的位移量。經由相關量測,得到元件在0.5mW的 功率下,共振頻振幅可達0.6μm,並且在給予負載情況下,能藉由前後共振

A CMOS micromachined resonant sensor with thermal actuation and piezoresistive sensing

student: Chun-Chieh Wang Advisors:Dr. Tsung-Lin Cheng

Department of Mechanical Engineering National Chiao Tung University

ABSTRACT

Micromachined resonant sensors have the advantages of robust measurement and quasi-digital output and thus have been applied to various applications such as: pressure measurement, bio-molecular detection, and etc. Realizing these devices with industrial IC CMOS processes is attractive for low cost. However, it can be very challenging for engineers to optimize the device performance. This study intends to develop a resonant sensor using commercially available CMOS process (TSMC, 2P4M) and one post-process step. This resonant sensor is excited by the electro-thermal actuations and the motions are measured by the piezoresistive sensing. The design procedures are discussed in details to indicate that this could be an optimal design with this fabrication process. Besides, different to most sensor applications that acquired piezoresistivity of a film by experiments, this study intend to develop theoretical models to predict it from the film conditions. The existing models cannot be applied because they were all developed for P-type silicon with low doping concentrations. However, it is highly doped, N-type polysilicon in this process.

誌

謝

研究所兩年的時間很快,從剛進實驗室的懵懂無知,到畢業時看著自 己的畢業論文,驚覺在學校的生活已經要離開了。兩年的研究生涯受到非 常多人的照顧與幫助,其中最感謝的是指導教授陳宗麟老師,老師在研究 方向以及態度給予我許多的靈感與幫助,另外在生活中也給予相當多的照 顧,讓我能在兩年的研究過程中收獲甚多。接著要感謝的是博士班的俊胤 學長,在研究遇到瓶頸時,學長總是和我一同討論和解決問題,而在實驗 器材上更是給予我非常大的幫助,指導我使用各種實驗儀器,讓我在實驗 上比別人更為順利,若是沒有學長的幫助,甚至可能沒辦法在兩年完成這 篇研究論文。另外要感謝國家晶片研究中心(CIC)的學長們的幫忙,給予元 件設計一個製程平台,另外在量測儀器上學長們也給予相當多的支援,使 我的研究成果能順利製作。另外要感謝許多在儀器操作以及其他幫忙的學 長們,希望老師以及各位學長在未來研究和工作中都能一帆風順,在人生 規劃上都能順心如意。

目

錄

中文摘要……….i 英文摘要………ii 致謝………...iii 目錄………iv 表目錄………vi 圖目錄………..vii 一、 序論……….………1 1.1 研究動機……….………1 1.2 文獻回顧……….2 1.2.1 MEMS 驅動方式………2 1.2.2 驅動器應用………4 1.2.3 MEMS 感測方式與應用………4 1.3 研究目標……….………...5 二、 壓阻模型建立……….13 2.1 多晶矽的阻抗性值……….13 2.2 單晶矽的壓阻原理……….17 2.2.1 單晶矽的壓阻性值………19 2.2.2 多晶矽的壓阻性值………21 2.3 實驗與計算………21 2.3.1 量測晶粒尺寸………..22 2.3.2 理論與實驗驗證………22 三、 微致動器結構設計……….31 3.1 概述 TSMC 0.35 μm 製程………...31 3.2 結構設計……...………..32 3.2.1 驅動方式與設計………..33 3.2.2 感測方式與設計………..35 3.3 模擬與分析……...………..37 3.3.1 電熱驅動結構選擇………..38 3.3.2 結構熱分析模擬………..40 3.3.3 元件特性模擬……….,,.41 四、 實驗量測與討論……….52 4.1 元件成品結構………52 4.2 未負載元件量測………52 4.2.1 穩態量測………..53 4.2.2 頻率響應量測………..54 4.3 負載元件量測………54

4.3.1 穩態量測………55 4.3.2 頻率響應……….………..55 五、 結論………...………..64 5.1 研究成果……….………64 5.2未來工作…….……….………65 參考文獻………..66

表目錄

表1. 各類型驅動方式特性比較………...7 表2. 不同方向之壓阻參數……….28 表3. 材料模擬參數……….45 表4. 不同設計之結果比較……….49 表5. 未負載時輸入電壓與兩端撓曲量之變化……….59 表6. 負載後輸入電壓與兩端撓曲變化……….62圖目錄

圖1. 以靜電驅動之電梳結構………8 圖2. 以靜電驅動之可變電容………8 圖3. 懸臂樑式音壓感測器………9 圖4. 橋樑式音壓感測器………9 圖5. 夾取生物細胞之力感測器………..10 圖6. 用以磁感測之懸臂樑………..10 圖7. 以表面Au吸附物質之懸臂樑感測器……….11 圖8. 懸臂樑結構陣列………..11 圖9. 結合惠斯通電橋與電路之微感測器………..12 圖10. 設計結構簡介………...12 圖 11. 多晶矽晶粒示意圖………...23 圖 12. 多晶矽晶粒等效電阻………...23 圖13. 純矽之能帶與摻雜不同濃度之 P 與 N 型半導體能帶圖………..24 圖14. 能帶熱平衡示意圖………...24 圖15. 能帶加入偏電壓變化………...25 圖16. 晶粒邊緣之能帶變化………...25 圖17. (a)自由電子能帶與(b)受晶格限制產生不連續之能帶………26 圖18. 自由電子與受晶格限制電子之能帶比較………...26 圖19. 三軸 k 向量空間形成之橢圓形能帶………27 圖20. 能帶受力產生之變形………...27 圖 21.尤拉角轉換………28 圖22. 不同溫度及濃度之 n-type 壓阻參數………29 圖23. 多晶矽晶粒………...29 圖24. 結構撓曲與其 gauge factor 關係圖……….30 圖25. 不同晶粒尺寸與電阻率及 gauge factor 關係圖……….30 圖26. CMOS 製程之材料結構層………42 圖27. 下線成品損壞部分………...42 圖28. 懸臂樑與橋樑結構之變形比較………...43 圖29. 為振盪器之結構設計………...44 圖30. 懸臂樑模擬尺寸………...46 圖31. 給予電壓後模擬撓曲結果………...46 圖32. 多晶矽加熱通道………...47 圖33. 不同驅動設計之剖面………...48 圖34. 提高厚度時結構撓曲情況(結構層至 metal 3)………49 圖35. 元件模擬示意圖………...50 圖36. 結構溫度變化分布………...50圖37. 結構受熱後之變形(俯視)……….51 圖38. 結構受熱後之變形(側視)……….51 圖39. 避免因蝕刻損毀所做補強………...57 圖40. 元件成品………...57 圖41. 掃描元件變形情況………...58 圖42. 量測驅動端之變形量(綠色區域為驅動端,虛線區域為吸附平台)………58 圖43. 量測感測端之變形量(虛線區域為吸附平台,紫色區域微感測端)………59 圖44. 感測端應變與電阻變化關係圖………...60 圖45. 驅動端加熱後溫度分布………...60 圖46. 未負載元件之頻率響應………...61 圖47. 給予質量塊於吸附平台………...61 圖48. 負載後驅動端撓曲變化………...62 圖49. 負載後元件頻率響應圖………...63 圖50. 負載前後共振頻比較………...63

第一章 序論

1.1 研究動機

從半導體產業的發展以來,CMOS(Complementary Metal Oxide

Semiconductor)已普遍使用在 IC 製程上,在許多年投注龐大的人力以及資金 於此製程的研究後,不僅提高了製程的可靠度以及良率,並且降低了製造 成本。如今 CMOS 製程的發展已趨近成熟和穩定,除了繼續延續製程的研 究外,對於特殊製程的需求以及更龐大的系統整合是更為重要。

在 CMOS 的應用領域中,與微機電(Micro Electric Mechanical System, MEMS)整合是一項重要的發展。微機電是以近似半導體元件製作方式,如 曝光、微影、蝕刻、沉積、濺鍍等方式製作出微米尺度之機械結構,其中 部分甚至包括特殊機械加工技術,以做出特殊規格之原件。微機電目前已 應用在製作各種微型驅動器感與測器等產品,對於以CMOS 製程來製作微 機電結構擁有許多優勢,包括: 1. 利用CMOS標準製程,可直接製作微機械結構,並且與周邊電路結合, 達到機電整合之目的。 2. 藉由整合CMOS與微機電系統,可降低事後機電整合所產生之雜訊,另 外可藉由電路設計,將訊號作類比與數位轉換,方便後段量測與控制等

3. 由於現今CMOS製程皆已自動化,對於人為因素所造成如光罩對準等因 素可大幅降低,藉由與半導體廠合作,提高製程精密度與穩定度,有利 於機械與半導體產技術合作與交流。 近年來CMOS MEMS已有相當的產品應用於日常生活,如陀螺儀、加 速規與溫度感測器……等皆與周邊電路共同整合於單晶片中。根據相關文 獻中描述,微機電元件大都是由驅動器、感測器與微型結構組成,在驅動 部分大多採用靜電式[1][2]或電熱式[3][4],感測器則採用壓阻或電容方式量 測,其主要原因在於與製程整合度高,且易於控制及量測。因此本研究以 使用CMOS 製程之優勢,將電熱驅動與壓阻感測功能設計於同一元件並且 製作,並透過量測,以了解元件之性能。

1.2 文獻回顧

近十多年來關於CMOS MEMS之研究已有相當規模之發展,其中較為 知名的產品,像是ADI所設計製作之加速規[5],應用於安全氣囊作動之感 測,以提高駕駛人與乘客的安全,另外德州儀器(TI)的微光學鏡面投影機 [6]……等。為了解現今CMOS MEMS所使用之技術,以下將分別介紹: CMOS MEMS 於驅動及感測部分與其應用。1.2.1 MEMS 驅動方式

一般主要的驅動原理有以下四大類,分別為壓電、靜電、電磁、電熱驅動等,以下將介紹各種驅動方式其特性。 (1) 壓電驅動:利用壓電材料將電能轉為形變,特色是轉換迅速,具有 高效率與準確性,可在高頻下操作,並能較容易將訊號進行機電轉 換。但由於MEMS 基材多以矽為主,矽材並不具壓電特性,因此 必須另外鍍上壓電材料,此方法無法於CMOS 製程中使用。 (2) 靜電驅動:其驅動特性為低耗能、反應迅速且與CMOS製程相容。 靜電致動主要靠不同電位所形成電場,產生靜電力,藉以驅動元 件。一般驅動元件有梳狀與平行極板,兩者皆可做垂直與水平位 移。以CMOS 製程製作靜電致動器,因電場強度會隨距離增加而迅 速降低,故必須事先考量驅動器之出力與運動行程之關係、使用面 積等因素。如垂直梳狀致動器(圖1.),致動行程受限於CMOS 製程 結構厚度,增加梳狀電極對數,理論上可增大出力,但因製程會有 殘餘應力問題,若結構形狀產生彎曲等改變,將使驅動能力大幅降 低。 (3) 電磁驅動:藉由電磁場產生之勞倫茲力來驅動元件,具有大驅動 力、大位移表現且無電極板限制之特點。但消耗功率大,使應用範 圍較為狹窄,且沉積線圈的磁性材料與CMOS 製程並不相容,不易 後續整合與晶片封裝。

將上列四種不同驅動方式之特性整理,並列於表1。

1.2.2 驅動器應用

CMOS MEMS 驅動器可應用於光學鏡面[7]、加速規[8]與RF電容調節 器[9]等,其致動原理多採靜電或電熱方式,主因為與CMOS 製程相容。其 中Boser採後段CMOS 製程之面型微加工技術,並將之應用於RF電壓控制可 變電容,如圖2.,Ioana Voiculescu則以電梳結構設計振動式驅動器[10]。電 熱驅動是藉由溫度變化,使材料產生膨脹或縮收現象,達到作動的效果。 藉由單一結構的熱膨脹,可設計出線性運動元件;或以不同材料的熱膨脹 係數,加熱後彎曲達到同平面或出平面的運動行為。Oliver Brand以電熱驅 動方式,振動平板結構,並且透過壓阻材料感測外界壓力變化,製作出樑 式(圖3.)和橋式(圖4.)聲壓感測器。此外,也有研究提出相關熱致動之理論分 析,便於設計者設計分析。1.2.3 MEMS 感測方式與應用

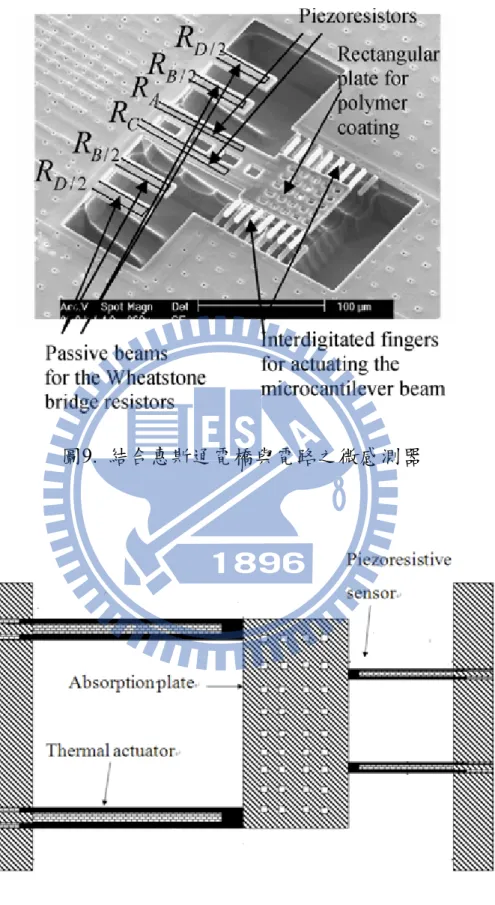

CMOS MEMS 最大宗的應用是微感測器與電路之整合。感測原理以電 容及壓阻式感測居多,兩者為目前發展較成熟的感測方式,優點是易於將 數值轉為電訊號輸出,且與CMOS 製程相容性高。Gisela設計具夾持生物細胞之機構[11],整合壓阻感測與電路,定量計算細胞收縮力之大小(圖5.)。 Beroulle以沉積鋁導線於U型懸臂樑自由端之設計[12],使感應電流流經線 圈,當外界存在電磁場時,將產生勞倫茲力,造成懸臂的形變或運動,另 外在懸臂樑的固定端以多晶矽層做為壓阻感測器,可做為磁感測之應用(圖 6.)。Don Klaitabtim以CMOS 製程製作成U 形懸臂樑結構[13],並採多晶矽 做為壓阻感測臂,在懸臂樑上覆蓋一層Au金屬,吸附生化物質或細胞感測 其重量,如圖7.與圖8.所示。Lakdawala藉著雙層膜熱膨脹係數的不同[14], 受熱致動同時以側向電容變化進行感測,製作熱紅外線像素感測元件並與 IC 整合,將電容變化轉換為電壓輸出。另外Fedder所提出的利用金屬及二 氧化矽作為結構層[15],完全不需與後續晶片再結合的技術,僅依賴CMOS 的製程而將電路及加感測器的結構一起製作完成,如圖9.。類似同樣的設計 概念也出現在其他文獻當中,如Tielert、Ha以多晶矽作為結構層,以及Pister 同時利用金屬、多晶矽及二氧化矽做結構層等設計。

1.3 研究目標

本研究使用的製程為TSMC 0.35μm製程,結構層則為2P4M(兩層多晶矽 層以及四層金屬層),經由研究壓阻材料特性,了解影響壓阻性質之因素, 得到設計結構所需要的相關資料,以便於元件設計。經由結構層模擬,設 計並製作出電熱式微型振盪器,並且擁有壓阻感測器的功能,圖10.為振盪特點是完全依賴CMOS製程來定義與釋放結構,以便未來與周邊電路整合, 便於量測訊號以及控制等操作。

致動形式 特性 缺點 壓電 (piezo-electric) 可在高頻下操作 大驅動力 準確的操控性 不易與IC 製程相容 靜電 (electro-static) 低消耗功率 反應速度快 在間距小時驅動力大 行程與驅動力相反 須串聯多平板 電磁 (electro-magnetic) 大驅動力及大位移 無電極板限制 消耗功率大 須外部供給磁場能量 不易與IC 製程相容 電熱 (electro-thermal) 低驅動電壓 驅動力大 可藉由機構設計放大 位移 消耗功率大 不易於高頻下操作 可靠度與穩定性問題 表1. 各類型驅動方式特性比較

圖1. 以靜電驅動之電梳結構

圖3. 懸臂樑式音壓感測器

圖5. 夾取生物細胞之力感測器

圖7. 以表面Au吸附物質之懸臂樑感測器

圖9. 結合惠斯通電橋與電路之微感測器

第二章 壓阻模型建立

在本研究設計之微振盪器中,包含了感測器功能,結構層的材料性質 與感測方式必須相互配合,才能達到其目的。微振盪器是令機械結構振動, 因此所感測的要素即是對共振頻率的變化量。在TSMC0.35 製程中,氧化 矽以及金屬層對於結構的變化並無明顯的回饋反映,而另一項材料-多晶矽 則是一種壓阻材料,恰好能與對應於所需要感測的項目相同。若要增進微 振盪器的效能,對於壓阻材料特性的了解是不可或缺的,以下介紹多晶矽 的電阻率,以及壓阻性質的原理。2.1 多晶矽的阻抗性值

多晶矽(polysilicon)是由許多晶粒(grain)所組成,每個晶粒的示意圖如圖 11.所示,在每個晶粒之間的邊緣都有邊界(grain boundary),故多晶矽的總 電阻值會包含晶格(crystalline)以及邊界的阻值,如圖 12.。多晶矽的總電阻 率如下[16] g 1 2W b 2W L L (2-1) 其中 是晶格的電阻率; 是邊界的電阻率;L 是晶粒長度;W 是晶格與 邊界之間空乏區的寬度;l 為晶格寬度;δ則是邊界寬度。 首先,晶格的阻值與自由電子濃度以及其移動率(mobility)有關[17],其阻值可以由(2-2)式來表示 g 0 1 qn (2-2) 其中q 為電子帶電量,μ為電子(或電洞)在導帶(conductivity band)的移動 率,n 為自由電子(或電洞)濃度。以 N-type 矽的能帶為例[18],導帶中自由 電子的數量,與其雜質參雜濃度有很大的關係。當參雜濃度較低時,由於 本質載子由價帶躍遷到導帶的數量高於雜質載子的濃度,所以自由電子的 來源大多是由本質載子(intrinsic carrier)躍遷所提供。當濃度逐漸升高,因雜 值能帶較接近導帶(圖 13.),其電子躍遷的數量會迅速增加,導帶中的自由 電子濃度逐漸以雜質載子為主。若 ,我們可以使用波茲曼分布 (Boltzmann distribution)來簡化能帶的表示式,能帶模型中的費米能階可由 (2-3)式表示: (2-3) 其中 為導帶能量, 為本質態位密度, 為雜質參雜濃度。在一般濃度 中,費米能階位於導帶與雜質能帶之間。得到費米能階後,可以計算導帶 中自由電子濃度: (2-4) 其中 為雜質能帶中電子密度, 為雜質能階。

當參雜濃度接近本質態位密度(intrinsic state density),甚至更高,此時 必須使用費米分布(Fermi distribution)來表示能帶狀況[18~20],此時導帶中

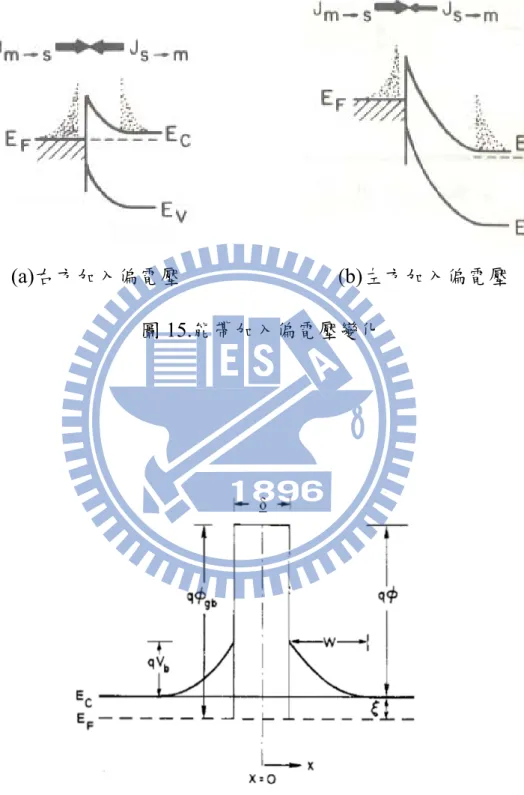

自由電子濃度為 (2-5) 此外,在高濃度的情況,由於雜質能帶上存在非常多電子,形成一近似導 電帶之能帶,故等效導電帶能隙將會下降: (2-6) (2-7) 在TSMC0.35 製程下,雜值參雜濃度為 ,由(2-3~7)式所得到 之自由電子濃度帶回(2-2)式,即可得到晶格的電阻率。 接著是計算晶粒邊界的電阻率[16][21][22],下面所考慮的是 n-type 的 多晶矽,由於p-type 多晶矽情況由於和 n-type 差異不大,只要將部分參數 改成p-type 所使用的數值,即可求得其阻值。在此我們將晶粒與邊界的情 況假設成類似MOS 電容的模型。不同的地方在於,MOS 電容式由金屬 (Metal)、氧化層(Oxide)和半導體層(semiconductor)所組成,而多晶矽則是由 半導體-邊界-半導體所組成。MOS 的邊界模型稱為 Shottky barrier,如圖 14.所示。當其達到熱平衡時,兩端的電流密度會相同,如圖 15.(a)及(2-8) 式所示。 * 2 bi m s s m qV J J A T exp kT (2-8) 其中 為電流密度係數; 為能障高度。當給予一順向偏壓 時,導體流

ΔJ 為 * 2 bi a a m s s m * 2 bi a qV qV qV J J ‐ J A T exp exp ‐exp

kT 2kT 2kT qV qV 2A T exp sinh kT 2kT (2-9) 多晶矽邊界部分由於其能帶高於兩端的半導體晶粒,故可視作ㄧ絕緣 體。邊界與其兩端的能帶關係圖如可參考圖16.。圖中可看出晶格導帶高度 較邊界低,在熱平衡後,靠近邊界的導帶將會向上彎曲,形成空乏區,彎 曲部分的寬度稱為空乏區寬度。在無外加偏壓的情況下,邊界兩端空乏區 寬度可視為相同。邊界與晶格的電位關係可由Poisson’s equation 求出 , => , (2-10) 則電位 可表示為 (2-11) 其中 為矽的介電常數;N 為摻入雜質濃度。

由材料的trapping state density 和雜質濃度的關係,可用(2-15)式求得空乏 區寬度W

(2-12) 在前面我們假定晶格與邊界的關係是一個半導體對半導體的

ba b

V

J 2W (2-13) 其中 為對每個晶粒所給予的偏電壓,J 則是通過邊界的電流密度。由 thermionic-emission theory 在 Schottky barrier diode 的應用,當給與ㄧ能障(在 此情況所指的是邊界)偏電壓 時,可得到其電流密度,如(2-14)式所表示 ---(2-14) 若偏電壓 <<2kT/q,則(2-14)式可改寫成 ---(2-15) 將(2-15)式帶入(2-13)式中,可得到邊界的電阻率 ---(16) 最後,由(2-1)、(2-2)、(2-12)和(2-16)式,即可求得多晶矽的總電阻率。

2.2 單晶矽的壓阻原理

當矽晶格在受到應力作用時,會使晶格的能量產生變化,進而改變電 子的傳導率,這就是所謂的壓阻性質。在說明應力如何改變電子傳導率之 前,首先要了解電子在晶格內的狀態。圖17.(a)是自由電子對倒晶格向量 k 的E-k 圖[23~25],在無拘束的情況下,自由電子對於向量 k 可以拋物線來 描述。若受到其它粒子或是邊界的束縛,將會使能量形狀產生改變。圖17. (b)是受到束縛時,轉變成近似自由電子的 E-k 圖。由圖中所示,在 時有能隙 , 是因電子波在 處發生布拉格散射(Bragg’s scattering)所 產生, 為第一布里淵區(Brillouin zone),第一與第二能帶相當於價帶 和導帶。將圖2-7.(b)每ㄧ能帶畫在每一布里淵區中,並與圖 17.(a)比較,如 圖18.所示晶格內的電子,會受到晶格粒子的影響而產生數個能帶,而每條 能帶之間都會有一個能隙(band gap)。由於自由電子無此影響,故其能量為 一連續曲線。圖19.為將傳導帶最小值附近所有倒晶格向量 k 的組合,在 k-space 所形成的等位面當[100]與[ ]受到壓應力作用時,其等位面會因此 而改變,如圖20.所示,其中[100]的導帶降低,投射到 k-space 的等位面因 此而變大。 ,能量用ε表示: 等位面的曲率也隨之改變。若電子的速度是

1 g 1 g 1 2 g 2 2 * 2 2v

d /dk

eEv

k

E

t

dk

dδ

dv

k

dt

dt

dv

dk

dt

dt

d /dk

m

k

g 2 2 2t

e

F

d d

dk

F

d /d

由於電子在矽晶格內的傳導率 ,其中e 為電子電量, 為電子有 效質量,τ為電子移動時間。由上式可知,當等位面曲率改變,會改變電 子的有效質量,進而改變電子的傳導率,所以矽晶格的導電性會因此而產生改變。

2.2.1 單晶矽的壓阻性值

ㄧ般來說,材料的阻抗值可以由(2-17)式表示[26] (2-17) 其中R 為材料的電阻值;L 為電流通過的長度;A 為電流通過的截面積; ρ為材料的電阻率。當材料受到應力拉伸或壓縮時,電阻將會因形變以及 阻抗性質改變而產生變化,電阻的改變量如下 (2-18) 其中ε為材料的應變;ν為Poisson’s ratio。此外,在許多論文中,經常會 以gauge factor (G)來討論材料的壓阻性質,G 的表示式如下 (2-19) 對於ㄧ般金屬材料而言,電阻的改變量大部分來自於形狀的改變,所 以G 值都不大,然而像是矽等半導體材料在受到應力改變時,電阻率會有 很大的變化,成為影響G 值非常重要的因素。由 G 值的定義可知,當 G 值 越大,因形變而改變的電阻值也會越大,故擁有較大G 值的材料對於製作 感測器是個很好的選擇。 電阻率可以由下列式子所表示(2-20) 其中π為材料的壓阻係數(piezoresistance coefficient);σ為施加在材料上的 應力(stress)。由材力相關書籍可知,σ=Eε,故可將(2-3)式改寫為 (2-21) 由於半導體晶格對於每個方向的應力所造成的改變均不相同,故每個方向 的壓阻係數也不盡相同。以下是單矽晶在不同方向下的壓阻係數[27]。 (2-22) 11 12 12 12 11 11 44 44 44 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 12 12 11 0 0 0 其中

11、 、12

44之數值列於表 2.,在計算材料的壓阻係數時,若是晶格方 向和 不同時,可以利用尤拉角轉換(圖 21.)得到材料的軸向以及橫 向壓阻係數,其轉換式如下 2 2 2 2 2 2 11 44 12 11 1 1 1 1 1 1 l 2 2 2 2 2 2 t 12 11 12 44 1 2 1 2 1 2 2 2 2 2 2 2 11 44 12 11 ii i i i i i i 2 2 2 2 2 2 1 12 11 12 44 ij 2 i j i j i j 2( )(l m l n m n ) ( )(l l m m n n ) S S (S 2S 2S )(l m l n m n ) S S (S S S )(l l m m n n ) (2-23) 1 1 1 2 2 2 3 3 3 l m n l m n l m nc c c

s s

s c c

c s

s c

c c s

s c

s c s

c c

s s

c s

s s

c

其中S 為材料的 compliance coefficient。另外,由於溫度和雜質濃度也會造 成壓阻係數的改變,所以在不同溫度及不同濃度中,單晶矽的壓阻係數必須做修正,在此以 300K 的壓阻係數π(300K)為基準,並且藉由圖 22.中不同 溫度及濃度的情況,對壓阻係數做修正 (2-24) 最後,將上列式子整理,並找出所需材料的壓阻係數。即可得知壓阻材料 的gauge factor。 (2-25)

2.2.2 多晶矽的壓阻性值

當了解單晶矽的壓阻性質後,可以此與多晶矽電阻率結合,得到多晶 矽的壓阻係數,假設當多晶矽受到應力拉伸時,晶格的部分被拉長,則多 晶矽的gauge factor 可表示為[28] (2-26) 因多晶矽是由許多晶粒所組成,每個晶粒的晶格方向並不相同,若多晶矽 中的每個晶粒,其晶格方向為隨機,此時可對多晶矽的壓阻係數與 compliance coefficient 取平均值,如下所示 (2-27) 從上面的方程式可以算出多晶矽的電阻率以及其G factor2.3 實驗與計算

2.3.1 量測晶粒尺寸

為計算多晶矽之電阻率與壓阻參數 Gauge factor,須了解研究中所使用 CMOS 製程其多晶矽層之相關參數,其中由於多晶矽晶粒尺寸無法得知, 相關文獻中得出晶粒尺寸與其製程有關,故無法由文獻來判斷。為量測多 晶矽層晶粒尺寸,設計一正方型平台,在後製成中將平台上方作為阻擋層 之金屬洗去,以場發式掃瞄電子顯微鏡(SEM)觀察晶粒形狀。如圖 23.,量 測40 項數據後,計算並平均其大小為 241.125nm,標準差為 105.54。2.3.2 理論與實驗驗證

將數值帶回(2-1)式與(2-26)式,得到理論電阻率為 ,實驗值 則是以總電阻計算其數值,其結果為5.5 5.89m mc m c 9 ~ 7.2m m m ,兩者相當接近。Gauge factor 理論值為-6.02,實驗則是以探針給予懸臂樑結構不同位移,並以白光 干涉儀量測最大位移量,由應變量與阻值變化關係(圖 24.)加以計算,其平 均值為5.58,在標準差內其電阻率為3. c ,而Gauge factor 為 -5.5~-11.7。將不同晶粒大小之電阻率與 Gauge factor 數值繪於圖 25.,可看 出其變化規律,若欲增進壓阻性能,可改良製程使其晶粒大小增大。圖11.多晶矽晶粒示意圖

圖13.純矽之能帶與摻雜不同濃度之 P 與 N 型半導體能帶圖

(a)右方加入偏電壓 (b)左方加入偏電壓

圖15.能帶加入偏電壓變化

圖17. (a)自由電子能帶與(b)受晶格限制產生不連續之能帶

圖19.三軸 k 向量空間形成之橢圓形能帶

圖21.尤拉角轉換

N-type Si -102.2 53.4 -13.6 P-type Si 6.6 -1.1 138.1

圖 22.不同溫度及濃度之 n-type 壓阻參數

圖24.結構撓曲與其 gauge factor 關係圖 50 100 150 200 250 300 350 400 450 500 0 0.005 0.01 0.015 0.02 0.025 R es is tiv ity ( Ω -c m ) 50 100 150 200 250 300 350 400 450 500 -10 -8 -6 -4 -2 0 Grain size (nm) G aug e f ac tor

Resistivity Gauge factor

第三章 微致動器結構設計

本章節首先針對致動器各部分元件設計概念詳細說明,並藉由理論推 導將元件做最佳化設計,並以有限元素法之商用模擬軟體加以輔佐與印證。3.1 概述 TSMC 0.35 μm 製程

TSMC 0.35μm 製程為一 2P4M 製程,代表其製程結構含有兩層多晶矽 (Poly Silicon)以及金屬層(Metal),其製程結構如圖 26.所示,兩層多晶矽層 位於製程底部,上方以四層金屬層覆蓋,每層結構均以一層氧化矽層加以 隔開,以避免結構層互相導通,若欲將結構層導通,可在氧化矽層中加入 via 金屬。在一般半導體製程中,將頂端金屬層上覆蓋一層阻擋層即完成元 件製程,但因微機電往往需使結構產生位移,因此必須增加兩道製程手續, 首先是將頂部部分阻擋層蝕刻開,將愈釋放之元件範圍暴露出來,接著以 RLS 溶液繼續向下蝕刻,將結構底部掏空,使元件釋放出來,完成所有製 程。 在幾次的下線和量測後,發現製程中有幾個現象需被加入設計時的考 量,使設計能與製程互相配合,提高元件成品良率。 a. 研究中選擇第二層多晶矽層(Poly 2)為加熱以及感測材料,是從過往設計 後的元件,發現Poly 1 結構層容易遭受破壞,其原因推測是結構層過於b. 切割後的元件晶片在運送時,會以光阻固定結構以避免運送時受到衝擊 而損壞,然而因光阻是以旋轉塗佈的方式平均覆蓋在晶片上,在高速旋 轉時元件容易因離心力使結構斷裂,如圖27.所示,左右的元件是以對稱 方式排列,可發現左邊兩個懸浮平板已斷裂,因此較脆弱的結構設計因 注意在製程或運送時可能受到破壞。 c. 結構層在沉積或是濺鍍過程時,因製程溫度上的差異,以及材料收縮率 不同等因素,當結構溫度回到室溫時,結構層之間會有殘餘應力產生, 此應力在經過元件釋放的過程後,會使元件產生彎曲的現象。如圖28. 所示,中右下角兩個懸空的平板結構,因結構間殘餘應力而產生翹曲的 現象,翹曲量最大可達到數十微米之多,若結構設計為橋梁式,如圖3-3. 上方兩個平板,可有效抑制結構彎曲的情況。

3.2 結構設計

本文所提出之微制動器為一橋樑式結構,如圖 29.(a)(b)所示,元件中包 含電熱驅動器、壓阻式感測器以及吸附平台三個部分,藉由電熱轉換使元 件產生出平面位移,並以壓阻材料特性感測共振頻率,其結構主要設計考 量如下[29]:A. 本研究所使用的感測材料為多晶矽,為一種壓阻材料,由於壓阻材料會 因溫度變化使壓阻性質改變,因此必須將壓阻感測器位置遠離電熱驅動 器。在本研究中藉由選擇橋樑式結構,將驅動與感測元件分別放置於吸 附平台兩端,藉由吸附平台的間隔,降低溫度影響之因素。 B. 懸臂樑結構的特性是一端懸空,擁有較高的靈敏度,但對於外界環境干 擾的影響也會較為明顯。與其相比,橋樑式結構優勢在於其剛性較高, 設計彈性與僅有一端固定的懸臂樑結構高。然而缺點為在相同功率驅動 器所產生之位移量較懸臂樑低,為解決此問題,本研究以壓阻材料作為 橋樑式結構的感測器。此外,感測端可能因中間吸附平台的彎曲使另一 端感測器無法得出預期之位移量,對於微制動器的靈敏度較為不利。因 此,在製程所限制的範圍內提高設計吸附平台的厚度,並選擇合適尺寸, 以減少平台彎曲量。 C. 電熱驅動器是以加熱多晶矽方式加以驅動,由於製程中有兩層矽晶層以 及四層金屬層,選擇適當的層數以及材料,提高驅動器的效率,並且維 持製程產品良率。為使元件擁有較高振動效率,將對結構做最佳化,其 方式將在下面提出。

3.2.1 驅動方式與設計

微振盪器所使用之驅動方式為電熱驅動[30],驅動原理為利用不同結構層之材料熱膨脹係數,當溫度升高時,材料會有不同程度的變形,變形量 較大的材料會被膨脹量較小之材料所限制,使結構產生彎曲變形。給予結 構中具導電性質之材料電壓,將電功率轉為熱能,讓結構層溫度升高,電 壓所產生之熱功率如(3-1)式所示,其中V 為輸入直流電壓,V 為輸入交流 電壓。當電壓源頻率為ω 之交流電時,熱功率將會使結構產生兩倍 ω 的振 動頻率。以直觀思考來看,因交流變的正負偏壓對功率並於差別,因此無 論偏壓值大於或小於0,熱功率皆為正值,元件的變形方向也會相同,因而 產生兩倍頻率之振動。為方便後端電路量測其頻率,若要使輸入電壓與輸 出訊號頻率相同,可給予熱阻一較大的直流偏壓,以及較小的交流電壓源, 降低(3-1)式中交流電源所產生 2ω 頻率的功率,使元件振動頻率與電壓源輸 入頻率相同。 D A 2 21 2 1 2 D 2 A D A 2 A V P V V 2V V sin t V cos 2 t R /R (3-1) 當電能轉換成熱能後,會以熱阻材料為中心向周圍擴散。熱能的傳遞分為 傳導、對流以及輻射[31][32],從相關參考文獻中指出[33],在微結構中熱 能主要是以熱傳導為傳遞方式,熱對流以及熱輻射由於傳遞能料極小,故 先予以忽略。為了使表面金屬溫度有較大的提升,因此必須設計高效率的 電熱驅動端結構。藉由計算等效應力,可以了解影響結構撓曲的因素,並 計算因溫度變化使驅動器對大位移量的改變,幫助設計出在同一溫度下能 達到最大撓曲量的結構。

材料的熱膨脹與其自身熱膨脹係數和溫度差有關,如(3-2)式所示 T (3-2) 其中α 為材料的熱膨脹係數。ε為結構應變量,T 為溫度差,懸臂樑撓曲量 與應力關係為 PL3 3EI---(3-3) ν 為懸臂樑的撓曲量。P 為施予懸臂樑前端之等效力,藉由(3-4)與(3-5)式的 換算,可推導出由熱膨脹所給予懸臂樑的等效力矩。 My I M PL E (3-4) M PL

y dA (3-5) 從(3-2~5)式各式可歸納出,驅動端撓曲的大小與結構的溫度差、楊氏係數、 膨脹係數相關。膨脹係數較高的材料,如金屬,當溫度改變越大,可使結 構撓曲量隨之增加。若結構中心軸兩端金屬比例相差越多,在相同溫度變 化中可以擁有更大的撓曲量。當結構楊氏係數越高,會使結構較不易彎曲。3.2.2 感測方式與設計

微振盪器可利用壓阻材料來感測平台上所負載的重量,使振盪器附有 感測功能[10]。感測方式是利用負載前後共振頻之變化來得到負載重量,此干擾。對一橋樑式微結構,其動態方程式為 2 2 2 2 2 2 w w EI A F x x t (3-6) 式中外力F方向與x相同,對動態系統而言,外力F僅改變系統穩態行為, 對於系統自然頻率並不會產生改變,令 ax w x,t W x Acos t Bsin t ,W x e 可以解得 4 2 n A a and i , EI (3-7) 得到 W x Acosh x Bsinh x Ccos x Dsin x (3-8)

由邊界條件W x 0,l 0,W x 0,l 0,可求得(8)式之係數 A、B、C、D。 以及得到結構之共振頻 2 4 n l EI 1A l4 (3-9) 當平台上有負載時,會使整體ρ密度增加,共振頻會因此降低,利用壓阻 材料對於變形所造成壓阻的明顯變化,感測結構共振頻。為了使感測端易 於變形,設計只使用第一層金屬作為阻擋層,較薄的厚度可使感測結構容 易變形,且避免製程中被破壞。 在製程中往往會有殘餘應力在結構中,造成元件變形甚至損壞,而吸 附平台在吸附不同物質時,亦有可能產生額外的應力,由於此應力方向與 振動方向垂直,將會影響元件的共振頻,無法準確感測負載重量,因此必 須另將應力所產生的影響加以考慮,以得到準確的負載重量。

2 2 2 2 2 2 2 2 w w w EI A 0 x x t x (3-10) (3-10)式為受到橫向應力σ影響的系統動態方程式,J. Wylde與T. J. Hubbard 利用Rayleigh’s method來求解此方程式的數值解,如(3-11)式。 4 2 n 2 EI 14 2 1 w 3 A l 3 l 2 (3-11) 利用不同尺寸之原件吸附重量後所量測的共振頻,將可得到一組聯立方程 式,以此求解可得到吸附重量,以及吸附時所產生之額外應力。

3.3 模擬與分析

在研究中使用商用有限元素分析軟體ANSYS作為分析的工具,詳細比 較不同結構層材料對於溫度以及驅動端撓曲的影響,並以此選擇設計結 構。另外藉由軟體模擬元件受熱後其溫度分布,評估感測端受溫度影響幅 度。 ANSYS模擬採用電、熱與機械結構三種元素做分析,並選擇solid98 作為元素。模擬中僅考慮熱傳導對於結構之熱傳遞,相對於熱對流以及熱 輻射,熱傳導對於結構溫度的影響最為明顯。給與模型邊界條件,並且加 以拘束,最後可得到模型的變形量以及穩態的溫度變化。 在選擇驅動器結構前,必須確認模擬中材料相關參數是否正確,藉由 現有懸臂樑結構,先建立簡易懸臂樑模型,模擬懸臂樑共振頻率,與實驗值互相比較。接著給予懸臂樑電壓加熱,使懸臂樑產生撓曲,其位移情況 同樣與實驗對照。模擬所使用相關參數參照表3.,懸臂樑尺寸如圖30.,長 度為300μm,寬度為20μm,為3.18μm。經由模擬得到結構共振頻為31.273 kHz,實驗則是利用壓電材料激振懸臂樑,並以雷射都普勒觀測各頻率的振 幅,得到確切共振頻,其量測結果為32.470 kHz,證明模擬結果與實驗極 為接近。接著模擬懸臂樑加熱後變形情況,給予懸臂樑輸入2伏特直流電 壓,模擬結果如圖31.,結構最大位移量為 2.58μm。實驗則是利用白光干涉 儀,在給予懸臂樑2伏特電壓源前後量測其位置,觀察懸臂樑撓曲情況, 其結果為2μm,由於實驗使用之懸臂樑有殘留內應力,在受到熱膨脹應力 時會抑制結構彎曲,因此模擬於實驗結果的誤差仍在合理範圍內。由兩項 模擬與實驗數值比較,可確認模擬所使用材料參數的正確性。

3.3.1 電熱驅動結構選擇

本研究所設計之驅動結構中包含一層多晶矽層以及兩層金屬層,如圖 30.,結構長度為 300μm,寬度為20μm,厚度則為3.18μm,多晶矽層結構, 如圖32.所示,為一馬蹄型設計,長度與寬度皆與結構相同,而導線寬度為 5um。由(3-2~5)式中可發現影響結構撓曲因素有溫度差、楊式係數以及熱膨 脹係數,由於金屬與氧化矽楊氏係數相當接近,在製程限制下無法對結構 層位置做更改,因此設計方針將著重於提高表面溫度,以及提高熱膨脹所產生之等效力矩為目標。接著比較下列各項設計: A. 原始設計:結構層組成如圖33.(a)。 B. 將多晶矽層尺寸減半:如圖33.(b),將多晶矽加熱層尺寸縮小為原來的 二分之一,觀察將熱源集中是否能給與局部更大溫度差,產生較大位移 量。 C. 兩層金屬中摻入via:如圖 33.(c),在兩金屬之間的氧化矽中摻入金屬 via,藉由增加膨脹係數較高之金屬含量,使有效力矩的施力面積更廣。 D. 將metal1以氧化矽取代:如圖33.(d),藉由增加熱阻材料與金屬之間氧 化矽的厚度,提高結構層間的溫度梯度,提升結構表面溫度,使金屬膨 脹所造成之等效應力增加。 結構之輸入電壓為 5伏特,主要觀察事項結構最大位移量以及表面溫 度變化,並將其結果整理於表 4.。經由比較後觀察到: a. 與原始設計相比,將多晶矽熱阻材料的尺寸減半,無論是溫度變化 或是撓曲量都因此降低,與預期結果不相同。 b. 將兩層金屬之間摻入via金屬導通,提昇熱能的傳導效率,材料層 之間的溫度差梯度降低,雖然增加金屬可使等效力矩施力範圍增加,但 較低的溫度變化使總熱等效力矩不如預期中大幅度的提升。 c. 將下層金屬層metal 1除去並以氧化矽代替,其結果會使溫度梯度

經由比較後得到以較厚氧化矽層以提高溫度差,再藉由頂端金屬層給 予結構力矩產生彎曲,但若結構越厚,其硬度亦會增加,如圖34.,在給予 相同電壓情況下,結構撓曲量反而不如較薄之設計,因此選擇以至metal 2 層作為驅動端結構之厚度。

3.3.2 結構熱分析模擬

本研究之微振盪器所使用的驅動方式為電熱驅動,因此熱能會由驅動 端擴散至結構各處。由於感測所使用之壓阻材料容易因溫度而改變壓阻性 能,為避免材料特性改變影響感測能力,將結構設計成橋樑式,以分離驅 動以及感測兩部分結構。為確認此設計能否避免感測端受溫度影響,藉由 模擬結構受熱後溫度分布,提升設計的可信度。模擬結構如圖35.所示,元 件左方為電熱驅動器,長度為200μm,寬度為 20μm;中央為吸附平台,其 長寬各為100μm與 200μm;右邊則為壓阻感測器,長度100μm,寬度為 10μm。為避免金屬以及其它易導熱材料導致熱能由驅動端流向感測端,平 台所使用的材料全為氧化矽,由於製程因素,若完全使用氧化矽作為結構 材料,平台厚度將無法自由選擇,由相關資料以及實驗得知,平台厚度約 為4um。在兩驅動端輸入 5伏特之電壓,模擬穩態後振盪器之溫度變化,其結果如圖36.。從結果中觀察到,驅動端表面溫度變化為23~26K,熱能從 驅動端向吸附平台擴散,因吸附平台構成材料為氧化矽,其熱導係數極低, 使熱傳導的溫度梯度相當大,因此在靠近感測端附近溫度變化已降為零, 此結果證明藉由吸附平台的阻隔,可有效避免感測端受到驅動端所產生之 熱能所影響。

3.3.3 元件特性模擬

藉由模擬微振盪器受電壓源後之形變,觀察是否符合設計目標,由於 本研究設計之元件為對稱結構,各項特性均為對稱,故在此僅建立部分元 件之模型,並在對稱處邊界設定為絕熱,以減少硬體計算之負擔,並得到 相同模擬結果。在驅動端給予5伏特之電壓源,模擬結果如圖 37.與圖 38., 圖中看出吸附平台幾乎無任何彎曲,使最大位移量位置於感測端之前端, 最大位移量為0.45μm,此現象符合設計目標,但驅動端變形情況與預測有 所不同,推測原因為結構受到吸附平台與感測端硬度之影響,因此造成驅 動端呈拱橋形狀之變形。將驅動端表面厚度增加並重新模擬,其驅動端隆 起幅度有明顯減小減小,但表面溫度卻亦降低,使得感測端位移並無增加 趨勢,因元件設計之感測方式與共振頻相關,為得到較大共振頻之振福, 因此維持原來設計,以較低剛性來得換取較大之振幅。圖 26. CMOS製程之材料結構層

(a)

(b)

項目 數值 楊氏係數(多晶矽) 160 GPa 楊氏係數(氧化矽) 70GPa 楊氏係數(鋁) 69GPa 密度(多晶矽) 2300 kg/m^3 密度(氧化矽) 2634 kg/m^3 密度(鋁) 2700 kg/m^3 熱導係數(多晶矽) 25 熱導係數(氧化矽) 0.059 熱導係數(鋁) 204 熱膨脹係數(多晶矽) 2.8 熱膨脹係數(氧化矽) 0.5 熱膨脹係數(鋁) 25 比熱(多晶矽) 700 比熱(氧化矽) 840 比熱(鋁) 897 電阻率(多晶矽) 0.056 mΩ*m 表3.材料模擬參數

圖30.懸臂樑模擬尺寸

(a)原設計結構層剖面

(b)多晶矽通道尺寸減半

(c)在氧化矽層摻入via金屬

(d)metal 1以氧化矽取代

表面溫度(⁰C) 最大位移量(μm) 原設計 13.91 1.617 多晶矽層尺寸減半 6.642 1.122 兩層金屬中摻入via 10.162 3.338 將metal1以氧化矽取 代 16.523 3.7 表 4.不同設計之結果比較 圖34.提高厚度時結構撓曲情況(結構層至metal 3)

圖35.元件模擬示意圖

第四章 實驗量測與討論

經由前述章節的研究與模擬,建立微振盪器結構設計,本章節將以 TSMC 0.35μm製程將元件加以實現,並且經由實際量測元件性能,與模擬 結果相比較,量測項目包括元件釋放後之結構,未負載前之穩態量測與頻 率響應,負載後之穩態量測與頻率響應。4.1 元件成品結構

本研究所設計的微振盪器,經由CMOS 製程而得到實際成品(圖39.), 圖中可發現驅動器與感測器均向內插入吸附平台,此情況是由於吸附平台 是以氧化矽構成,考慮製程對準誤差可能造成RLS蝕刻造成結構斷裂,因 此將驅動與感測兩端向中央內縮5μm,防止成品失敗。另外元件周圍呈現 各種顏色,是由於結構厚度不均所產生之現象,推測原因是RLS在侵蝕基 底時,除了將元件釋放,對於邊緣亦有掏空的情況,從SEM 所拍攝之成品 圖40.可看出侵蝕範圍相當廣泛,在量測元件特性以及給予外加電壓是在周 圍設置極板,並經由打線與PCB板連接,若元件距離極版過近,將造成極 板底部被掏空,在打線時容易破裂甚至崩壞,導致元件無法給予電壓及量 測。4.2 未負載元件量測

實驗室以白光干涉儀量測元件之結構,掃描後所得立體結構如圖41., 在此發現其結構變形量相當大,與當初設計之形狀有相當的出入,圖42.左 半部為量測元件中驅動器與吸附平台兩部分,由於驅動與感測兩端位置不 同,因此頗面圖無法同時呈現兩端截面情況,經量測驅動端彎曲幅度結果 為1.23μm,而感測端的彎曲量更大,圖43.左半部為平台與感測端之剖面, 最大高低差為2.57μm。造成此結果的原因,推測是由於結構剛性不高,使 得無法有效抑制殘餘應力所產生之變形,此外,從不同晶圓位置所得到的 元件,結構彎曲量也有所不同,驅動端最大彎曲量可達10μm,此結果證 明殘餘應力對於剛性不高的元件形狀影響相當大

4-2.1 穩態量測

為得到元件位移與感測壓阻之變化,給與驅動端1~4伏特直流電源, 並以白光干涉儀量測,在未輸入電壓源情況下,感測端已有3.45μm 的撓曲 量,記錄各輸入電壓時電阻與撓曲變化,整理列於表5.,並將電阻變化與 應變量關係繪於圖44.。由位移結果,可發現在給與電壓後,驅動端表面金 屬溫度升高產生熱膨脹,其等效力矩使驅動端撓曲量下降,此位移經由吸 附平板傳遞,連帶使得感測端撓曲量下降。由於殘餘應力使結構在未加外 力情況下即有彎曲情況,使受到電熱驅動之位移有所落差。 接著以紅外線測溫儀量測輸入電壓時的溫度分布,以驗證結果是否與度差近60度,但吸附平台的溫度未有明顯上升,在距離驅動端邊緣20μm 位置幾乎沒有溫度改變,此結果與模擬結果互相吻合,代表此設計可避免 感測端之壓阻材料受到驅動端熱能的影響。

4-2.2 頻率響應量測

為量測元件之頻率響應,元量測方法是以網格分析儀給與驅動端不同 頻率之電壓,使元件振動,並量測電阻改變量以判斷共振頻,但由於分析 儀僅能接收電訊號,無法針對電阻作量測,因此研究中利用雷射都普勒作 為量測元件共振頻之儀器。圖46.為量測所得到之結果,由振幅以及相位變 化,得出元件共振頻為65.9 kHz,其值與模擬結果49.71 kHz 有相當差距, 造成推測原因可能是殘餘應力所造成。4-3.負載元件量測

為了證明給予微振盪器負載可改變共振頻率,研究中將在吸附平台上 給予一質量塊,量測給予負載前後穩態與頻率響應有何改變。給予質量塊 的方法是利用聚焦離子束顯微鏡(Focus Ion Beam, FIB),利用儀器可在物體 表面鍍上一塊白金(Pt)金屬,如圖47.所示,因儀器輸入功率大小會對所鍍 的金屬形狀與尺寸有所影響,故以白光干涉儀掃描及量測金屬負載尺寸, 並計算負載重量。在實驗時儀器所設定之尺寸為10μm × 5μm × 1μm, 但經由干涉儀量測結果為15μm × 15μm × 4μm,與設定結果有相當出入。經計算後質量塊重量為 2.04×10^-5 mg,由於所鍍質量塊重量相當大, 將原本翹曲的結構向下壓(圖48.),驅動端前後位移量高達 2.16μm,使結 構形狀變的與原設計相似。

4-3.1 穩態量測

與未負載之元件相同,輸入1~4伏特之直流電源,量測其各部份穩態 位移,量測結果如表6.,當輸入電壓越大,可發現驅動器前端有向上位移 趨勢,而吸附平板兩端差距則越來越大,此現象代表輸入電壓後,驅動端 產生彎曲,但因受吸附平台與感測端影響,使結構形狀呈拱橋狀彎曲,而 感測端則向下撓曲。元件形狀受負載重量影響,將殘餘應力造成之形變減 少,因此其驅動後結構變形情況與模擬相當接近。4-3.2 頻率響應

由理論描述若給與元件負載,其共振頻將會降低。由於給予元件電壓 前須將晶片與PCB板黏合,但聚焦離子束顯微鏡無法容納PCB板,為避免 晶片反覆黏合與分開時遭受破壞,因此再給與負載前直接以壓電片振動方 式量測共振頻率,給予負載後再與PCB板黏合,以電熱驅動量測其共振頻。 負載後元件之頻率響應如圖49.所示,其振幅與向為之頻率響應圖趨勢皆與 未負載元件相同。量測所得共振頻為54.6 kHz,與負載前所量測63.4 kHz負載重量為3.05 10 5mg,而利用白光干涉儀量測負載體積,計算重量為 mg,兩者有些微差距,造成誤差的可能原因除了量測誤差外,從 (3-11)式中表示,結構中的殘餘應力對共振頻亦有影響,因殘餘應力與共振 頻並非比例關係,故無法得知其應力大小。 5 2.04 10 此外,圖50.中也可看出以壓電片振盪與電熱驅動其響應結果之差異, 由低頻到高頻中,壓電片驅動之元件,振幅一直維持在同一範圍,而以電 熱驅動的結果,則發現隨著頻率升高其振幅有下降趨勢。此現象代表當頻 率升高時,結構溫度變化的穩定時間已高於輸入頻率,以至於振幅無法與 低頻時相同。藉由頻率響應圖的概念,可解釋為電熱驅動元件其系統轉移 函數在低頻含有一熱暫態極點,因此隨著頻率越高,系統增益值逐漸下降。

圖39.避免因蝕刻損毀所做補強

驅動端

圖 41.掃描元件變形情況

圖43.量測感測端之變形量(虛線區域為吸附平台,紫色區域微感測端) 輸入電壓 (V) 驅動端撓曲量 (μm) 感測端撓曲量 (μm) 電阻值(kΩ) 0 1.504 3.447 4.259 1 1.379 3.309 4.261 2 1.036 3.154 4.263 3 0.860 3.019 4.265 4 0.704 2.810 4.268 表 5.未負載時輸入電壓與兩端撓曲量之變化

圖44.感測端應變與電阻變化關係圖

圖46.未負載元件之頻率響應

圖48.負載後驅動端撓曲變化 輸入電壓(V) 驅動端撓曲量(μm) 感測端撓曲量(μm) 0V -0.98 μm 2.11μm 1V -0.90 μm 2.14μm 2V -0.80 μm 2.22μm 3V -0.71μm 2.81μm 表6.負載後輸入電壓與兩端撓曲變化

圖49.負載後元件頻率響應圖

第五章 結論

5.1 研究成果

本研究採用TSMC 0.35μm 標準CMOS 製程,在不加入任何後製程的 情況,成功製作出以電熱驅動之微振盪器。且在研究過程中設計出整合電 熱驅動與壓阻感測功能之元件,其中電熱驅動使吸附平台作出平面運動, 同時利用平台帶動令壓阻結構進行感測,元件所占面積為400μm x 200μ m。 由於結構設計與製程殘餘應力所影響,使元件在未驅動情況及造成彎 曲,此現象造成穩態位移不如預期,壓阻材料的量測變化較不明顯,但在 共振頻時由動態頻率響應的量測中,在2伏特驅動電壓下,能使結構產生 0.43μm之共振頻位移,其效能遠比靜電驅動所需功率來的優秀,低電壓輸 入之優勢將易於與IC 電路進行整合。在給予負載後,共振頻的變化能得到 所負載重量,若能克服殘餘應力造成結構變形問題,應能得到更準確的結 果。最後,壓阻材料的性質、元件之穩態形為以及溫度變化分布,經比較 修正與實際量測之結果相符,因此其理論以及模擬結果可提供未來使用者 元件設計製作時做為參考依據。5.2 未來工作

在TSMC 0.35μm 標準CMOS 製程中,可成功製做出所設計元件,其 元件尺寸均與設計相符,但製程所產生之殘餘應力,對於元件作動的性能 有不小的影響,在無法更改製程內容的情況,如何將殘餘應力產生的結構 變形降低,使作動結果更符合設計之預期,將是未來要解決的目標。 另外由於製程最後用於掏空基材之溶液,對結構邊緣均有侵蝕現象, 造成部分結構較易斷裂,在未來的下線設計時,應考量此問題並在晶片規 畫時避開,以避免同樣情況再次產生。 為了確實量測壓阻材料所感測的訊號,未來將與 IC 電路作結合,並將 結構加以持續改良,使量測訊號更為明顯,以利於將來元件產品化。參考文獻

1. J. Buhler, J. Funk, J.G. Korvink, F.-P. Steiner, P.M. Sarro, and H. Baltes,“ Electrostatic aluminum micromirrors using double-pass

metallization,” Journal of Microelectromechanical Systems. 6, pp 126-135, 1997.

2. T. Yasuda, I. Shimoyama, and H. Miura,“ CMOS drivable electrostatic microactuator with large deflection.” The 10th IEEE International

Conference on Micro Electro Mechanical Systems. pp 26-30, 1997.

3. M. Parameswaran, L. Ristic, K. Chau, A.M. Robinson, and W. Allegretto, “ CMOS electrothermal microactuators.” Micro Electro Mechanical

Systems, 'Proceedings, An Investigation of Micro Structures, Sensors, Actuators, Machines and Robots'. , IEEE. pp 128 -131, 1990.

4. M. Huja, and M. Husak,“ Thermal microactuators for optical purpose,” Proceedings of International Conference on Information Technology: Coding and Computing. pp 137 -142, 2001.

5. http://www.analog.com/ 6. http://www.dlp.com/

7. J. Buhler, J.G. Korvink, F.P. Steiner, P.M. Sarro, and H.

baltes, ”Electrostatics aluminum micromirrors using bouble-pass

metallization”, Journal of Microelectromechanical Systems. 6, pp126-135, 1997.

8. K.H.-L. Chau, S.R. Lewis, Y.Zhao, R.T. Howe, S.F. Bart, and R.G. Marcheselli,“ An integrated force-balanced capacitive accelerometeror low-G applications,” Tech. Digest, 9th Int. Conf. Solid-State

9. D.J. Young, and B.E. Boser,“ A micromachine-based RF low-noisevoltage-controlled oscillator,” Custom integrated circuitsconference, proceeding of the IEEE. pp 5-8, 1997.

10. Ioana Voiculescu, Mona E. Zaghloul , R. Andrew McGill, Eric J. Houser, and Gary K. Fedder, “Electrostatically Actuated Resonant Microcantilever Beam in CMOS Technology for the Detection of Chemical Weapons”, IEEE SENSORS JOURNAL, VOL. 5, NO. 4, AUGUST 2005

11. L. Gisela, K. S. J. Pister, and K. P. Roos, “ Standard CMOS piezoresistive sensor to quantify heart cell contractile forces,” Micro Electro Mechanical Systems, 'Proceedings, An Investigation of Micro Structures, Sensors, Actuators, Machines and Systems'. , IEEE. pp 150 -155, 1996.

12. V. Beroulle, Y. Bertrand, L. Latorre, and P. Nouet,“ Micromachined CMOS magnetic field sensors with low-noise signal conditioning,” The 15th IEEE

International Conference on Micro Electro

13. Don Klaitabtim and Adisorn Tuantranont, Design Consideration and Finite Element Modeling of MEMS Cantilever for Nano-Biosensor Applications, Proceedings of 2005 5th IEEE Conference on Nanotechnology, Nagoya, Japan, July 2005

14. H. Lakdawala, and G.K. Fedder,“ CMOS micromachined infraredimager pixel,” Tech. Digest, 11th Int. Conf. Solid-State Sensors and Actuators,

Munich Germany, June, 2001. pp 556-559.

15. G. Zhang, H. Xie, L. E. de Rosset, and G. K. Fedder,“ A lateral capacitive CMOS accelerometer with structural curl compensation,” The Twelfth

IEEE International Conference on Micro Electro Mechanical Systems, 1999, pp. 606 –611.

16. Mohammad M. Mandurah, Krishna C. Saraswat, Theodore I. Kamins, A Model for Conduction in PolycrystallineSilicon-Part I: Theory, IEEE Trans. Electron Device, ED-28, NO. 10 (1981) 1163-71.

17. Semiconductor physics and device, Donald A. Neamen 18. Semiconductor physics, 劉恩科

19. Tsu-Jae King, James P. McVittie, Krishna C. Saraswat, Fellow, and James R. Pfiester, Senior Member, Electrical Properties of Heavily Doped

Polycrystalline Silicon-Germanium Films IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41, NO. 2, FEBRUARY 1994

20. Lucia Romano,* Alberto Maria Piro, and Maria Grazia Grimaldi, Effect of Strain on the Carrier Mobility in Heavily Doped p-Type Si PHYSICAL REVIEW LETTERS 29 SEP (2006)

21. Nicky Chau Chun Lu, Levy Gerzberg, Chih Yuan Lu, James D Meindl, Modelling and optimisation of monolithic polycrystalline silicon resistors, IEEE Trans. Electron Device, ED-28, NO. 10 (1981) 818-29

22. Dae M. Kim, A. N. Khondker, S. Sahmed, and Rajiv R. Shah, Theory of Conduction in Polysilicon: Drift-Diffusion Approach in

Crystalline-Amorphous-Crystalline Semiconductor System---Part I: Small Signal Theory, IEEE Transaction on Electron Device, Vol. ED-31, NO. 4, April 1984

23. R. W. Keyes, “The effect of elastic deformation on the electrical

24. Conyers Herring, Erich Vogt, Transport and Deformation-Potential Theory for Many-Valley Semiconductors with Anisotropic Scattering, physical Review, Vol 101, num 3, Feb 1,1956

25. M. Dean and R. D. Douglas, Eds., Semiconductor Strain Gauges, New York: Academic Press, 1962.

26. Tyler Lane Waterfall, Design of Piezoresistive MEMS Force and Displacement Sensors.

27. Y. Kanda, A graphical representation of the piezoresistance coefficients in silicon, IEEE Trans. Electron Device, ED-29 (1982) 64-70.

28. P. J. French, A. G. R. Evans, Piezoresistance in polysilicon, Electronics Letters, Vol20, NO.24, 1984

29. Brand, Oliver, CMOS-MEMS, 2005

30. Lange, D. (Dirk), CMOS cantilever sensor systems : atomic force microscopy and gas sensing applications, 2002

31. Heat Tranfer Analysis, Xiang Li 32. Holman, J. P., Heat Tranfer

33. Li-Sheng Zheng, Michael S.-C. Lu, A large-displacement CMOS micromachined thermal actuator with comb electrodes for capacitive sensing, Sensors and Actuators A 136 (2007) 697–703